## **General description**

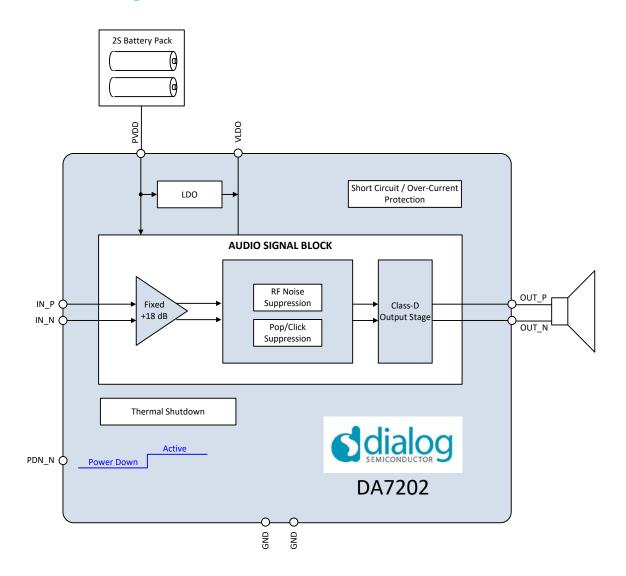

DA7202 is a powerful, high efficiency, low EMI Class-D speaker driver that can drive 10 W into 4  $\Omega$  loads directly from a 2S lithium ion battery pack.

DA7202 is a standalone high performance mono Class-D audio amplifier targeted at powering a variety of two cell portable applications such as Ultrabooks<sup>™</sup> and tablets.

It uses a fully-differential switched mode amplifier architecture with a fixed +18 dB gain, with differential analogue inputs. It also has a PWM modulator and an H-bridged switched power output stage that delivers 8 W into an 8  $\Omega$  load, making a speaker sound louder on portable devices.

The DA7202 can be directly connected between the two-cell battery and the speaker. Noise suppression circuitry to reduce audible pops and clicks at the speaker output is also included.

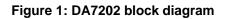

Available as a 9-bump WL-CSP package with 0.5 mm pitch that is suited to low cost PCB technology, it is ideal for portable applications that require small footprints.

## **Key features**

- PRMS: 3.8 W into 8 Ω load at 8.2 V, 1% THD+N

- Efficiency: 90% @ Pout = 3.5 W at 8.2 V, 8 Ω and 85%@Pout = 7.0 W at 8.2 V, 4 Ω

- Supports 4  $\Omega$  and 8  $\Omega$  loads

- SNR (A-weighted) 104 dB

- THD+N: 94 dB @ 3.0 W, 8.2 V, 8 Ω

- PSRR: 78 dB

## **Applications**

- Tablets

- Personal navigation devices

- Ultrabooks<sup>™</sup>

- Auto-Shutdown/Start-up: <3.5 ms</li>

- Ultra low standby current: 7 μA

- Short-Circuit & Thermal-Overload Protection with auto recovery

- Wide supply voltage range 4.5 to 9.0 V

- 9-bump WL-CSP with 0.5 mm pitch

- 2S battery pack

- Speaker accessories

- Handheld gaming devices

10 W Mono Class-D Amplifier for 2S Battery Devices

## Contents

| Ge  | General description |                                                                 |            |  |  |  |  |

|-----|---------------------|-----------------------------------------------------------------|------------|--|--|--|--|

| Ke  | y featu             | Ires                                                            | . 1        |  |  |  |  |

| Ар  | plicati             | ons                                                             | .1         |  |  |  |  |

| Co  | ntents              | 5                                                               | . 2        |  |  |  |  |

| Fig | jures               |                                                                 | . 3        |  |  |  |  |

| Tal | bles                |                                                                 | . 3        |  |  |  |  |

| 1   | Term                | s and definitions                                               | . 4        |  |  |  |  |

| 2   | Block               | diagram                                                         | . 5        |  |  |  |  |

| 3   | Pinou               | ıt                                                              | . 6        |  |  |  |  |

| 4   | Abso                | lute maximum ratings                                            | .7         |  |  |  |  |

| 5   | Reco                | mmended operating conditions                                    | . 8        |  |  |  |  |

| 6   | Elect               | rical characteristics                                           | . 9        |  |  |  |  |

| 7   | Therr               | nal protection                                                  | . 9        |  |  |  |  |

| 8   |                     | tional description                                              |            |  |  |  |  |

| •   | 8.1                 | Pop and click suppression                                       |            |  |  |  |  |

|     | 8.2                 | Short circuit/over-current protection                           |            |  |  |  |  |

|     | 8.3                 | Thermal performance and thermal protection                      |            |  |  |  |  |

|     |                     | 8.3.1 Thermal shutdown                                          |            |  |  |  |  |

|     |                     | 8.3.2 Maximum power dissipation                                 |            |  |  |  |  |

|     | 8.4                 | Gain                                                            |            |  |  |  |  |

|     | 8.5                 | Class D output stage                                            |            |  |  |  |  |

|     | 8.6                 | Power down (PDN_N)                                              |            |  |  |  |  |

| 9   | Typic               | al performance plots                                            | 12         |  |  |  |  |

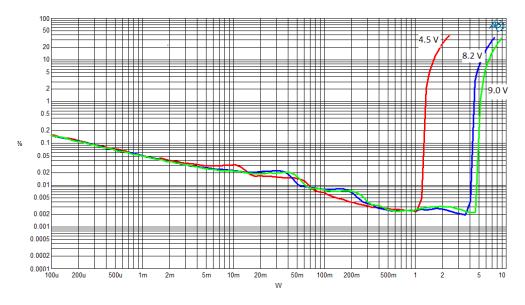

|     | 9.1                 | THD versus output power (8 $\Omega$ + 33 $\mu$ H)               |            |  |  |  |  |

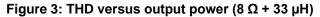

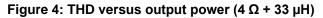

|     | 9.2                 | THD versus output power (4 $\Omega$ + 33 $\mu$ H)               |            |  |  |  |  |

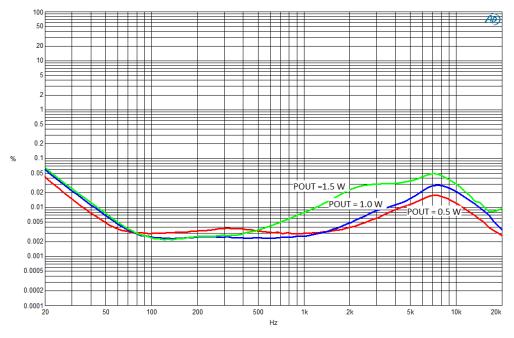

|     | 9.3                 | THD versus frequency (8 $\Omega$ + 33 $\mu$ H) 4.5 V            |            |  |  |  |  |

|     | 9.4                 | THD versus frequency (4 $\Omega$ + 33 $\mu$ H) 4.5 V            |            |  |  |  |  |

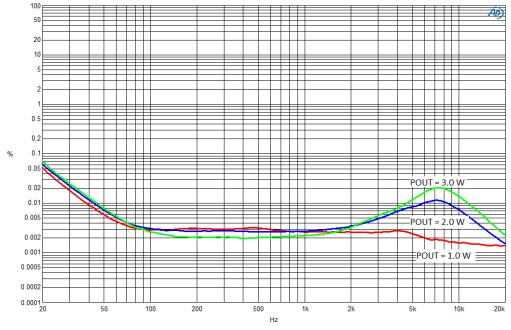

|     | 9.5                 | THD versus frequency (8 $\Omega$ + 33 $\mu$ H) 8.2 V            |            |  |  |  |  |

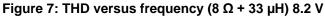

|     | 9.6                 | THD versus frequency (4 $\Omega$ + 33 $\mu$ H) 8.2 V            |            |  |  |  |  |

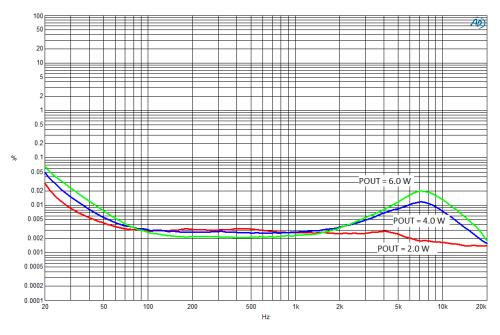

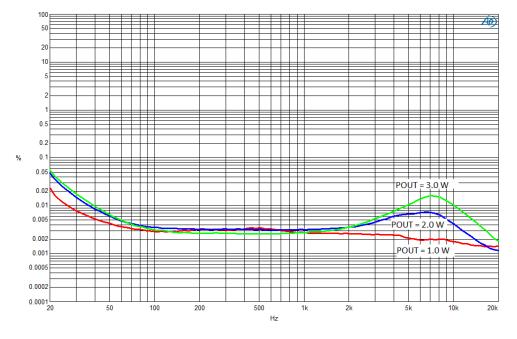

|     | 9.7                 | THD versus frequency (8 $\Omega$ + 33 $\mu$ H) 9.0 V            |            |  |  |  |  |

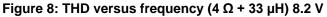

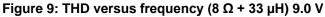

|     | 9.8                 | THD versus frequency (4 $\Omega$ + 33 $\mu$ H) 9.0 V            |            |  |  |  |  |

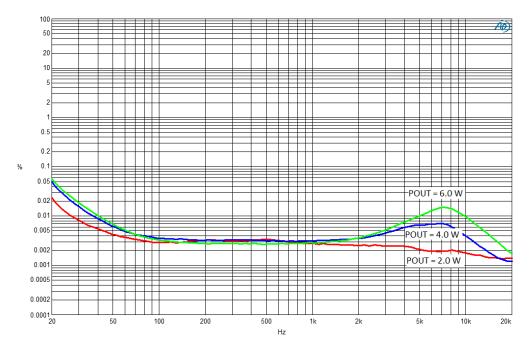

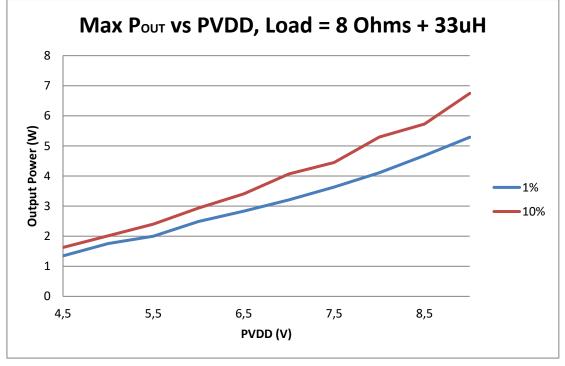

|     | 9.9                 | Max $P_{out}$ versus supply voltage (8 $\Omega$ + 33 $\mu$ H)   |            |  |  |  |  |

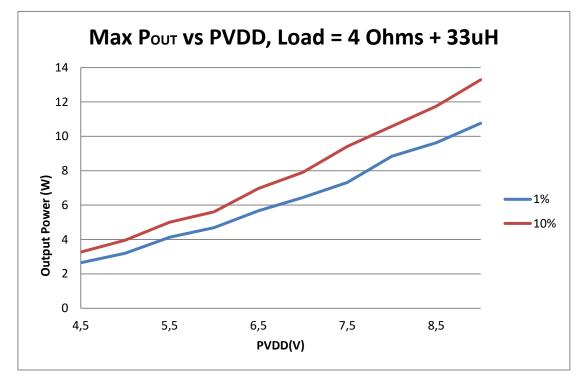

|     | 9.10                | Max $P_{out}$ versus supply voltage (4 $\Omega$ + 33 $\mu$ H)   |            |  |  |  |  |

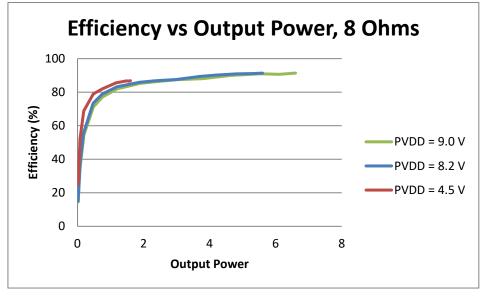

|     | 9.11                | Efficiency versus output power (8 $\Omega$ + 33 $\mu$ H)        |            |  |  |  |  |

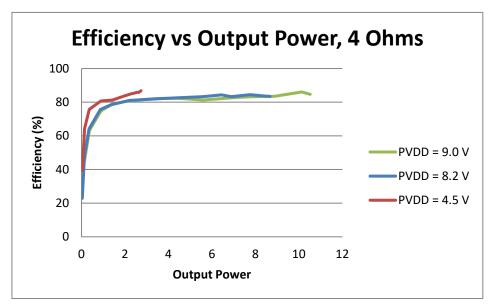

|     | 9.12                | Efficiency versus output power (4 $\Omega$ + 33 $\mu$ H)        |            |  |  |  |  |

|     | 9.13                | Start-up timing                                                 |            |  |  |  |  |

|     | 9.14                | Shutdown timing                                                 |            |  |  |  |  |

|     | 9.15                | Power dissipation versus output power (8 $\Omega$ + 33 $\mu$ H) | 19         |  |  |  |  |

|     | 9.16                | Power dissipation versus output power (4 $\Omega$ + 33 $\mu$ H) |            |  |  |  |  |

|     | 9.17                | Electromagnetic interference (EMI) performance                  |            |  |  |  |  |

| 10  | Appli               | cation information                                              |            |  |  |  |  |

|     |                     |                                                                 |            |  |  |  |  |

| νď  | tashee              | et Revision 3.4 23-Dec-20                                       | <b>Z</b> I |  |  |  |  |

# 10 W Mono Class-D Amplifier for 2S Battery Devices

| Re | vision | history                                      |    |

|----|--------|----------------------------------------------|----|

| 12 | Orde   | ring information                             | 25 |

|    | 11.4   | Soldering information                        |    |

|    | 11.3   | WLCSP Handling                               |    |

|    |        | Moisture Sensitivity Level (MSL)             |    |

|    | 11.1   | Package outlines                             |    |

| 11 | Pack   | age information                              |    |

|    |        | 10.5.2 Input and output capacitor properties |    |

|    |        | 10.5.1 Input and output capacitors           |    |

|    | 10.5   | Capacitor selection                          |    |

|    | 10.4   | Recommended external components              |    |

|    | 10.3   | Recommended external component layout        |    |

|    | 10.2   | Speaker selection                            |    |

|    | 10.1   | PCB layout                                   | 21 |

# **Figures**

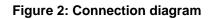

| Figure 1: DA7202 block diagram<br>Figure 2: Connection diagram                                | 5  |

|-----------------------------------------------------------------------------------------------|----|

| Figure 2: Connection diagram                                                                  | 6  |

| Figure 3: THD versus output power (8 $\Omega$ + 33 $\mu$ H)                                   | 12 |

| Figure 4: THD versus output power (4 $\Omega$ + 33 $\mu$ H)                                   | 12 |

| Figure 5: THD versus frequency (8 $\Omega$ + 33 $\mu$ H) 4.5 V                                | 13 |

| Figure 6: THD versus frequency (4 $\Omega$ + 33 $\mu$ H) 4.5 V                                | 13 |

| Figure 7: THD versus frequency (8 $\Omega$ + 33 $\mu$ H) 8.2 V                                | 14 |

| Figure 8: THD versus frequency (4 $\Omega$ + 33 $\mu$ H) 8.2 V                                | 14 |

| Figure 9: THD versus frequency (8 $\Omega$ + 33 $\mu$ H) 9.0 V                                | 15 |

| Figure 10: THD versus frequency (4 $\Omega$ + 33 $\mu$ H) 9.0 V                               | 15 |

| Figure 11: Maximum output power (Pout) versus supply voltage (8 Ω + 33 μH)                    | 16 |

| Figure 12: Maximum output power ( $P_{out}$ ) versus supply voltage (4 $\Omega$ + 33 $\mu$ H) | 16 |

| Figure 13: Efficiency versus output power (8 $\Omega$ + 33 $\mu$ H)                           | 17 |

| Figure 14: Efficiency versus output power (4 $\Omega$ + 33 $\mu$ H)                           | 17 |

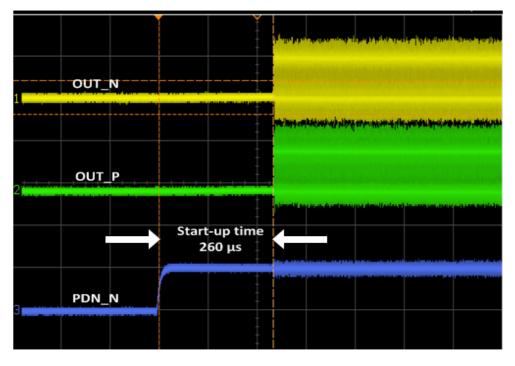

| Figure 15: Start-up timing (260 µs from asserting PDN_N to valid output)                      | 18 |

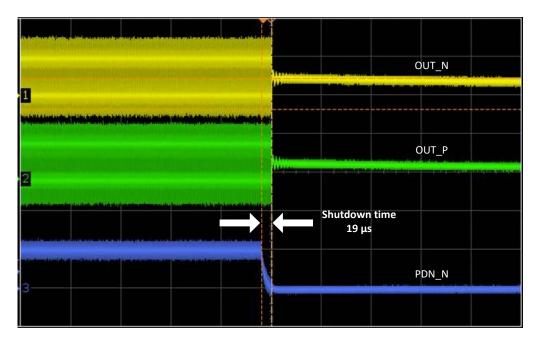

| Figure 16: Shutdown timing (19 µs from de-asserting PDN_N to zero output)                     | 18 |

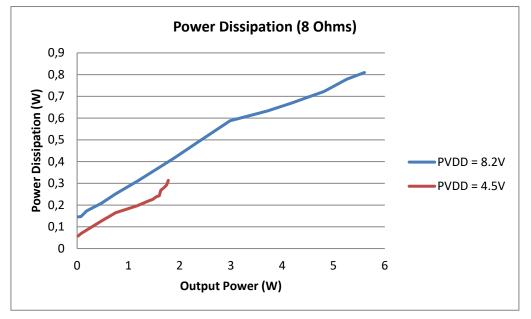

| Figure 17: Power dissipation versus output power (8 $\Omega$ + 33 $\mu$ H)                    | 19 |

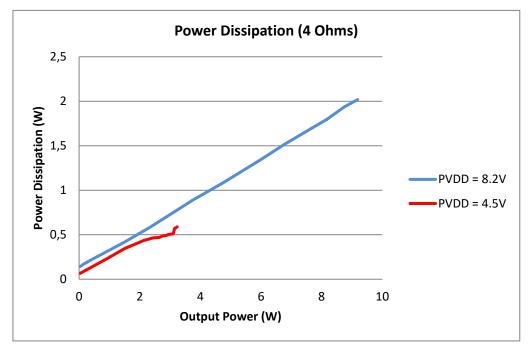

| Figure 18: Power dissipation versus output power (4 $\Omega$ + 33 $\mu$ H)                    | 19 |

| Figure 19: EMI performance with FCC Class-D limit also shown                                  | 20 |

| Figure 20: Layout of recommended external components and their values                         | 22 |

| Figure 21: Performance plot of the sample capacitor used in the example (below)               | 23 |

| Figure 22: DA7202 package outline drawing (9-bump WL-CSP 0.5 mm pitch)                        | 24 |

## **Tables**

| Table 1: Pin description                  | 6  |

|-------------------------------------------|----|

| Table 2: Absolute maximum ratings         | 7  |

| Table 3: Recommended operating conditions | 8  |

| Table 4: Digital inputs (PDN_N)           | 9  |

| Table 5: Analog inputs (IN_P, IN_N)       |    |

| Table 6: Thermal protection               | 9  |

| Table 7: Actions of the PDN_N pin         |    |

| Table 8: Recommended external components  | 22 |

| Table 9: Ordering information             | 25 |

| 5                                         |    |

10 W Mono Class-D Amplifier for 2S Battery Devices

## **1** Terms and definitions

| EMC    | Electromagnetic Compatibility        |

|--------|--------------------------------------|

| EMI    | Electromagnetic Interference         |

| FCC    | Federal Communications Commission    |

| LDO    | Low Dropout regulator                |

| PCB    | Printed Circuit Board                |

| PWM    | Pulse Width Modulation               |

| PSRR   | Power Supply Rejection Ratio         |

| RF     | Radio Frequency                      |

| RMS    | Root Mean Square                     |

| SNR    | Signal to Noise Ratio                |

| THD    | Total Harmonic Distortion            |

| THD+N  | Total Harmonic Distortion plus Noise |

| WL-CSP | Wafer Level-Chip Scale Packaging     |

|        |                                      |

## 2 Block diagram

10 W Mono Class-D Amplifier for 2S Battery Devices

## 3 Pinout

| Pin no. | Pin name | Description             |

|---------|----------|-------------------------|

| A1      | IN_P     | Positive Analogue Input |

| A2      | GND      | Ground                  |

| A3      | OUT_N    | Negative Output         |

| B1      | VLDO     | Output voltage from LDO |

| B2      | GND      | Ground                  |

| B3      | PVDD     | Power Supply            |

| C1      | IN_N     | Negative Analogue Input |

```

Datasheet

```

**Revision 3.4**

# **10 W Mono Class-D Amplifier for 2S Battery Devices**

| Pin no. | Pin name | Description                                      |

|---------|----------|--------------------------------------------------|

| C2      | PDN_N    | Power Down Control (0 = Power Down / 1 = Active) |

| C3      | OUT_P    | Positive Output                                  |

## 4 Absolute maximum ratings

#### Table 2: Absolute maximum ratings

| Parameter | Description                            | Conditions (Note 1) | Min  | Тур  | Мах            | Unit |

|-----------|----------------------------------------|---------------------|------|------|----------------|------|

|           | Storage temperature                    |                     | -65  |      | +85            | °C   |

|           | Operating temperature                  |                     | -45  |      | +85            | °C   |

|           | Junction temperature (T <sub>J</sub> ) |                     |      |      | +150           | °C   |

| PVDD      | - Supply voltage                       |                     | +4.5 | +8.2 | +10.0          | V    |

| VLDO      |                                        |                     |      | +5.0 |                | V    |

| PDN_N     | Power down control                     |                     | -0.3 |      | +5.0<br>(VLDO) | V    |

|           | ESD susceptibility                     | Human body model    |      |      | 2              | kV   |

**Note 1** Stresses beyond those listed under 'Absolute maximum ratings' may cause permanent damage to the device. These are stress ratings only, so functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specification are not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

**Datasheet**

## 5 Recommended operating conditions

#### **Table 3: Recommended operating conditions**

$V_{\text{DD}}$  = 8.2 V,  $T_{\text{A}}$  = 25°C,  $R_{\text{L}}$  = 8  $\Omega$  +33  $\mu H,$  unless otherwise noted.

| Parameter              | Description                                   | Conditions                                                                        | Min | Тур | Max  | Unit |

|------------------------|-----------------------------------------------|-----------------------------------------------------------------------------------|-----|-----|------|------|

| PVDD                   |                                               |                                                                                   | 4.5 |     | 9.0  | V    |

| VLDO                   | Supply voltage                                | Output                                                                            |     | 5.0 |      | V    |

|                        |                                               |                                                                                   |     | 30  |      | kΩ   |

|                        |                                               |                                                                                   | 18  |     |      | μH   |

| Prms                   |                                               | $R_{LOAD} = 8 \Omega$ $V_{PWR} = 8.2 V$ $THD+N = 1\%$                             |     | 3.8 |      | W    |

| Pmpo (rms)             | Output power                                  | $R_{LOAD} = 8 \Omega$ $V_{PWR} = 8.2 V$ $THD+N = 1\%$                             |     |     | 7.6  | W    |

| P <sub>RMS</sub>       |                                               | $R_{LOAD} = 4 \Omega$ $V_{PWR} = 8.2 V$ $THD+N = 1\%$                             |     | 8.0 |      | W    |

| P <sub>MPO (RMS)</sub> |                                               | $R_{LOAD} = 4 \Omega$ $V_{PWR} = 8.2 V$ $THD+N = 1\%$                             |     |     | 10.0 | W    |

|                        | Efficiency                                    | P <sub>OUT</sub> = 3.5 W<br>R <sub>LOAD</sub> = 8 Ω + 18 $\mu$ H<br>audio = 1 kHz |     |     | 90   | %    |

|                        | THD+N                                         | Pout = 3.0 W, 8 Ω, 8.2 V                                                          |     | 94  |      | dB   |

|                        | SNR                                           |                                                                                   |     | 104 |      | dB   |

|                        | PSRR (AC grounded)                            | Frequency = 217 Hz                                                                |     | 78  |      | dB   |

|                        | Gain                                          | Fixed                                                                             |     | 18  |      | dB   |

|                        | Output switching<br>frequency                 | Fixed                                                                             |     | 1   |      | MHz  |

|                        | Output Noise (RMS)                            | Integrated over bandwidth<br>SNR = 99 dB,<br>Gain = 18 dB                         |     |     | 60   | μV   |

|                        | Standby current<br>consumption at<br>Shutdown |                                                                                   |     | 7   |      | μA   |

## **6** Electrical characteristics

#### Table 4: Digital inputs (PDN\_N)

| Parameter | Description                   | Conditions                                    | Min | Тур | Max          | Unit |

|-----------|-------------------------------|-----------------------------------------------|-----|-----|--------------|------|

| Vін       | Input-Voltage High            |                                               | 1.3 |     | +5<br>(VLDO) | V    |

| VIL       | Input-Voltage Low             |                                               | 0   |     | 0.7          | V    |

|           | Input Hysteresis              |                                               |     | 0.4 |              | V    |

| Іін       | Input High Leakage<br>current | V <sub>IN</sub> =5 V,<br>T <sub>A</sub> =25°C |     |     | 25           | μA   |

| lı.       | Input Low Leakage current     | V <sub>IN</sub> =GND,<br>T <sub>A</sub> =25°C |     |     | 0.1          | μA   |

**Note 2**  $V_{IH}$  and  $V_{IL}$  define logic levels to enable or disable the DA7202.

#### Table 5: Analog inputs (IN\_P, IN\_N)

| Parameter | Description        | Conditions | Min | Тур | Max  | Unit |

|-----------|--------------------|------------|-----|-----|------|------|

|           | Audio input signal |            |     |     | +5.0 | V    |

## 7 Thermal protection

Monitoring of the ambient temperature does not guarantee that the junction temperature (T<sub>J</sub>) is within the specified temperature limits.

The junction temperature of the device is dependent on the ambient temperature (T<sub>A</sub>), the power dissipation of the device (P<sub>D</sub>), and the junction-to-ambient thermal resistance of the package ( $\theta_{JA}$ ). An estimation of the junction temperature (T<sub>J</sub>) can be calculated using the formula

$$T_{J} = T_{A} + (P_{D} \times \theta_{JA})$$

Where:

- T<sub>J</sub> = junction temperature

- T<sub>A</sub> = ambient temperature of the package (°C)

- P<sub>D</sub> = power dissipation of the package (W)

- $\theta_{JA}$  = junction to ambient thermal resistance (°C / W) = 72°C/W

The value of  $\theta_{JA}$  can vary, depending on PCB material, the layout, and the environmental conditions. The specified value of  $\theta_{JA}$  (72°C/W) is based on a 4-layer, 101.5 mm x 114.5 mm circuit board as specified in the JEDEC standard JESD51-9.

| Parameter | Description                           | Conditions | Min | Тур | Max | Unit |

|-----------|---------------------------------------|------------|-----|-----|-----|------|

|           | Thermal Shutdown<br>Threshold         |            |     | 150 |     | °C   |

|           | Thermal Shutdown Restart<br>Threshold |            |     | 100 |     | °C   |

|           | Thermal Shutdown<br>Hysteresis        |            |     | 50  |     | °C   |

#### **Table 6: Thermal protection**

# 10 W Mono Class-D Amplifier for 2S Battery Devices

| Parameter | Description                            | Conditions | Min | Тур | Max | Unit |

|-----------|----------------------------------------|------------|-----|-----|-----|------|

| θյΑ       | Junction to ambient thermal resistance |            |     | 72  |     | °C/W |

## 8 Functional description

The DA7202 is a powerful, high efficiency, low EMI Class-D speaker driver that can drive a maximum of 10 W into 4  $\Omega$  loads directly from a 2S lithium ion battery pack.

The device provides audio noise and RF noise suppression. It also has short circuit protection, as well as protection against over-heating.

The DA7202 is available in a 9-bump WL-CSP package with 0.5 mm pitch that enables low cost PCB technology which is ideal for portable applications that require small footprints.

### 8.1 **Pop and click suppression**

DA7202 includes noise suppression circuitry that reduces audible pops and clicks at the speaker output when enabling or disabling the device.

### 8.2 Short circuit/over-current protection

The DA7202 is protected by a short circuit/over current detector. If a short circuit is detected, regardless of the frequency of the signal, the device is disabled immediately. After 8 ms, the short-circuit status is checked. If the short condition has been resolved, the chip will be re-enabled. If the short condition still persists, the DA7202 remains disabled. The short-circuit status is checked every 8 ms until the short condition has been resolved. The chip will then be re-enabled.

Note that the disabling of the chip, and its later re-enabling, are both performed without using the noise suppression circuitry. Audible artefacts may be present in the output signal.

Note also that whenever the DA7202 has been powered down, the power stage is placed in a high impedance (high-Z) state to minimise power consumption.

### 8.3 Thermal performance and thermal protection

#### 8.3.1 Thermal shutdown

DA7202 is provided with a thermal protection feature that automatically disables the power stage and the LDO if the junction temperature reaches 150°C.

When a thermal shutdown is performed, the chip is disabled, leaving only the temperature sensor block active. The process of disabling the chip is performed using the noise suppression circuitry, so no audible artefacts will be present on the output signal during the disabling process. The time taken for a noise free shutdown is illustrated in Figure 16.

If thermal shutdown is activated, the chip is not re-enabled until the temperature has dropped to 100°C. Once the temperature has reached 100°C, the DA7202 restarts with an automatic soft start. The process of re enabling the chip is performed using the noise suppression circuitry, so no audible artefacts will be present on the output signal during start-up process. The time taken for a noise free start-up is illustrated in Figure 15.

Note that whenever the DA7202 has been powered down, the power stage is placed in a high impedance (high-Z) state to minimise power consumption.

#### 8.3.2 Maximum power dissipation

Given the Junction-to-Ambient thermal impedance (72°C/W), the Power Dissipation versus Output Power (from Figure 17 and Figure 18), and the maximum junction temperature ( $T_{J(MAX)}$  specified in

Datasheet

Table 6), it is possible to calculate the maximum ambient temperature  $(T_{A(MAX)})$  using the following equation:

$$T_{A(MAX)} = T_{J(MAX)} - \theta_{JA} \times P_{D(MAX)}$$

Up to an ambient temperature of 85°C, DA7202 can dissipate 0.56 W of heat before reaching 125°C.

Note that if the DA7202 is operated continuously at, or close to, its maximum output power, there is a risk of overheating and thermal shutdown unless steps are taken to dissipate this excess heat.

### 8.4 Gain

The DA7202 has a fixed gain of +18 dB.

Output volume is directly proportional to the input signal strength. It is assumed that any required variation in output volume will be controlled by varying the DA7202 input signal. The input signal amplitude can be reduced by the use of resistor dividers in conjunction with the known input impedance.

### 8.5 Class D output stage

The class D output stage is connected directly to the PVDD (two cell battery pack) power supply. High-efficiency operation is achieved by operating the output transistors as switches. The output power transistors are either fully On or fully Off, providing a minimum resistance path for current from the power supply to the load. The block's outputs are connected directly to the speaker at OUT\_P and OUT\_N.

Filterless operation is achieved by connecting a load (a speaker) between the output terminals of the Class D ouput block. As a result, the voltage across the load represents a PWM (Pulse Width Modulated) audio signal, while the output current in the load is a filtered, demodulated representation of the input audio signal.

For filterless operation, the speaker load can be considered as a first order output filter with a cut-off frequency well below the PWM carrier signal (the current in the load is a filtered version of the output PWM voltage signal). See section 10.2 for further detail on speaker selection.

### 8.6 Power down (PDN\_N)

The DA7202 is powered down by pulling the PDN\_N pin low. When the device is powered down, a controlled shutdown process is performed, thus ensuring that there are no audible artefacts (pops and clicks) on the output path.

The time to disable the device is illustrated in Figure 16.

#### Table 7: Actions of the PDN\_N pin

| PDN_N Value | Description |

|-------------|-------------|

| 0           | Power Down  |

| 1           | Active      |

10 W Mono Class-D Amplifier for 2S Battery Devices

## 9 Typical performance plots

## 9.1 THD versus output power (8 $\Omega$ + 33 $\mu$ H)

### 9.2 THD versus output power (4 $\Omega$ + 33 $\mu$ H)

## 9.3 THD versus frequency (8 $\Omega$ + 33 $\mu$ H) 4.5 V

## 9.4 THD versus frequency (4 $\Omega$ + 33 $\mu$ H) 4.5 V

Figure 6: THD versus frequency (4  $\Omega$  + 33  $\mu$ H) 4.5 V

| _  |     | -   |      |

|----|-----|-----|------|

| na | tas | hc  | sof. |

| υa | เลอ | 116 | eet. |

## 9.5 THD versus frequency (8 $\Omega$ + 33 $\mu$ H) 8.2 V

### 9.6 THD versus frequency (4 $\Omega$ + 33 $\mu$ H) 8.2 V

### 9.7 THD versus frequency (8 $\Omega$ + 33 $\mu$ H) 9.0 V

### 9.8 THD versus frequency (4 $\Omega$ + 33 $\mu$ H) 9.0 V

Figure 10: THD versus frequency (4  $\Omega$  + 33  $\mu$ H) 9.0 V

10 W Mono Class-D Amplifier for 2S Battery Devices

## 9.9 Max $P_{out}$ versus supply voltage (8 $\Omega$ + 33 $\mu$ H)

Figure 11: Maximum output power ( $P_{out}$ ) versus supply voltage (8  $\Omega$  + 33  $\mu$ H)

### 9.10 Max P<sub>out</sub> versus supply voltage (4 $\Omega$ + 33 $\mu$ H)

Figure 12: Maximum output power ( $P_{out}$ ) versus supply voltage (4  $\Omega$  + 33  $\mu$ H)

Datasheet

## 9.11 Efficiency versus output power (8 $\Omega$ + 33 $\mu$ H)

Figure 13: Efficiency versus output power (8  $\Omega$  + 33  $\mu$ H)

## 9.12 Efficiency versus output power (4 $\Omega$ + 33 $\mu$ H)

## 9.13 Start-up timing

Figure 15: Start-up timing (260 µs from asserting PDN\_N to valid output)

## 9.14 Shutdown timing

Figure 16: Shutdown timing (19 µs from de-asserting PDN\_N to zero output)

## 9.15 Power dissipation versus output power (8 $\Omega$ + 33 $\mu$ H)

Figure 17: Power dissipation versus output power (8  $\Omega$  + 33  $\mu$ H)

## 9.16 Power dissipation versus output power (4 $\Omega$ + 33 $\mu$ H)

Figure 18: Power dissipation versus output power (4  $\Omega$  + 33  $\mu$ H)

| D | at | a  | sh  | e | et |

|---|----|----|-----|---|----|

|   | a  | C. | 511 | 6 |    |

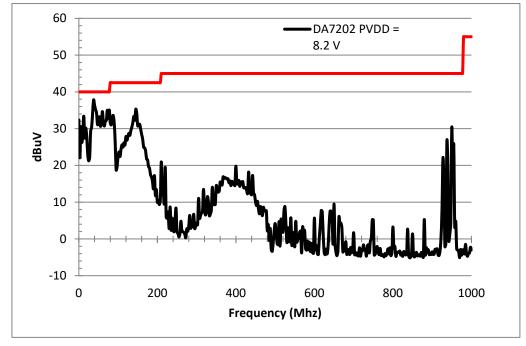

## 9.17 Electromagnetic interference (EMI) performance

#### Figure 19: EMI performance with FCC Class-D limit also shown

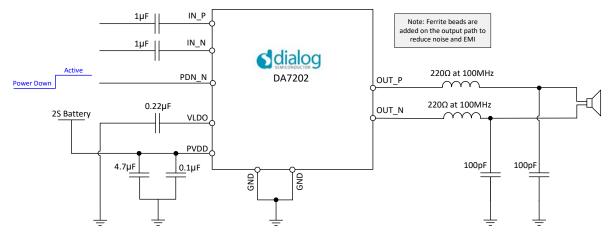

**Note 3** Measurements taken using a typical layout as illustrated in Figure 20 (speaker cable length = 12 cm).

## **10** Application information

### 10.1 PCB layout

The performance of the DA7202 relies on good PCB layout. Failure to follow best practice can have undesired side effects that include, but are not limited to, electromagnetic interference (EMI) and electromagnetic compatibility (EMC) problems, ground bounce, and voltage losses. Poor layout can also affect regulation and stability. Dialog Semiconductor recommend that the following guidelines are followed:

- Place any input capacitors and output capacitors close to the device using short tracks. These components carry high switching frequencies, and long tracks can act as an antenna.

- Maximise the size of ground metal on the component side to help with thermal dissipation.

- Use a ground plane with several vias connecting to the component side ground to further reduce noise interference on sensitive circuit nodes.

- If external resistors are to be used to change the gain, these should be placed close to the device.

- It is recommended that ferrite beads are included on the output paths to reduce EMI interference and noise.

## **10.2 Speaker selection**

The output from the DA7202 Class-D amplifier contains high frequency signals that are a result of its switched PWM operation. These high frequency harmonics are at a much higher frequency than is recommended for most speakers, so they must be filtered out to protect the speaker.

The correct choice of speaker is therefore important since the speaker itself can act as a low-pass filter, attenuating the undesirable high frequency harmonics while still passing the desired audio frequencies.

The 3 dB cut-off frequency for speaker inductance and resistance can be calculated using the following formula:

#### $f_c = R_{LOAD} / 2\pi L$

Therefore to achieve a 3 dB cut-off frequency of 20 kHz with an 8  $\Omega$  speaker, a speaker should be selected with an inductance of:

#### L = R<sub>LOAD</sub> / $2\pi fc$ = 8 $\Omega$ / $2\pi$ \* 20 kHz = 64 $\mu$ H

8 Ω speakers for portable applications typically have an inductance in the range of 20 µH to 100 µH. Speakers with a higher inductance than the 64 µH calculated above will have a 3 dB cut-off frequency below 20 kHz, resulting in a reduced audio bandwidth. Conversely, speakers with an inductance lower than 64 µH will have a higher cut-off frequency.

### **10.3 Recommended external component layout**

Figure 20: Layout of recommended external components and their values

### **10.4** Recommended external components

| Pin<br>Name            | Capacitance         | Tolerance | Voltage | Dielectric | Manufacturer | Part number        |

|------------------------|---------------------|-----------|---------|------------|--------------|--------------------|

| PVDD                   | 4.7 µF              | ±10%      | 35 V    | X5R        | Muruta       | GRM188R6YA475KE15  |

| PVDD<br>OUT_P<br>OUT_N | 100 pF              | ±5%       | 50 V    | COG/NPO    | Muruta       | GRM1555C1H101JD01D |

| VLDO                   | 4.7 µF              | ±10%      | 16 V    | X7R        | Muruta       | GRM155R71C224KA12D |

| IN_P<br>IN_N           | 1 µF                | ±10%      | 10 V    | X5R        | Muruta       | GRM155R61A105KE15D |

| Ferrite<br>bead        | 220 Ω at<br>100 MHz | ±25%      | 2 A     |            | ТDК          | MPZ1608S221A       |

#### **Table 8: Recommended external components**

### **10.5 Capacitor selection**

#### 10.5.1 Input and output capacitors

The DA7202 is designed for operation with small, space-saving ceramic capacitors, but function with most commonly used capacitors as long as attention is paid to the ESR value. The ESR of the output capacitor affects the stability of the LDO control loop. A minimum of 3.0  $\mu$ F capacitance with an ESR of 1  $\Omega$  or less is recommended for the input capacitor on PVDD to ensure the stability of the DA7202.

Transient response to changes in load current is also affected by output capacitance. Using a larger value of output capacitance improves the DA7202's transient response to large changes in load current.

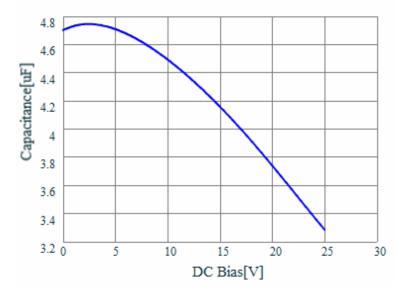

#### **10.5.2** Input and output capacitor properties

Use any good quality ceramic capacitors with the DA7202 that meet the minimum capacitance and maximum ESR requirements. Ceramic capacitors are manufactured with a variety of dielectrics, each

|     | tas |    | - 4 |

|-----|-----|----|-----|

| 112 | tae | no | OT. |

| Da  | Las |    | σι. |

with a different behaviour over temperature and applied voltage. Capacitors must have a dielectric sufficient to ensure that the minimum capacitance over the required temperature range and the DC bias conditions. X5R or X7R dielectrics with a voltage rating of greater than 16 V are recommended for best performance. Y5V and Z5U dielectrics are not recommended.

The voltage stability of a capacitor is strongly influenced by the capacitor size and its voltage rating. In general, a capacitor in a larger package or with a higher voltage rating exhibits better stability. The temperature variation of the X5R dielectric is about 15% over the  $-40^{\circ}$ C to  $+85^{\circ}$ C operating temperature range of the DA7202, and is not a function of package or voltage rating.

Figure 21: Performance plot of the sample capacitor used in the example (below)

Use the following equation to determine the worst case capacitance, accounting for capacitor variation over temperature, component tolerance, and voltage.

$$C_{OUT} = C_{EFF} \times (1 - TEMPCO) \times (1 - TOL)$$

Where:

- CEFF is the effective capacitance at the operating voltage

- **TEMPCO** is the worst-case capacitor temperature coefficient, specified as a value between 0 and 1.

- TOL is the worst-case component tolerance, specified as a value between 0 and 1.

In this example, the worst case temperature coefficient (TEMPCO) over  $-40^{\circ}$ C to  $+85^{\circ}$ C is assumed to be 15% for an X5R dielectric. The tolerance of the capacitor (TOL) is assumed to be 10%, and CEFF is 4.620 µF at 7.2 V, as shown in Figure 21. Substituting these values into the equation yields

#### $C_{OUT} = 4.620 \ \mu F \times (1 - 0.15) \times (1 - 0.1) = 3.53 \ \mu F$

The capacitor chosen in this example therefore meets the minimum capacitance requirement of the LDO over temperature and tolerance at the chosen output voltage.

To guarantee the performance of the DA7202, it is imperative that the effects of DC bias and temperature on the behaviour of the capacitors are evaluated for each application.

| _ |      |      |    |

|---|------|------|----|

| D | atas | shee | et |

23-Dec-2021

10 W Mono Class-D Amplifier for 2S Battery Devices

## **11 Package information**

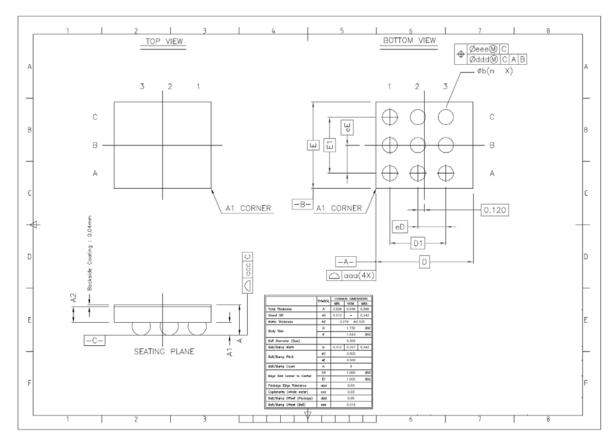

### **11.1 Package outlines**

Figure 22: DA7202 package outline drawing (9-bump WL-CSP 0.5 mm pitch)

## 11.2 Moisture Sensitivity Level (MSL)

The MSL is an indicator for the maximum allowable time period (floor life time) in which a moisture sensitive plastic device, once removed from the dry bag, can be exposed to an environment with a maximum temperature of 30 °C and a maximum relative humidity of 60 % RH. before the solder reflow process.

WLCSP packages are qualified for MSL 1

| MSL Level | Floor Life Time              |

|-----------|------------------------------|

| MSL 4     | 72 hours                     |

| MSL 3     | 168 hours                    |

| MSL 2A    | 4 weeks                      |

| MSL 2     | 1 year                       |

| MSL 1     | Unlimited at 30 °C / 85 % RH |

### 11.3 WLCSP Handling

Manual handling of WLCSP packages should be reduced to the absolute minimum. In cases where it is still necessary, a vacuum pick-up tool should be used. In extreme cases plastic tweezers could be used, but metal tweezers are not acceptable, since contact may easily damage the silicon chip.

Removal will cause damage to the solder balls and therefore a removed sample cannot be reused.

WLCSP is sensitive to visible and infrared light. Precautions should be taken to properly shield the chip in the final product.

#### **11.4 Soldering information**

Refer to the JEDEC standard J-STD-020 for relevant soldering information. This document can be downloaded from http://www.jedec.org.

## **12 Ordering information**

The ordering number consists of the part number followed by a suffix indicating the packing method. For details and availability, please consult Dialog Semiconductor's customer portal or your local sales representative.

#### Table 9: Ordering information

| Part number  | Package                  | Shipment form | Pack quantity |

|--------------|--------------------------|---------------|---------------|

| DA7202-00UH2 | 9-bump CSP Pb free/green | T & R         | 4000          |

# **Revision history**

| Revision                      | Date        | Description                                                                                                                                                                                                                                                                                                                                                                                         |

|-------------------------------|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DA7202-<br>IDS1a-<br>18042013 | Apr 2013    | Initial draft release                                                                                                                                                                                                                                                                                                                                                                               |

| DA7202-<br>IDS2a-<br>18042013 | Jun 2013    | Updated headline power number, page 1<br>Updated parametric<br>Added performance plots<br>Updated ordering info                                                                                                                                                                                                                                                                                     |

| DA7202-<br>IDS2b-<br>110614   | Jun 2014    | <ul> <li>Added typical performance plots (section 2.7)</li> <li>Updated section 2.3.2 (Power Dissipation)</li> <li>Added input impedance and standby current flow figures</li> <li>Modified External Layout diagram to include ferrite beads to reduce EMI</li> <li>Corrected/updated a few performance figures in light of the latest information</li> <li>External components modified</li> </ul> |

| DA7202-<br>IDS3a-<br>20150820 | Aug 2015    | Converted to latest template<br>Updated Absolute maximum ratings table with latest Junction<br>temperature data<br>Updated H-bridge to Class D output stage<br>Corrected Rθ <sub>JA</sub> and θJA to θ <sub>JA</sub><br>Production revision number now assigned                                                                                                                                     |

| 3.1                           | 03-Jul-2018 | Removed Company Confidential status<br>Updated back page                                                                                                                                                                                                                                                                                                                                            |

| 3.2                           | 01-Feb-2019 | THD+N characteristics altered based on lab results from was 90 dB now 94 dB                                                                                                                                                                                                                                                                                                                         |

| 3.3                           | 09-Mar-2021 | Added MSL information                                                                                                                                                                                                                                                                                                                                                                               |

| 3.4                           | 23-Dec-2021 | Rebranded as Renesas.                                                                                                                                                                                                                                                                                                                                                                               |

#### **Status Definitions**

| Revision   | Datasheet Status | Product Status | Definition                                                                                                                                                                                                                                                                                                                                        |

|------------|------------------|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1. <n></n> | Target           | Development    | This datasheet contains the design specifications for product development.<br>Specifications may be changed in any manner without notice.                                                                                                                                                                                                         |

| 2. <n></n> | Preliminary      | Qualification  | This datasheet contains the specifications and preliminary characterization data for products in pre-production. Specifications may be changed at any time without notice in order to improve the design.                                                                                                                                         |

| 3. <n></n> | Final            | Production     | This datasheet contains the final specifications for products in volume production. The specifications may be changed at any time in order to improve the design, manufacturing and supply. Major specification changes are communicated via Customer Product Notifications. Datasheet changes are communicated via www.dialog-semiconductor.com. |

| 4. <n></n> | Obsolete         | Archived       | This datasheet contains the specifications for discontinued products. The information is provided for reference only.                                                                                                                                                                                                                             |

#### **RoHS Compliance**

Dialog Semiconductor's suppliers certify that its products are in compliance with the requirements of Directive 2011/65/EU of the European Parliament on the restriction of the use of certain hazardous substances in electrical and electronic equipment. RoHS certificates from our suppliers are available on request.

#### **Important Notice and Disclaimer**

RENESAS ELECTRONICS CORPORATION AND ITS SUBSIDIARIES ("RENESAS") PROVIDES TECHNICAL SPECIFICATIONS AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS OR IMPLIED, INCLUDING, WITHOUT LIMITATION, ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for developers skilled in the art designing with Renesas products. You are solely responsible for (1) selecting the appropriate products for your application, (2) designing, validating, and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. Renesas grants you permission to use these resources only for development of an application that uses Renesas products. Other reproduction or use of these resources is strictly prohibited. No license is granted to any other Renesas intellectual property or to any third party intellectual property. Renesas disclaims responsibility for, and you will fully indemnify Renesas and its representatives against, any claims, damages, costs, losses, or liabilities arising out of your use of these resources. Renesas' products are provided only subject to Renesas' Terms and Conditions of Sale or other applicable terms agreed to in writing. No use of any Renesas resources expands or otherwise alters any applicable warranties or warranty disclaimers for these products.

© 2021 Renesas Electronics Corporation. All rights reserved.

## **Corporate Headquarters**

TOYOSU FORESIA, 3-2-24 Toyosu

Contact Information

Koto-ku, Tokyo 135-0061, Japan www.renesas.com

https://www.renesas.com/contact/

#### **Datasheet**

CFR0011-120-00 Rev 5

23-Dec-2021

#### IMPORTANT NOTICE AND DISCLAIMER

RENESAS ELECTRONICS CORPORATION AND ITS SUBSIDIARIES ("RENESAS") PROVIDES TECHNICAL SPECIFICATIONS AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS OR IMPLIED, INCLUDING, WITHOUT LIMITATION, ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for developers skilled in the art designing with Renesas products. You are solely responsible for (1) selecting the appropriate products for your application, (2) designing, validating, and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. Renesas grants you permission to use these resources only for development of an application that uses Renesas products. Other reproduction or use of these resources is strictly prohibited. No license is granted to any other Renesas intellectual property or to any third party intellectual property. Renesas disclaims responsibility for, and you will fully indemnify Renesas and its representatives against, any claims, damages, costs, losses, or liabilities arising out of your use of these resources. Renesas' products are provided only subject to Renesas' Terms and Conditions of Sale or other applicable terms agreed to in writing. No use of any Renesas resources expands or otherwise alters any applicable warranties or warranty disclaimers for these products.

(Rev.1.0 Mar 2020)

#### **Corporate Headquarters**

TOYOSU FORESIA, 3-2-24 Toyosu, Koto-ku, Tokyo 135-0061, Japan www.renesas.com

#### **Trademarks**

Renesas and the Renesas logo are trademarks of Renesas Electronics Corporation. All trademarks and registered trademarks are the property of their respective owners.

#### **Contact Information**

For further information on a product, technology, the most up-to-date version of a document, or your nearest sales office, please visit: www.renesas.com/contact/