# **DSP1627 Digital Signal Processor**

### 1 Features

- Optimized for digital cellular applications with a bit manipulation unit for higher coding efficiency.

- On-chip, programmable, PLL clock synthesizer.

- 14 ns and 11 ns instruction cycle times at 5 V, 10 ns instruction cycle time at 3.0 V, and 20 ns and 12.5 ns instruction cycle times at 2.7 V, respectively.

- Mask-programmable memory map option: The DSP1627x36 features 36 Kwords on-chip ROM. The DSP1627x32 features 32 Kwords on-chip ROM and access to 16 Kwords external ROM in the same map. Both feature 6 Kwords on-chip, dual-port RAM and a secure option for on-chip ROM.

- Low power consumption:

- <5.5 mW/MIPS typical at 5 V.</p>

- <1.5 mW/MIPS typical at 2.7 V.

- Flexible power management modes:

- Standard sleep: 0.5 mW/MIPS at 5 V.

0.12 mW/MIPS at 2.7 V.

- Sleep with slow internal clock: 1.4 mW at 5 V.

0.4 mW at 2.7 V.

- Hardware STOP (pin halts DSP): <20 μA.</li>

- Mask-programmable clock options: crystal oscillator, small signal, and CMOS.

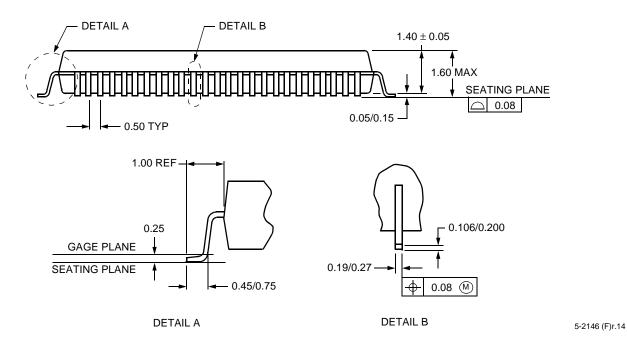

- Low-profile TQFP package (1.5 mm) available.

- Sequenced accesses to X and Y external memory.

- Object code compatible with the DSP1617.

- Single-cycle squaring.

- 16 x 16-bit multiplication and 36-bit accumulation in one instruction cycle.

- Instruction cache for high-speed, program-efficient, zerooverhead looping.

- Dual 25 Mbits/s serial I/O ports with multiprocessor capability—16-bit data channel, 8-bit protocol channel.

- 8-bit parallel host interface:

- Supports 8- or 16-bit transfers.

- Motorola\* or Intel† compatible.

- 8-bit control I/O interface.

- 256 memory-mapped I/O ports.

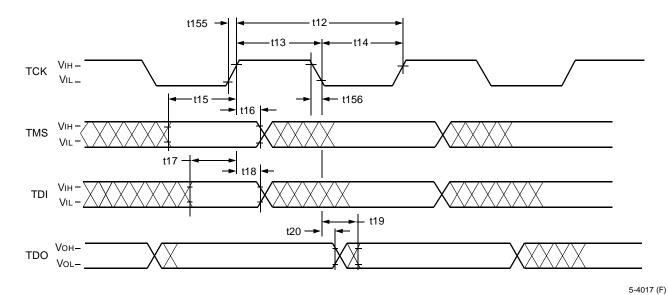

- IEEE<sup>‡</sup> P1149.1 test port (JTAG boundary scan).

- \* Motorola is a registered trademark of Motorola, Inc.

- † Intel is a registered trademark of Intel Corp.

- ‡ IEEE is a registered trademark of The Institute of Electrical and Electronics Engineers, Inc.

- Full-speed in-circuit emulation hardware development system on-chip.

- Supported by DSP1627 software and hardware development tools.

# 2 Description

The DSP1627 is Lucent Technologies Microelectronics Group first digital signal processor offering 100 MIPS operation at 3.0 V and 80 MIPS operation at 2.7 V with a reduction in power consumption. Designed specifically for applications requiring low power dissipation in digital cellular systems, the DSP1627 is a signal-coding device that can be programmed to perform a wide variety of fixed-point signal processing functions. The device is based on the DSP1600 core with a bit manipulation unit for enhanced signal coding efficiency. The DSP1627 includes a mix of peripherals specifically intended to support processing-intensive but cost-sensitive applications in the area of digital wireless communications.

The DSP1627x36 contains 36 Kwords of internal ROM (IROM), but it doesn't support the use of IROM and external ROM (EROM) in the same memory map. The DSP1627x32 supports the use of 32 Kwords of IROM with 16 Kwords of EROM in the same map. Both devices contain 6 Kwords of dual-port RAM (DPRAM), which allows simultaneous access to two RAM locations in a single instruction cycle.

The DSP1627 is object code compatible with the DSP1617, while providing more memory and architectural enhancements including an on-chip clock synthesizer and an 8-bit parallel host interface for hardware flexibility.

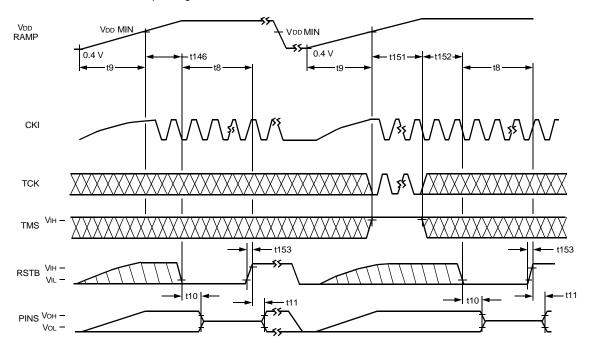

The DSP1627 supports 2.7 V, 3.0 V, and 5 V operation and flexible power management modes required for portable cellular terminals. Several control mechanisms achieve low-power operation, including a STOP pin for placing the DSP into a fully static, halted state and a programmable power control register used to power down unused on-chip I/O units. These power management modes allow for trade-offs between power reduction and wake-up latency requirements. During system standby, power consumption is reduced to less than 20  $\mu A$ .

The on-chip clock synthesizer can be driven by an external clock whose frequency is a fraction of the instruction rate.

The device is packaged in a 100-pin BQFP or a 100-pin TQFP and is available with 14 ns and 11 ns instruction cycle times at 5 V, 10 ns instruction cycle times at 3.0 V, and 20 ns and 12.5 ns instruction cycle times at 2.7 V, respectively.

# **Table of Contents**

| Co | nten   | ts Pa                                  | age | Co | ontents Pag                                    | ge |

|----|--------|----------------------------------------|-----|----|------------------------------------------------|----|

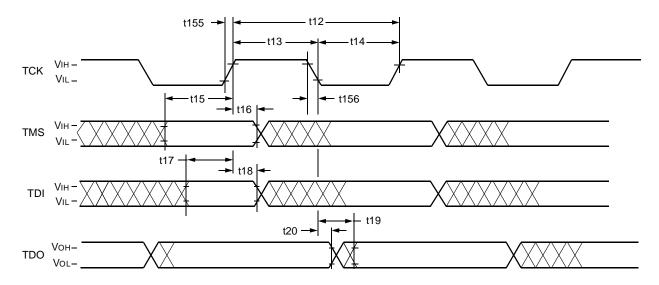

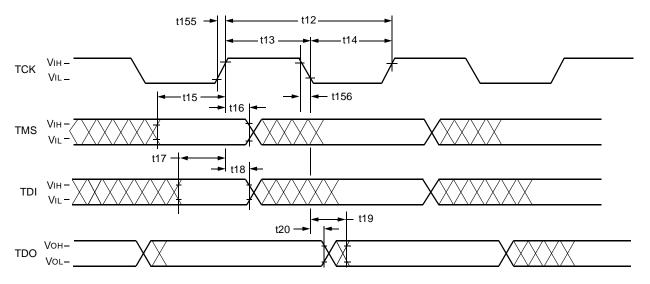

| 1  | Featu  | ıres                                   | 1   |    | 10.4 JTAG I/O Specifications                   | 79 |

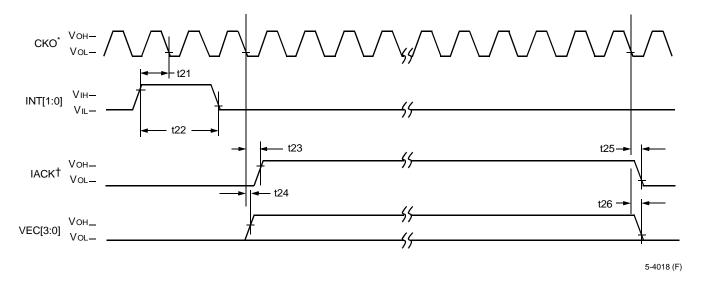

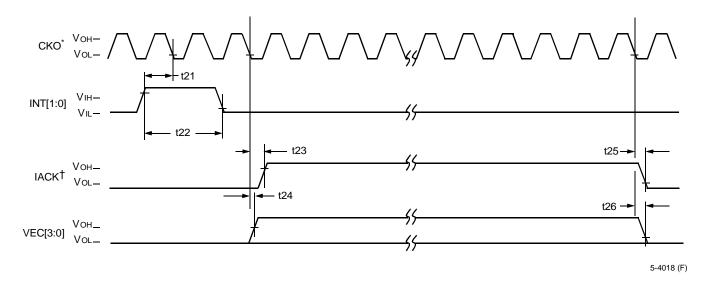

| 2  | Desci  | ription                                | 1   |    | 10.5 Interrupt                                 |    |

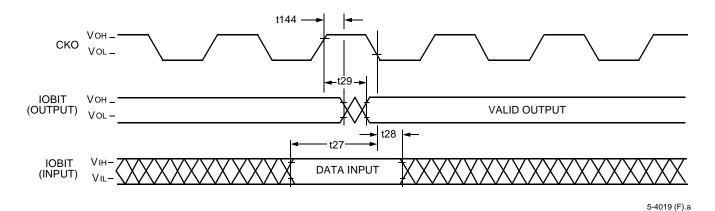

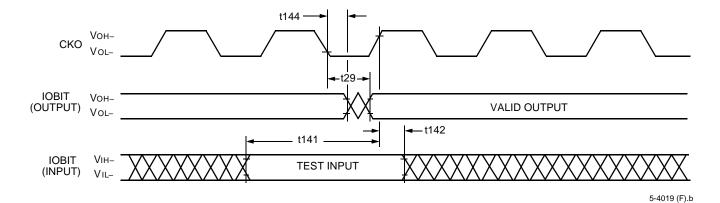

| 3  | Pin In | formation                              | 3   |    | 10.6 Bit Input/Output (BIO)                    | 81 |

| 4  | Hard   | ware Architecture                      | . 7 |    | 10.7 External Memory Interface                 |    |

|    | 4.1    | DSP1627 Architectural Overview         | 7   |    | 10.8 PHIF Specifications                       |    |

|    | 4.2    | DSP1600 Core Architectural Overview    | 10  |    | 10.9 Serial I/O Specifications                 |    |

|    | 4.3    | Interrupts and Trap                    | 11  |    | 10.10 Multiprocessor Communication             |    |

|    | 4.4    | Memory Maps and Wait-States            |     | 11 |                                                |    |

|    | 4.5    | External Memory Interface (EMI)        | 18  |    | 11.1 DSP Clock Generation                      | 99 |

|    | 4.6    | Bit Manipulation Unit (BMU)            |     |    | 11.2 Reset Circuit 1                           | 00 |

|    | 4.7    | Serial I/O Units (SIOs)                | 19  |    | 11.3 Reset Synchronization 1                   | 01 |

|    | 4.8    | Parallel Host Interface (PHIF)         |     |    | 11.4 JTAG I/O Specifications 1                 | 02 |

|    | 4.9    | Bit Input/Output Unit (BIO)            |     |    | 11.5 Interrupt 1                               |    |

|    | 4.10   | Timer                                  |     |    | 11.6 Bit Input/Output (BIO) 1                  |    |

|    | 4.11   | JTAG Test Port                         | 24  |    | 11.7 External Memory Interface 1               |    |

|    | 4.12   | Clock Synthesis                        | 26  |    | 11.8 PHIF Specifications 1                     | 09 |

|    | 4.13   | Power Management                       |     |    | 11.9 Serial I/O Specifications 1               |    |

| 5  | Softw  | rare Architecture                      |     |    | 11.10 Multiprocessor Communication 1           | 20 |

|    | 5.1    | Instruction Set                        | 36  | 12 | 2 Timing Characteristics for 2.7 V Operation 1 | 21 |

|    | 5.2    | Register Settings                      | 45  |    | 12.1 DSP Clock Generation 1                    | 22 |

|    | 5.3    | Instruction Set Formats                |     |    | 12.2 Reset Circuit 1                           | 23 |

| 6  | Signa  | al Descriptions                        | 61  |    | 12.3 Reset Synchronization 1                   | 24 |

|    | 6.1    | System Interface                       |     |    | 12.4 JTAG I/O Specifications 1                 |    |

|    | 6.2    | External Memory Interface              |     |    | 12.5 Interrupt 1                               |    |

|    | 6.3    | Serial Interface #1                    | 64  |    | 12.6 Bit Input/Output (BIO) 1                  | 27 |

|    | 6.4    | Parallel Host Interface or Serial      |     |    | 12.7 External Memory Interface 1               | 28 |

|    |        | Interface #2 and Control I/O Interface | 65  |    | 12.8 PHIF Specifications 1                     | 32 |

|    | 6.5    | Control I/O Interface                  | 65  |    | 12.9 Serial I/O Specifications 1               | 38 |

|    | 6.6    | JTAG Test Interface                    | 66  |    | 12.10 Multiprocessor Communication 1           | 43 |

| 7  | Mask   | -Programmable Options                  | 67  | 13 | 3 Crystal Electrical Characteristics and       |    |

|    | 7.1    | Input Clock Options                    | 67  |    | Requirements1                                  | 44 |

|    | 7.2    | Memory Map Options                     | 67  |    | 13.1 External Components for the Crystal       |    |

|    | 7.3    | ROM Security Options                   | 67  |    | Oscillator1                                    | 44 |

| 8  | Devic  | e Characteristics                      | 68  |    | 13.2 Power Dissipation 1                       | 44 |

|    | 8.1    | Absolute Maximum Ratings               | 68  |    | 13.3 LC Network Design for Third               |    |

|    | 8.2    | Handling Precautions                   | 68  |    | Overtone Crystal Circuits 1                    | 47 |

|    | 8.3    | Recommended Operating Conditions       | 68  |    | 13.4 Frequency Accuracy Considerations 1       | 49 |

|    | 8.4    | Package Thermal Considerations         | 69  | 14 | 1 Outline Diagrams 1                           | 52 |

| 9  | Electi | rical Characteristics and Requirements | 70  |    | 14.1 100-Pin BQFP (Bumpered Quad               |    |

|    | 9.1    | Power Dissipation                      | 73  |    | Flat Pack) 1                                   | 52 |

| 10 | Timin  | g Characteristics for 5 V Operation    | 75  |    | 14.2 100-Pin TQFP (Thin Quad Flat Pack) 1      | 53 |

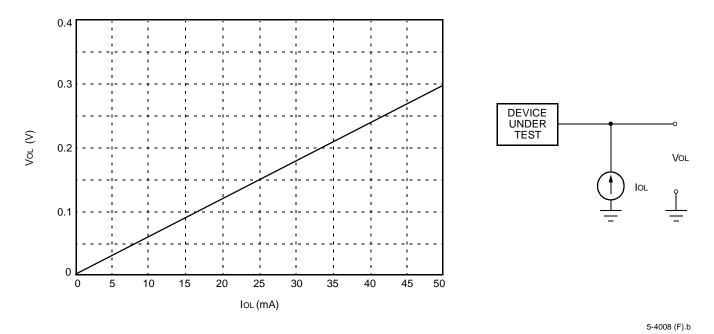

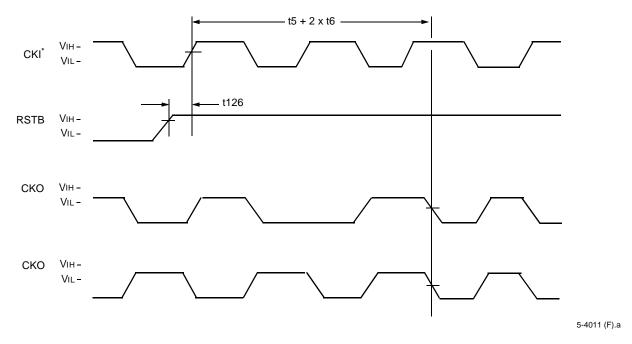

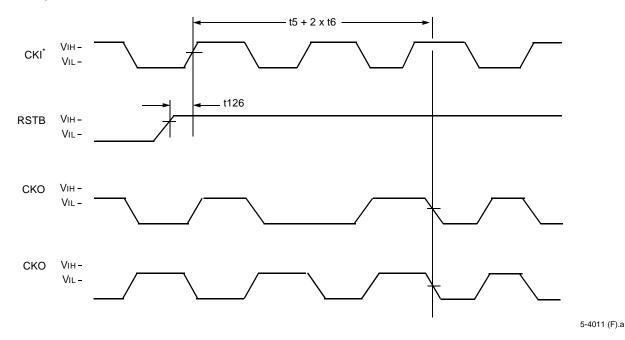

|    | 10.1   | DSP Clock Generation                   | 76  |    |                                                |    |

|    | 10.2   | Reset Circuit                          | 77  |    |                                                |    |

|    | 10.3   | Reset Synchronization                  | 78  |    |                                                |    |

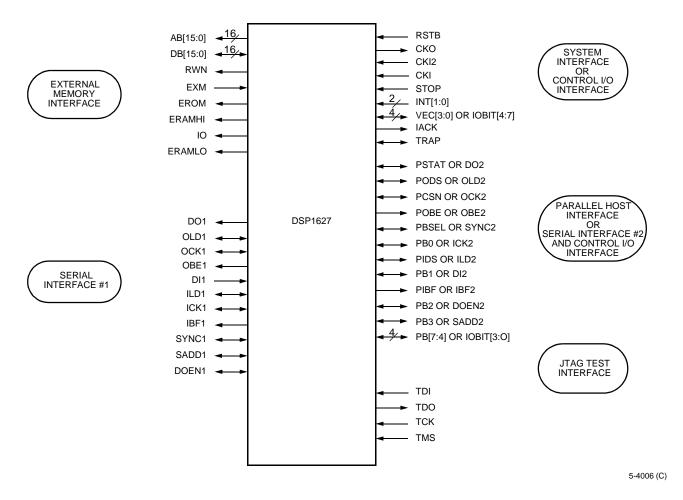

### 3 Pin Information

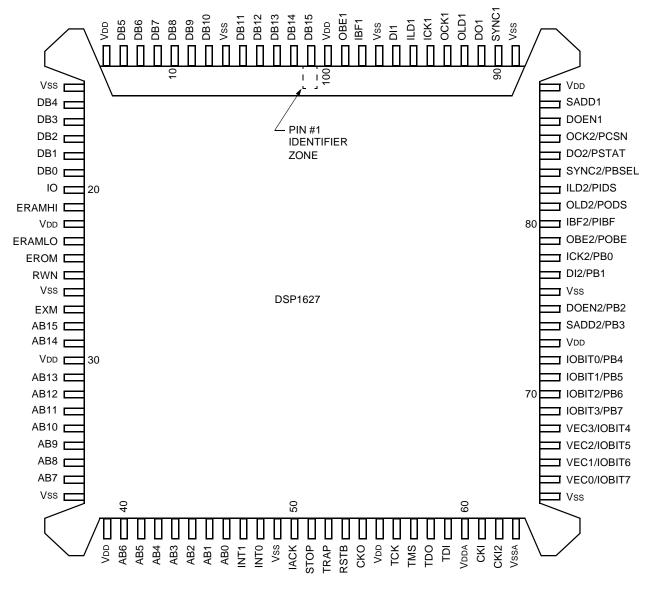

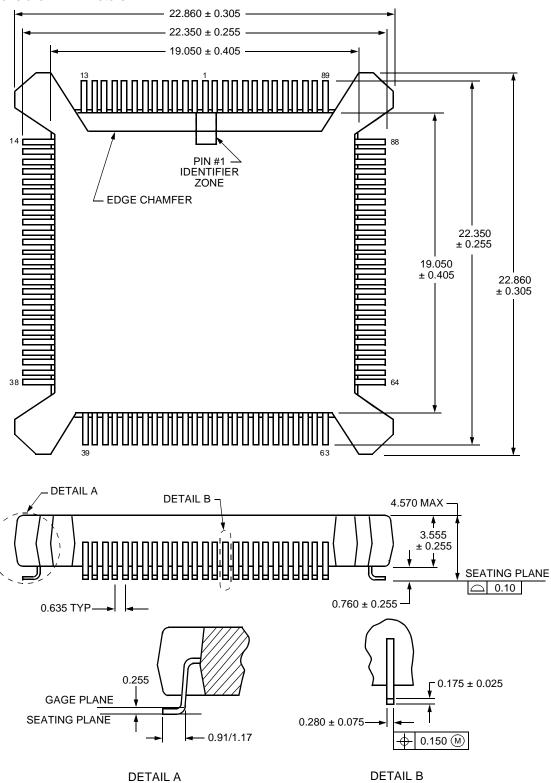

Figure 1. DSP1627 BQFP Pin Diagram

5-4218 (F).b

# 3 Pin Information (continued)

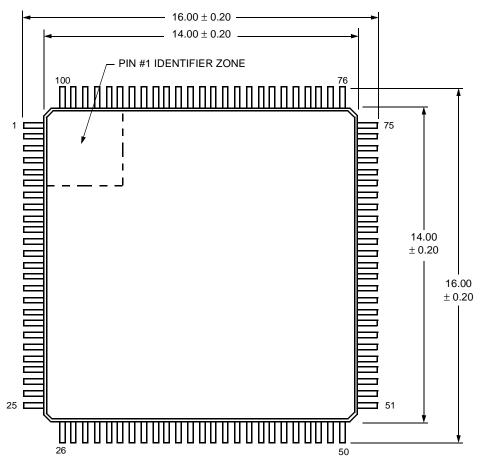

Figure 2. DSP1627 TQFP Pin Diagram

# 3 Pin Information (continued)

Functional descriptions of pins 1—100 are found in Section 6, Signal Descriptions. The functionality of pins 61 and 62 (TQFP pins 48 and 49) are mask-programmable (see Section 7, Mask-Programmable Options). Input levels on all I and I/O type pins are designed to remain at full CMOS levels when not driven by the DSP.

**Table 1. Pin Descriptions**

| BQFP Pin    | TQFP Pin    | Symbol      | Туре           |                                                       |            | Name/Function                 |       |  |  |

|-------------|-------------|-------------|----------------|-------------------------------------------------------|------------|-------------------------------|-------|--|--|

| 1, 2, 3, 4, | 88, 89, 90, | DB[15:0]    | I/O*           | External Mei                                          | mory Data  | Bus DB[15:0].                 |       |  |  |

| 5, 7, 8, 9, | 91, 92, 94, |             |                |                                                       |            |                               |       |  |  |

| 10, 11, 12, | 95, 96, 97, |             |                |                                                       |            |                               |       |  |  |

| 15, 16, 17, | 98, 99, 2,  |             |                |                                                       |            |                               |       |  |  |

| 18, 19      | 3, 4, 5, 6  |             |                |                                                       |            |                               |       |  |  |

| 20          | 7           | Ю           | O <sup>†</sup> |                                                       |            | to 0x40FF I/O Enable.         |       |  |  |

| 21          | 8           | ERAMHI      | O <sup>†</sup> |                                                       |            | to 0xFFFF External RAM Enable |       |  |  |

| 23          | 10          | ERAMLO      | O <sup>†</sup> |                                                       |            | to 0x7FFF External RAM Enable | ).    |  |  |

| 24          | 11          | EROM        | O <sup>†</sup> |                                                       |            | rnal ROM Enable.              |       |  |  |

| 25          | 12          | RWN         | O <sup>†</sup> | Read/Write I                                          | Not.       |                               |       |  |  |

| 27          | 14          | EXM         |                | External RO                                           | M Enable.  |                               |       |  |  |

| 28, 29, 31, | 15, 16, 18, | AB[15:0]    | O*             | External Mei                                          | mory Addre | ess Bus 15—0.                 |       |  |  |

| 32, 33, 34, | 19, 20, 21, |             |                |                                                       |            |                               |       |  |  |

| 35, 36, 37, | 22, 23, 24, |             |                |                                                       |            |                               |       |  |  |

| 40, 41, 42, | 27, 28, 29, |             |                |                                                       |            |                               |       |  |  |

| 43, 44, 45, | 30, 31, 32, |             |                |                                                       |            |                               |       |  |  |

| 46          | 33          |             |                |                                                       |            |                               |       |  |  |

| 47          | 34          | INT1        |                | Vectored Inte                                         | •          |                               |       |  |  |

| 48          | 35          | INT0        | I              | Vectored Inte                                         | •          |                               |       |  |  |

| 50          | 37          | IACK        | 0*             | Interrupt Ack                                         |            | •                             |       |  |  |

| 51          | 38          | STOP        | I              | STOP Input                                            |            |                               |       |  |  |

| 52          | 39          | TRAP        | I/O*           |                                                       | e Program  | Trap/Breakpoint Indication.   |       |  |  |

| 53          | 40          | RSTB        | I              | Reset Bar.                                            |            |                               |       |  |  |

| 54          | 41          | CKO         | O <sup>†</sup> | Processor C                                           |            | ıt.                           |       |  |  |

| 56          | 43          | TCK         | ı              | JTAG Text C                                           |            |                               |       |  |  |

| 57          | 44          | TMS         | <b> </b> ‡     | JTAG Test N                                           |            |                               |       |  |  |

| 58          | 45          | TDO         | Ő              | JTAG Test D                                           | •          |                               |       |  |  |

| 59          | 46          | TDI         | I‡             | JTAG Test D                                           | -          |                               |       |  |  |

|             |             |             |                |                                                       |            | ammable Input Clock Option    |       |  |  |

|             |             |             |                | CMOS                                                  | Small      | Crystal                       | 01/02 |  |  |

|             | T           | <u> </u>    |                |                                                       | Signal     | Oscillator                    | CMOS  |  |  |

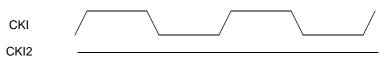

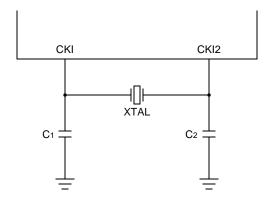

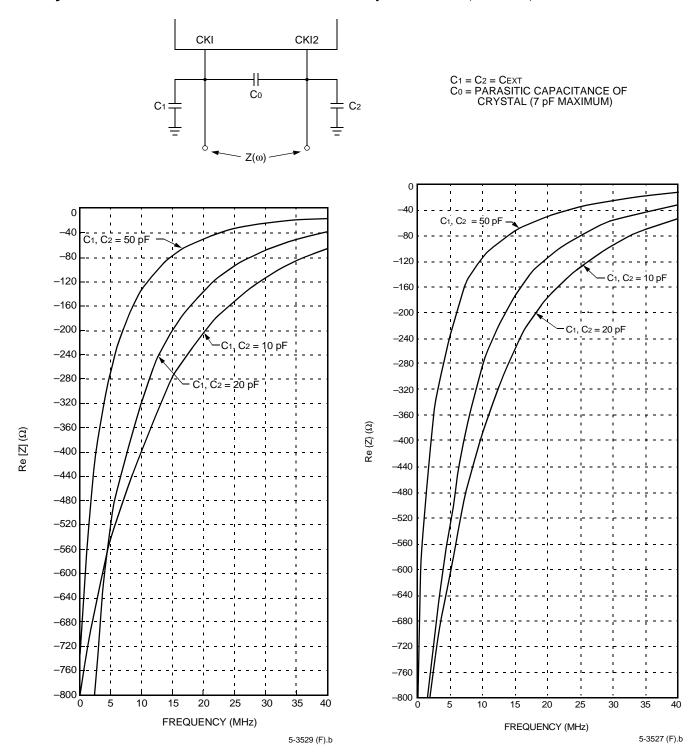

| 61          | 48          | CKI**       | I              | CKI                                                   | VAC        | XLO, 10 pF capacitor to Vss   | CKI   |  |  |

| 62          | 49          | CKI2**      |                | VSSA VCM XHI, 10 pF capacitor to Vss Open             |            |                               |       |  |  |

| 65          | 52          | VEC0/IOBIT7 | I/O*           | ' ' ' ' ' ' ' ' ' ' ' ' ' ' ' ' ' ' '                 |            |                               |       |  |  |

| 66          | 53          | VEC1/IOBIT6 | I/O*           | Vectored Interrupt Indication 1/Status/Control Bit 6. |            |                               |       |  |  |

| 67          | 54          | VEC2/IOBIT5 | I/O*           | Vectored Interrupt Indication 2/Status/Control Bit 5. |            |                               |       |  |  |

| 68          | 55          | VEC3/IOBIT4 | I/O*           | Vectored Interrupt Indication 3/Status/Control Bit 4. |            |                               |       |  |  |

<sup>3</sup>-states when RSTB = 0, or by JTAG control.

<sup>† 3-</sup>states when RSTB = 0 and INT0 = 1. Output = 1 when RSTB = 0 and INT0 = 0, except CKO which is free-running.

<sup>‡</sup> Pull-up devices on input.

<sup>§ 3-</sup>states by JTAG control.

\*\* See Section 7. Mask-Proc See Section 7, Mask-Programmable Options.

<sup>††</sup> For SIO multiprocessor applications, add 5 k $\Omega$  external pull-up resistors to SADD1 and/or SADD2 for proper initialization.

# 3 Pin Information (continued)

Functional descriptions of pins 1—100 are found in Section 6, Signal Descriptions.

Table 1. Pin Descriptions (continued)

| BQFP Pin               | TQFP Pin     | Symbol                  | Туре | Name/Function                                         |

|------------------------|--------------|-------------------------|------|-------------------------------------------------------|

| 69                     | 56           | IOBIT3/PB7              | I/O* | Status/Control Bit 3/PHIF Data Bus Bit 7.             |

| 70                     | 57           | IOBIT2/PB6              | I/O* | Status/Control Bit 2/PHIF Data Bus Bit 6.             |

| 71                     | 58           | IOBIT1/PB5              | I/O* | Status/Control Bit 1/PHIF Data Bus Bit 5.             |

| 72                     | 59           | IOBIT0/PB4              | I/O* | Status/Control Bit 0/PHIF Data Bus Bit 4.             |

| 74                     | 61           | SADD2/PB3 <sup>††</sup> | I/O* | SIO2 Multiprocessor Address/PHIF Data Bus Bit 3.      |

| 75                     | 62           | DOEN2/PB2               | I/O* | SIO2 Data Output Enable/PHIF Data Bus Bit 2.          |

| 77                     | 64           | DI2/PB1                 | I/O* | SIO2 Data Input/PHIF Data Bus Bit 1.                  |

| 78                     | 65           | ICK2/PB0                | I/O* | SIO2 Input Clock/PHIF Data Bus Bit 0.                 |

| 79                     | 66           | OBE2/POBE               | O*   | SIO2 Output Buffer Empty/PHIF Output Buffer Empty.    |

| 80                     | 67           | IBF2/PIBF               | O*   | SIO2 Input Buffer Full/PHIF Input Buffer Full.        |

| 81                     | 68           | OLD2/PODS               | I/O* | SIO2 Output Load/PHIF Output Data Strobe.             |

| 82                     | 69           | ILD2/PIDS               | I/O* | SIO2 Input Load/PHIF Input Data Strobe.               |

| 83                     | 70           | SYNC2/PBSEL             | I/O* | SIO2 Multiprocessor Synchronization/PHIF Byte Select. |

| 84                     | 71           | DO2/PSTAT               | I/O* | SIO2 Data Output/PHIF Status Register Select.         |

| 85                     | 72           | OCK2/PCSN               | I/O* | SIO2 Output Clock/PHIF Chip Select Not.               |

| 86                     | 73           | DOEN1                   | I/O* | SIO1 Data Output Enable.                              |

| 87                     | 74           | SADD1 <sup>††</sup>     | I/O* | SIO1 Multiprocessor Address.                          |

| 90                     | 77           | SYNC1                   | I/O* | SIO1 Multiprocessor Synchronization.                  |

| 91                     | 78           | DO1                     | O*   | SIO1 Data Output.                                     |

| 92                     | 79           | OLD1                    | I/O* | SIO1 Output Load.                                     |

| 93                     | 80           | OCK1                    | I/O* | SIO1 Output Clock.                                    |

| 94                     | 81           | ICK1                    | I/O* | SIO1 Input Clock.                                     |

| 95                     | 82           | ILD1                    | I/O* | SIO1 Input Load.                                      |

| 96                     | 83           | DI1                     | I    | SIO1 Data Input.                                      |

| 98                     | 85           | IBF1                    | O*   | SIO1 Input Buffer Full.                               |

| 99                     | 86           | OBE1                    | O*   | SIO1 Output Buffer Empty.                             |

| 6, 15, 26,             | 93, 1, 13,   | Vss                     | Р    | Ground.                                               |

| 38, 49, 64,            | 25, 36, 51,  |                         |      |                                                       |

| 76, 89, 97             | 63, 76, 84   |                         |      |                                                       |

| 14, 22, 30,            | 100, 9, 17,  | VDD                     | Р    | Power Supply.                                         |

| 39, 55, 73,<br>88, 100 | 26, 42, 60,  |                         |      |                                                       |

| 60                     | 75, 87<br>47 | VDDA                    | Р    | Analog Power Supply.                                  |

| 63                     | 50           | VDDA                    | P    | Analog Fower Supply.  Analog Ground.                  |

| 03                     | 50           | VSSA                    | ۲    | Analog Ground.                                        |

<sup>3</sup>-states when RSTB = 0, or by JTAG control.

$<sup>\</sup>dagger$  3-states when RSTB = 0 and INT0 = 1. Output = 1 when RSTB = 0 and INT0 = 0.

<sup>§</sup> Pull-up devices on input.

<sup>3-</sup>states by JTAG control.\*\* See Section 7, Mask-Programmable Options.

<sup>††</sup> For SIO multiprocessor applications, add 5 k $\Omega$  external pull-up resistors to SADD1 and/or SADD2 for proper initialization.

### 4 Hardware Architecture

The DSP1627 device is a 16-bit, fixed-point programmable digital signal processor (DSP). The DSP1627 consists of a DSP1600 core together with on-chip memory and peripherals. Added architectural features give the DSP1627 high program efficiency for signal coding applications.

#### 4.1 DSP1627 Architectural Overview

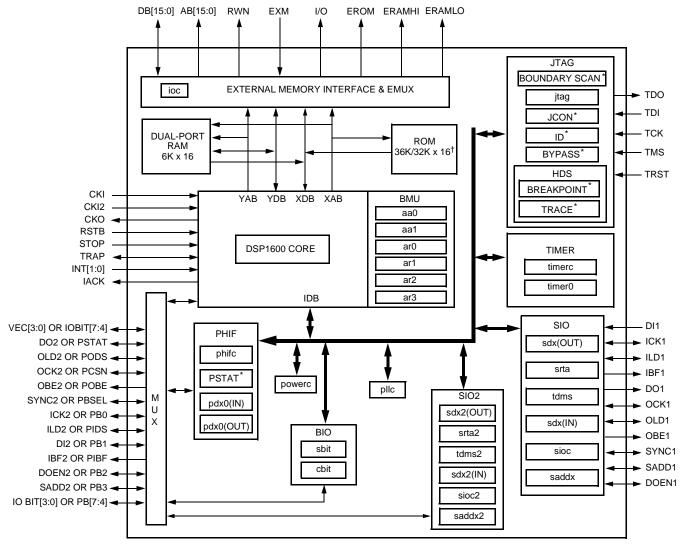

Figure 3 shows a block diagram of the DSP1627. The following modules make up the DSP1627.

#### DSP1600 Core

The DSP1600 core is the heart of the DSP1627 chip. The core contains data and address arithmetic units, and control for on-chip memory and peripherals. The core provides support for external memory wait-states and on-chip, dual-port RAM and features vectored interrupts and a trap mechanism.

#### **Dual-Port RAM (DPRAM)**

This module contains six banks of zero wait-state memory. Each bank consists of 1K 16-bit words and has separate address and data ports to the instruction/coefficient and data memory spaces. A program can reference memory from either space. The DSP1600 core automatically performs the required multiplexing. If references to both ports of a single bank are made simultaneously, the DSP1600 core automatically inserts a wait-state and performs the data port access first, followed by the instruction/coefficient port access.

A program can be downloaded from slow, off-chip memory into DPRAM, and then executed without wait-states. DPRAM is also useful for improving convolution performance in cases where the coefficients are adaptive. Since DPRAM can be downloaded through the JTAG port, full-speed remote in-circuit emulation is possible. DPRAM can also be used for downloading self-test code via the JTAG port.

#### Read-Only Memory (ROM)

The DSP1627x36 contains 36K 16-bit words of zero wait-state mask-programmable ROM for program and fixed coefficients. Similarly, the DSP1627x32 has 32K 16-bit words of ROM and access to 16 Kwords of external ROM.

#### **External Memory Multiplexer (EMUX)**

The EMUX is used to connect the DSP1627 to external memory and I/O devices. It supports read/write operations from/to instruction/coefficient memory (X memory space) and data memory (Y memory space). The DSP1600 core automatically controls the EMUX. Instructucent Technologies Inc.

tions can transparently reference external memory from either set of internal buses. A sequencer allows a single instruction to access both the X and the Y external memory spaces.

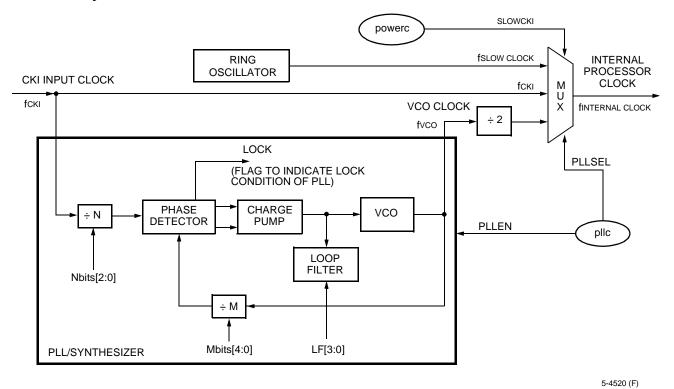

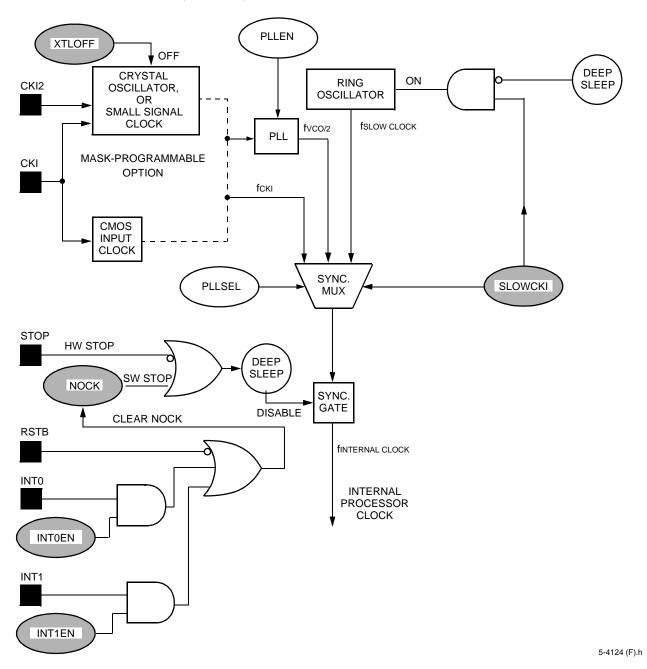

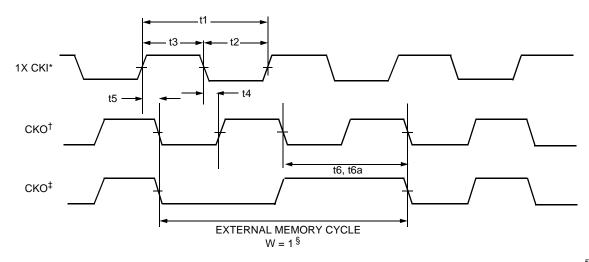

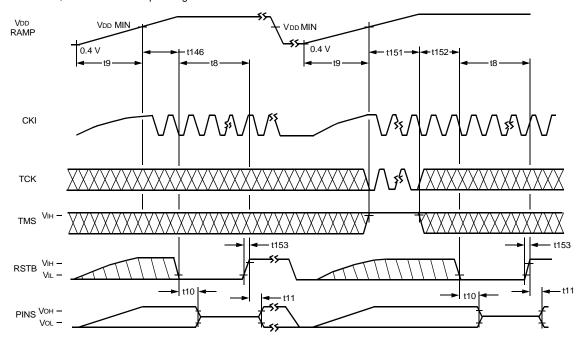

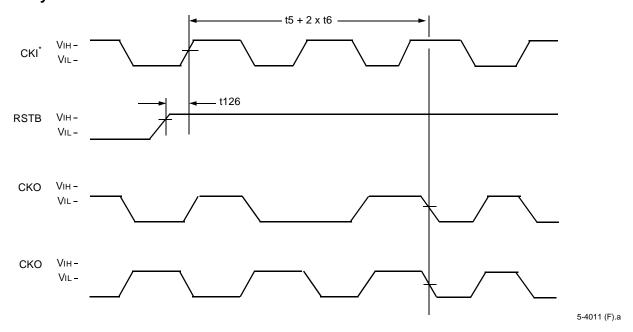

### **Clock Synthesis**

The DSP powers up with a 1X input clock (CKI/CKI2) as the source for the processor clock. An on-chip clock synthesizer (PLL) can also be used to generate the system clock for the DSP, which will run at a frequency multiple of the input clock. The clock synthesizer is deselected and powered down on reset. For low-power operation, an internally generated slow clock can be used to drive the DSP. If both the clock synthesizer and the internally generated slow clock are selected, the slow clock will drive the DSP; however, the synthesizer will continue to run.

The clock synthesizer and other programmable clock sources are discussed in Section 4.12. The use of these programmable clock sources for power management is discussed in Section 4.13.

### Bit Manipulation Unit (BMU)

The BMU extends the DSP1600 core instruction set to provide more efficient bit operations on accumulators. The BMU contains logic for barrel shifting, normalization, and bit field insertion/extraction. The unit also contains a set of 36-bit alternate accumulators. The data in the alternate accumulators can be shuffled with the data in the main accumulators. Flags returned by the BMU mesh seamlessly with the DSP1600 conditional instructions.

#### Bit Input/Output (BIO)

The BIO provides convenient and efficient monitoring and control of eight individually configurable pins. When configured as outputs, the pins can be individually set, cleared, or toggled. When configured as inputs, individual pins or combinations of pins can be tested for patterns. Flags returned by the BIO mesh seamlessly with conditional instructions.

#### Serial Input/Output Units (SIO and SIO2)

SIO and SIO2 offer asynchronous, full-duplex, double-buffered channels that operate at up to 25 Mbits/s (for 20 ns instruction cycle in a nonmultiprocessor configuration), and easily interface with other Lucent Technologies fixed-point DSPs in a multiple-processor environment. Commercially available codecs and time-division multiplex (TDM) channels can be interfaced to the serial I/O ports with few, if any, additional components. SIO2 is identical to SIO.

An 8-bit serial protocol channel may be transmitted in addition to the address of the called processor in multiprocessor mode. This feature is useful for transmitting high-level framing information or for error detection and correction. SIO2 and BIO are pin-multiplexed with the PHIF.

5-4142 (F).f

- \* These registers are accessible through the pins only.

- $\dagger$  36K x 16 for the DSP1627x36; 32K x 16 for the DSP1627x32.

Figure 3. DSP1627 Block Diagram

Table 2. DSP1627 Block Diagram Legend

| Symbol     | Name                                                                 |

|------------|----------------------------------------------------------------------|

| aa<0—1>    | Alternate Accumulators.                                              |

| ar<0—3>    | Auxiliary BMU Registers.                                             |

| BIO        | Bit Input/Output Unit.                                               |

| BMU        | Bit Manipulation Unit.                                               |

| BREAKPOINT | Four Instruction Breakpoint Registers.                               |

| BYPASS     | JTAG Bypass Register.                                                |

| cbit       | Control Register for BIO.                                            |

| EMUX       | External Memory Multiplexer.                                         |

| HDS        | Hardware Development System.                                         |

| ID         | JTAG Device Identification Register.                                 |

| IDB        | Internal Data Bus.                                                   |

| ioc        | I/O Configuration Register.                                          |

| JCON       | JTAG Configuration Registers.                                        |

| jtag       | 16-bit Serial/Parallel Register.                                     |

| pdx0(in)   | Parallel Data Transmit Input Register 0.                             |

| pdx0(out)  | Parallel Data Transmit Output Register 0.                            |

| PHIF       | Parallel Host Interface.                                             |

| phifc      | Parallel Host Interface Control Register.                            |

| pllc       | Phase-Locked Loop Control Register.                                  |

| powerc     | Power Control Register.                                              |

| PSTAT      | Parallel Host Interface Status Register.                             |

| ROM        | Internal ROM (36 Kwords for DSP1627x36, 32 Kwords for DSP1627x32).   |

| saddx      | Multiprocessor Protocol Register.                                    |

| saddx2     | Multiprocessor Protocol Register for SIO2.                           |

| sbit       | Status Register for BIO.                                             |

| sdx(in)    | Serial Data Transmit Input Register.                                 |

| sdx2(in)   | Serial Data Transmit Input Register for SIO2.                        |

| sdx(out)   | Serial Data Transmit Output Register.                                |

| sdx2(out)  | Serial Data Transmit Output Register for SIO2.                       |

| SIO        | Serial Input/Output Unit.                                            |

| SIO2       | Serial Input/Output Unit #2.                                         |

| sioc       | Serial I/O Control Register.                                         |

| sioc2      | Serial I/O Control Register for SIO2.                                |

| srta       | Serial Receive/Transmit Address Register.                            |

| srta2      | Serial Receive/Transmit Address Register for SIO2.                   |

| tdms       | Serial I/O Time-division Multiplex Signal Control Register.          |

| tdms2      | Serial I/O Time-division Multiplex Signal Control Register for SIO2. |

| TIMER      | Programmable Timer.                                                  |

| timer0     | Timer Running Count Register.                                        |

| timerc     | Timer Control Register.                                              |

| TRACE      | Program Discontinuity Trace Buffer.                                  |

| XAB        | Program Memory Address Bus.                                          |

| XDB        | Program Memory Data Bus.                                             |

| YAB        | Data Memory Address Bus.                                             |

| YDB        | Data Memory Data Bus.                                                |

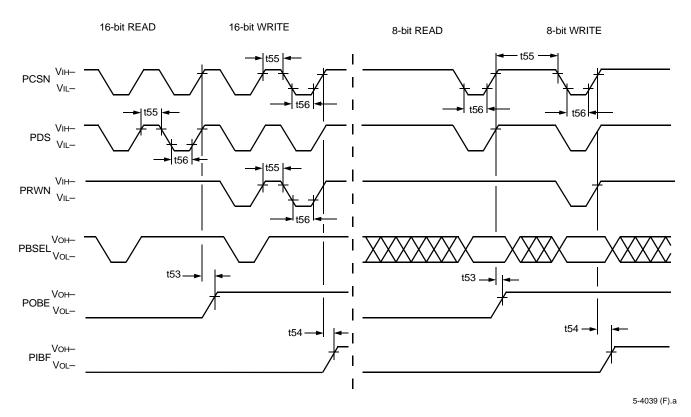

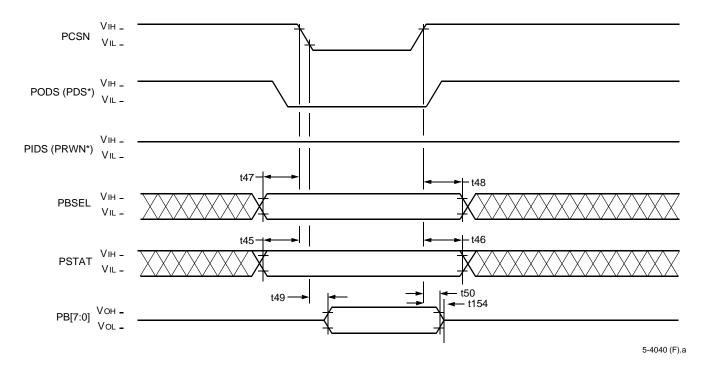

#### Parallel Host Interface (PHIF)

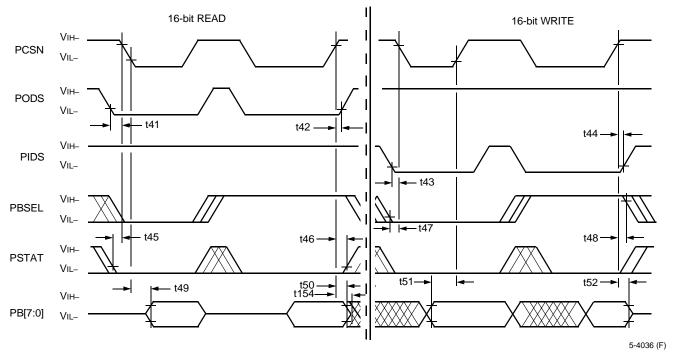

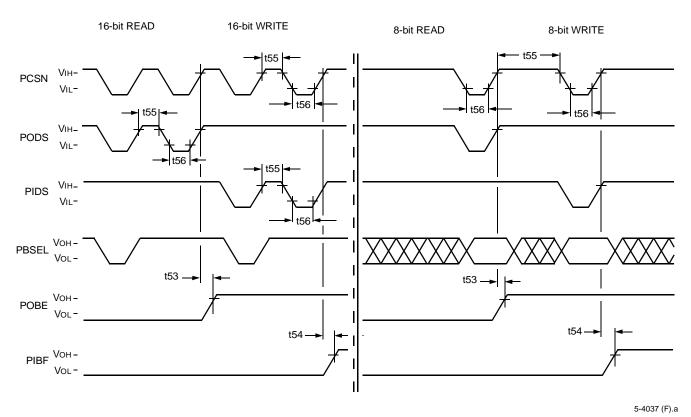

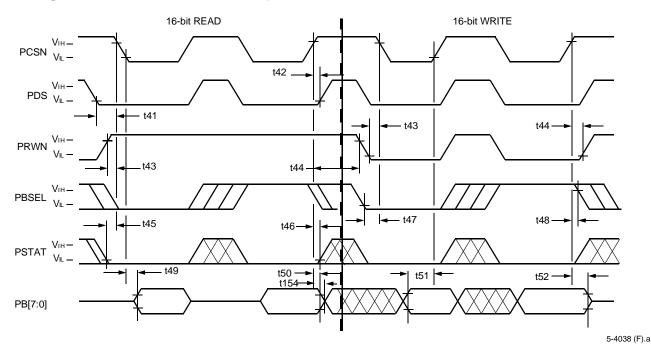

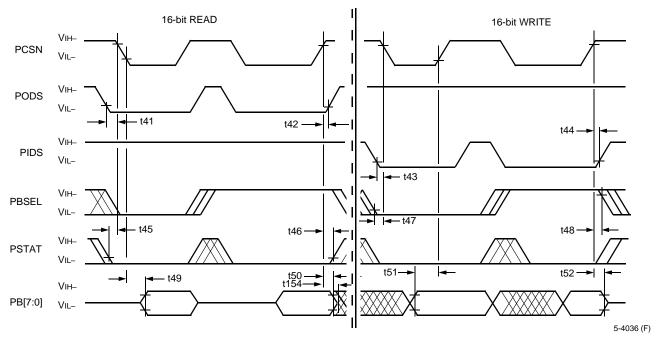

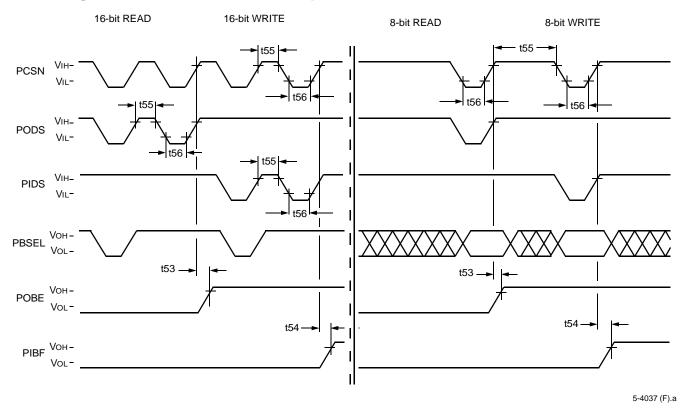

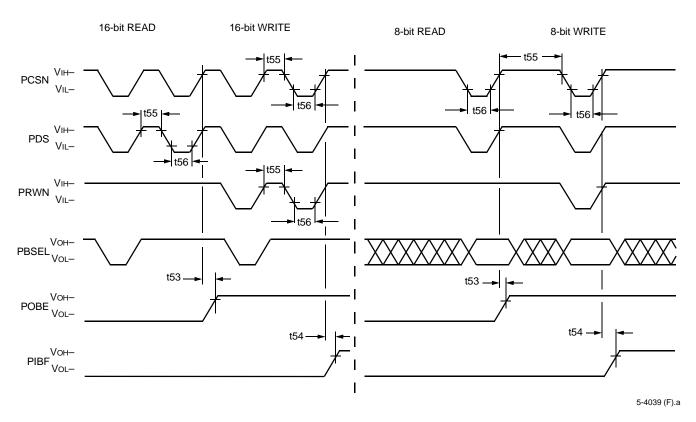

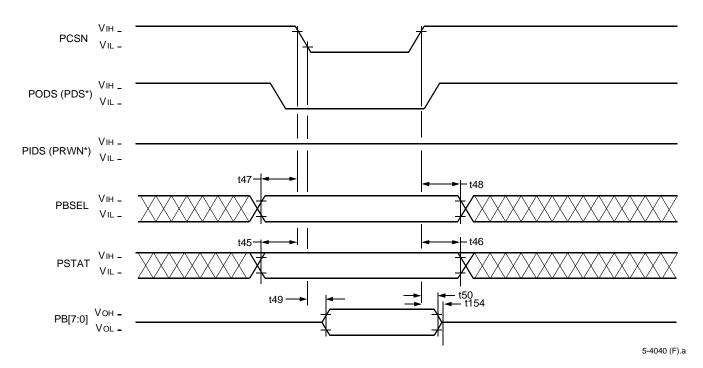

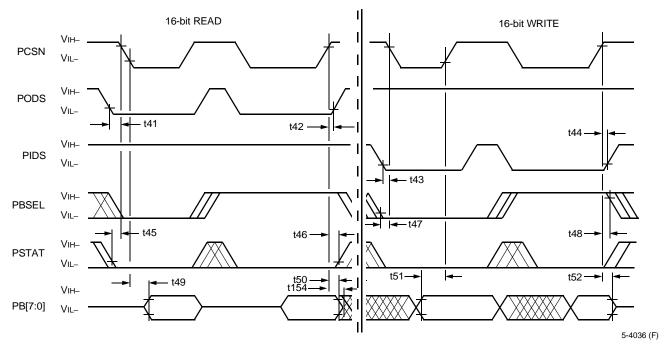

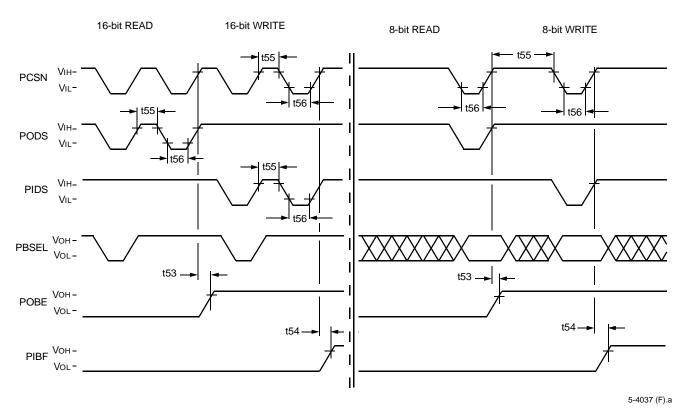

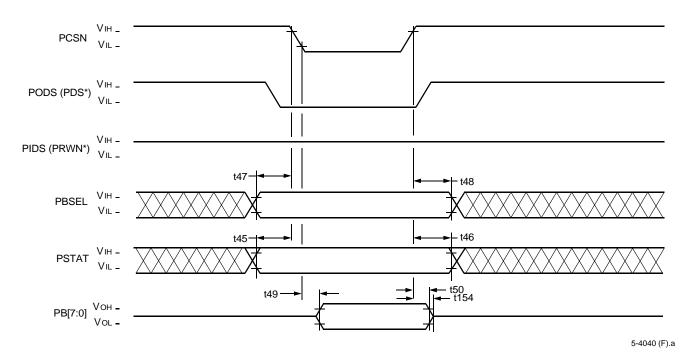

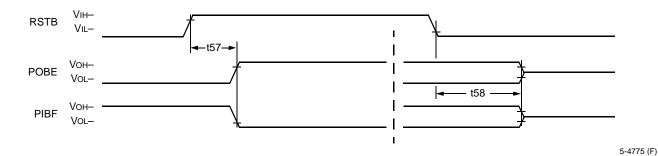

The PHIF is a passive, 8-bit parallel port which can interface to an 8-bit bus containing other Lucent Technologies DSPs (e.g., DSP1620, DSP1627, DSP1628, DSP1629, DSP1611, DSP1616, DSP1617, DSP1618), microprocessors, or peripheral I/O devices. The PHIF port supports either *Motorola* or *Intel* protocols, as well as 8-bit or 16-bit transfers, configured in software. The port data rate depends upon the instruction cycle rate. A 25 ns instruction cycle allows the PHIF to support data rates up to 11.85 Mbytes/s, assuming the external host device can transfer 1 byte of data in 25 ns.

The PHIF is accessed in two basic modes: 8-bit or 16-bit mode. In 16-bit mode, the host determines an access of the high or low byte. In 8-bit mode, only the low byte is accessed. Software-programmable features allow for a glueless host interface to microprocessors (see Section 4.8, Parallel Host Interface).

#### **Timer**

The timer can be used to provide an interrupt at the expiration of a programmed interval. The interrupt may be single or repetitive. More than nine orders of magnitude of interval selection are provided. The timer may be stopped and restarted at any time.

### Hardware Development System (HDS) Module

The on-chip HDS performs instruction breakpointing and branch tracing at full speed without additional off-chip hardware. Using the JTAG port, the breakpointing is set up, and the trace history is read back. The port works in conjunction with the HDS code in the on-chip ROM and the hardware and software in a remote computer. The HDS code must be linked to the user's application code and reside in the first 4 Kwords of ROM. The on-chip HDS cannot be used with the secure ROM masking option (see Section 7.3, ROM Security Options).

Four hardware breakpoints can be set on instruction addresses. A counter can be preset with the number of breakpoints to receive before trapping the core. Breakpoints can be set in interrupt service routines. Alternately, the counter can be preset with the number of cache instructions to execute before trapping the core.

Every time the program branches instead of executing the next sequential instruction, the addresses of the instructions executed before and after the branch are caught in circular memory. The memory contains the last four pairs of program discontinuities for hardware tracing. In systems with multiple processors, the processors may be configured such that any processor reaching a breakpoint will cause all the other processors to be trapped (see Section 4.3, Interrupts and Trap).

### **Pin Multiplexing**

In order to allow flexible device interfacing while maintaining a low package pin count, the DSP1627 multiplexes 16 package pins between BIO, PHIF, VEC[3:0], and SIO2.

Upon reset, the vectored interrupt indication signals, VEC[3:0], are connected to the package pins while IOBIT[4:7] are disconnected. Setting bit 12, EBIOH, of the ioc register connects IOBIT[4:7] to the package pins and disconnects VEC[3:0].

Upon reset, the parallel host interface (PHIF) is connected to the package pins while the second serial port (SIO2) and IOBIT[3:0] are disconnected. Setting bit 10, ESIO2, of the ioc register connects the SIO2 and IOBIT[3:0] and disconnects the PHIF.

### **Power Management**

Many applications, such as portable cellular terminals, require programmable sleep modes for power management. There are three different control mechanisms for achieving low-power operation: the powerc control register, the STOP pin, and the AWAIT bit in the alf register. The AWAIT bit in the alf register allows the processor to go into a power-saving standby mode until an interrupt occurs. The powerc register configures various power-saving modes by controlling internal clocks and peripheral I/O units. The STOP pin controls the internal processor clock. The various power management options may be chosen based on power consumption and/or wake-up latency requirements.

#### 4.2 DSP1600 Core Architectural Overview

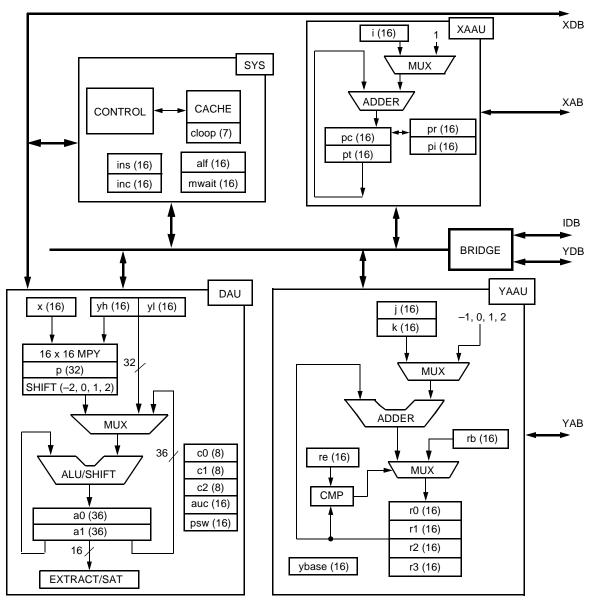

Figure 4 shows a block diagram of the DSP1600 core.

### System Cache and Control Section (SYS)

This section of the core contains a 15-word cache memory and controls the instruction sequencing. It handles vectored interrupts and traps, and also provides decoding for registers outside of the DSP1600 core. SYS stretches the processor cycle if wait-states are required (wait-states are programmable for external memory accesses). SYS sequences downloading via JTAG of self-test programs to on-chip, dual-port RAM.

The cache loop iteration count can be specified at run time under program control as well as at assembly time.

### Data Arithmetic Unit (DAU)

The data arithmetic unit (DAU) contains a 16 x 16-bit parallel multiplier that generates a full 32-bit product in one instruction cycle. The product can be accumulated with one of two 36-bit accumulators. The accumulator data can be directly loaded from, or stored to, memory in two 16-bit words with optional saturation on overflow. The arithmetic logic unit (ALU) supports a full set of arithmetic and logical operations on either 16- or 32-bit data. A standard set of flags can be tested for conditional ALU operations, branches, and subroutine calls. This procedure allows the processor to perform as a powerful 16- or 32-bit microprocessor for logical and control applications. The available instruction set is fully compatible with the DSP1617 instruction set. See Section 5.1 for more information on the instruction set.

The user also has access to two additional DAU registers. The psw register contains status information from the DAU (see Table 26, Processor Status Word Register). The arithmetic control register, auc, is used to configure some of the features of the DAU (see Table 27) including single-cycle squaring. The auc register alignment field supports an arithmetic shift left by one and left or right by two. The auc register is cleared by reset.

The counters c0 to c2 are signed, 8 bits wide, and may be used to count events such as the number of times the program has executed a sequence of code. They are controlled by the conditional instructions and provide a convenient method of program looping.

### Y Space Address Arithmetic Unit (YAAU)

The YAAU supports high-speed, register-indirect, compound, and direct addressing of data (Y) memory. Four general-purpose, 16-bit registers, r0 to r3, are available in the YAAU. These registers can be used to supply the read or write addresses for Y space data. The YAAU also decodes the 16-bit data memory address and outputs individual memory enables for the data access. The YAAU can address the six 1 Kword banks of onchip DPRAM or three external data memory segments. Up to 48 Kwords of off-chip RAM are addressable, with 16K addresses reserved for internal RAM.

Two 16-bit registers, rb and re, allow zero-overhead modulo addressing of data for efficient filter implementations. Two 16-bit signed registers, j and k, are used to hold user-defined postmodification increments. Fixed increments of +1, -1, and +2 are also available. Four compound-addressing modes are provided to make read/write operations more efficient.

The YAAU allows direct (or indexed) addressing of data memory. In direct addressing, the 16-bit base register (ybase) supplies the 11 most significant bits of the address. The direct data instruction supplies the remaining 5 bits to form an address to Y memory space and also specifies one of 16 registers for the source or destination.

#### X Space Address Arithmetic Unit (XAAU)

The XAAU supports high-speed, register-indirect, instruction/coefficient memory addressing with postmodification of the register. The 16-bit pt register is used for addressing coefficients. The signed register i holds a user-defined postincrement. A fixed postincrement of +1 is also available. Register PC is the program counter. Registers pr and pi hold the return address for subroutine calls and interrupts, respectively.

The XAAU decodes the 16-bit instruction/coefficient address and produces enable signals for the appropriate X memory segment. The addressable X segments are internal ROM (up to 36 Kwords for the DSP1627x36, up to 32 Kwords for the DSP1627x32), six 1K banks of DPRAM, and external ROM.

The locations of these memory segments depend upon the memory map selected (see Table 5). A security mode can be selected by mask option. This prevents unauthorized access to the contents of on-chip ROM (see Section 7, Mask-Programmable Options).

### 4.3 Interrupts and Trap

The DSP1627 supports prioritized, vectored interrupts and a trap. The device has eight internal hardware sources of program interrupt and two external interrupt pins. Additionally, there is a trap pin and a trap signal from the hardware development system (HDS). A software interrupt is available through the **icall** instruction. The **icall** instruction is reserved for use by the HDS. Each of these sources of interrupt and trap has a unique vector address and priority assigned to it. DSP16A interrupt compatibility is not maintained.

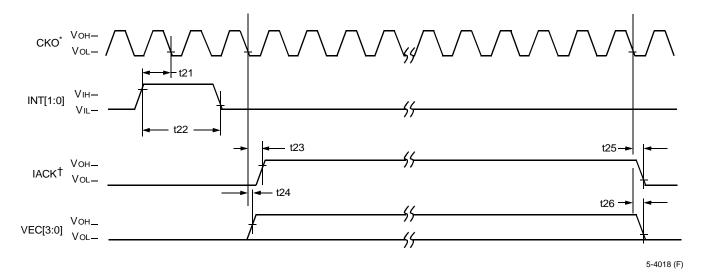

The software interrupt and the traps are always enabled and do not have a corresponding bit in the ins register. Other vectored interrupts are enabled in the inc register (see Table 29, Interrupt Control (inc) Register) and monitored in the ins register (see Table 30, Interrupt Status (ins) Register). When the DSP1627 goes into an interrupt or trap service routine, the IACK pin is asserted. In addition, pins VEC[3:0] encode which interrupt/ trap is being serviced. Table 4 details the encoding used for VEC[3:0].

5-1741 (F).b

Figure 4. DSP1600 Core Block Diagram

Table 3. DSP1600 Core Block Diagram Legend

| Symbol      | Name                                                                     |

|-------------|--------------------------------------------------------------------------|

| 16 x 16 MPY | 16-bit x 16-bit Multiplier.                                              |

| a0—a1       | Accumulators 0 and 1 (16-bit halves specified as a0, a0l, a1, and a1l)*. |

| alf         | AWAIT, LOWPR, Flags.                                                     |

| ALU/SHIFT   | Arithmetic Logic Unit/Shifter.                                           |

| auc         | Arithmetic Unit Control.                                                 |

| c0—c2       | Counters 0—2.                                                            |

| cloop       | Cache Loop Count.                                                        |

| CMP         | Comparator.                                                              |

| DAU         | Digital Arithmetic Unit.                                                 |

| i           | Increment Register for the X Address Space.                              |

| IDB         | Internal Data Bus.                                                       |

| inc         | Interrupt Control.                                                       |

| ins         | Interrupt Status.                                                        |

| j           | Increment Register for the Y Address Space.                              |

| k           | Increment Register for the Y Address Space.                              |

| MUX         | Multiplexer.                                                             |

| mwait       | External Memory Wait-states Register.                                    |

| р           | Product Register (16-bit halves specified as p, pl).                     |

| PC          | Program Counter.                                                         |

| pi          | Program Interrupt Return Register.                                       |

| pr          | Program Return Register.                                                 |

| psw         | Processor Status Word.                                                   |

| pt          | X Address Space Pointer.                                                 |

| r0—r3       | Y Address Space Pointers.                                                |

| rb          | Modulo Addressing Register (begin address).                              |

| re          | Modulo Addressing Register (end address).                                |

| SYS         | System Cache and Control Section.                                        |

| X           | Multiplier Input Register.                                               |

| XAAU        | X Space Address Arithmetic Unit.                                         |

| XAB         | X Space Address Bus.                                                     |

| XDB         | X Space Data Bus.                                                        |

| YAAU        | Y Space Address Arithmetic Unit.                                         |

| YAB         | Y Space Address Bus.                                                     |

| YDB         | Y Space Data Bus.                                                        |

| ybase       | Direct Addressing Base Register.                                         |

| у           | DAU Register (16-bit halves specified as y, yl).                         |

<sup>\*</sup> F3 ALU instructions with immediates require specifying the high half of the accumulators as a0h and a1h.

### Interruptibility

Vectored interrupts are serviced only after the execution of an interruptible instruction. If more than one vectored interrupt is asserted at the same time, the interrupts are serviced sequentially according to their assigned priorities. See Table 4 for the priorities assigned to the vectored interrupts. Interrupt service routines, branch and conditional branch instructions, cache loops, and instructions that only decrement one of the RAM pointers, r0 to r3 (e.g., \*r3--), are not interruptible.

A trap is similar to an interrupt, but it gains control of the processor by branching to the trap service routine even when the current instruction is noninterruptible. It may not be possible to return to normal instruction execution from the trap service routine since the machine state cannot always be saved. In particular, program execution cannot be continued from a trapped cache loop or interrupt service routine. While in a trap service routine, another trap is ignored.

When set to 1, the status bits in the ins register indicate that an interrupt has occurred. The processor must reach an interruptible state (completion of an interruptible instruction) before an enabled vectored interrupt will be acted on. An interrupt will not be serviced if it is not enabled. Polled interrupt service can be implemented by disabling the interrupt in the inc register and then polling the ins register for the expected event.

## **Vectored Interrupts**

Tables 29 and 30 show the inc and ins registers. A logic 1 written to any bit of inc enables (or unmasks) the associated interrupt. If the bit is cleared to a logic 0, the interrupt is masked. Note that neither the software interrupt nor traps can be masked.

The occurrence of an interrupt that is not masked will cause the program execution to transfer to the memory location pointed to by that interrupt's vector address, assuming no other interrupt is being serviced (see Table 4, Interrupt Vector Table). The occurrence of an interrupt that is masked causes no automatic processor action, but will set the corresponding status bit in the ins register. If a masked interrupt occurs, it is latched in the ins register, but the interrupt is not taken. When unlatched, this latched interrupt will initiate automatic processor interrupt action. See the DSP1611/17/18/27 Digital Signal Processor Information Manual for a more detailed description of the interrupts.

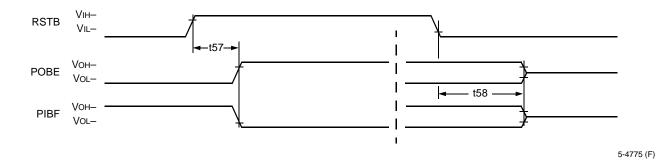

### Signaling Interrupt Service Status

Five pins of DSP1627 are devoted to signaling interrupt service status. The IACK pin goes high while any interrupt or user trap is being serviced, and goes low when the ireturn instruction from the service routine is issued. Four pins, VEC[3:0], carry a code indicating which of the interrupts or trap is being serviced. Table 4 contains the encodings used by each interrupt.

Traps due to HDS breakpoints have no effect on either the IACK or VEC[3:0] pins. Instead, they show the interrupt state or interrupt source of the DSP when the trap occurred.

#### **Clearing Interrupts**

The PHIF interrupts (PIBF and POBE) are cleared by reading or writing the parallel host interface data transmit registers pdx0[in] and pdx0[out], respectively. The SIO and SIO2 interrupts (IBF, IBF2, OBE, and OBE2) are cleared by reading or writing, as appropriate, the serial data registers sdx[in], sdx2[in], sdx[out], and sdx2[out]. The JTAG interrupt (JINT) is cleared by reading the jtag register.

Three of the vectored interrupts are cleared by writing to the ins register. Writing a 1 to the INTO, INT1, or TIME bits in the ins will cause the corresponding interrupt status bit to be cleared to a logic 0. The status bit for these vectored interrupts is also cleared when the ireturn instruction is executed, leaving set any other vectored interrupts that are pending.

# **Traps**

The TRAP pin of the DSP1627 is a bidirectional signal. At reset, it is configured as an input to the processor. Asserting the TRAP pin will force a user trap. The trap mechanism is used for two purposes. It can be used by an application to rapidly gain control of the processor for asynchronous time-critical event handling (typically for catastrophic error recovery). It is also used by the HDS for breakpointing and gaining control of the processor. Separate vectors are provided for the user trap (0x46) and the HDS trap (0x3). Traps are not maskable.

**Table 4. Interrupt Vector Table**

| Source             | Vector | Priority     | VEC[3:0] | Issued by                |

|--------------------|--------|--------------|----------|--------------------------|

| No Interrupt       | _      | _            | 0x0      | _                        |

| Software Interrupt | 0x2    | 1            | 0x1      | icall                    |

| INT0               | 0x1    | 2            | 0x2      | pin                      |

| JINT               | 0x42   | 3            | 0x8      | jtag in                  |

| INT1               | 0x4    | 4            | 0x9      | pin                      |

| TIME               | 0x10   | 7            | 0xc      | timer                    |

| IBF2               | 0x14   | 8            | 0xd      | SIO2 in                  |

| OBE2               | 0x18   | 9            | 0xe      | SIO2 out                 |

| Reserved           | 0x1c   | 10           | 0x0      | _                        |

| Reserved           | 0x20   | 11           | 0x1      | _                        |

| Reserved           | 0x24   | 12           | 0x2      | _                        |

| IBF                | 0x2c   | 14           | 0x3      | SIO in                   |

| OBE                | 0x30   | 15           | 0x4      | SIO out                  |

| PIBF               | 0x34   | 16           | 0x5      | PHIF in                  |

| POBE               | 0x38   | 17           | 0x6      | PHIF out                 |

| TRAP from HDS      | 0x3    | 18           | _*       | breakpoint, jtag, or pin |

| TRAP from User     | 0x46   | 19 = highest | 0x7      | pin                      |

<sup>\*</sup> Traps due to HDS breakpoints have no effect on VEC[3:0] pins.

A trap has four cycles of latency. At most, two instructions will execute from the time the trap is received at the pin to when it gains control. An instruction that is executing when a trap occurs is allowed to complete before the trap service routine is entered. (Note that the instruction could be lengthened by wait-states.) During normal program execution, the pi register contains either the address of the next instruction (two-cycle instruction executing) or the address following the next instruction (one-cycle instruction executing). In an interrupt service routine, pi contains the interrupt return address. When a trap occurs during an interrupt service routine, the value of the pi register may be overwritten. Specifically, it is not possible to return to an interrupt service routine from a user trap (0x46) service routine. Continuing program execution when a trap occurs during a cache loop is also not possible.

The HDS trap causes circuitry to force the program memory map to MAP1 (with on-chip ROM starting at address 0x0) when the trap is taken. The previous memory map is restored when the trap service routine exits by issuing an ireturn. The map is forced to MAP1 because the HDS code, if present, resides in the on-chip ROM.

Using the Lucent Technologies development tools, the TRAP pin may be configured to be an output, or an input vectoring to address 0x3. In a multiprocessor environment, the TRAP pins of all the DSPs present can be tied together. During HDS operations, one DSP is selected by the host software to be the master. The master processor's TRAP pin is configured to be an output.

The TRAP pins of the slave processors are configured as inputs. When the master processor reaches a breakpoint, the master's TRAP pin is asserted. The slave processors will respond to their TRAP input by beginning to execute the HDS code.

### **AWAIT Interrupt (Standby or Sleep Mode)**

Setting the AWAIT bit (bit 15) of the alf register (alf = 0x8000) causes the processor to go into a power-saving standby or sleep mode. Only the minimum circuitry on the chip required to process an incoming interrupt remains active. After the AWAIT bit is set, one additional instruction will be executed before the stand-by power-saving mode is entered. A PHIF or SIO word transfer will complete if already in progress. The AWAIT bit is reset when the first interrupt occurs. The chip then wakes up and continues executing.

Two **nop** instructions should be programmed after the AWAIT bit is set. The first **nop** (one cycle) will be executed before sleeping; the second will be executed after the interrupt signal awakens the DSP and before the interrupt service routine is executed.

The AWAIT bit should be set from within the cache if the code which is executing resides in external ROM where more than one wait-state has been programmed. This ensures that an interrupt will not disturb the device from completely entering the sleep state.

For additional power savings, set ioc = 0x0180 and timerc = 0x0040 in addition to setting alf = 0x8000. This will hold the CKO pin low and shut down the timer and prescaler (see Table 38 and Table 31).

For a description of the control mechanisms for putting the DSP into low-power modes, see Section 4.13, Power Management.

# 4.4 Memory Maps and Wait-States

The DSP1600 core implements a modified Harvard architecture that has separate on-chip 16-bit address and data buses for the instruction/coefficient (X) and data (Y) memory spaces. Table 5 shows the instruction/coefficient memory space maps for both the DSP1627x36 and DSP1627x32.

The differences between the x36 and x32 memory maps can be seen by comparing the respective MAP1 and MAP3. For instance, MAP1 of the x36 provides for 36 Kwords of IROM and 6 Kwords of dual-port RAM (DPRAM), whereas MAP1 of the x32 provides for 32 Kwords of IROM, 6 Kwords of DPRAM, and 16 Kwords of EROM.

The DSP1627 provides a multiplexed external bus which accesses external RAM (ERAM) and ROM (EROM). Programmable wait-states are provided for external memory accesses. The instruction/coefficient memory map is configurable to provide application flexibility. Table 6 shows the data memory space, which has one map.

### **Instruction/Coefficient Memory Map Selection**

In determining which memory map to use, the processor evaluates the state of two parameters. The first is the LOWPR bit (bit 14) of the alf register. The LOWPR bit of the alf register is initialized to 0 automatically at reset. LOWPR controls the starting address in memory assigned to the six 1K banks of dual-port RAM. If LOWPR is low, internal dual-port RAM begins at address 0xC000. If LOWPR is high, internal dual-port RAM begins at address 0x0. LOWPR also moves IROM from 0x0 in MAP1 to 0x4000 in MAP3, and EROM from 0x0 in MAP2 to 0x4000 in MAP4.

The second parameter is the value at reset of the EXM pin (pin 27 or pin 14, depending upon the package type). EXM determines whether the internal 36 Kwords ROM (IROM) will be addressable in the memory map.

The Lucent Technologies development system tools, together with the on-chip HDS circuitry and the JTAG port, can independently set the memory map. Specifically, during an HDS trap, the memory map is forced to

MAP1. The user's map selection is restored when the trap service routine has completed execution.

#### MAP1

MAP1 has the IROM starting at 0x0 and six 1 Kword banks of DPRAM starting at 0xC000. Additionally, MAP1 for the x32 has 16 Kwords of EROM starting at 0x8000. MAP1 is used if DSP1627 has EXM low at reset and the LOWPR parameter is programmed to zero. It is also used during an HDS trap.

#### MAP2

MAP2 differs from MAP1 in that the lowest 48 Kwords reference external ROM (EROM). MAP2 is used if EXM is high at reset, the LOWPR parameter is programmed to zero, and an HDS trap is not in progress.

#### MAP3

MAP3 has the six 1 Kword banks of DPRAM starting at address 0x0. In MAP3 of the x36, the 36 Kwords of IROM start at 0x4000. Similarly, for the x32, 32 Kwords of IROM start at 0x4000. Additionally, MAP3 for the x32 has 16 Kwords of EROM starting at 0xC000. MAP3 is used if EXM is low at reset, the LOWPR bit is programmed to 1, and an HDS trap is not in progress. Note that this map is not available if the secure mask-programmable option has been ordered.

#### MAP4

MAP4 differs from MAP3 in that addresses above 0x4000 reference external ROM (EROM). This map is used if the LOWPR bit is programmed to 1, an HDS trap is not in progress, and, either EXM is high during reset, or the secure mask-programmable option has been ordered.

Whenever the chip is reset using the RSTB pin, the default memory map will be MAP1 or MAP2, depending upon the state of the EXM pin at reset. A reset through the HDS will not reinitialize the alf register, so the previous memory map is retained.

#### **Boot from External ROM**

After RSTB goes from low to high, the DSP1627 comes out of reset and fetches an instruction from address zero of the instruction/coefficient space. The physical location of address zero is determined by the memory map in effect. If EXM is high at the rising edge of RSTB, MAP2 is selected. MAP2 has EROM at location zero; thus, program execution begins from external memory. If EXM is high and INT1 is low when RSTB rises, the mwait register defaults to 15 wait-states for all external memory segments. If INT1 is high, the mwait register defaults to 0 wait-states.

**Table 5. Instruction/Coefficient Memory Maps**

### DSP1627x36

| X Address | AB[0:15] | MAP 1*<br>EXM = 0<br>LOWPR = 0 <sup>†</sup> | MAP 2<br>EXM = 1<br>LOWPR = 0 | MAP 3 <sup>‡</sup><br>EXM = 0<br>LOWPR = 1 | MAP 4<br>EXM = 1<br>LOWPR = 1 |

|-----------|----------|---------------------------------------------|-------------------------------|--------------------------------------------|-------------------------------|

| 0         | 0x0000   | IROM                                        | EROM                          | DPRAM                                      | DPRAM                         |

| 4K        | 0x1000   | (36K)                                       | (48K)                         | (6K)                                       | (6K)                          |

| 6K        | 0x1800   |                                             |                               | Reserved                                   | Reserved                      |

| 12K       | 0x3000   |                                             |                               | (10K)                                      | (10K)                         |

| 16K       | 0x4000   |                                             |                               | IROM                                       | EROM                          |

| 20K       | 0x5000   |                                             |                               | (36K)                                      | (48K)                         |

| 24K       | 0x6000   |                                             |                               |                                            |                               |

| 28K       | 0x7000   |                                             |                               |                                            |                               |

| 32K       | 0x8000   |                                             |                               |                                            |                               |

| 36K       | 0x9000   | Reserved                                    |                               |                                            |                               |

| 40K       | 0xA000   | (12K)                                       |                               |                                            |                               |

| 44K       | 0xB000   |                                             |                               |                                            |                               |

| 48K       | 0xC000   | DPRAM                                       | DPRAM                         |                                            |                               |

| 52K       | 0xD000   | (6K)                                        | (6K)                          | Reserved                                   |                               |

| 54K       | 0xD800   | Reserved                                    | Reserved                      | (12K)                                      |                               |

| 56K       | 0xE000   | (10K)                                       | (10K)                         |                                            |                               |

| 60K—64K   | 0xFFFF   |                                             |                               |                                            |                               |

<sup>\*</sup> MAP1 is set automatically during an HDS trap. The user-selected map is restored at the end of the HDS trap service routine.

### DSP1627x32

| X Address | AB[0:15] | MAP 1*<br>EXM = 0<br>LOWPR = 0 <sup>†</sup> | MAP 2<br>EXM = 1<br>LOWPR = 0 | MAP 3 <sup>‡</sup><br>EXM = 0<br>LOWPR = 1 | MAP 4<br>EXM = 1<br>LOWPR = 1 |

|-----------|----------|---------------------------------------------|-------------------------------|--------------------------------------------|-------------------------------|

| 0         | 0x0000   | IROM                                        | EROM                          | DPRAM                                      | DPRAM                         |

| 4K        | 0x1000   | (32K)                                       | (48K)                         | (6K)                                       | (6K)                          |

| 6K        | 0x1800   |                                             |                               | Reserved                                   | Reserved                      |

| 12K       | 0x3000   |                                             |                               | (10K)                                      | (10K)                         |

| 16K       | 0x4000   | ]                                           |                               | IROM                                       | EROM                          |

| 20K       | 0x5000   | ]                                           |                               | (32K)                                      | (48K)                         |

| 24K       | 0x6000   | ]                                           |                               |                                            |                               |

| 28K       | 0x7000   | ]                                           |                               |                                            |                               |

| 32K       | 0x8000   | EROM                                        |                               |                                            |                               |

| 36K       | 0x9000   | (16K)                                       |                               |                                            |                               |

| 40K       | 0xA000   |                                             |                               |                                            |                               |

| 44K       | 0xB000   |                                             |                               |                                            |                               |

| 48K       | 0xC000   | DPRAM                                       | DPRAM                         | EROM                                       |                               |

| 52K       | 0xD000   | (6K)                                        | (6K)                          | (16K)                                      |                               |

| 54K       | 0xD800   | Reserved                                    | Reserved                      |                                            |                               |

| 56K       | 0xE000   | (10K)                                       | (10K)                         |                                            |                               |

| 60K—64K   | 0xFFFF   |                                             |                               |                                            |                               |

<sup>\*</sup> MAP1 is set automatically during an HDS trap. The user-selected map is restored at the end of the HDS trap service routine.

<sup>†</sup> LOWPR is an alf register bit. The Lucent Technologies development system tools can independently set the memory map.

<sup>‡</sup> MAP3 is not available if the secure mask-programmable option is selected.

<sup>†</sup> LOWPR is an alf register bit. The Lucent Technologies development system tools can independently set the memory map.

<sup>‡</sup> MAP3 is not available if the secure mask-programmable option is selected.

#### **Data Memory Mapping**

Table 6. Data Memory Map (Not to Scale)

| Decimal<br>Address | Address in r0, r1, r2, r3 | Segment           |

|--------------------|---------------------------|-------------------|

| 0                  | 0x0000                    | DPRAM[1:6]        |

| 6K                 | 0x1800                    | Reserved<br>(10K) |

| 16K                | 0x4000                    | Ю                 |

| 16,640             | 0x4100                    | ERAMLO            |

| 32K                | 0x8000                    | ERAMHI            |

| 64K – 1            | 0xFFFF                    |                   |

On the data memory side (see Table 6), the six 1K banks of dual-port RAM are located starting at address 0. Addresses from 0x4000 to 0x40FF reference a 256-word memory-mapped I/O segment (IO). Addresses from 0x4100 to 0x7FFF reference the low external data RAM segment (ERAMLO). Addresses above 0x8000 reference high external data RAM (ERAMHI).

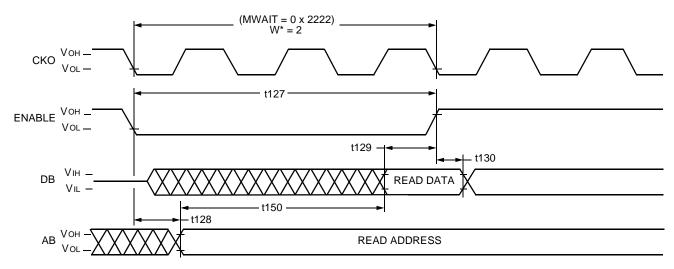

#### **Wait-States**

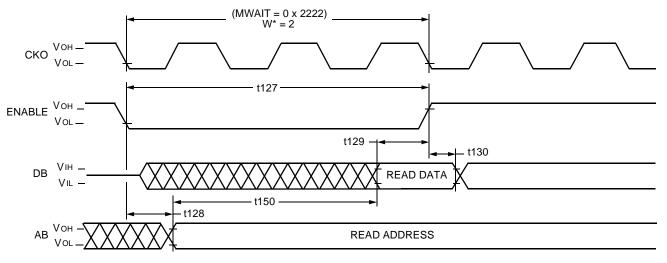

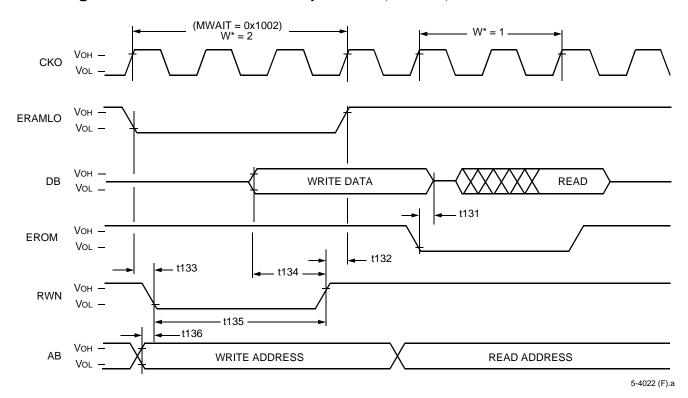

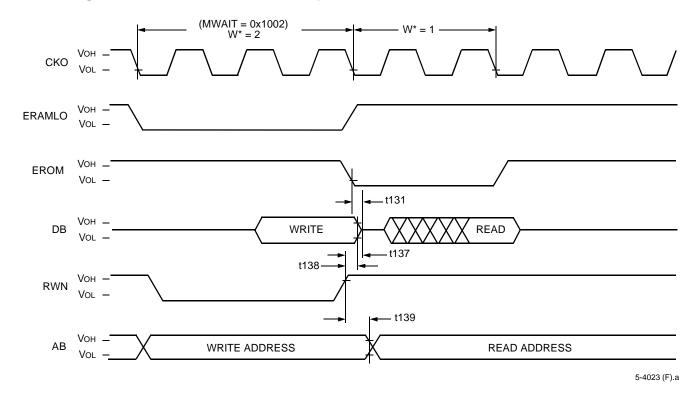

The number of wait-states (from 0 to 15) used when accessing each of the four external memory segments (ERAMLO, IO, ERAMHI, and EROM) is programmable in the mwait register (see Table 36). When the program references memory in one of the four external segments, the internal multiplexer is automatically switched to the appropriate set of internal buses, and the associated external enable of ERAMLO, IO, ERAMHI, or EROM is issued. The external memory cycle is automatically stretched by the number of wait-states configured in the appropriate field of the mwait register.

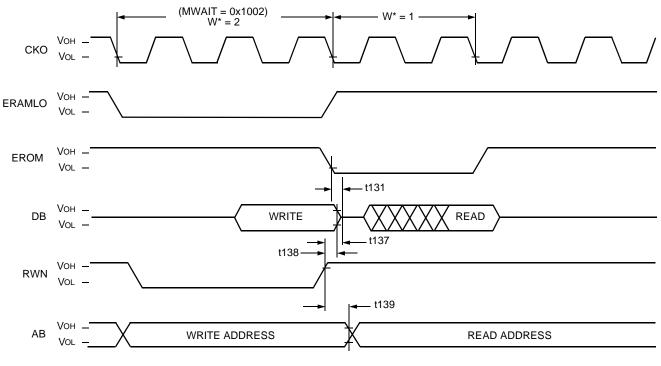

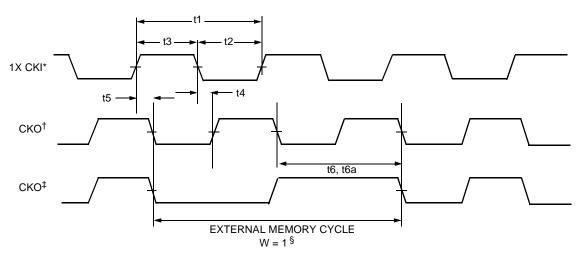

# 4.5 External Memory Interface (EMI)

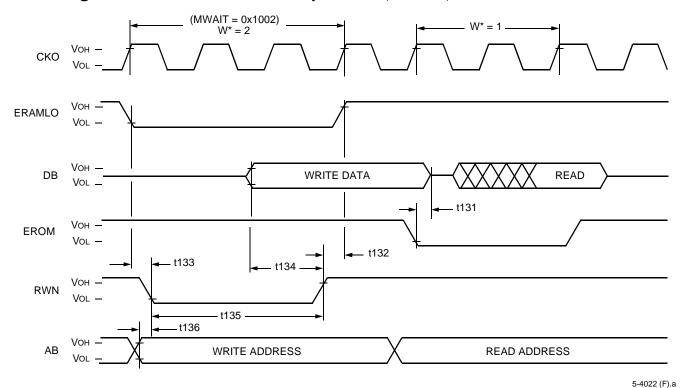

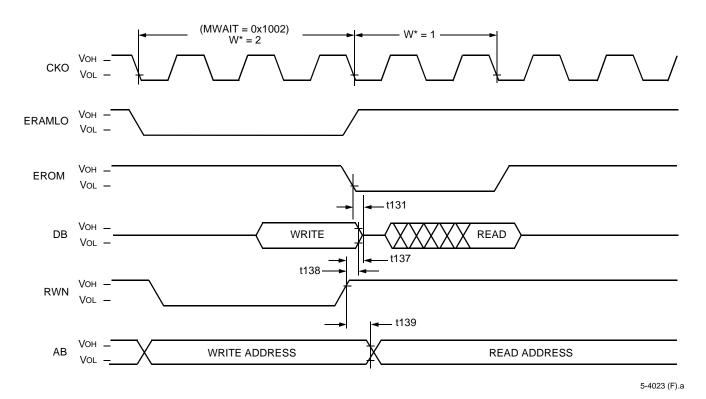

The external memory interface supports read/write operations from instruction/coefficient memory, data memory, and memory-mapped I/O devices. The DSP1627 provides a 16-bit external address bus, AB[15:0], and a 16-bit external data bus, DB[15:0]. These buses are multiplexed between the internal buses for the instruction/coefficient memory and the data memory. Four external memory segment enables, ERAMLO, IO, ERAMHI, and EROM, select the external memory segment to be addressed.

If a data memory location with an address between 0x4100 and 0x7FFF is addressed, ERAMLO is asserted low.

If one of the 256 external data memory locations, with an address greater than or equal to 0x4000, and less than or equal to 0x40FF, is addressed, IO is asserted low. IO is intended for memory-mapped I/O.

If a data memory location with an address greater than or equal to 0x8000 is addressed, ERAMHI is asserted low. When the external instruction/coefficient memory is addressed, EROM is asserted low.

The flexibility provided by the programmable options of the external memory interface (see Table 36, mwait Register and Table 38, ioc Register) allows the DSP1627 to interface gluelessly with a variety of commercial memory chips.

Each of the four external memory segments, ERAMLO, IO, ERAMHI, and EROM, has a number of wait-states that is programmable (from 0 to 15) by writing to the mwait register. When the program references memory in one of the four external segments, the internal multiplexer is automatically switched to the appropriate set of internal buses, and the associated external enable of ERAMLO, IO, ERAMHI, or EROM is issued. The external memory cycle is automatically stretched by the number of wait-states in the appropriate field of the mwait register.

When writing to external memory, the RWN pin goes low for the external cycle. The external data bus, DB[15:0], is driven by the DSP1627 starting halfway through the cycle. The data driven on the external data bus is automatically held after the cycle unless an external read cycle immediately follows.

The DSP1627 has one external address bus and one external data bus for both memory spaces. Since some instructions provide the capability of simultaneous access to both X space and Y space, some provision must be made to avoid collisions for external accesses. The DSP1627 has a sequencer that does the external X access first, and then the external Y access, transparently to the programmer. Wait-states are maintained as

programmed in the mwait register. For example, let two instructions be executed: the first reads a coefficient from EROM and writes data to ERAM; the second reads a coefficient from EROM and reads data from ERAM. The sequencer carries out the following steps at the external memory interface: read EROM, write ERAM, read EROM, and read ERAM. Each step is done in sequential one-instruction cycle steps, assuming zero wait-states are programmed. Note that the number of instruction cycles taken by the two instructions is four. Also, in this case, the write hold time is zero.

The DSP1627 allows writing into external instruction/coefficient memory. By setting bit 11, WEROM, of the ioc register (see Table 38), writing to (or reading from) data memory or memory-mapped I/O asserts the EROM strobe instead of ERAMLO, IO, or ERAMHI. Therefore, with WEROM set, EROM appears in both Y space (replacing ERAM) and X space, in its normal position.

Bit 14 of the ioc register (see Table 38), EXTROM, may be used with WEROM to download to a full 64K of external memory. When WEROM and EXTROM are both asserted, address bit 15 (AB15) is held low, aliasing the upper 32K of external memory into the lower 32K.

When an access to internal memory is made, the AB[15:0] bus holds the last valid external memory address. Asserting the RSTB pin low 3-states the AB[15:0] bus. After reset, the AB[15:0] value is undefined.

The leading edge of the memory segment enables can be delayed by approximately one-half a CKO period by programming the ioc register (see Table 38). This is used to avoid a situation in which two devices drive the data bus simultaneously.

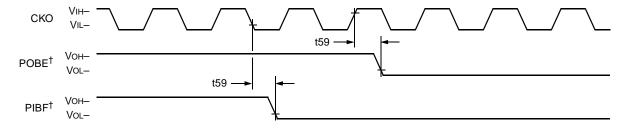

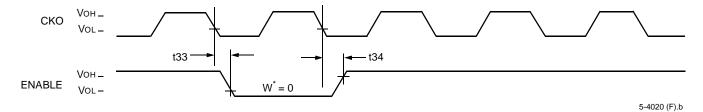

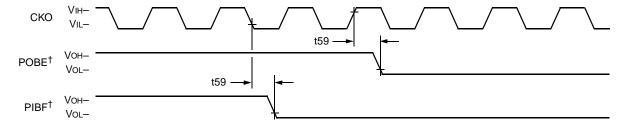

Bits 7, 8, and 13 of the ioc register select the mode of operation for the CKO pin (see Table 38). Available options are a free-running unstretched clock, a wait-stated sequenced clock (runs through two complete cycles during a sequenced external memory access), and a wait-stated clock based on the internal instruction cycle. These clocks drop to the low-speed internal ring oscillator when SLOWCKI is enabled (see 4.13, Power Management). The high-to-low transitions of the wait-stated clock are synchronized to the high-to-low transition of the free-running clock. Also, the CKO pin provides either a continuously high level, a continuously low level, or changes at the rate of the internal processor clock. This last option, only available with the crystal and small-signal input clock options, enables the DSP1627 CKI input buffer to deliver a full-rate clock to other devices while the DSP1627 itself is in one of the low-power modes.

### 4.6 Bit Manipulation Unit (BMU)

The BMU interfaces directly to the main accumulators in the DAU providing the following features:

- Barrel shifting—logical and arithmetic, left and right shift

- Normalization and extraction of exponent

- Bit-field extraction and insertion

These features increase the efficiency of the DSP in applications such as control or data encoding and decoding. For example, data packing and unpacking, in which short data words are packed into one 16-bit word for more efficient memory storage, is very easy.

In addition, the BMU provides two auxiliary accumulators, aa0 and aa1. In one instruction cycle, 36-bit data can be shuffled, or swapped, between one of the main accumulators and one of the alternate accumulators. The ar<0—3> registers are 16-bit registers that control the operations of the BMU. They store a value that determines the amount of shift or the width and offset fields for bit extraction or insertion. Certain operations in the BMU set flags in the DAU psw register and the alf register (see Table 26, Processor Status Word (psw) Register, and Table 35, alf Register). The ar<0—3> registers can also be used as general-purpose registers.

The BMU instructions are detailed in Section 5.1. For a thorough description of the BMU, see the *DSP1611/17/18/27 Digital Signal Processor Information Manual*.

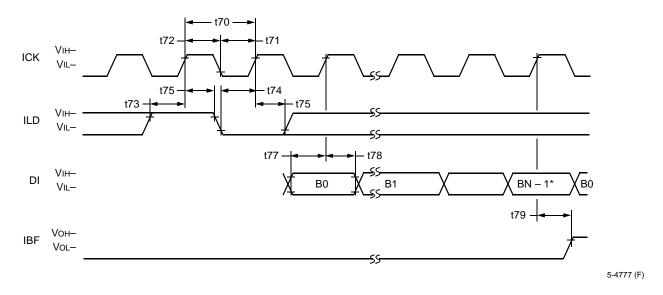

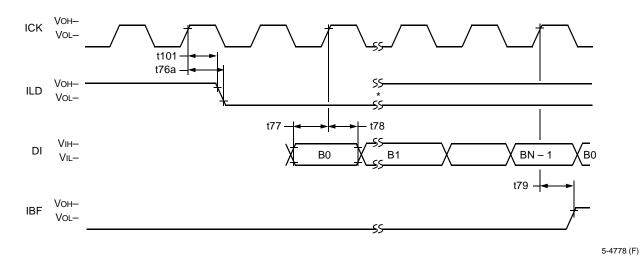

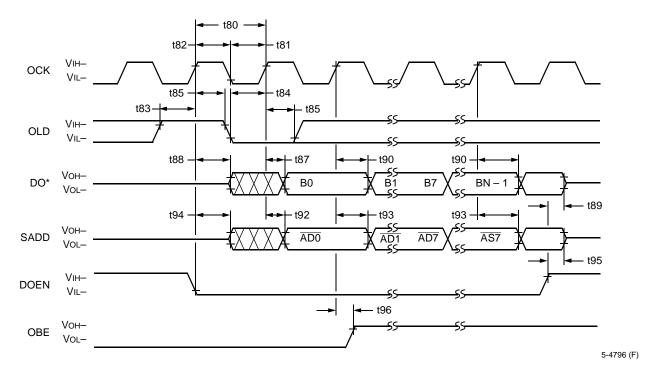

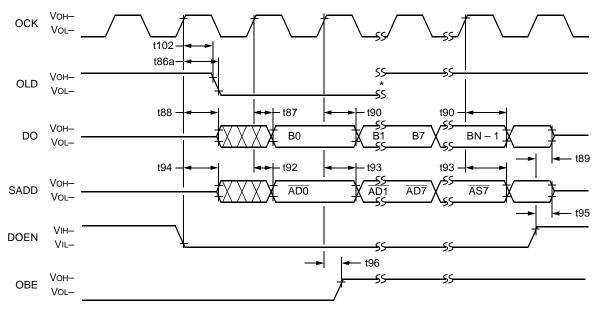

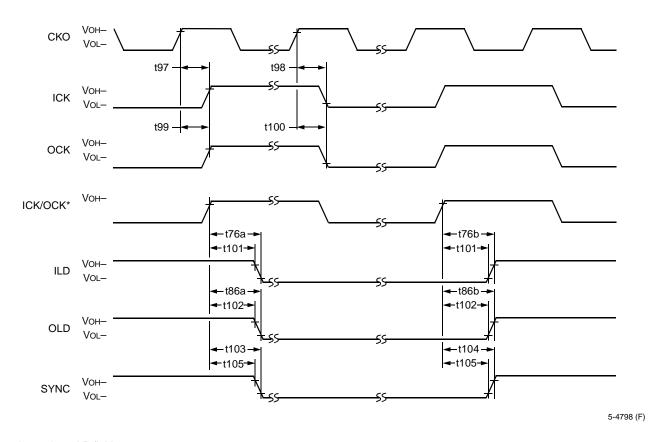

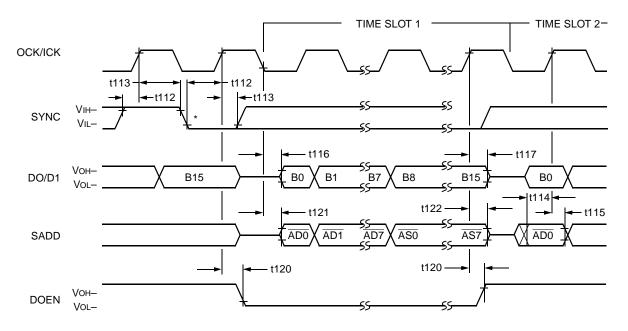

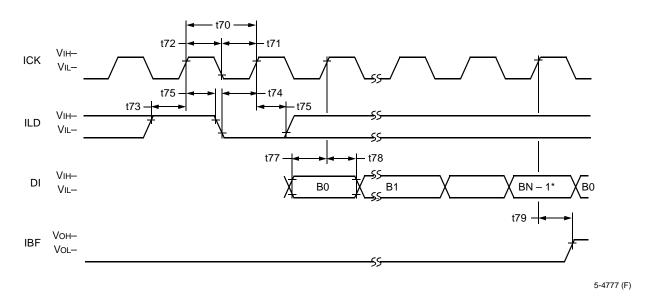

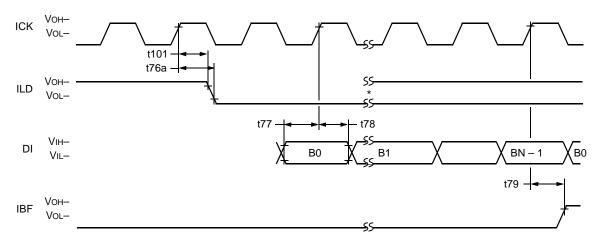

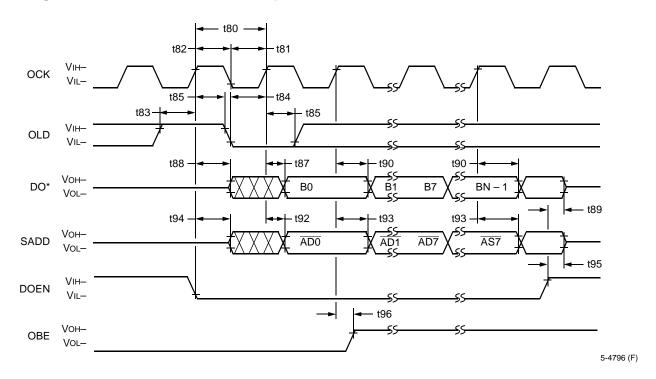

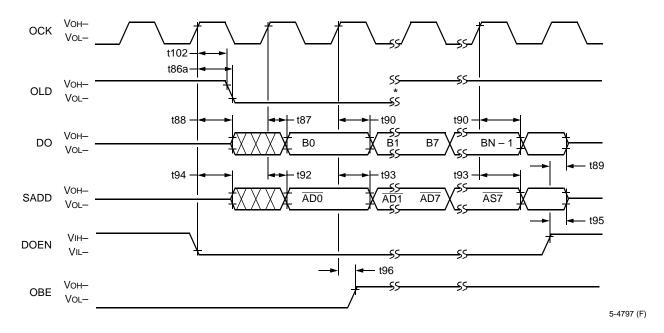

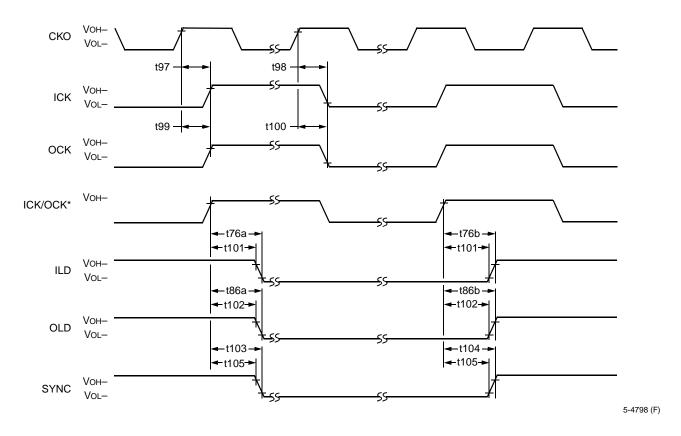

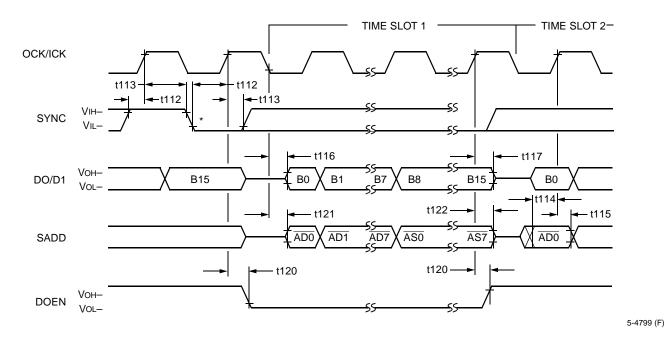

### 4.7 Serial I/O Units (SIOs)

The serial I/O ports on the DSP1627 device provide a serial interface to many codecs and signal processors with little, if any, external hardware required. Each high-speed, double-buffered port (sdx and sdx2) supports back-to-back transmissions of data. SIO and SIO2 are identical. The output buffer empty (OBE and OBE2) and input buffer full (IBF and IBF2) flags facilitate the reading and/or writing of each serial I/O port by programor interrupt-driven I/O. There are four selectable active clock speeds.

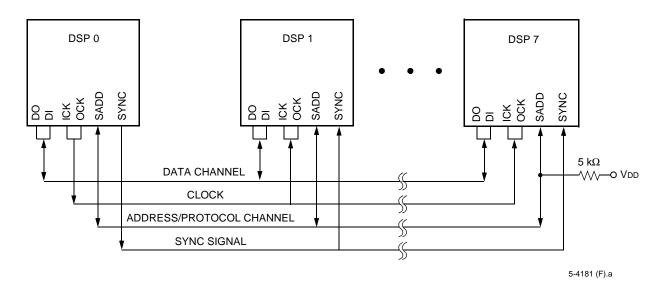

A bit-reversal mode provides compatibility with either the most significant bit (MSB) first or least significant bit (LSB) first serial I/O formats (see Table 22, Serial I/O Control Registers (sioc and sioc2)). A multiprocessor I/O configuration is supported. This feature allows up to eight DSP161X devices to be connected together on an SIO port without requiring external glue logic.

The serial data may be internally looped back by setting the SIO loopback control bit, SIOLBC, of the ioc register. SIOLBC affects both the SIO and SIO2. The data output signals are wrapped around internally from the output to the input (DO1 to DI1 and DO2 to DI2). To exercise loopback, the SIO clocks (ICK1, ICK2, OCK1, and OCK2) should either all be in the active mode, 16-bit condition, or each pair should be driven from one external source in passive mode. Similarly, pins ILD1 (ILD2) and OLD1 (OLD2) must both be in active mode or tied together and driven from one external frame clock in passive mode. During loopback, DO1, DO2, DI1, DI2, ICK1, ICK2, OCK1, OCK2, ILD1, ILD2, OLD1, OLD2, SADD1, SADD2, SYNC1, SYNC2, DOEN1, and DOEN2 are 3-stated.

Setting DODLY = 1 (sioc and sioc2) delays DO by one phase of OCK so that DO changes on the falling edge of OCK instead of the rising edge (DODLY = 0). This reduces the time available for DO to drive DI and to be valid for the rising edge of ICK, but increases the hold time on DO by half a cycle on OCK.

### **Programmable Modes**

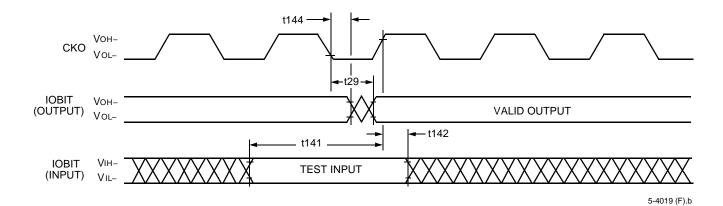

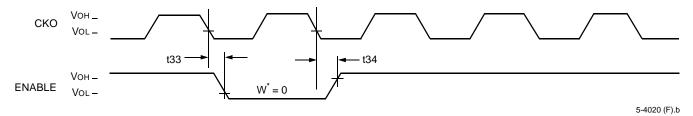

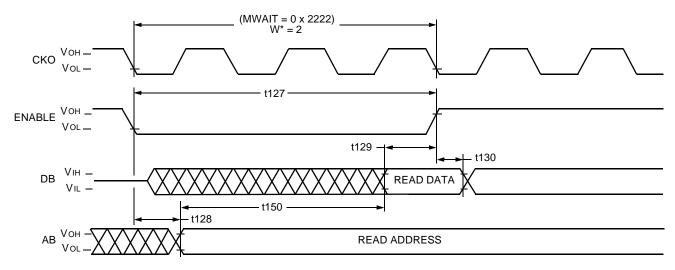

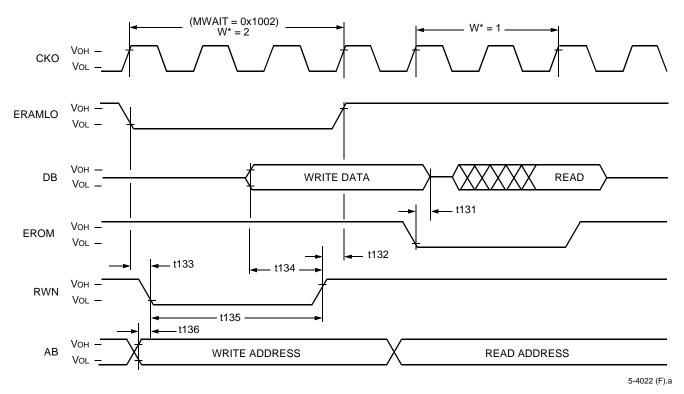

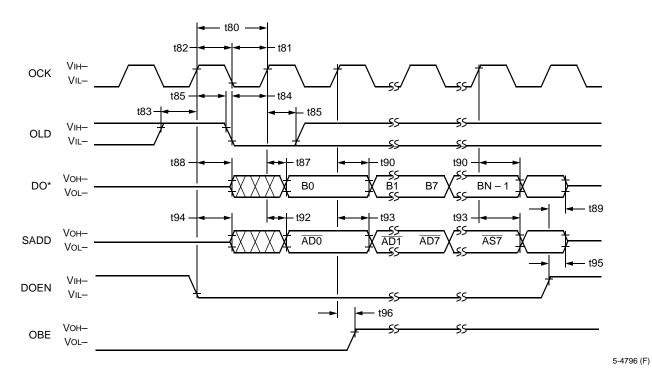

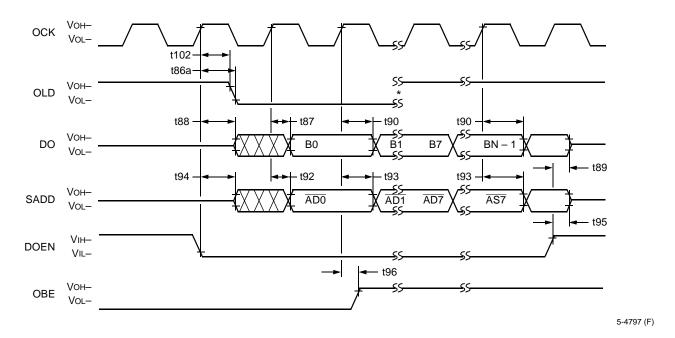

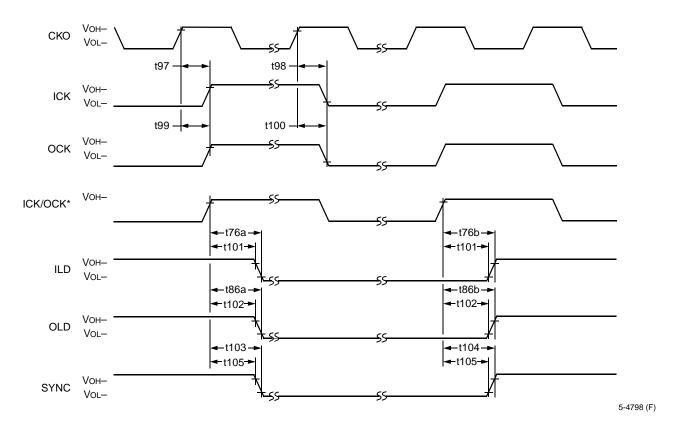

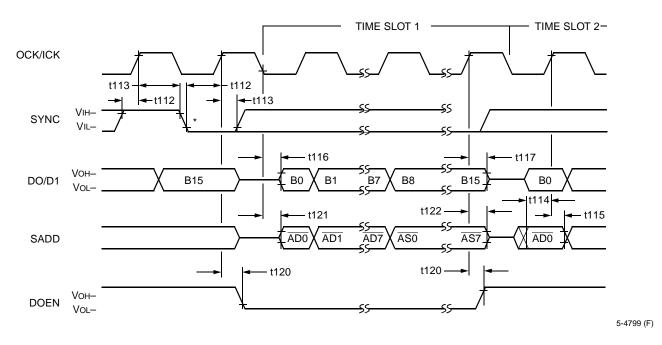

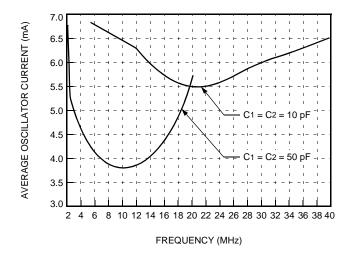

Programmable modes of operation for the SIO and SIO2 are controlled by the serial I/O control registers (sioc and sioc2). These registers, shown in Table 22, are used to set the ports into various configurations. Both input and output operations can be independently configured as either active or passive. When active, the DSP1627 generates load and clock signals. When passive, load and clock signal pins are inputs.