Order Number EB346/D: Rev. 2 4/20/2001

# Functional Differences Between DSP56302 and DSP56309 (formerly DSP56302A)

# 1 Purpose of this Document

To meet the increasing demands for higher performance and lower power consumption, an advanced DSP56302 has been designed; it is was formerly known as DSP302A; it is now designated DSP56309. The new part is designed to be a functional replacement for the DSP56302. This document summarizes the differences between the DSP56302 and the DSP56309.

## 2 Differences Overview

The primary functional differences between the DSP56302 and the DSP56309 are due to inherent differences between the two design technologies. **Table 1.** compares the two chips.

## Contents

| 1 | Purpose of this Document                  | 1 |

|---|-------------------------------------------|---|

| 2 | Differences Overview                      | 1 |

|   | Input Power Changes                       |   |

|   | I/O Power Changes                         |   |

|   | PLL Input Capacitor (C <sub>PCAP</sub> ). |   |

|   | Operating Modes                           |   |

Table 1. Functional Comparison of DSP56302 and DSP56309

| Feature                                        | DSP56302                                                                                                                                                                            | DSP56309                                                                                                                                                                                                                                                                               |  |  |  |

|------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Operating frequency                            | ≤ 66 MHz down to 0 Hz                                                                                                                                                               | ≤ 100 MHz down to 0 Hz                                                                                                                                                                                                                                                                 |  |  |  |

| Technology                                     | 0.5 micron                                                                                                                                                                          | Sub 0.4 micron                                                                                                                                                                                                                                                                         |  |  |  |

| Input power                                    | V <sub>CC</sub> = 3.0-3.6 V combined core and I/O power and ground                                                                                                                  | Split power: Core V <sub>CC</sub> (3.0–3.6 V currently) I/O V <sub>CC</sub> (3.0–3.6 V currently) A pinout change is required to support the split power configuration. See <b>Section 3</b> for more information and a description of the pinout change for the 144-pin TQFP package. |  |  |  |

| I/O pins                                       | 5 V tolerant (exceptions: see data sheet)                                                                                                                                           | Tolerant up to 3.6 V                                                                                                                                                                                                                                                                   |  |  |  |

| Package                                        | 144-pin TQFP                                                                                                                                                                        | 144-pin TQFP or 196-pin PBGA                                                                                                                                                                                                                                                           |  |  |  |

| PLL input<br>capacitor<br>(C <sub>PCAP</sub> ) | Uses the following rules:<br>For MF $\leq$ 4:<br>$C_{PCAP} = [(500 \times MF) - 150] pF$<br>For MF > 4:<br>$C_{PCAP} = (690 \times MF) pF$                                          | Uses the following rules:<br>For MF $\leq$ 4:<br>$C_{PCAP} = [(680 \times MF) - 120] pF$<br>For MF > 4:<br>$C_{PCAP} = (1100 \times MF) pF$                                                                                                                                            |  |  |  |

| Operating modes                                |                                                                                                                                                                                     | See <b>Table 3</b> for details.                                                                                                                                                                                                                                                        |  |  |  |

| Other functionality                            | All memory, control functions, and peripherals are identical. Refer to the <i>DSP56309 Technical Data Sheet</i> (order by DSP56309/D) for a detailed description of these features. |                                                                                                                                                                                                                                                                                        |  |  |  |

# 3 Input Power Changes

One method to increase the operating frequency of an integrated circuit is to "shrink" the die (that is, reduce the die dimensions, both linearly and vertically). Reducing the die size can yield additional benefits, such as a reduction of power consumption, but can also result in other functional changes. The DSP56309 is a "shrink" of the DSP56302. This die size reduction enables the DSP56309 to achieve higher operating frequencies. Decreasing the die size, however, requires a reduction of the thickness of the oxide dielectrics, which also reduces the maximum allowable voltages across some oxides within the die. To support future "shrinks" of the DSP56309 while maximizing system level compatibility, Motorola has elected to separate the power supply networks on the die. This split allows the I/O pins to operate over a voltage range which is different from that used by the core digital logic. Although the initial release of this product specifies the same voltage ranges for the I/O pins and the core logic, future versions of the DSP56309 or its derivatives are likely to have reduced core logic V<sub>CC</sub> requirements (for example, 2.5 V and lower voltages) while the I/O levels use a higher level (for example, 3.3 V). This allows Motorola to continue aggressively to "shrink" the device, while preserving the ability to maintain system level compatibility.

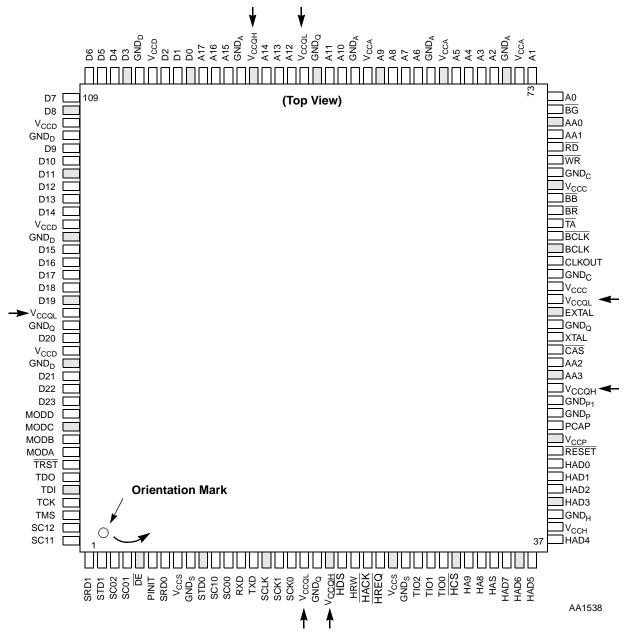

The split-power design requires a modification in the chip pinout. A top view of the DSP56309 TQFP package is shown in **Figure 1**. **Table 2** lists the pin differences between the DSP56302 and the DSP56309.

Note:

The power input for the core logic is designated  $V_{CCQ}$  for the DSP56302. For the DSP56309, the independent core logic input voltage is designated  $V_{CCQL}$ , while the independent I/O input voltage is designated  $V_{CCQH}$ .  $V_{CCQL}$  should be connected to the core input power supply.  $V_{CCQH}$  and all other input power ( $V_{CCA}$ ,  $V_{CCC}$ ,  $V_{CCD}$ ,  $V_{CCH}$ ,  $V_{CCP}$ , and  $V_{CCS}$ ) should be connected to the external input power supply.

Note: Arrows (→) indicate the pins that are different from the DSP56302, as listed in **Table 2**. on page 4.

Figure 1. DSP56309 Thin Quad Flat Pack (TQFP), Top View

Table 2. Pin Differences between DSP56302 and DSP56309 (144-pin TQFP package)

| Pin                                                                                                                                                                                                                     | Pin Name         |                   |  |  |  |  |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|-------------------|--|--|--|--|--|--|

| ""                                                                                                                                                                                                                      | DSP56302         | DSP56309          |  |  |  |  |  |  |

| 18                                                                                                                                                                                                                      | V <sub>CCQ</sub> | V <sub>CCQL</sub> |  |  |  |  |  |  |

| 20                                                                                                                                                                                                                      | NC               | V <sub>CCQH</sub> |  |  |  |  |  |  |

| 49                                                                                                                                                                                                                      | NC               | V <sub>CCQH</sub> |  |  |  |  |  |  |

| 56                                                                                                                                                                                                                      | V <sub>CCQ</sub> | V <sub>CCQL</sub> |  |  |  |  |  |  |

| 91                                                                                                                                                                                                                      | V <sub>CCQ</sub> | V <sub>CCQL</sub> |  |  |  |  |  |  |

| 95                                                                                                                                                                                                                      | V <sub>CCA</sub> | V <sub>ССQН</sub> |  |  |  |  |  |  |

| 126                                                                                                                                                                                                                     | V <sub>CCQ</sub> | V <sub>CCQL</sub> |  |  |  |  |  |  |

| $V_{CCQ}$ = input voltage for core logic $V_{CCQL}$ = independent input voltage for core logic $NC$ = not connected $V_{CCQH}$ = independent input voltage for I/O lines $V_{CCA}$ = voltage for external address lines |                  |                   |  |  |  |  |  |  |

A pinout for the 196-pin PBGA package is included in the DSP56309 Technical Data Sheet. This package will include the split power configuration described for the 144-pin TQFP package.

Unlisted pins are the same for both chips.

# 4 I/O Power Changes

The DSP56302 supports 5 V inputs for its peripherals. Complete requirements are described in the DSP56302 Technical Data Sheet.

The DSP56309 supports 3.3 V inputs. Detailed voltage requirements are included in the DSP56309 Technical Data Sheet.

# 5 PLL Input Capacitor (C<sub>PCAP</sub>)

The process change results in a changed requirement for computing the size of  $C_{PCAP}$ , the capacitor used with the PCAP input. **Table 1** lists the new formulas for computing the value of this input capacitor for the DSP56309.

# 6 Operating Modes

The operating modes of the DSP56302 are documented in the DSP56302 User's Manual. **Table 3.** documents the operating modes of the DSP56309. Modes that differ from those of the DSP56302 are highlighted in the table.

Table 3. DSP56309 Operating Modes

| Mode | MODD | MODC | MODB | MODA | Reset Vector | Description                                 |

|------|------|------|------|------|--------------|---------------------------------------------|

| 0    | 0    | 0    | 0    | 0    | \$C00000     | Expanded mode                               |

| 1    | 0    | 0    | 0    | 1    | \$FF0000     | Reserved                                    |

| 2    | 0    | 0    | 1    | 0    | \$FF0000     | Reserved                                    |

| 3    | 0    | 0    | 1    | 1    | \$FF0000     | Reserved                                    |

| 4    | 0    | 1    | 0    | 0    | \$FF0000     | Reserved                                    |

| 5    | 0    | 1    | 0    | 1    | \$FF0000     | Reserved                                    |

| 6    | 0    | 1    | 1    | 0    | \$FF0000     | Reserved                                    |

| 7    | 0    | 1    | 1    | 1    | \$FF0000     | Reserved                                    |

| 8    | 1    | 0    | 0    | 0    | \$008000     | Expanded mode                               |

| 9    | 1    | 0    | 0    | 1    | \$FF0000     | Boot from byte-wide memory                  |

| Α    | 1    | 0    | 1    | 0    | \$FF0000     | Boot from SCI                               |

| В    | 1    | 0    | 1    | 1    | \$FF0000     | Reserved                                    |

| С    | 1    | 1    | 0    | 0    | \$FF0000     | HI08 bootstrap in ISA mode                  |

| D    | 1    | 1    | 0    | 1    | \$FF0000     | HI08 bootstrap in HC11 non-multiplexed mode |

| Е    | 1    | 1    | 1    | 0    | \$FF0000     | HI08 bootstrap in 8051 multiplexed bus mode |

| F    | 1    | 1    | 1    | 1    | \$FF0000     | HI08 bootstrap in MC68302 mode              |

OnCE, DigitalDNA, and the DigitalDNA logo are trademarks of Motorola, Inc.

Motorola reserves the right to make changes without further notice to any products herein. Motorola makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Motorola assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters which may be provided in Motorola data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. Motorola does not convey any license under its patent rights nor the rights of others. Motorola products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support life, or for any other application in which the failure of the Motorola product could create a situation where personal injury or death may occur. Should Buyer purchase or use Motorola products for any such unintended or unauthorized application, Buyer shall indemnify and hold Motorola and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Motorola was negligent regarding the design or manufacture of the part. Motorola and was negligent regarding the design or manufacture of the part. Motorola and was negligent regarding the design or manufacture of the part. Motorola

#### How to reach us:

#### USA/EUROPE Motorola Literature Distribution

P.O. Box 5405 Denver, Colorado 80217 1-303-675-2140 1-800-441-2447

## Technical InformationCenter 1-800-521-6274

**JAPAN**

Motorola Japan Ltd. SPS, Technical Information Center 3-20-1, Minami-Azabu, Minato-ku Tokyo 106-8573 Japan 81-3-3440-3569

#### ASIA/PACIFIC

Motorola Semiconductors H.K. Ltd. Silicon Harbour Centre 2 Dai King Street Tai Po Industrial Estate Tai Po, N.T., Hong Kong 852-26668334

#### Home Page

http://www.mot.com/SPS/DSP

#### DSP Helpline

http://www.motorola-dsp.com/contact email: dsphelp@dsp.sps.mot.com