Is Now Part of

# **ON Semiconductor**®

# To learn more about ON Semiconductor, please visit our website at <u>www.onsemi.com</u>

Please note: As part of the Fairchild Semiconductor integration, some of the Fairchild orderable part numbers will need to change in order to meet ON Semiconductor's system requirements. Since the ON Semiconductor product management systems do not have the ability to manage part nomenclature that utilizes an underscore (\_), the underscore (\_) in the Fairchild part numbers will be changed to a dash (-). This document may contain device numbers with an underscore (\_). Please check the ON Semiconductor website to verify the updated device numbers. The most current and up-to-date ordering information can be found at <a href="https://www.onsemi.com">www.onsemi.com</a>. Please email any questions regarding the system integration to <a href="https://www.onsemi.com">Fairchild\_questions@onsemi.com</a>.

ON Semiconductor and the ON Semiconductor logo are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of ON Semiconductor's product/patent coverage may be accessed at www.onsemi.com/site/pdf/Patent-Marking.pdf. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using ON Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. ON Semiconductor does not convey any license under its patent rights of others. ON Semiconductor products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or unavteries, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out or i, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that ON Semiconductor was negligent regarding the design or manufacture of the part. ON Semiconductor and is officers, employees, weni four charmane may manner.

## FL7930B Single-Stage Flyback and Boundary-Mode PFC Controller for Lighting

#### Features

- Additional OVP Detection Pin

- V<sub>IN</sub>-Absent Detection

- Maximum Switching Frequency Limitation

- Internal Soft-Start and Startup without Overshoot

- Internal Total Harmonic Distortion (THD) Optimizer

- Precise Adjustable Output Over-Voltage Protection

- Open-Feedback Protection and Disable Function

- Zero Current Detector (ZCD)

- 150 µs Internal Startup Timer

- MOSFET Over-Current Protection (OCP)

- Under-Voltage Lockout with 3.5 V Hysteresis

- Low Startup and Operating Current

- Totem-Pole Output with High State Clamp

- +500/-800 mA Peak Gate Drive Current

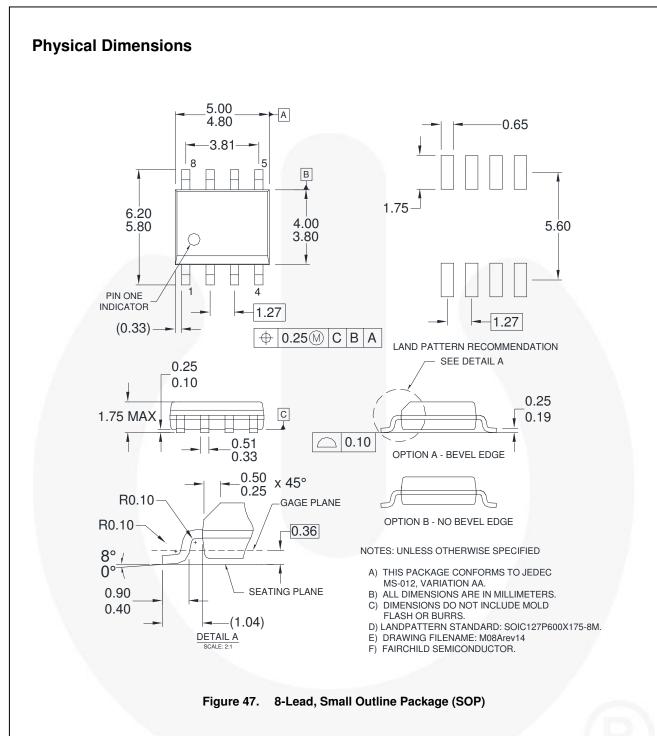

- 8-Pin, Small-Outline Package (SOP)

### **Applications**

- Ballast

- General LED Lighting

- Industrial, Commercial, and Residential Fixtures

- Outdoor Lighting: Street, Roadway, Parking, Construction, Ornamental LED Lighting Fixtures

### Description

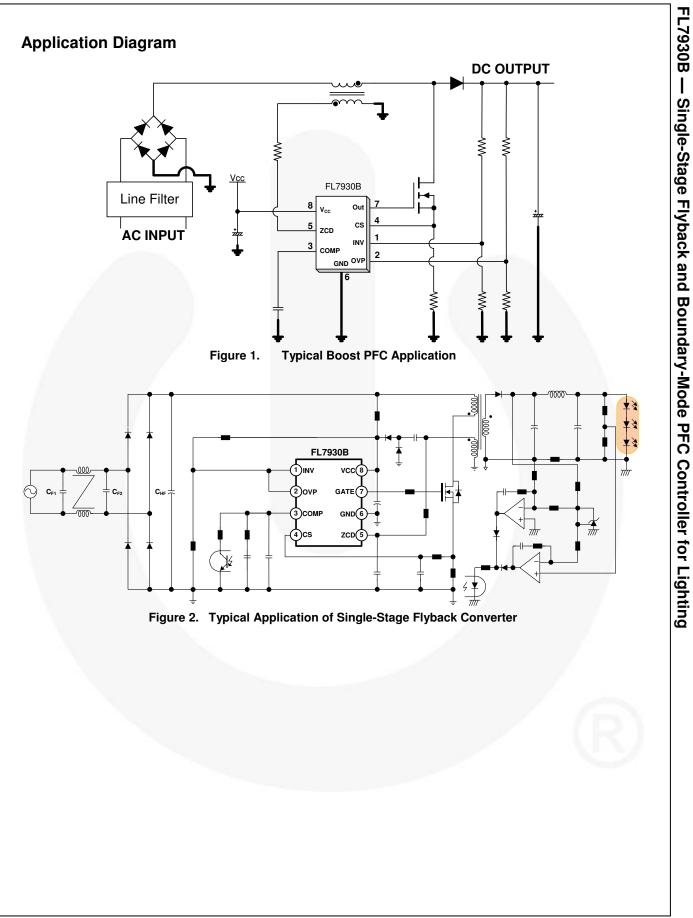

The FL7930B is an active power factor correction (PFC) controller for boost PFC applications that operate in critical conduction mode (CRM). It uses a voltage-mode PWM that compares an internal ramp signal with the error amplifier output to generate a MOSFET turn-off signal. Because the voltage-mode CRM PFC controller does not need rectified AC line voltage information, it saves the power loss of an input voltage sensing network necessary for a current-mode CRM PFC controller.

FL7930B provides over-voltage protection (OVP), openfeedback protection, over-current protection (OCP), input-voltage-absent detection, and under-voltage lockout protection (UVLO). The additional OVP pin can be used to shut down the boost power stage when output voltage exceeds OVP level due to the resistors that are connected at INV pin are damaged. The FL7930B can be disabled if the INV pin voltage is lower than 0.45 V and the operating current decreases to a very low level. Using a new variable on-time control method, total harmonic distortion (THD) is lower than in conventional CRM boost PFC ICs.

| Ordering Information |                                |          |                                    |                   |  |  |

|----------------------|--------------------------------|----------|------------------------------------|-------------------|--|--|

| Part Number          | Operating<br>Temperature Range | Top Mark | Package                            | Packing<br>Method |  |  |

| FL7930BMX_G          | -40 to +125°C                  | FL7930BG | 8-Lead Small Outline Package (SOP) | Tape & Reel       |  |  |

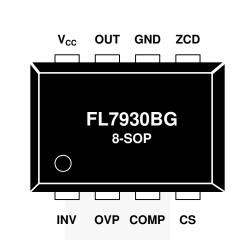

Figure 4. Pin Configuration (Top View)

### **Pin Definitions**

**Pin Configuration**

| Pin #                                                                                                                                                                                                           | Name                                                                                                                                                                                                                                       | Description                                                                                                                                                              |  |  |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 1                                                                                                                                                                                                               | 1 INV This pin is the inverting input of the error amplifier. The output voltage of the boost PFC conversion should be resistively divided to 2.5 V.                                                                                       |                                                                                                                                                                          |  |  |  |  |

| 2                                                                                                                                                                                                               | OVP                                                                                                                                                                                                                                        | This pin is used to detect PFC output over voltage when INV pin information is not correct.                                                                              |  |  |  |  |

| 3                                                                                                                                                                                                               | COMP This pin is the output of the transconductance error amplifier. Components for the output voltage compensation should be connected between this pin and GND.                                                                          |                                                                                                                                                                          |  |  |  |  |

| 4                                                                                                                                                                                                               | 4 CS This pin is the input of the over-current protection comparator. The MOSFET current is sensed using a sensing resistor and the resulting voltage is applied to this pin. An internal RC filter is included to filter switching noise. |                                                                                                                                                                          |  |  |  |  |

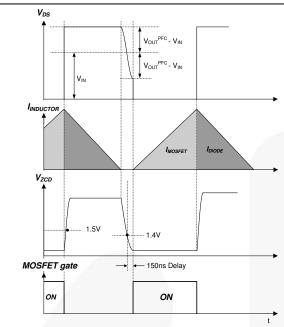

| 5                                                                                                                                                                                                               | ZCD                                                                                                                                                                                                                                        | This pin is the input of the zero-current detection (ZCD) block. If the voltage of this pin goes higher than 1.5 V, then goes lower than 1.4 V, the MOSFET is turned on. |  |  |  |  |

| 6                                                                                                                                                                                                               | GND                                                                                                                                                                                                                                        | This pin is used for the ground potential of all the pins. For proper operation, the signal ground and the power ground should be separated.                             |  |  |  |  |

| 7 OUT This pin is the gate drive output. The peak sourcing and sinking current levels are +500 mA<br>-800 mA, respectively. For proper operation, the stray inductance in the gate driving path m<br>minimized. |                                                                                                                                                                                                                                            |                                                                                                                                                                          |  |  |  |  |

| 8                                                                                                                                                                                                               | V <sub>CC</sub>                                                                                                                                                                                                                            | This is the IC supply pin. IC current and MOSFET drive current are supplied using this pin.                                                                              |  |  |  |  |

### **Absolute Maximum Ratings**

Stresses exceeding the absolute maximum ratings may damage the device. The device may not function or be operable above the recommended operating conditions and stressing the parts to these levels is not recommended. In addition, extended exposure to stresses above the recommended operating conditions may affect device reliability. The absolute maximum ratings are stress ratings only.

| Symbol                            | P                                 | arameter                                                  | Min.  | Max. | Unit |

|-----------------------------------|-----------------------------------|-----------------------------------------------------------|-------|------|------|

| V <sub>CC</sub>                   | Supply Voltage                    |                                                           |       | Vz   | V    |

| I <sub>OH</sub> , I <sub>OL</sub> | Peak Drive Output Current         |                                                           | -800  | +500 | mA   |

| ICLAMP                            | Driver Output Clamping Diodes \   | / <sub>0</sub> >V <sub>CC</sub> or V <sub>0</sub> <-0.3 V | -10   | +10  | mA   |

| I <sub>DET</sub>                  | Detector Clamping Diodes          |                                                           | -10   | +10  | mA   |

| M                                 | Error Amplifier Input, Output, OV | P Input, ZCD, RDY, and OVP Pins <sup>(1)</sup>            | -0.3  | 8.0  | v    |

| V <sub>IN</sub>                   | CS Input Voltage <sup>(2)</sup>   |                                                           | -10.0 | 6.0  | v    |

| TJ                                | Operating Junction Temperature    |                                                           |       | +150 | °C   |

| TA                                | Operating Temperature Range       |                                                           | -40   | +125 | °C   |

| T <sub>STG</sub>                  | Storage Temperature Range         |                                                           | -65   | +150 | °C   |

| ESD                               | Electrostatic Discharge           | Human Body Model, JESD22-A114                             |       | 2.5  | kV   |

| ESD                               | Capability                        | Charged Device Model, JESD22-C101                         |       | 2.0  | ĸν   |

#### Notes:

1. When this pin is supplied by external power sources by accident, its maximum allowable current is 50 mA.

2. In case of DC input, the acceptable input range is -0.3 V~6 V: within 100 ns -10 V~6 V is acceptable, but electrical specifications are not guaranteed during such a short time.

### Thermal Impedance

| Symbol        | Parameter                                              | Min. | Max. | Unit |

|---------------|--------------------------------------------------------|------|------|------|

| $\Theta_{JA}$ | Thermal Resistance, Junction-to-Ambient <sup>(3)</sup> | 150  |      | °C/W |

Note:

3. Regarding the test environment and PCB type, please refer to JESD51-2 and JESD51-10.

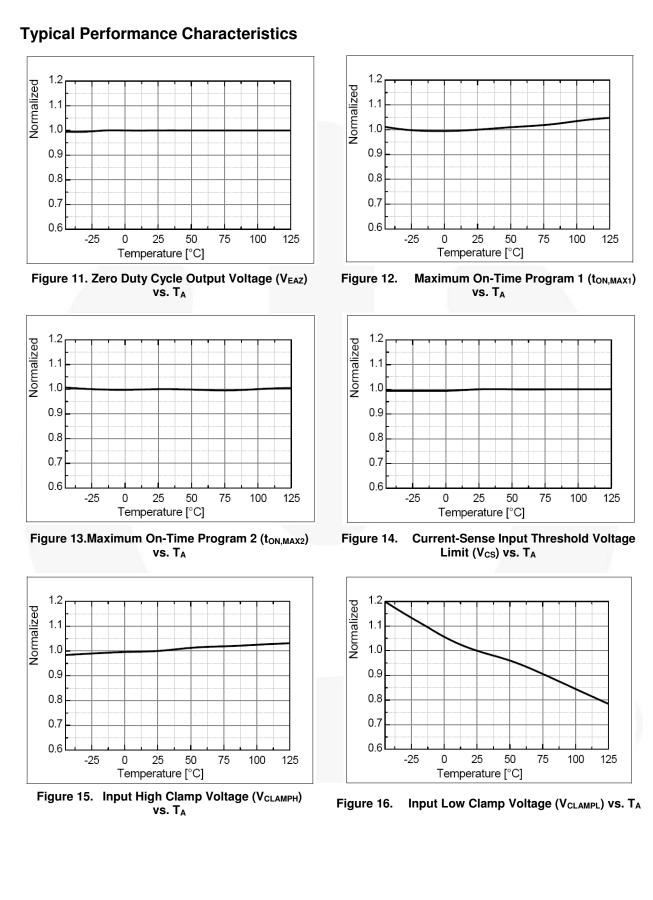

### **Electrical Characteristics**

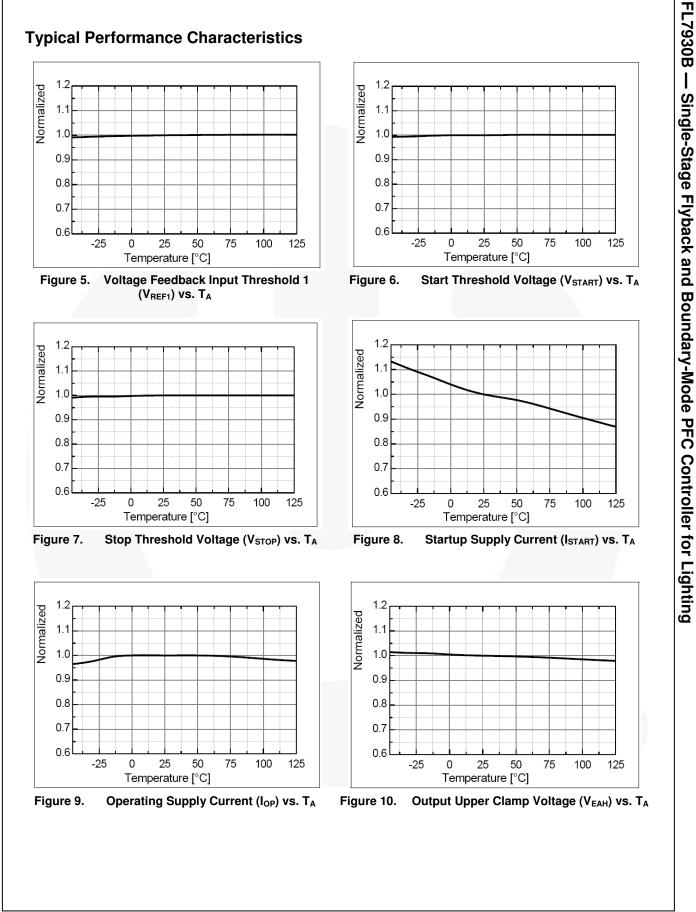

$V_{CC}$  = 14 V and  $T_A$  = -40°C~+125°C, unless otherwise specified.

| Symbol                  | Parameter                                                 | Conditions                                                                 | Min.  | Тур.  | Max.  | Unit |

|-------------------------|-----------------------------------------------------------|----------------------------------------------------------------------------|-------|-------|-------|------|

| V <sub>cc</sub> Section |                                                           |                                                                            |       |       |       |      |

| VSTART                  | Start Threshold Voltage                                   | V <sub>CC</sub> Increasing                                                 | 11    | 12    | 13    | V    |

| V <sub>STOP</sub>       | Stop Threshold Voltage                                    | V <sub>CC</sub> Decreasing                                                 | 7.5   | 8.5   | 9.5   | V    |

| $HY_{UVLO}$             | UVLO Hysteresis                                           |                                                                            | 3.0   | 3.5   | 4.0   | V    |

| Vz                      | Zener Voltage                                             | I <sub>CC</sub> =20 mA                                                     | 20    | 22    | 24    | V    |

| V <sub>OP</sub>         | Recommended Operating Range                               |                                                                            | 13    |       | 20    | V    |

| Supply Curr             | rent Section                                              |                                                                            |       |       |       |      |

| I <sub>START</sub>      | Startup Supply Current                                    | $V_{CC}=V_{START}$ -0.2 V                                                  |       | 120   | 190   | μA   |

| I <sub>OP</sub>         | Operating Supply Current                                  | Output Not Switching                                                       | 1     | 1.5   | 3.0   | mA   |

| I <sub>DOP</sub>        | Dynamic Operating Supply Current                          | 50 kHz, C <sub>I</sub> =1 nF                                               |       | 2.5   | 4.0   | mA   |

| I <sub>OPDIS</sub>      | Operating Current at Disable                              | V <sub>INV</sub> =0 V                                                      | 90    | 160   | 230   | μA   |

| Error Ampli             | fier Section                                              |                                                                            |       |       |       |      |

| V <sub>REF1</sub>       | Voltage Feedback Input Threshold1                         | T <sub>A</sub> =25°C                                                       | 2.465 | 2.500 | 2.535 | V    |

| $\Delta V_{REF1}$       | Line Regulation                                           | V <sub>CC</sub> =14 V~20 V                                                 |       | 0.1   | 10.0  | mV   |

| $\Delta V_{REF2}$       | Temperature Stability of V <sub>REF1</sub> <sup>(4)</sup> |                                                                            |       | 20    |       | mV   |

| I <sub>EA,BS</sub>      | Input Bias Current                                        | V <sub>INV</sub> =1 V~4 V                                                  | -0.5  |       | 0.5   | μA   |

| I <sub>EAS,SR</sub>     | Output Source Current                                     | V <sub>INV</sub> =V <sub>REF</sub> -0.1 V                                  |       | -12   |       | μA   |

| I <sub>EAS,SK</sub>     | Output Sink Current                                       | V <sub>INV</sub> =V <sub>REF</sub> +0.1 V                                  |       | 12    |       | μA   |

| $V_{EAH}$               | Output Upper Clamp Voltage                                | $V_{INV}=1 V, V_{CS}=0 V$                                                  | 6.0   | 6.5   | 7.0   | V    |

| $V_{EAZ}$               | Zero Duty Cycle Output Voltage                            |                                                                            | 0.9   | 1.0   | 1.1   | V    |

| g <sub>m</sub>          | Transconductance <sup>(4)</sup>                           |                                                                            | 90    | 115   | 140   | μmho |

| Maximum O               | n-Time Section                                            |                                                                            |       |       |       |      |

| t <sub>ON,MAX1</sub>    | Maximum On-Time Programming 1                             | $T_A=25^{\circ}C, V_{ZCD}=1 V$                                             | 35.5  | 41.5  | 47.5  | μs   |

| t <sub>on,max2</sub>    | Maximum On-Time Programming 2                             | $\begin{array}{l} T_A=25^{\circ}C,\\ I_{ZCD}=0.469 \text{ mA} \end{array}$ | 11.2  | 13.0  | 14.8  | μs   |

| Current-Ser             | se Section                                                |                                                                            |       |       |       |      |

| V <sub>CS</sub>         | Current Sense Input Threshold<br>Voltage Limit            |                                                                            | 0.7   | 0.8   | 0.9   | V    |

| I <sub>CS,BS</sub>      | Input Bias Current                                        | V <sub>CS</sub> =0~1 V                                                     | -1.0  | -0.1  | 1.0   | μA   |

| t <sub>CS,D</sub>       | Current Sense Delay to Output <sup>(4)</sup>              | dV/dt=1 V/100 ns,<br>from 0 V to 5 V                                       |       | 350   | 500   | ns   |

Continued on the following page ...

### **Electrical Characteristics**

$V_{CC}$  = 14 V and  $T_A$  = -40°C~+125°C, unless otherwise specified.

| Symbol                | Parameter                                               | Conditions                                    | Min.  | Тур.  | Max.  | Unit |

|-----------------------|---------------------------------------------------------|-----------------------------------------------|-------|-------|-------|------|

| Zero-Cur              | rent Detect Section                                     |                                               |       |       |       |      |

| V <sub>ZCD</sub>      | Input Voltage Threshold <sup>(4)</sup>                  |                                               | 1.35  | 1.50  | 1.65  | V    |

| HY <sub>ZCD</sub>     | Detect Hysteresis <sup>(4)</sup>                        |                                               | 0.05  | 0.10  | 0.15  | V    |

| V <sub>CLAMPH</sub>   | Input High Clamp Voltage                                | I <sub>DET</sub> =3 mA                        | 5.5   | 6.2   | 7.5   | V    |

| V <sub>CLAMPL</sub>   | Input Low Clamp Voltage                                 | I <sub>DET</sub> =-3 mA                       | 0     | 0.65  | 1.00  | V    |

| I <sub>ZCD,BS</sub>   | Input Bias Current                                      | V <sub>ZCD</sub> =1 V~5 V                     | -1.0  | -0.1  | 1.0   | μA   |

| I <sub>ZCD,SR</sub>   | Source Current Capability <sup>(4)</sup>                | T <sub>A</sub> =25°C                          |       |       | -4    | mA   |

| I <sub>ZCD,SK</sub>   | Sink Current Capability <sup>(4)</sup>                  | T <sub>A</sub> =25°C                          |       |       | 10    | mA   |

| t <sub>ZCD,D</sub>    | Maximum Delay From ZCD to Output Turn-On <sup>(4)</sup> | dV/dt=-1 V/100 ns, from<br>5 V to 0 V         | 100   |       | 200   | ns   |

| Output S              | ection                                                  |                                               |       |       |       |      |

| V <sub>OH</sub>       | Output Voltage High                                     | I <sub>O</sub> =-100 mA, T <sub>A</sub> =25°C | 9.2   | 11.0  | 12.8  | V    |

| V <sub>OL</sub>       | Output Voltage Low                                      | I <sub>O</sub> =200 mA, T <sub>A</sub> =25°C  |       | 1.0   | 2.5   | V    |

| t <sub>RISE</sub>     | Rising Time <sup>(4)</sup>                              | C <sub>IN</sub> =1 nF                         |       | 50    | 100   | ns   |

| t <sub>FALL</sub>     | Falling Time <sup>(4)</sup>                             | C <sub>IN</sub> =1 nF                         |       | 50    | 100   | ns   |

| V <sub>O,MAX</sub>    | Maximum Output Voltage                                  | V <sub>CC</sub> =20 V, I <sub>O</sub> =100 μA | 11.5  | 13.0  | 14.5  | V    |

| V <sub>O,UVLO</sub>   | Output Voltage with UVLO Activated                      | V <sub>CC</sub> =5 V, I <sub>O</sub> =100 μA  |       |       | 1     | V    |

| Restart /             | Maximum Switching Frequency Limit                       | Section                                       |       |       |       |      |

| t <sub>RST</sub>      | Restart Timer Delay                                     |                                               | 50    | 150   | 300   | μs   |

| f <sub>MAX</sub>      | Maximum Switching Frequency <sup>(4)</sup>              |                                               | 250   | 300   | 350   | kHz  |

| Soft-Star             | t Timer Section                                         |                                               |       |       |       |      |

| t <sub>ss</sub>       | Internal Soft-Soft <sup>(4)</sup>                       |                                               | 3     | 5     | 7     | ms   |

| Protectio             | ns                                                      |                                               | •     |       |       |      |

| V <sub>OVP,INV</sub>  | OVP Threshold Voltage at INV Pin                        | T <sub>A</sub> =25°C                          | 2.620 | 2.675 | 2.730 | V    |

| HY <sub>OVP,INV</sub> | OVP Hysteresis at INV Pin                               | T <sub>A</sub> =25°C                          | 0.120 | 0.175 | 0.230 | V    |

| V <sub>OVP,OVP</sub>  | OVP Threshold Voltage at OVP Pin                        | T <sub>A</sub> =25°C                          | 2.740 | 2.845 | 2.960 | V    |

| HY <sub>OVP,OVP</sub> | OVP Hysteresis at OVP Pin                               | T <sub>A</sub> =25°C                          |       | 0.345 |       | V    |

| V <sub>EN</sub>       | Enable Threshold Voltage                                |                                               | 0.40  | 0.45  | 0.50  | V    |

| $HY_{\text{EN}}$      | Enable Hysteresis                                       |                                               | 0.05  | 0.10  | 0.15  | V    |

| $T_{SD}$              | Thermal Shutdown Temperature <sup>(4)</sup>             |                                               | 125   | 140   | 155   | °C   |

| T <sub>HYS</sub>      | Hysteresis Temperature of TSD <sup>(4)</sup>            |                                               |       | 60    |       | °C   |

#### Note:

4. These parameters, although guaranteed by design, are not production tested.

| Function                          | FL6961   | FL7930B         | FL7930B Advantages                                                                            |

|-----------------------------------|----------|-----------------|-----------------------------------------------------------------------------------------------|

|                                   |          |                 | No External Circuit for additional OVP                                                        |

| OVP Pin                           | None     | Integrated      | <ul> <li>Reduction of Power Loss and BOM Cost Caused by<br/>Additional OVP Circuit</li> </ul> |

|                                   |          |                 | Abnormal CCM Operation Prohibited                                                             |

| Frequency Limit                   | None     | Integrated      | <ul> <li>Abnormal Inductor Current Accumulation Can Be<br/>Prohibited</li> </ul>              |

|                                   | News     | late mate d     | <ul> <li>Increase System Reliability by Testing for Input Supply<br/>Voltage</li> </ul>       |

| V <sub>IN</sub> -Absent Detection | None     | Integrated      | <ul> <li>Guarantee Stable Operation at Short Electric Power<br/>Failure</li> </ul>            |

| Soft-Start and                    |          |                 | <ul> <li>Reduce Voltage and Current Stress at Startup</li> </ul>                              |

| Startup without<br>Overshoot      | None     | Integrated      | <ul> <li>Eliminate Audible Noise Due to Unwanted OVP<br/>Triggering</li> </ul>                |

| Control Range                     | News     | late mate d     | <ul> <li>Can Avoid Burst Operation at Light Load and High Input<br/>Voltage</li> </ul>        |

| Compensation                      | None     | Integrated      | <ul> <li>Reduce Probability of Audible Noise Due to Burst<br/>Operation</li> </ul>            |

| THD Optimizer                     | External | Internal        | No External Resistor is Needed                                                                |

| TOD                               | News     | 140°C with      | Stable and Reliable TSD Operation                                                             |

| TSD                               | None     | 60°C Hysteresis | Converter Temperature Range Limited Range                                                     |

| Control Range<br>Compensation     | None     | Integrated      |                                                                                               |

### Comparison of FL6961 and FL7930B

### Comparison of FL7930B and FL7930C

| Function | FL7930B    | FL7930C    | FL7930B Remark                           |

|----------|------------|------------|------------------------------------------|

| RDY Pin  | None       | Integrated | User Choice for the Use of Number #2 Pin |

| OVP Pin  | Integrated | None       |                                          |

### **Applications Information**

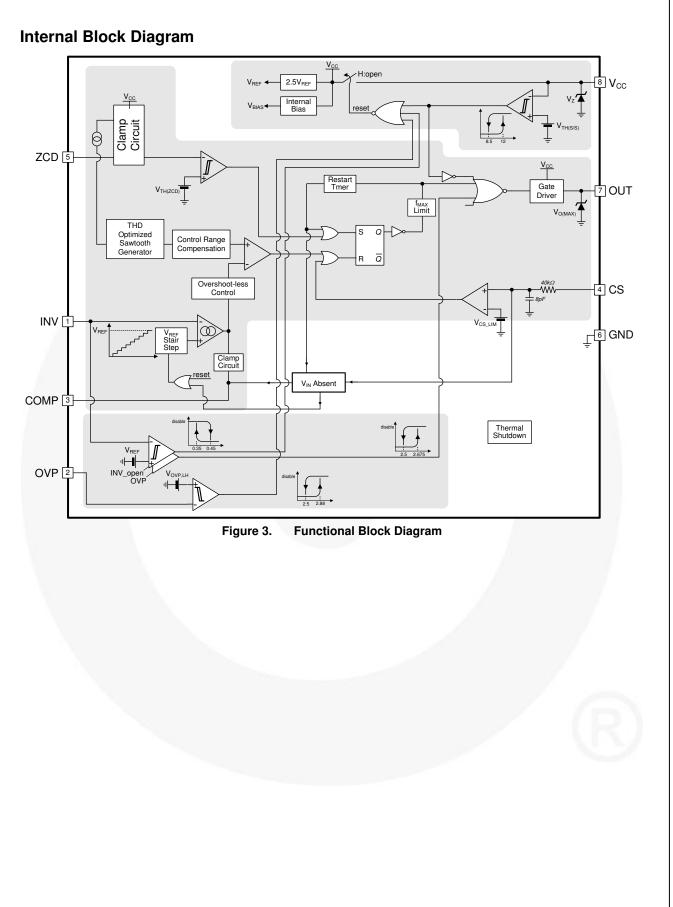

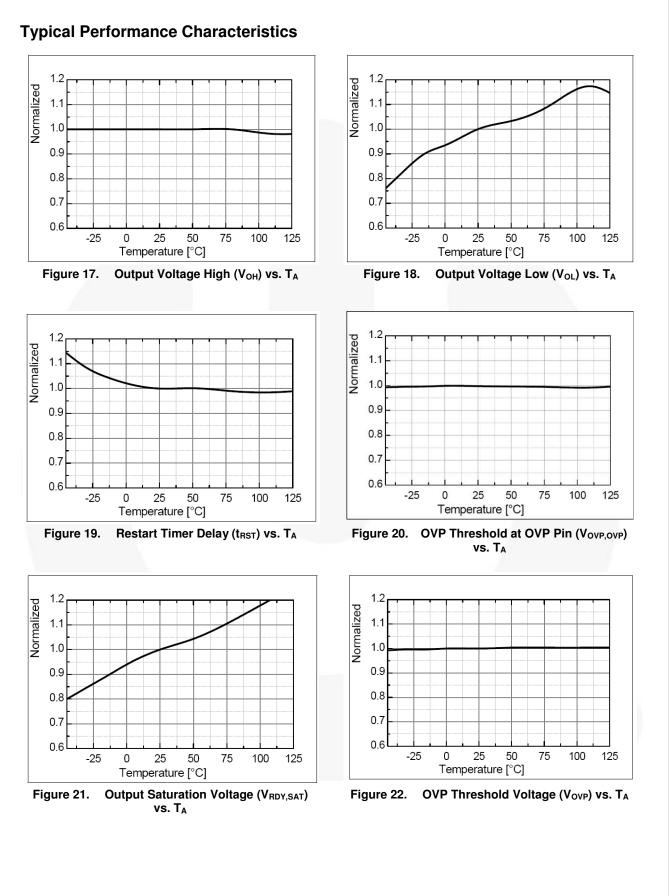

1. Startup: Normally, supply voltage (V<sub>CC</sub>) of a PFC block is fed from the additional power supply, which can be called standby power. Without this standby power, auxiliary winding for zero current detection can be used as a supply source. Once the supply voltage of the PFC block exceeds 12 V, internal operation is enabled until the voltage drops to 8.5 V. If V<sub>CC</sub> exceeds V<sub>Z</sub>, 20 mA current is sinking from V<sub>CC</sub>.

Figure 23. Startup Circuit

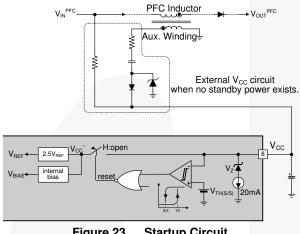

2. INV Block: Scaled-down voltage from the output is the input for the INV pin. Many functions are embedded based on the INV pin: transconductance amplifier, output OVP comparator, and disable comparator.

For the output voltage control, a transconductance amplifier is used instead of the conventional voltage amplifier. The transconductance amplifier (voltagecontrolled current source) aids the implementation of the OVP and disable functions. The output current of the amplifier changes according to the voltage difference of the inverting and non-inverting input of the amplifier. To cancel down the line input voltage effect on power factor correction, the effective control response of the PFC block should be slower than the line frequency and this conflicts with the transient response of the controller. Two-pole one-zero type compensation can meet both requirements.

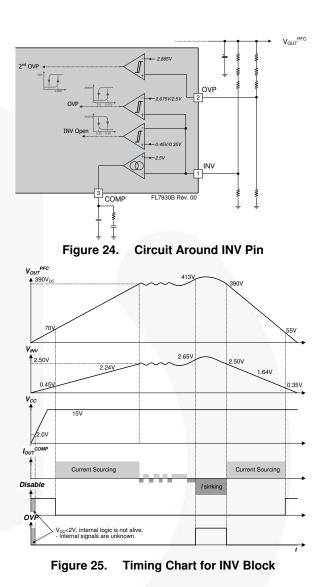

The OVP comparator shuts down the output drive block when the voltage of the INV pin is higher than 2.675 V and there is 0.175 V hysteresis. The disable comparator disables operation when the voltage of the inverting input is lower than 0.35 V and there is 100 mV hysteresis. An external small-signal MOSFET can be used to disable the IC, as shown in Figure 24. The IC operating current decreases to reduce power consumption if the IC is disabled. Figure 25 is the timing chart of the internal circuit near the INV pin when rated PFC output voltage is 390 V<sub>DC</sub> and V<sub>CC</sub> supply voltage is 15 V.

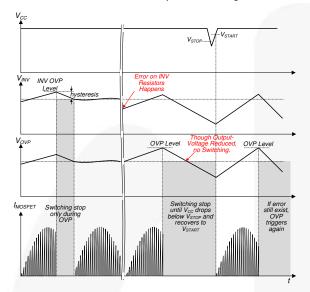

3. OVP Pin: Over-Voltage Protection (OVP) is embedded by the information at the INV pin. That information comes from the output through the voltage dividing resistors. To scale down from a high voltage to a low one, high resistance is normally used with low resistance. If the resistor of high resistance gets damaged and resistance is changed to high, though INV pin information is normal, output voltage exceeds its rated output. If this occurs, the output electrolytic capacitor may be damaged. To prevent such a catastrophe additional OVP pin is assigned to doublecheck output voltage. Additional OVP may be called "second" OVP, while INV pin OVP is called "first" OVP. Since the two OVP conditions are quite different, the protection recovering mode is different.

Once the first OVP triggers, switching stops immediately and recovers switching when the output voltage is decreased with a hysteresis. When the second OVP triggers, switching can be recovered only when the  $V_{CC}$ supply voltage falls below  $V_{STOP}$  and builds up higher than  $V_{START}$  again and  $V_{OVP}$  should be lower than hysteresis. If the second OVP is not used, the OVP pin must be connected to the INV pin or to the ground.

#### Figure 26. Comparison of First and Second OVP Recovery Modes

4. Control Range Compensation: On time is controlled by the output voltage compensator with FL7930B. Due to this when input voltage is high and load is light, control range becomes narrow compared to when input voltage is low. That control range decrease is inversely proportional to the double square of the input voltage (control range  $\propto \frac{1}{\text{input voltage}^2}$ ). Thus at high line, unwanted burst operation easily happens at light load and audible noise may be generated from the boost inductor or inductor at input filter. Different from the other converters, burst operation in PFC block is not needed because the PFC block itself is normally disabled during standby mode. To reduce unwanted burst operation at light load, an internal control range compensation function is implemented and shows no burst operation until 5% load at high line.

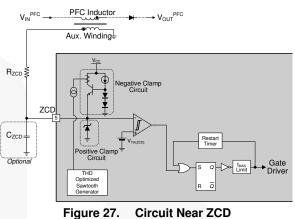

**5. Zero-Current Detection**: Zero-current detection (ZCD) generates the turn-on signal of the MOSFET when the boost inductor current reaches zero using an auxiliary winding coupled with the inductor. When the power switch turns on, negative voltage is induced at the auxiliary winding due to the opposite winding direction (*see Equation 1*). Positive voltage is induced (*see Equation 2*) when the power switch turns off:

$$V_{AUX} = -\frac{T_{AUX}}{T_{IND}} \cdot V_{AC}$$

(1)

$$V_{AUX} = \frac{T_{AUX}}{T_{IND}} \cdot \left( V_{PFCOUT} - V_{AC} \right)$$

(2)

where,  $V_{AUX}$  is the auxiliary winding voltage;  $T_{\text{IND}}$  and  $T_{AUX}$  are boost inductor turns and auxiliary winding turns, respectively;  $V_{AC}$  is input voltage for PFC converter; and  $V_{OUT\_PFC}$  is output voltage from the PFC converter.

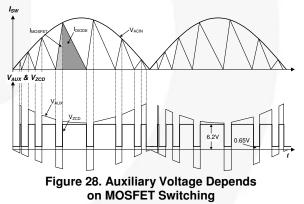

Because auxiliary winding voltage can swing from negative to positive voltage, the internal block in ZCD pin has both positive and negative voltage clamping circuits. When the auxiliary voltage is negative, an internal circuit clamps the negative voltage at the ZCD pin around 0.65 V by sourcing current to the serial resistor between the ZCD pin and the auxiliary winding. When the auxiliary voltage is higher than 6.5 V, current is sinked through a resistor from the auxiliary winding to the ZCD pin.

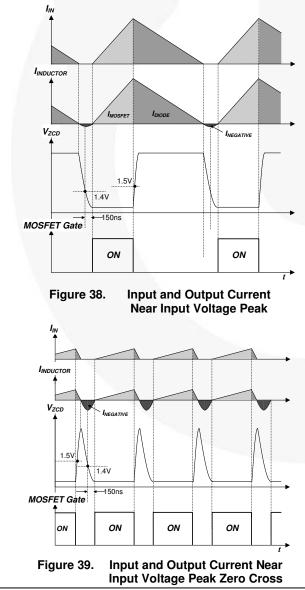

The auxiliary winding voltage is used to check the boost inductor current zero instance. When boost inductor current becomes zero, there is a resonance between boost inductor and all capacitors at the MOSFET drain pin, including Coss of the MOSFET; an external capacitor at the D-S pin to reduce the voltage rising and falling slope of the MOSFET; a parasitic capacitor at inductor; and so on to improve performance. Resonated voltage is reflected to the auxiliary winding and can be used for detecting zero current of boost inductor and valley position of MOSFET voltage stress. For valley detection, a minor delay by the resistor and capacitor is needed. A capacitor increases the noise immunity at the ZCD pin. If ZCD voltage is higher than 1.5 V. an internal ZCD comparator output becomes HIGH and LOW when the ZCD goes below 1.4 V. At the falling edge of comparator output, internal logic turns on the MOSFET.

Figure 29. Auxiliary Voltage Threshold

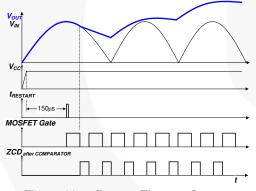

When no ZCD signal is available, the PFC controller cannot turn on the MOSFET, so the controller checks every switching off time and forces MOSFET turn on when the off time is longer than 150 µs. This restart timer triggers MOSFET turn-on at startup and may be used at the input voltage zero cross period.

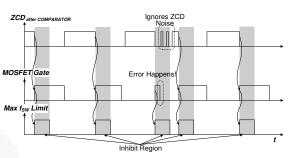

Because the MOSFET turn-on depends on the ZCD input, switching frequency may increase to higher than several megahertz due to the mis-triggering or noise on the nearby ZCD pin. If the switching frequency is higher than needed for critical conduction mode (CRM), operation mode shifts to continuous conduction mode (CCM). In CCM, unlike CRM where the boost inductor current is reset to zero at the next switch on; inductor current builds up at every switching cycle and can be raised to very high current that exceeds the current rating of the power switch or diode. This can seriously damage the power switch. To avoid this, maximum switching frequency limitation is embedded. If ZCD signal is applied again within 3.3 µs after the previous rising edge of gate signal, this signal is ignored internally and FL7930B waits for another ZCD signal. This slightly degrades the power factor performance at light load and high input voltage.

Figure 31. Maximum Switching Frequency Limit Operation

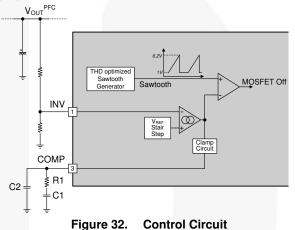

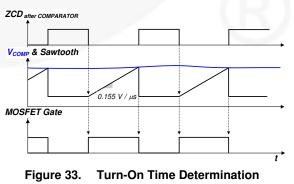

**6. Control**: The scaled output is compared with the internal reference voltage and sinking or sourcing current is generated from the COMP pin by the transconductance amplifier. The error amplifier output is compared with the internal sawtooth waveform to give proper turn-on time based on the controller.

Unlike a conventional voltage-mode PWM controller, FL7930B turns on the MOSFET at the falling edge of ZCD signal. The "ON" instant is determined by the external signal and the turn-on time lasts until the error amplifier output ( $V_{COMP}$ ) and sawtooth waveform meet. When load is heavy, output voltage decreases, scaled output decreases, COMP voltage increases to compensate low output, turn-on time lengthens to give more inductor turn-on time, and increased inductor current raises the output voltage. This is how a PFC negative feedback controller regulates output.

The maximum of  $V_{COMP}$  is limited to 6.5 V, which dictates the maximum turn-on time. Switching stops when  $V_{COMP}$  is lower than 1.0 V.

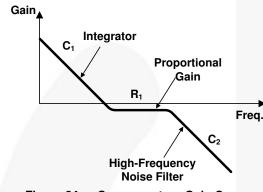

The roles of PFC controller are regulating output voltage and input current shaping to increase power factor. Duty control based on the output voltage should be fast enough to compensate output voltage dip or overshoot. For the power factor, however, the control loop must not react to the fluctuating AC input voltage. These two requirements conflict; therefore, when designing a feedback loop, the feedback loop should be least ten times slower than AC line frequency. That slow response is made by C1 at the compensator. R1 makes gain boost around operation region and C2 attenuates gain at higher frequency. Boost gain by R1 helps raise the response time and improves phase margin.

Figure 34. Compensators Gain Curve

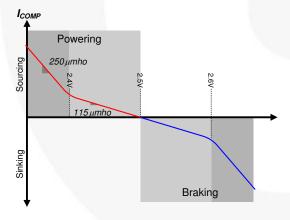

For the transconductance error amplifier side, gain changes based on differential input. When the error is large, gain is large to suppress the output dip or peak quickly. When the error is small, low gain is used to improve power factor performance.

Figure 35. Gain Characteristic

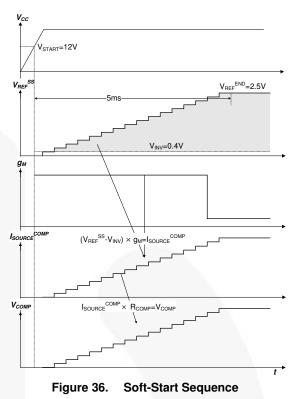

**7. Soft-Start**: When V<sub>CC</sub> reaches V<sub>START</sub>, the internal reference voltage is increased like a stair step for 5 ms. As a result, V<sub>COMP</sub> is also raised gradually and MOSFET turn-on time increases smoothly. This reduces voltage and current stress on the power switch during startup.

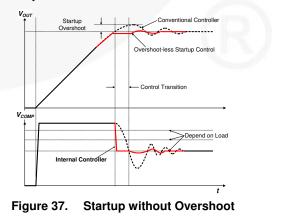

8. Startup without Overshoot: Feedback control speed of PFC is quite slow. Due to the slow response, there is a gap between output voltage and feedback control. That is why over-voltage protection (OVP) is critical at the PFC controller and voltage dip caused by fast load changes from light to heavy is diminished by a bulk capacitor. OVP can be triggered during startup phase. Operation on and off by OVP at startup may cause audible noise and can increase voltage stress at startup, which is normally higher than in normal operation. This operation is improved when soft start time is very long. However, too much startup time enlarges the output voltage building time at light load. FL7930B has overshoot protection at startup. During startup, the feedback loop is controlled by an internal proportional gain controller and when the output voltage reaches the rated value, it switches to an external compensator after a transition time of 30 ms. This internal proportional gain controller eliminates overshoot at startup and an external conventional compensator takes over successfully afterward.

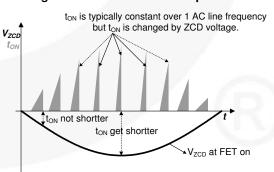

9. THD Optimization: Total harmonic distortion (THD) is the factor that dictates how closely input current shape matches sinusoidal form. The turn-on time of the PFC controller is almost constant over one AC line period due to the extremely low feedback control response. The turn-off time is determined by the current decrease slope of the boost inductor made by the input voltage and output voltage. Once inductor current becomes zero, resonance between Coss and the boost inductor makes oscillating waveforms at the drain pin and auxiliary winding. By checking the auxiliary winding voltage through the ZCD pin, the controller can check the zero current of boost inductor. At the same time, a minor delay is inserted to determine the valley position of drain voltage. The input and output voltage difference is at its maximum at the zero cross point of AC input voltage. The current decrease slope is steep near the zero cross region and more negative inductor current flows during a drain voltage valley detection time. Such a negative inductor current cancels down the positive current flows and input current becomes zero, called "zero-cross distortion" in PFC.

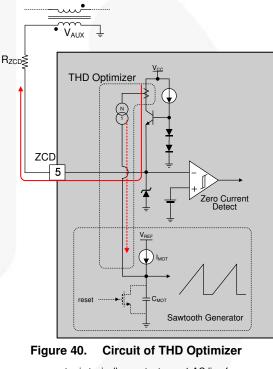

To improve this, lengthened turn-on time near the zero cross region is a well-known technique, though the method may vary and may be proprietary. FL7930B optimizes this by sourcing current through the ZCD pin. Auxiliary winding voltage becomes negative when the MOSFET turns on and is proportional to input voltage. The negative clamping circuit of ZCD outputs the current to maintain the ZCD voltage at a fixed value. The sourcing current from the ZCD is directly proportional to the input voltage. Some portion of this current is applied to the internal sawtooth generator together with a fixed-current source. Theoretically the fixed-current source and the capacitor at sawtooth generator determine the maximum turn-on time when no current is sourcing at ZCD clamp circuit and available turn-on time gets shorter proportional to the ZCD sourcing current.

#### Figure 41. Effect of THD Optimizer

By THD optimizer, turn-on time over one AC line period is proportionally changed, depending on input voltage. Near zero cross, lengthened turn-on time improves THD performance.

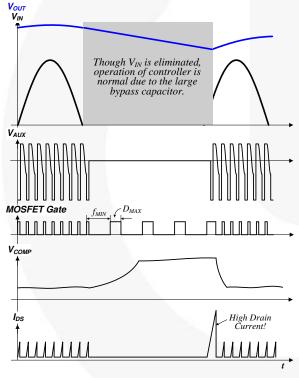

FL7930B — Single-Stage Flyback and Boundary-Mode PFC Controller for Lighting

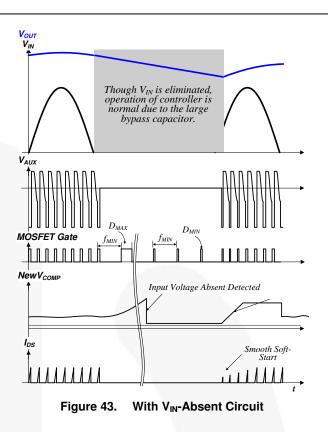

10. VIN-Absent Detection: To reduce power loss caused by input voltage sensing resistors and to optimize THD, the FL7930B omits AC input voltage detection. Therefore, no information about AC input is available from the internal controller. In many cases, the V<sub>CC</sub> of PFC controller is supplied by an independent power source like standby power. In this scheme, some mismatch may exist. For example, when the electric power is suddenly interrupted during two or three AC line periods; V<sub>CC</sub> is still live during that time, but output voltage drops because there is no input power source. Consequently, the control loop tries to compensate for the output voltage drop and V<sub>COMP</sub> reaches its maximum. This lasts until AC input voltage is live again. When AC input voltage is live again, high V<sub>COMP</sub> allows high switching current and more stress is put on the MOSFET and diode. To protect against this, FL7930B checks if the input AC voltage exists. If input does not exist, soft-start is reset and waits until AC input is live again. Soft-start manages the turn-on time for smooth operation when it detects AC input is applied again and applies less voltage and current stress on startup.

Figure 42. Without VIN-Absent Circuit

**11. Current Sense**: The MOSFET current is sensed using an external sensing resistor for over-current protection. If the CS pin voltage is higher than 0.8 V, the over-current protection comparator generates a protection signal. An internal RC filter of 40 k $\Omega$  and 8 pF is included to filter switching noise.

**12. Gate Driver Output**: FL7930B contains a single totem-pole output stage designed for a direct drive of the power MOSFET. The drive output is capable of up to +500 / -800 mA peak current with a typical rise and fall time of 50 ns with 1 nF load. The output voltage is clamped to 13 V to protect the MOSFET gate even if the  $V_{CC}$  voltage is higher than 13 V.

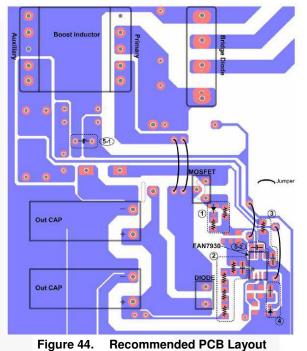

### **PCB Layout Guide**

PFC block normally handles high switching current and the voltage low-energy signal path can be affected by the high-energy path. Cautious PCB layout is mandatory for stable operation.

- 1 The gate drive path should be as short as possible. The closed-loop that starts from the gate driver, MOSFET gate, and MOSFET source to ground of PFC controller should be as close as possible. This is also crossing point between power ground and signal ground. Power ground path from the bridge diode to the output bulk capacitor should be short and wide. The sharing position between power ground and signal ground should be only at one position to avoid ground loop noise. Signal path of the PFC controller should be short and wide for external components to contact.

- 2 The PFC output voltage sensing resistor is normally high to reduce current consumption. This path can be affected by external noise. To reduce noise potential at the INV pin, a shorter path for output sensing is recommended. If a shorter path is not possible, place some dividing resistors between PFC output and the INV pin — closer to the INV pin is better. Relative high voltage close to the INV pin can be helpful.

- 3 The ZCD path is recommended close to auxiliary winding from boost inductor and to the ZCD pin. If that is difficult, place a small capacitor (below 50 pF) to reduce noise.

- 4 The switching current sense path should not share with another path to avoid interference. Some additional components may be needed to reduce the noise level applied to the CS pin.

5 A stabilizing capacitor for  $V_{CC}$  is recommended as close as possible to the  $V_{CC}$  and ground pins. If it is difficult, place the SMD capacitor as close to the corresponding pins as possible.

© 2010 Fairchild Semiconductor Corporation FL7930B • Rev. 1.0.4

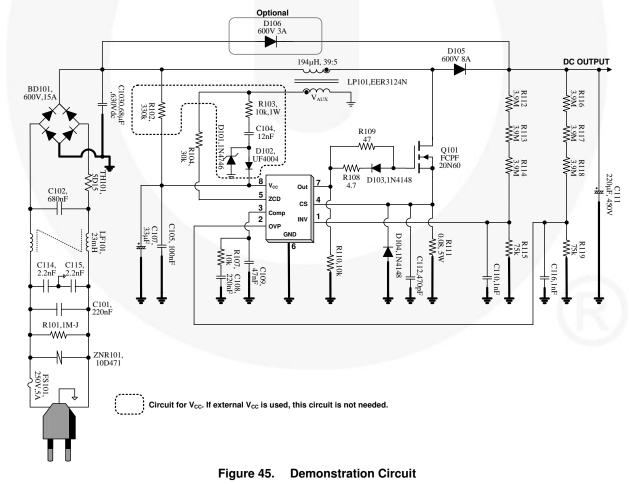

### **Typical Application Circuit**

| Application  | Device  | Input Voltage<br>Range | Rated Output<br>Power | Output Voltage<br>(Maximum Current) |

|--------------|---------|------------------------|-----------------------|-------------------------------------|

| LED Lighting | FL7930B | 90-265 V <sub>AC</sub> | 195 W                 | 390 V (0.5 A)                       |

#### **Features**

- Average efficiency of 25%, 50%, 75%, and 100% load conditions is higher than 95% at universal input.

- Power factor at rated load is higher than 0.98 at universal input.

- Total Harmonic Distortion (THD) at rated load is lower than 15% at universal input.

#### **Key Design Notes**

- When auxiliary V<sub>CC</sub> supply is not available, V<sub>CC</sub> power can be supplied through Zero Current Detect (ZCD) winding. The power consumption of R103 is quite high, so its power rating needs checking.

- Because the input bias current of INV pin is almost zero, output voltage sensing resistors (R112~R115) should be as high as possible. However, too-high resistance makes the node susceptible to noise. Resistor values need to strike a balance between power consumption and noise immunity.

- Quick charge diode (D106) can be eliminated if output diode inrush current capability is sufficient. Through D106, system operation is normal due to the controller's highly reliable protection features.

#### Schematic

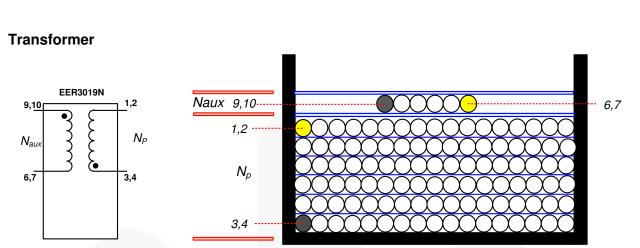

Figure 46. Transformer Schematic Diagram

### Winding Specifications

| Position | No                                               | $\text{Pin} \ (\text{S} \rightarrow \text{F})$ | Wire    | Turns | Winding Method   |  |

|----------|--------------------------------------------------|------------------------------------------------|---------|-------|------------------|--|

| Bottom   | Np                                               | $3,4\rightarrow1,2$                            | 0.1φ×50 | 39    | Solenoid Winding |  |

| Bolion   | Insulation: Polyester Tape t = 0.05mm, 3 Layers  |                                                |         |       |                  |  |

| Tan      | N <sub>AUX</sub>                                 | 9,10 → 6,7                                     | 0.3φ    | 5     | Solenoid Winding |  |

| Тор      | Insulation: Polyester Tape t = 0.05 mm, 4 Layers |                                                |         |       |                  |  |

### **Electrical Characteristics**

|            | Pin                     | Specification | Remark       |  |

|------------|-------------------------|---------------|--------------|--|

| Inductance | $3, 4 \rightarrow 1, 2$ | 194 μH ± 5%   | 100 kHz, 1 V |  |

### Core & Bobbin

Core: EER3019, Samhwa (PL-7) (Ae=137.0mm<sup>2</sup>) Bobbin: EER3019

| Part #                       | Value                        | Note                   | Part #     | Value       | Note                                                     |

|------------------------------|------------------------------|------------------------|------------|-------------|----------------------------------------------------------|

|                              | Resistor                     |                        |            | Switch      |                                                          |

| R101                         | 1 MΩ                         | 1W                     | Q101       | FCPF20N60   | 20 A, 600 V, SuperFET <sup>®</sup>                       |

| R102                         | 330 kΩ                       | 1/2W                   |            |             | Diode                                                    |

| R103                         | 10 kΩ                        | 1W                     | D101       | 1N4746      | 1 W, 18 V, Zener Diode                                   |

| R104                         | 30 kΩ                        | 1/4W                   | D102       | UF4004      | 1 A, 400 V Glass Passivated<br>High-Efficiency Rectifier |

| R107                         | 10 kΩ                        | 1/4W                   | D103       | 1N4148      | 1 A, 100 V Small-Signal Diode                            |

| R108                         | 4.7 kΩ                       | 1/4W                   | D104       | 1N4148      | 1 A, 100 V Small-Signal Diode                            |

| R109                         | 47 kΩ                        | 1/4W                   | D105       |             | 8 A, 600 V, General-Purpose<br>Rectifier                 |

| R110                         | 10 kΩ                        | 1/4W                   | D106       |             | 3 A, 600 V, General-Purpose<br>Rectifier                 |

| R111                         | 0.80 kΩ                      | 5W                     |            |             |                                                          |

| R112, 113,<br>14,116,117,118 | 3.9 kΩ                       | 1/4W                   | IC101      | FL7930B     | CRM PFC Controller                                       |

| R115,119                     | 75 kΩ                        | 1/4W                   |            |             |                                                          |

|                              | Capacitor                    |                        |            |             | Fuse                                                     |

| C101                         | 220 nF / 275 V <sub>AC</sub> | Box Capacitor          | FS101      | 5 A / 250 V |                                                          |

| C102                         | 680 nF / 275 V <sub>AC</sub> | Box Capacitor          | NTC        |             | NTC                                                      |

| C103                         | 0.68 µF / 630 V              | Box Capacitor          | TH101      | 5D-15       |                                                          |

| C104                         | 12 nF / 50 V                 | Ceramic Capacitor      |            | Brid        | lge Diode                                                |

| C105                         | 100 nF / 50 V                | SMD (1206)             | BD101      |             | 15 A, 600 V                                              |

| C107                         | 33 μF / 50 V                 | Electrolytic Capacitor |            | Li          | ne Filter                                                |

| C108                         | 220 nF / 50 V                | Ceramic Capacitor      | LF101      | 23 mH       |                                                          |

| C109                         | 47 nF / 50 V                 | Ceramic Capacitor      |            | Tra         | nsformer                                                 |

| C110,116                     | 1 nF / 50 V                  | Ceramic Capacitor      | T1 EER3019 |             | Ae=137.0 mm <sup>2</sup>                                 |

| C112                         | 47 nF / 50 V                 | Ceramic Capacitor      |            |             | ZNR                                                      |

| C111                         | 220 µF / 450 V               | Electrolytic Capacitor | ZNR101     | 10D471      |                                                          |

| C114                         | 2.2 nF / 450 V               | Box Capacitor          |            |             |                                                          |

| C115                         | 2.2 nF / 450 V               | Box Capacitor          |            |             |                                                          |

Package drawings are provided as a service to customers considering Fairchild components. Drawings may change in any manner without notice. Please note the revision and/or date on the drawing and contact a Fairchild Semiconductor representative to verify or obtain the most recent revision. Package specifications do not expand the terms of Fairchild's worldwide terms and conditions, specifically the warranty therein, which covers Fairchild products.

Always visit Fairchild Semiconductor's online packaging area for the most recent package drawings: <u>http://www.fairchildsemi.com/dwg/M0/M08A.pdf</u>.

FL7930B — Single-Stage Flyback and Boundary-Mode PFC Controller for Lighting

####

#### TRADEMARKS

The following includes registered and unregistered trademarks and service marks, owned by Fairchild Semiconductor and/or its global subsidiaries, and is not intended to be an exhaustive list of all such trademarks.

| AccuPower™                             | F-PFS™                  |

|----------------------------------------|-------------------------|

| AX-CAP®*                               | FRFET <sup>6</sup>      |

| BitSiC™                                | Global F                |

| Build it Now™                          | GreenB                  |

| CorePLUS™                              | Green F                 |

| CorePOWER™                             | Green F                 |

| CROSSVOLT™                             | Gmax™                   |

| CTL™                                   | <b>GTO</b> <sup>™</sup> |

| Current Transfer Logic™                | IntelliMA               |

|                                        | ISOPLA                  |

| Dual Cool™                             | Making                  |

| EcoSPARK <sup>®</sup>                  | and                     |

| EfficientMax™                          | MegaBu                  |

| ESBCTM                                 | MICRO                   |

| <b>F</b> <sup>®</sup>                  | MicroFE                 |

| <b>T</b> ®                             | MicroPa                 |

| Fairchild®                             | MicroPa                 |

| Fairchild Semiconductor®               | MillerDri               |

| FACT Quiet Series™                     | MotionN                 |

| FACT <sup>®</sup><br>FAST <sup>®</sup> | mWSav                   |

|                                        | OptoHiT                 |

| FastvCore <sup>™</sup>                 | OPTOL                   |

| FETBench™                              | OBTOR                   |

FET® bal Power Resource<sup>s</sup> enBridge™ en FPS™ en FPS™ e-Series™ axTM TM IIIMAX<sup>TM</sup> PLANAR<sup>™</sup> king Small Speakers Sound Louder and Better gaBuck™ ROCOUPLER OFFT roPak™ roPak2™ erDrive™ ionMax™ Saver oHiT™ TOLOGIC® **OPTOPLANAR<sup>®</sup>**

PowerTrench® PowerXS<sup>™</sup> Programmable Active Droop™ OFET QS<sup>TM</sup> Quiet Series™ RapidConfigure™ Saving our world, 1mW/W/kW at a time™ SignalWise SmartMax™ SMART START Solutions for Your Success™ SPM STEALTH\*\* SuperFET® SuperSOT™-3 SuperSOT™-6 SuperSOT™-8 SupreMOS® SvncFET<sup>TM</sup>

#### Sync-Lock™ SYSTEM GENERAL®

TinyBoost<sup>®</sup> TinyCalc<sup>™</sup> TinyLogic<sup>®</sup> TinyCoyc<sup>®</sup> TinyPOVer<sup>™</sup> TinyPover<sup>™</sup> TinyPWM<sup>™</sup> TinyWire<sup>™</sup> TranSiC<sup>™</sup> TriFault Detect<sup>™</sup> TRUECURRENT<sup>®</sup>\* µSerDes<sup>™</sup>

W SerDes"

UHC® Ultra FRFET™ UniFET™ VCX™ VisualMax™ VoltagePlus™ XS™

\* Trademarks of System General Corporation, used under license by Fairchild Semiconductor.

#### DISCLAIMER

**FPS**<sup>TM</sup>

FAIRCHILD SEMICONDUCTOR RESERVES THE RIGHT TO MAKE CHANGES WITHOUT FURTHER NOTICE TO ANY PRODUCTS HEREIN TO IMPROVE RELIABILITY, FUNCTION, OR DESIGN. FAIRCHILD DOES NOT ASSUME ANY LIABILITY ARISING OUT OF THE APPLICATION OR USE OF ANY PRODUCT OR CIRCUIT DESCRIBED HEREIN; NEITHER DOES IT CONVEY ANY LICENSE UNDER ITS PATENT RIGHTS, NOR THE RIGHTS OF OTHERS. THESE SPECIFICATIONS DO NOT EXPAND THE TERMS OF FAIRCHILD'S WORLDWIDE TERMS AND CONDITIONS, SPECIFICALLY THE WARRANTY THEREIN, WHICH COVERS THESE PRODUCTS.

#### LIFE SUPPORT POLICY

FAIRCHILD'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF FAIRCHILD SEMICONDUCTOR CORPORATION.

#### As used herein:

- Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body or (b) support or sustain life, and (c) whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury of the user.

- A critical component in any component of a life support, device, or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

#### ANTI-COUNTERFEITING POLICY

Fairchild Semiconductor Corporation's Anti-Counterfeiting Policy. Fairchild's Anti-Counterfeiting Policy is also stated on our external website, www.fairchildsemi.com, under Sales Support.

Counterfeiting of semiconductor parts is a growing problem in the industry. All manufacturers of semiconductor products are experiencing counterfeiting of their parts. Customers who inadvertently purchase counterfeit parts experience many problems such as loss of brand reputation, substandard performance, failed applications, and increased cost of production and manufacturing delays. Fairchild is taking strong measures to protect ourselves and our customers from the proliferation of counterfeit parts. Fairchild strongly encourages customers to purchase Fairchild parts either directly from Fairchild or from Authorized Fairchild Distributors who are listed by country on our web page cited above. Products customers buy either from Fairchild directly or from Authorized Fairchild Distributors are genuine parts, have full traceability, meet Fairchild's quality standards for handling and storage and provide access to Fairchild's full range of up-to-date technical and product information. Fairchild and our Authorized Distributors will stand behind all warranties and will appropriately address any warranty issues that may arise. Fairchild will not provide any warranty coverage or other assistance for parts bought from Unauthorized Surces. Fairchild is committed to combat this global problem and encourage our customers to do their part in stopping this practice by buying direct or from authorized distributors.

#### PRODUCT STATUS DEFINITIONS

| Datasheet Identification | Product Status        | Definition                                                                                                                                                                                             |

|--------------------------|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Advance Information      | Formative / In Design | Datasheet contains the design specifications for product development. Specifications may change in any manner without notice.                                                                          |

| Preliminary              | First Production      | Datasheet contains preliminary data; supplementary data will be published at a later date. Fairchild<br>Semiconductor reserves the right to make changes at any time without notice to improve design. |

| No Identification Needed | Full Production       | Datasheet contains final specifications. Fairchild Semiconductor reserves the right to make<br>changes at any time without notice to improve the design.                                               |

| Obsolete                 | Not In Production     | Datasheet contains specifications on a product that is discontinued by Fairchild Semiconductor.<br>The datasheet is for reference information only.                                                    |

Rev. 166

ON Semiconductor and are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of ON Semiconductor's product/patent coverage may be accessed at <u>www.onsemi.com/site/pdf/Patent-Marking.pdf</u>. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using ON Semiconductor products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by ON Semiconductor. "Typical" parameters which may be provided in ON Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. ON Semiconductor does not convey any license under its patent rights of others. ON Semiconductor products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use ON Semiconductor has against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death ass

#### PUBLICATION ORDERING INFORMATION

#### LITERATURE FULFILLMENT:

Literature Distribution Center for ON Semiconductor 19521 E. 32nd Pkwy, Aurora, Colorado 80011 USA Phone: 303-675-2175 or 800-344-3860 Toll Free USA/Canada Fax: 303-675-2176 or 800-344-3867 Toll Free USA/Canada Email: orderlit@onsemi.com N. American Technical Support: 800–282–9855 Toll Free USA/Canada Europe, Middle East and Africa Technical Support: Phone: 421 33 790 2910

Japan Customer Focus Center Phone: 81-3-5817-1050 ON Semiconductor Website: www.onsemi.com

Order Literature: http://www.onsemi.com/orderlit

For additional information, please contact your local Sales Representative

© Semiconductor Components Industries, LLC