July 2000

FM93C86A 16K-Bit Serial CMOS EEPROM

MICROWIRE<sup>TM</sup> Synchronous Bus)

# FM93C86A 16K-Bit Serial CMOS EEPROM (MICROWIRE™ Synchronous Bus)

# **General Description**

FM93C86A is a 16,384-bit CMOS non-volatile EEPROM organized as 1024 x 16-bit array. This device features MICROWIRE interface which is a 4-wire serial bus with chipselect (CS), clock (SK), data input (DI) and data output (DO) signals. This interface is compatible to many of standard Microcontrollers and Microprocessors. This device offers a pin (ORG), using which, the user can select the format of the data (16-bit or 8-bit). If ORG is tied to GND, then 8-bit format is selected, while if ORG is tied to V<sub>CC</sub>, then 16-bit format is selected. There are 7 instructions implemented on the FM93C86A for various Read, Write, Erase, and Write Enable/ Disable operations. This device is fabricated using Fairchild Semiconductor floating-gate CMOS process for high reliability, high endurance and low power consumption.

"LZ" and "L" versions of FM93C86A offer very low standby current making them suitable for low power applications. This device is offered in both SO and DIP packages.

#### Features

- Wide V<sub>CC</sub> 2.7V 5.5V

- User selectable organization x16 (ORG = 1) x8 (ORG = 0)

- Typical active current of 200μA 10μA standby current typical 1μA standby current typical (L) 0.1μA standby current typical (LZ)

- No Erase instruction required before Write instruction

- Self timed write cycle

- Device status during programming cycles

- 40 year data retention

- Endurance: 1,000,000 data changes

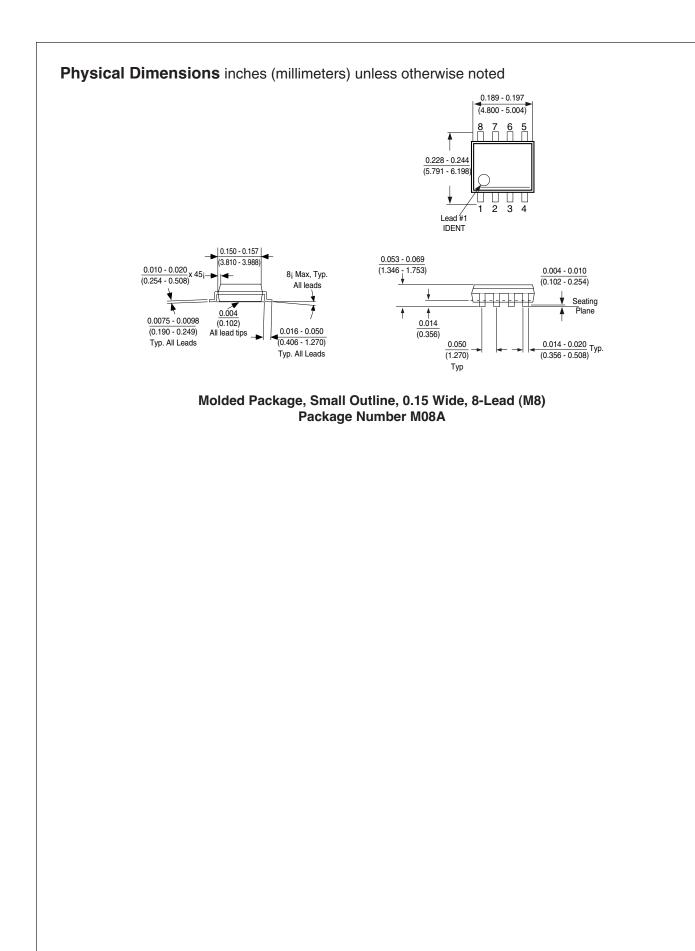

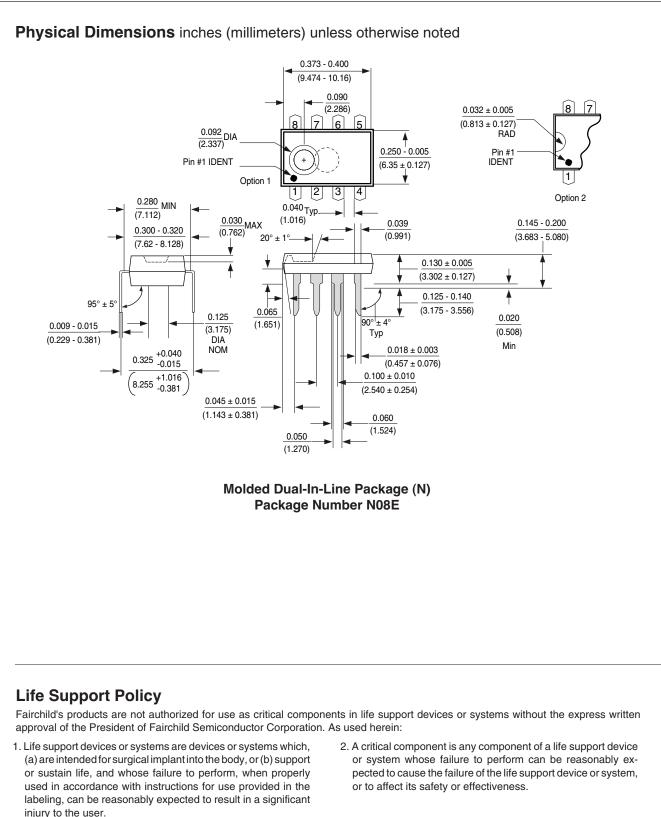

- Packages available: 8-pin SO and 8-pin DIP

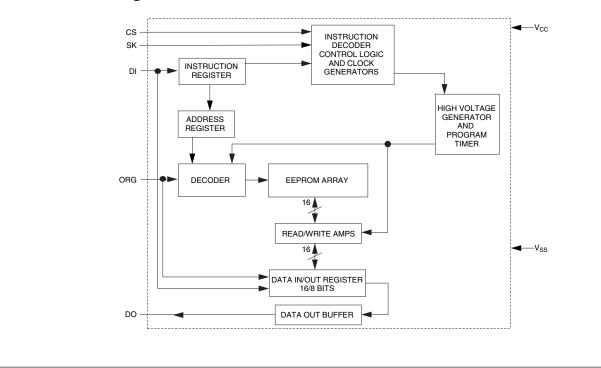

## **Functional Diagram**

FM93C86A 16K-Bit Serial CMOS EEPROM (MICROWIRE<sup>TM</sup> Synchronous Bus)

# Absolute Maximum Ratings (Note 1)

| Ambient Storage Temperature                            | -65°C to +150°C |

|--------------------------------------------------------|-----------------|

| All Input or Output Voltages<br>with Respect to Ground | +6.5V to -0.3V  |

| Lead Temperature                                       |                 |

| (Soldering, 10 sec.)                                   | +300°C          |

| ESD rating                                             | 2000V           |

## **Operating Conditions**

| O°C        | Ambient Operating Temperature<br>FM93C86A | 0°C to +70°C    |  |

|------------|-------------------------------------------|-----------------|--|

| .3V        | FM93C86AE                                 | -40°C to +85°C  |  |

|            | FM93C86AV                                 | -40°C to +125°C |  |

| 0°C<br>N0V | Power Supply (V <sub>CC</sub> )           | 4.5V to 5.5V    |  |

# DC and AC Electrical Characteristics $V_{\text{CC}}$ = 4.5V to 5.5V unless otherwise specified

| Symbol                               | Parameter                                 | Conditions                                                          | Min                   | Max                       | Units<br>mA |  |

|--------------------------------------|-------------------------------------------|---------------------------------------------------------------------|-----------------------|---------------------------|-------------|--|

| I <sub>CCA</sub>                     | Operating Current                         | CS = V <sub>IH</sub> , SK=1.0 MHz                                   |                       | 1                         |             |  |

| I <sub>ccs</sub>                     | Standby Current                           | CS = V <sub>IL</sub>                                                |                       | 50                        | μA          |  |

| I <sub>IL</sub><br>I <sub>OL</sub>   | Input Leakage<br>Output Leakage           | V <sub>IN</sub> = 0V to V <sub>CC</sub><br>(Note 2)                 |                       | ±-1                       | μA          |  |

| I <sub>ILO</sub>                     | Input Leakage ORG Pin                     | ORG tied to V <sub>CC</sub><br>ORG tied to V <sub>SS</sub> (Note 3) | -1<br>-2.5            | 1<br>2.5                  | μA          |  |

| V <sub>IL</sub><br>V <sub>IH</sub>   | Input Low Voltage<br>Input High Voltage   |                                                                     | -0.1<br>2             | 0.8<br>V <sub>CC</sub> +1 | V           |  |

| V <sub>OL1</sub><br>V <sub>OH1</sub> | Output Low Voltage<br>Output High Voltage | I <sub>OL</sub> = 2.1 mA<br>I <sub>OH</sub> = -400 μA               | 2.4                   | 0.4                       | V           |  |

| V <sub>OL2</sub><br>V <sub>OH2</sub> | Output Low Voltage<br>Output High Voltage | I <sub>OL</sub> = 10 μA<br>I <sub>OH</sub> = -10 μA                 | V <sub>CC</sub> - 0.2 | 0.2                       | V           |  |

| f <sub>SK</sub>                      | SK Clock Frequency                        | (Note 4)                                                            |                       | 1                         | MHz         |  |

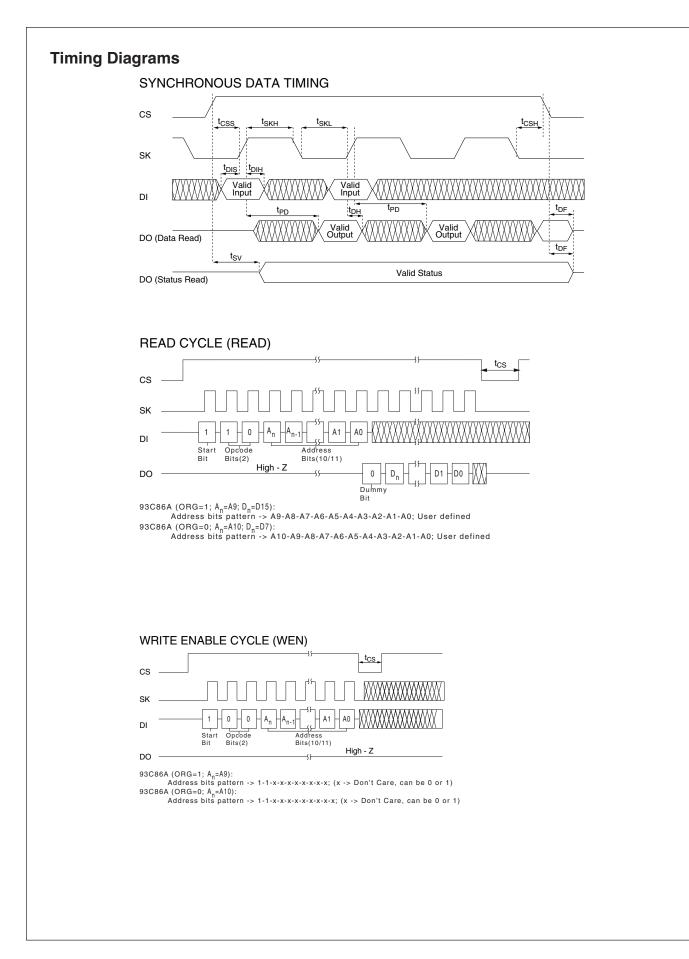

| t <sub>SKH</sub>                     | SK High Time                              | 0°C to +70°C<br>-40°C to +125°C                                     | 250<br>300            |                           | ns          |  |

| t <sub>SKL</sub>                     | SK Low Time                               |                                                                     | 250                   |                           | ns          |  |

| t <sub>CS</sub>                      | Minimum CS Low Time                       | (Note 5)                                                            | 250                   |                           | ns          |  |

| t <sub>CSS</sub>                     | CS Setup Time                             |                                                                     | 50                    |                           | ns          |  |

| t <sub>DH</sub>                      | DO Hold Time                              |                                                                     | 70                    |                           | ns          |  |

| t <sub>DIS</sub>                     | DI Setup Time                             |                                                                     | 100                   |                           | ns          |  |

| t <sub>CSH</sub>                     | CS Hold Time                              |                                                                     | 0                     |                           | ns          |  |

| t <sub>DIH</sub>                     | DI Hold Time                              |                                                                     | 20                    |                           | ns          |  |

| t <sub>PD</sub>                      | Output Delay                              |                                                                     |                       | 500                       | ns          |  |

| t <sub>SV</sub>                      | CS to Status Valid                        |                                                                     |                       | 500                       | ns          |  |

| t <sub>DF</sub>                      | CS to DO in Hi-Z                          | CS = V <sub>IL</sub>                                                |                       | 100                       | ns          |  |

| t <sub>WP</sub>                      | Write Cycle Time                          |                                                                     |                       | 10                        | ms          |  |

FM93C86A 16K-Bit Serial CMOS EEPROM (MICROWIRE<sup>TM</sup> Synchronous Bus)

#### Absolute Maximum Ratings (Note 1)

| Ambient Storage Temperature                            | -65°C to +150°C | Ambient Op     |

|--------------------------------------------------------|-----------------|----------------|

| All Input or Output Voltages<br>with Respect to Ground | +6.5V to -0.3V  | FM930<br>FM930 |

| Lead Temperature                                       |                 | FM930          |

| (Soldering, 10 sec.)                                   | +300°C          | Power Supp     |

| ESD rating                                             | 2000V           |                |

#### **Operating Conditions**

| C to +150°C  | Ambient Operating Temperature   |                 |

|--------------|---------------------------------|-----------------|

| .5V to -0.3V | FM93C86AL/LZ                    | 0°C to +70°C    |

|              | FM93C86ALE/LZE                  | -40°C to +85°C  |

|              | FM93C86ALV/LZV                  | -40°C to +125°C |

| +300°C       | Power Supply (V <sub>CC</sub> ) | 2.7V to 5.5V    |

| 2000V        |                                 |                 |

# **DC and AC Electrical Characteristics** $V_{CC} = 2.7V$ to 4.5V unless otherwise specified. Refer to

page 3 for 4.5V to 5.5V  $\mathrm{V}_{\mathrm{CC}}$

| Symbol                             | Parameter                                 | Conditions                                                          | Min                        | Max                                       | Units    |

|------------------------------------|-------------------------------------------|---------------------------------------------------------------------|----------------------------|-------------------------------------------|----------|

| I <sub>CCA</sub>                   | Operating Current                         | CS = V <sub>IH</sub> , SK=250 KHz                                   |                            | 1                                         | mA       |

| I <sub>CCS</sub>                   | Standby Current<br>L<br>LZ (2.7V to 4.5V) | CS = V <sub>IL</sub>                                                |                            | 10<br>1                                   | μA<br>μA |

| I <sub>IL</sub><br>I <sub>OL</sub> | Input Leakage<br>Output Leakage           | V <sub>IN</sub> = 0V to V <sub>CC</sub><br>(Note 2)                 |                            | ±1                                        | μΑ       |

| I <sub>ILO</sub>                   | Input Leakage ORG Pin                     | ORG tied to V <sub>CC</sub><br>ORG tied to V <sub>SS</sub> (Note 3) | -1<br>-2.5                 | 1<br>2.5                                  | μA       |

| V <sub>IL</sub><br>V <sub>IH</sub> | Input Low Voltage<br>Input High Voltage   |                                                                     | -0.1<br>0.8V <sub>CC</sub> | 0.15V <sub>CC</sub><br>V <sub>CC</sub> +1 | V        |

| V <sub>OL</sub><br>V <sub>OH</sub> | Output Low Voltage<br>Output High Voltage | I <sub>OL</sub> = 10μA<br>I <sub>OH</sub> = -10μA                   | 0.9V <sub>CC</sub>         | 0.1V <sub>CC</sub>                        | V        |

| f <sub>SK</sub>                    | SK Clock Frequency                        | (Note 4)                                                            | 0                          | 250                                       | KHz      |

| t <sub>SKH</sub>                   | SK High Time                              |                                                                     | 1                          |                                           | μs       |

| t <sub>SKL</sub>                   | SK Low Time                               |                                                                     | 1                          |                                           | μs       |

| t <sub>cs</sub>                    | Minimum CS Low Time                       | (Note 5)                                                            | 1                          |                                           | μs       |

| t <sub>css</sub>                   | CS Setup Time                             |                                                                     | 0.2                        |                                           | μs       |

| t <sub>DH</sub>                    | DO Hold Time                              |                                                                     | 70                         |                                           | ns       |

| t <sub>DIS</sub>                   | DI Setup Time                             |                                                                     | 0.4                        |                                           | μs       |

| t <sub>CSH</sub>                   | CS Hold Time                              |                                                                     | 0                          |                                           | ns       |

| t <sub>DIH</sub>                   | DI Hold Time                              |                                                                     | 0.4                        |                                           | μs       |

| t <sub>PD</sub>                    | Output Delay                              |                                                                     |                            | 2                                         | μs       |

| t <sub>sv</sub>                    | CS to Status Valid                        |                                                                     |                            | 1                                         | μs       |

| t <sub>DF</sub>                    | CS to DO in Hi-Z                          | CS = V <sub>IL</sub>                                                |                            | 0.4                                       | μs       |

| t <sub>WP</sub>                    | Write Cycle Time                          |                                                                     |                            | 15                                        | ms       |

# **Capacitance** $T_A = 25^{\circ}C$ , f = 1 MHz or 250 KHz (Note 6)

| Symbol           | Test               | Тур | Max | Units |

|------------------|--------------------|-----|-----|-------|

| C <sub>OUT</sub> | Output Capacitance |     | 5   | pF    |

| C <sub>IN</sub>  | Input Capacitance  |     | 5   | pF    |

**Note 1:** Stress above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of the specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

Note 2: Typical leakage values are in the 20nA range.

Note 3: ORG pin may draw >1 $\mu$ A when in x8 mode due to the internal pull-up transistor.

Note 4: The shortest allowable SK clock period =  $1/f_{SK}$  (as shown under the  $f_{SK}$  parameter). Maximum SK clock speed (minimum SK period) is determined by the interaction of several AC parameters stated in the datasheet. Within this SK period, both  $t_{SK}$ , and  $t_{SK}$  (minimum for shorter SK cycle time operation.

**Note 5:** CS (Chip Select) must be brought low (to  $V_{lL}$ ) for an interval of  $t_{CS}$  in order to reset all internal device registers (device reset) prior to beginning another opcode cycle. (This is shown in the opcode diagram on the following page.)

Note 6: This parameter is periodically sampled and not 100% tested.

# **AC Test Conditions**

| V <sub>CC</sub> Range                                   | V <sub>IL</sub> /V <sub>IH</sub><br>Input Levels | V <sub>OL</sub> /V <sub>OH</sub><br>Timing Level | I <sub>OL</sub> /I <sub>OH</sub> |              |  |  |  |  |  |

|---------------------------------------------------------|--------------------------------------------------|--------------------------------------------------|----------------------------------|--------------|--|--|--|--|--|

| $2.7V \le V_{CC} \le 5.5V$<br>(Extended Voltage Levels) | 0.3V/1.8V                                        | 1.0V                                             | 0.8V/1.5V                        | ±10μA        |  |  |  |  |  |

| $4.5V \le V_{CC} \le 5.5V$ (TTL Levels)                 | 0.4V/2.4V                                        | 1.0V/2.0V                                        | 0.4V/2.4V                        | 2.1mA/-0.4mA |  |  |  |  |  |

| Output Load: 1 TTL Gate (C <sub>L</sub> = 100 pF)       |                                                  |                                                  |                                  |              |  |  |  |  |  |

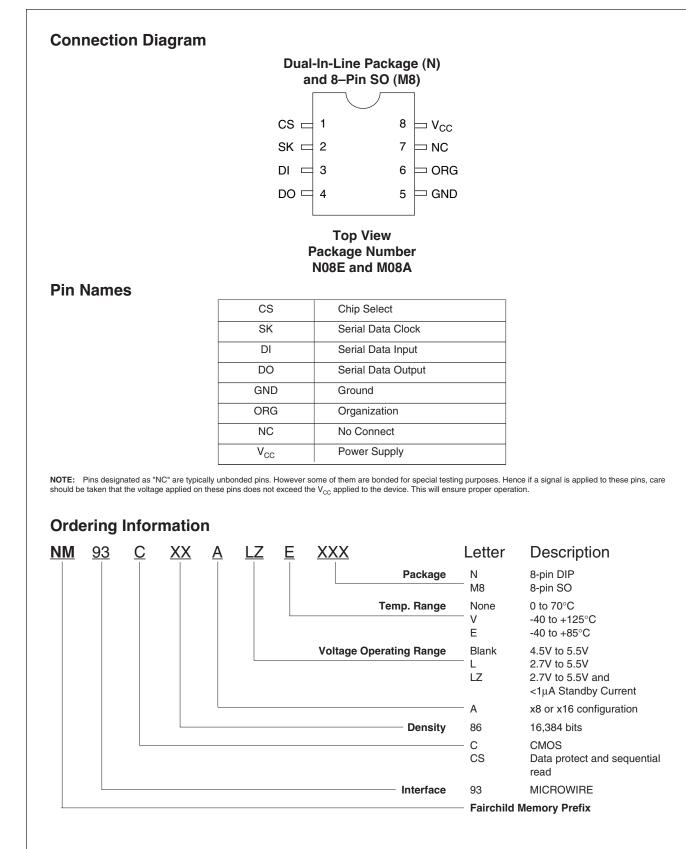

# **Pin Description**

#### Chip Select (CS)

This is an active high input pin to FM93C86A EEPROM (the device) and is generated by a master that is controlling the device. A high level on this pin selects the device and a low level deselects the device. All serial communications with the device is enabled only when this pin is held high. However this pin cannot be permanently tied high, as a rising edge on this signal is required to reset the internal state-machine to accept a new cycle. All activity on the SK, DI and DO pins are ignored while CS is held low.

#### Serial Clock (SK)

This is an input pin to the device and is generated by the master that is controlling the device. This is a clock signal that synchronizes the communication between a master and the device. All input information (DI) to the device is latched on the rising edge of this clock input, while output data (DO) from the device is driven from the rising edge of this clock input. This pin is gated by CS signal.

#### Serial Input (DI)

This is an input pin to the device and is generated by the master that is controlling the device. The master transfers Input information (Start bit, Opcode bits, Array addresses and Data) serially via this pin into the device. This Input information is latched on the rising edge of the SCK. This pin is gated by CS signal.

#### Serial Output (DO)

This is an output pin from the device and is used to transfer Output data via this pin to the controlling master. Output data is serially shifted out on this pin from the rising edge of the SCK. This pin is active only when the device is selected.

#### **Organization (ORG)**

This is an input pin to the device and is used to select the format of data (16-bit or 8-bit). If this pin is tied high, 16-bit format is selected, while if it is tied low, 8-bit format is selected. Depending on the format selected, FM93C86A requires 10-bit address field (for 16-bit data format) or 11-bit address field (for 8-bit data format). Refer Table 1 and Table 2 for more details. This pin is

#### Table 1. Instruction set (16-bit organization)

internally pulled-up to  $V_{\text{CC}}.$  Hence leaving this pin unconnected would default to 16-bit data format.

## **Microwire Interface**

A typical communication on the Microwire bus is made through the CS, SK, DI and DO signals. To facilitate various operations on the Memory array, a set of 7 instructions are implemented on FM93C86A. The format of each instruction is listed under Table 1 (for 16-bit format) and Table 2 (for 8-bit format).

#### Instruction

Each of the above 7 instructions is explained under individual instruction descriptions.

#### Start bit

This is a 1-bit field and is the first bit that is clocked into the device when a Microwire cycle starts. This bit has to be "1" for a valid cycle to begin. Any number of preceding "0" can be clocked into the device before clocking a "1".

#### Opcode

This is a 2-bit field and should immediately follow the start bit. These two bits (along with 2 MSB of address field) select a particular instruction to be executed.

#### **Address Field**

Depending on the selected organization, this is a 10-bit or 11-bit field and should immediately follow the Opcode bits. In FM93C86A, all 10 bits (or 11 bits) are used for address decoding during READ, WRITE and ERASE instructions. During all other instructions, the MSB 2 bits are used to decode instruction (along with Opcode bits).

#### **Data Field**

Depending on the selected organization, this is a 16-bit or 8-bit field and should immediately follow the Address bits. Only the WRITE and WRALL instructions require this field. MSB bit (D15 or D7) is clocked first and LSB bit (D0) is clocked last (both during writes as well as reads).

| Instruction | Start Bit | Opcode Field |    | Address Field |    |    |    |    |    | Data Field |    |    |        |

|-------------|-----------|--------------|----|---------------|----|----|----|----|----|------------|----|----|--------|

| READ        | 1         | 10           | A9 | A8            | A7 | A6 | A5 | A4 | A3 | A2         | A1 | A0 |        |

| WEN         | 1         | 00           | 1  | 1             | Х  | Х  | Х  | Х  | Х  | Х          | Х  | Х  |        |

| WRITE       | 1         | 01           | A9 | A8            | A7 | A6 | A5 | A4 | A3 | A2         | A1 | A0 | D15-D0 |

| WRALL       | 1         | 00           | 0  | 1             | Х  | Х  | Х  | Х  | Х  | Х          | Х  | Х  | D15-D0 |

| WDS         | 1         | 00           | 0  | 0             | Х  | Х  | Х  | Х  | Х  | Х          | Х  | Х  |        |

| ERASE       | 1         | 11           | A9 | A8            | A7 | A6 | A5 | A4 | A3 | A2         | A1 | A0 |        |

| ERAL        | 1         | 00           | 1  | 0             | Х  | Х  | Х  | Х  | Х  | Х          | Х  | Х  |        |

|             |           | it of gamzatio | .,  |               |    |    |    |    |    |    |    |            |    |       |

|-------------|-----------|----------------|-----|---------------|----|----|----|----|----|----|----|------------|----|-------|

| Instruction | Start Bit | Opcode Field   |     | Address Field |    |    |    |    |    |    |    | Data Field |    |       |

| READ        | 1         | 10             | A10 | A9            | A8 | A7 | A6 | A5 | A4 | A3 | A2 | A1         | A0 |       |

| WEN         | 1         | 00             | 1   | 1             | Х  | Х  | Х  | Х  | Х  | Х  | Х  | Х          | Х  |       |

| WRITE       | 1         | 01             | A10 | A9            | A8 | A7 | A6 | A5 | A4 | A3 | A2 | A1         | A0 | D7-D0 |

| WRALL       | 1         | 00             | 0   | 1             | Х  | Х  | Х  | Х  | Х  | Х  | Х  | Х          | Х  | D7-D0 |

| WDS         | 1         | 00             | 0   | 0             | Х  | Х  | Х  | Х  | Х  | Х  | Х  | Х          | Х  |       |

| ERASE       | 1         | 11             | A10 | A9            | A8 | A7 | A6 | A5 | A4 | A3 | A2 | A1         | A0 |       |

| ERAL        | 1         | 00             | 1   | 0             | Х  | X  | Х  | Х  | Х  | Х  | Х  | Х          | Х  |       |

#### Table 2. Instruction set (8-bit organization)

## **Functional Description**

A typical Microwire cycle starts by first selecting the device (bringing the CS signal high). Once the device is selected, a valid Start bit ("1") should be issued to properly recognize the cycle. Following this, the 2-bit opcode of appropriate instruction should be issued. After the opcode bits, the 10-bit (or 11-bit) address information should be issued. For certain instructions, some of the bits of this field are don't care values (can be "0" or "1"), but they should still be issued. Following the address information, depending on the instruction (WRITE and WRALL), 16-Bit data (or 8-Bit) is issued. Otherwise, depending on the instruction (READ), the device starts to drive the output data on the DO line. Other instructions perform certain control functions and do not deal with data bits. The Microwire cycle ends when the CS signal is brought low. However during certain instructions, falling edge of the CS signal initiates an internal cycle (Programming), and the device remains busy till the completion of the internal cycle. Each of the 7 instructions is explained in detail in the following sections.

#### 1) Read (READ)

READ instruction allows data to be read from a selected location in the memory array. Input information (Start bit, Opcode and Address) for this instruction should be issued as listed under Table 1 or Table 2. Upon receiving a valid input information, decoding of the opcode and the address is made, followed by data transfer from the selected memory location into a 16-bit serial-out shift register. This 16-bit data (or 8-bit data) is then shifted out on the DO pin. MSB of the data (D15 or D8) is shifted out first and LSB (DO) is shifted out last. A dummy-bit (logical 0) precedes this data output string. Output data changes are initiated on the rising edge of the SK clock. After reading the 16-bit (or 8-bit) data, the CS signal can be brought low to end the Read cycle. Refer *Read cycle diagram*.

#### 2) Write Enable (WEN)

When  $V_{CC}$  is applied to the part, it "powers up" in the Write Disable (WDS) state. Therefore, all programming operations must be preceded by a Write Enable (WEN) instruction. Once a Write Enable instruction is executed, programming remains enabled until a Write Disable (WDS) instruction is executed or  $V_{CC}$  is completely removed from the part. Input information (Start bit, Opcode and Address) for this WEN instruction should be issued as listed under Table 1 or Table 2. The device becomes write-enabled at the end of this cycle when the CS signal is brought low. Execution of a READ instruction is independent of WEN instruction. Refer *Write Enable cycle diagram*.

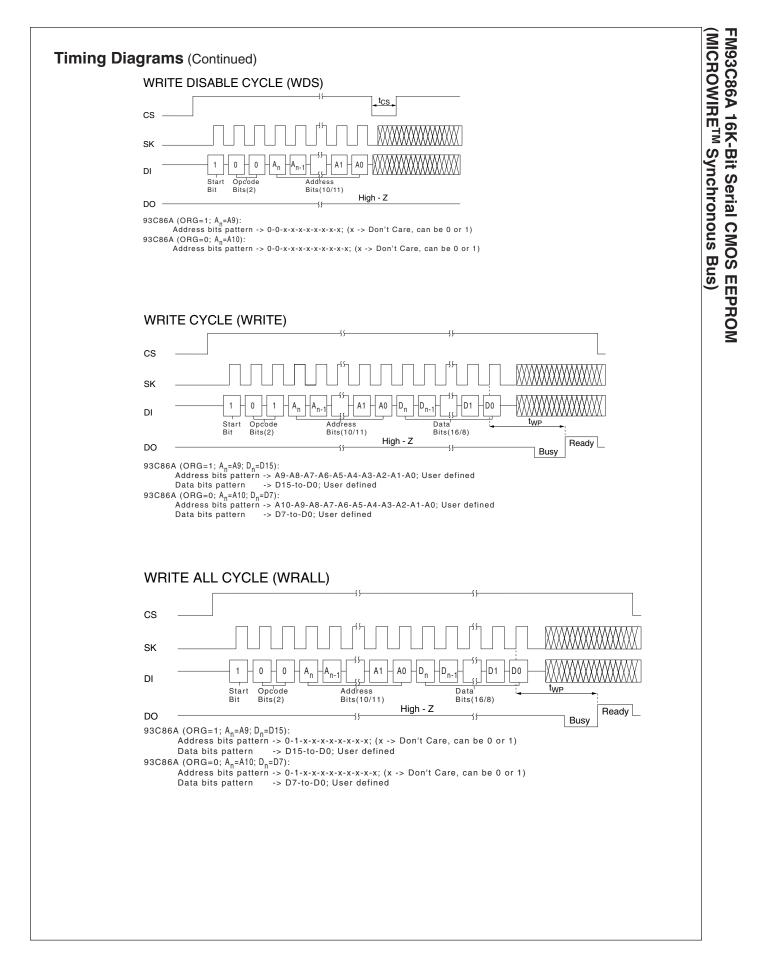

#### 3) Write (WRITE)

WRITE instruction allows write operation to a specified location in the memory with a specified data. This instruction is valid only when device is write-enabled (Refer WEN instruction).

Input information (Start bit, Opcode, Address and Data) for this WRITE instruction should be issued as listed under Table 1 or Table 2. The self-timed programming cycle starts with the clocking of the last data bit (DO). It takes  $t_{WP}$  time (refer appropriate DC and AC Electrical Characteristics table) for the internal programming cycle to finish. During this time, the device remains busy and is not ready for another instruction.

The status of the internal programming cycle can be polled at any time by bringing the CS signal high again, after  $t_{CS}$  interval. When CS signal is high, the DO pin indicates the READY/BUSY status of the chip. DO = logical 0 indicates that the programming is still in progress. DO = logical 1 indicates that the programming is finished and the device is ready for another instruction. It is not required to provide the SK clock during this status polling. While the device is busy, it is recommended that no new instruction be issued. Refer *Write cycle diagram*.

It is also recommended to follow this instruction (after the device becomes READY) with a Write Disable (WDS) instruction to safeguard data against corruption due to spurious noise, inadvertent writes etc.

#### 4) Write All (WRALL)

Write all (WRALL) instruction is similar to the Write instruction except that WRALL instruction will simultaneously program all memory locations with the data pattern specified in the instruction. This instruction is valid only when device is write-enabled (Refer WEN instruction).

Input information (Start bit, Opcode, Address and Data) for this WRALL instruction should be issued as listed under Table 1 or Table 2. The self-timed programming cycle starts with the clocking of the last data bit (DO). It takes  $t_{WP}$  time (Refer appropriate DC and AC Electrical Characteristics table) for the internal programming cycle to finish. During this time, the device remains busy and is not ready for another instruction. Status of the internal programming can be polled as described under WRITE instruction description. While the device is busy, it is recommended that no new instruction be issued. Refer *Write All cycle diagram*.

#### 5) Write Disable (WDS)

Write Disable (WDS) instruction disables all programming operations and should follow all programming operations. Executing this instruction after a valid write instruction would protect against accidental data disturb due to spurious noise, glitches, inadvertent writes etc. Input information (Start bit, Opcode and Address) for this WDS instruction should be issued as listed under Table 1 or Table 2. The device becomes write-disabled at the end of this cycle when the CS signal is brought low. Execution of a READ instruction is independent of WDS instruction. Refer *Write Disable cycle diagram*.

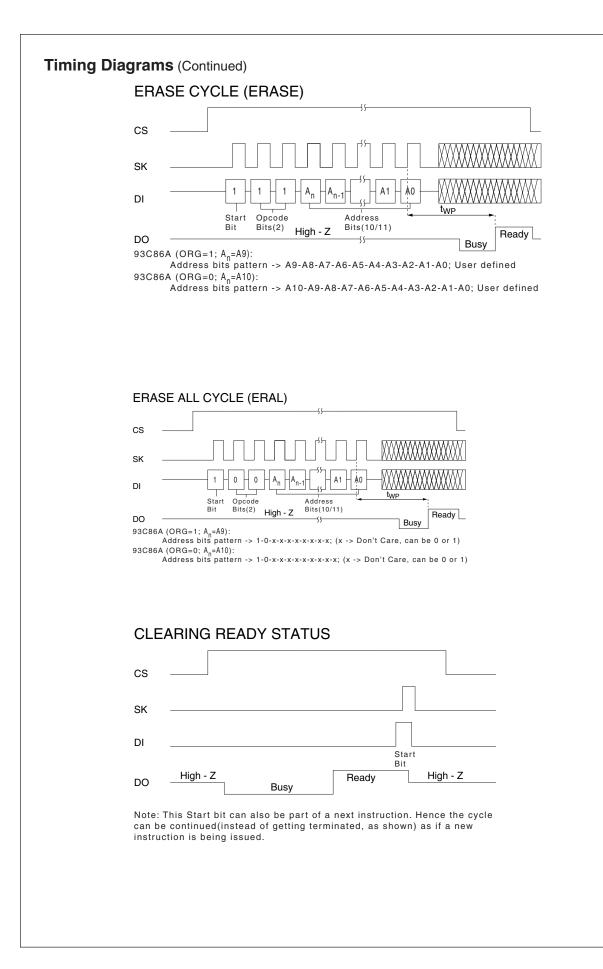

#### 6) Erase (ERASE)

The ERASE instruction will program all bits in the specified location to logical "1" state. Input information (Start bit, Opcode and Address) for this WDS instruction should be issued as listed under Table 1 or Table 2. The self-timed programming cycle starts with the clocking of the last data bit (DO). It takes  $t_{WP}$  time (Refer appropriate DC and AC Electrical Characteristics table) for the internal programming cycle to finish. During this time, the device remains busy and is not ready for another instruction. Status of the internal programming can be polled as described under WRITE instruction description. While the device is busy, it is recommended that no new instruction be issued. Refer *Erase cycle diagram.*

## 7) Erase All (ERAL)

The Erase all instruction will program all locations to logical "1" state. Input information (Start bit, Opcode and Address) for this WDS instruction should be issued as listed under Table 1 or Table

2. The self-timed programming cycle starts with the clocking of the last data bit (DO). It takes  $t_{WP}$  time (Refer appropriate DC and AC Electrical Characteristics table) for the internal programming cycle to finish. During this time, the device remains busy and is not ready for another instruction. Status of the internal programming can be polled as described under WRITE instruction description. While the device is busy, it is recommended that no new instruction be issued. Refer *Erase All cycle diagram*.

Note: The Fairchild CMOS EEPROMs do not require an "ERASE" or "ERASE ALL" instruction prior to the "WRITE" or "WRITE ALL" instruction, respectively. The "ERASE" and "ERASE ALL" instructions are included to maintain compatibility with earlier technology EEPROMs.

#### **Clearing of Ready/Busy status**

When programming is in progress, the Data-Out pin will display the programming status as either BUSY (low) or READY (high) when CS is brought high (DO output will be tri-stated when CS is low). To restate, during programming, the CS pin may be brought high and low any number of times to view the programming status without affecting the programming operation. Once programming is completed (Output in READY state), the output is 'cleared' (returned to normal tri-state condition) by clocking in a Start Bit. After the Start Bit is clocked in, the output will return to a tri-stated condition. When clocked in, this Start Bit can be the first bit in a command string, or CS can be brought low again to reset all internal circuits. Refer *Clearing Ready Status* diagram.

#### **Related Document**

Application Note: AN758 - Using Fairchild's MICROWIRE™ EE-PROM.

Fairchild Semiconductor

Kowloon. Hong Kong Tel; +852-2722-8338 Fax: +852-2722-8383

Hong Kong 8/F, Room 808, Empire Centre

68 Mody Road, Tsimshatsui East

#### FM93C86A Rev. C.1

Fairchild Semiconductor

Tel. 1-888-522-5372

Americas Customer Response Center

Fairchild Semiconductor

Fax

Tel:

Tel Tel: Tel +44 (0) 1793-856858

+49 (0) 8141-6102-0

+44 (0) 1793-856856 +33 (0) 1-6930-3696 +39 (0) 2-249111-1

Fairchild does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and Fairchild reserves the right at any time without notice to change said circuitry and specifications

Europe

Deutsch

English Français Italiano

www.fairchildsemi.com

Fairchild Semiconductor

Fairchild Semiconductor Japan Ltd. 4F, Natsume Bldg. 2-18-6, Yushima, Bunkyo-ku Tokyo, 113-0034 Japan Tel: 81-3-3818-8840 Fax: 81-3-3818-8841