# **CONSUMER MICROCIRCUITS LTD**

# **PRODUCT INFORMATION**

#### Features

- 1200 Baud FFSK Modem

- Meets Cellular and Trunked Radio Specifications

- Full Duplex 1200 Baud

- On-Chip Rx and Tx Bandpass Filters

- Clock Recovery and Carrier Detect Facilities

- Single 5 Volt CMOS Process

- Surface Mount or DIL Package Styles

Publication D/419/4 May 1987 Provisional Issue

- Applications Mobile and Cellular Radio Data Signalling

- NMT 450/900

- Band III

- Radiocom 2000

- ZVEI

- Personal Radio

- Portable Data Terminals

- General Purpose Applications

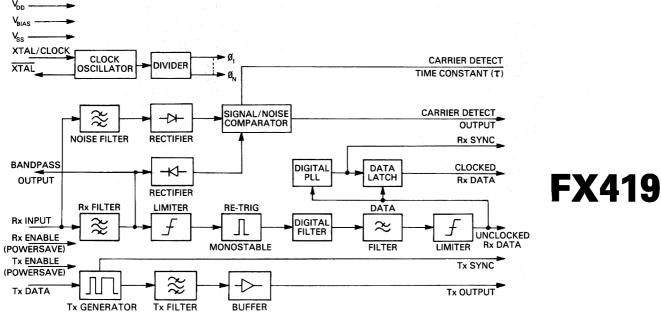

Fig. 1 Internal Block Diagram

#### Stief Description

The FX419 is a single chip CMOS LSI circuit which operates as a 1200 baud FFSK modem. The mark and space frequencies are 1200Hz and 1800Hz phase continuous and the frequency transitions occur at the zero crossing point. The transmitter and receiver will work independently, thus providing full duplex operation at 1200 baud. The baud rate, transmit mark and space frequencies, Tx synchronization and Rx synchronization are all derived from a crystal oscillator for high stability, and an external 1.008MHz

crystal is required for this purpose. The device includes circuitry for carrier detect and facility for the Rx clock recovery. An onboard switched capacitor 900Hz—2100Hz bandpass filter provides optimum carrier filtering. The use of switched capacitor analogue filters and digital signal processing results in excellent dynamic performance with few external components, the CMOS process and current saving techniques offer low standby supply current for portable battery powered applications.

## Pin Number Function

| DIL<br>FX419J | Quad<br>Plastic<br>FX419LG | PLCC<br>FX419LH |                                                                                                                                                                                                                                                                                                                                         |  |  |

|---------------|----------------------------|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 1             | 1                          | 1               | <b>Xtal/Clock:</b> The input to an on-chip inverter for use with a 1.008MHz xtal.<br>Alternatively, a 1.008MHz clock may be used.                                                                                                                                                                                                       |  |  |

| 2             | 2                          | 2               | Xtal: Output of on-chip inverter.                                                                                                                                                                                                                                                                                                       |  |  |

|               | _                          | 3               | No Connection: Leave open circuit.                                                                                                                                                                                                                                                                                                      |  |  |

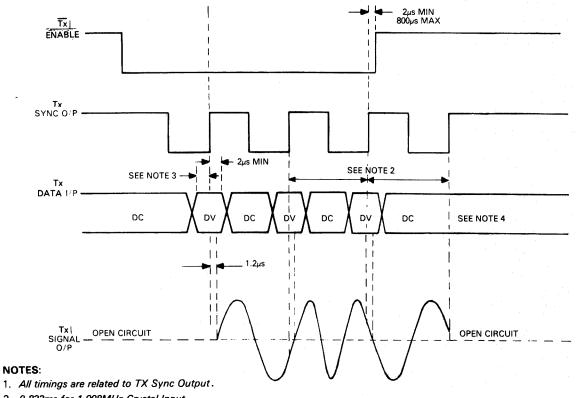

| 3             | 3                          | 4               | <b>Tx Sync O/P:</b> A 1200Hz squarewave used to synchronize the input of logic data and transmission of the FFSK signal <i>(See Fig. 5).</i>                                                                                                                                                                                            |  |  |

| 4             | 4                          | 5,6             | No Connection: Leave open circuit.                                                                                                                                                                                                                                                                                                      |  |  |

| 5             | 5                          | 7               | <b>Tx Signal O/P:</b> With transmitter disabled, this pin is set to a high impedance state. When transmitter is enabled, this pin outputs the 1200/1800Hz (140 step pseudo-sinewave) FFSK signal ( <i>See Fig. 5</i> ).                                                                                                                 |  |  |

| —             |                            | 8               | No Connection: Leave open circuit.                                                                                                                                                                                                                                                                                                      |  |  |

| 6             | 7                          | 9               | <b>Tx Data I/P:</b> Serial logic data to be transmitted, is input to this pin and synchronized by the "Tx Sync O/P" ( <i>See Fig. 5</i> ).                                                                                                                                                                                              |  |  |

| 7             | 8                          | 10              | <b>Tx Enable</b> : A logic '1' applied to this input will put the transmitter into powersave whilst forcing "Tx Sync O/P" to logic '1' and "Tx Signal O/P" to a high impedance state. A logic '0' will enable the transmitter ( <i>See Fig. 5</i> ). This pin is internally pulled to $V_{DD}$ .                                        |  |  |

| 8             | 9                          | 11              | <b>Bandpass O/P:</b> This is the output of the Rx 900-2100Hz bandpass filter. The output impedance of this pin is typically $10k\Omega$ and may require buffering prior to use.                                                                                                                                                         |  |  |

| 9             | 10                         | 12              | <b>Rx Enable</b> : A logic '0' applied to this input will put the receiver into powersave whilst forcing "Clocked Data O/P" and "Carrier Detect" to logic '0'. A logic '1' will enable the receiver ( <i>See Figures 2 and 6</i> ). "Rx Sync Out" may be logic '1' or '0' during powersave. This pin is internally pulled to $V_{DD}$ . |  |  |

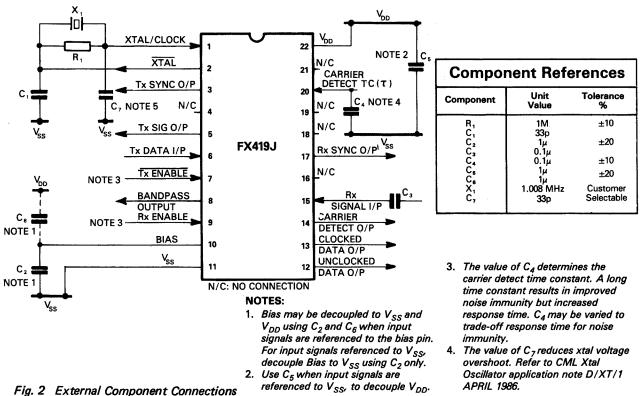

| 10            | 11                         | 13              | <b>Bias:</b> Provides bias internally and should be decoupled externally to $V_{SS}$ by a capacitor (See Fig 2).                                                                                                                                                                                                                        |  |  |

| 11            | 12                         | 14              | V <sub>ss</sub> : Negative supply.                                                                                                                                                                                                                                                                                                      |  |  |

| 12            | 13                         | 15              | <b>Unclocked Data O/P:</b> This pin outputs recovered asynchronous serial data from the receiver.                                                                                                                                                                                                                                       |  |  |

| 13            | 14                         | 16              | <b>Clocked Data O/P:</b> This pin outputs recovered synchronous serial data from the receiver and is internally latched out by a recovered clock appearing on the "Rx Sync O/P" pin ( <i>See Figures 2 and 6</i> ).                                                                                                                     |  |  |

| 14            | 15                         | 17              | <b>Carrier Detect:</b> This pin will output a logic '1' when an FFSK signal is being received.                                                                                                                                                                                                                                          |  |  |

|               |                            | 18,19           | No Connection: Leave open circuit.                                                                                                                                                                                                                                                                                                      |  |  |

| 15            | 16                         | 20              | <b>Rx Signal I/P</b> : This is the FFSK signal input pin for the receiver and should be decoupled via a capacitor $C_3$ .                                                                                                                                                                                                               |  |  |

| 16            | 17                         | 21              | No Connection: Leave open circuit.                                                                                                                                                                                                                                                                                                      |  |  |

| 17            | 18                         | 22              | <b>Rx Sync O/P:</b> This is a flywheel 1200Hz squarewave output which upon presentation of FFSK data signal is synchronised internally to the incoming data ( <i>See Figures 2 and 6</i> ).                                                                                                                                             |  |  |

| 18,19         | 19,20,21                   | 23,24,<br>25,26 | No Connection: Leave open circuit.                                                                                                                                                                                                                                                                                                      |  |  |

| 20            | 22                         | 27              | <b>Carrier Detect Time Constant (T):</b> This input forms part of the carrier detect integration function. The value of $C_4$ connected to this pin will affect the carrier detect response time and hence noise performance (See Fig. 2, Note 4).                                                                                      |  |  |

| 21            | 23                         |                 | No Connection: Leave open circuit.                                                                                                                                                                                                                                                                                                      |  |  |

| 22            | 24                         | 28              | V <sub>DD</sub> : Positive supply.<br>Note: Output Loading.<br>Large capacitive loads could cause the output pins of this device to oscillate. If capacitive loads in excess of 200pF are unavoidable, a resistor of typically <100Ω put in series with the load should minimise this effect.                                           |  |  |

Fig. 2 External Component Connections

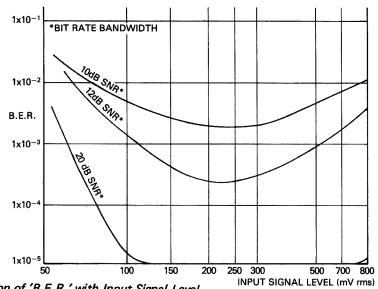

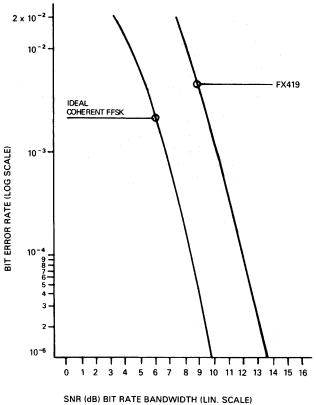

Fig. 3 Typical Variation of 'B.E.R.' with Input Signal Level

#### **Specification Absolute Maximum Ratings**

Exceeding the maximum rating can result in device damage. Operation of the device outside the operating limits is not implied.

| Supply voltage                  |                                   | -0.3V to 7.0V                      |

|---------------------------------|-----------------------------------|------------------------------------|

| Input voltage at any pin (ref \ | -0.3V to (V <sub>DD</sub> + 0.3V) |                                    |

| Output sink/source current (t   | 20mA                              |                                    |

| Operating temperature range:    | $-30^{\circ}$ C to + 85°C         |                                    |

|                                 | FX419LG/LH                        | $-30^{\circ}$ C to + 70°C          |

| Storage temperature range:      | FX419J                            | -55°C to +125°C                    |

|                                 | FX419LGLH                         | $-40^{\circ}$ C to $+85^{\circ}$ C |

| Maximum device dissipation:     | All versions 100mW                |                                    |

#### **Operating Limits**

$V_{DD} = +5V$ ,  $T_{amb} = 25^{\circ}C$ ,  $\emptyset = 1.008MHz$  (Xtal),  $\Delta f \phi = 0$ All characteristics measured using the standard test circuit (figure 4) with the following test parameters and is valid for all tests unless otherwise stated:

0dB reference 300mV rms Noise (band limited 5kHz gaussian white noise) SNR ratio measured in bit rate bandwidth (1200Hz)

| Characteristics                            | See Note | Min                 | Тур   | Max                | Unit             |

|--------------------------------------------|----------|---------------------|-------|--------------------|------------------|

| Static Characteristics                     |          |                     |       |                    |                  |

| Supply volts                               |          | 4.5                 | 5.0   | 5.5                | V                |

| Supply current: Rx (Enabled) Tx (Disabled) |          |                     | 3.6   | _                  | mA               |

| Rx (Enabled) Tx (Enabled)                  |          |                     | 4.5   | _                  | mA               |

| Rx (Disabled) Tx (Disabled)                |          | _                   | 650   |                    | μA               |

| Logic '1' level                            |          | 80%V <sub>DD</sub>  |       |                    | V                |

| Logic '0' level                            |          |                     | _     | 20%∨ <sub>DD</sub> | V                |

| Digital O/P Impedance                      |          | _                   | 4     | _ 00               | kΩ               |

| Analogue and Digital input impedance       |          | 100                 | _     |                    | kΩ               |

| Tx O/P impedance                           |          | -                   | 10    | _                  | kΩ               |

| On-chip crystal oscillator:                |          |                     |       |                    |                  |

| R <sub>in</sub>                            |          | 10                  | -     |                    | MΩ               |

| R <sub>out</sub>                           |          | 5                   | _     | 15                 | kΩ               |

| Inverter gain                              |          | 10                  |       | 20                 | dB               |

| Gain Bandwidth Product                     |          | 3 x 10 <sup>6</sup> | —     |                    |                  |

| Crystal frequency                          | 1        |                     | 1.008 | _                  | MHz              |

| Dynamic Characteristics                    |          |                     |       |                    |                  |

| Receiver:                                  |          |                     |       |                    |                  |

| Signal Input: Dynamic range (50dB SNR)     | 2, 3     | 100                 | 230   | 1000               | mV rms           |

| Bit Error Rate: 12dB SNR                   | 3        | _                   | 7.0   | <u> </u>           | 10 <sup>-4</sup> |

| 20dB SNR                                   | 3        | —                   | 1.0   |                    | 10 <sup>-8</sup> |

| Receiver Synchronization 12dB SNR:         | 6        |                     |       |                    |                  |

| Probability of bit 8 being correct         |          |                     | 0.99  |                    |                  |

| Probability of bit 16 being correct        |          |                     | 0.995 |                    |                  |

| Carrier Detect                             | 6        |                     |       |                    |                  |

| Probability of Carrier Detect being high:  |          |                     |       |                    |                  |

| 12dB SNR after bit 8                       | 4        |                     | 0.99  | 0.98               |                  |

| 12dB SNR after bit 16                      | 4        |                     | 0.999 | 0.995              |                  |

| 0dB noise                                  |          |                     |       | 0.01               |                  |

| Transmitter O/P                            |          |                     |       |                    |                  |

| Tx O/P level                               |          | _                   | 775   |                    | mV rms           |

| Output level variation 1200/1800Hz         |          | 0                   | _     | ±1.00              | dB               |

| O/P distortion                             |          | _                   | 3     | 5                  | %                |

| 3rd harmonic distortion                    |          | _                   | 2     | 3                  | %                |

| Logic '1' carrier frequency                | 5        | _                   | 1200  | _                  | Hz               |

| Logic '0' carrier frequency                | 5        | _                   | 1800  | _                  | Hz               |

| Isochronous distortion                     |          |                     |       |                    |                  |

| 1200Hz – 1800Hz                            |          | _                   | 25    | 40                 | μs               |

| 1800Hz – 1200Hz                            |          | _                   | 20    | 40                 | μs               |

Notes: 1. Crystal tolerance depends on system requirements.

- 3. SNR (Bit Rate Bandwidth).

- 4. See Fig. 2 Note 5.

- 5. Depending on crystal tolerance.

- 6. 101010 Pattern.

<sup>2.</sup> See Fig. 3.

- 2. 0.833ms for 1.008MHz Crystal Input.

- 3. 2µs Min + Crystal tolerance.

- 4. DC = Don't Care, DV = Data Valid.

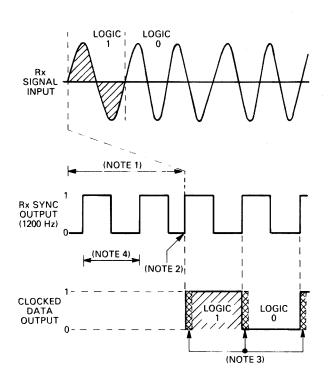

#### NOTES:

- 1. Internal Delay-typ 1.5ms.

- 2. From freely running to Sync in 8 data bits (See spec).

3. Undetermined state – 2µs max.

4. Min. 800µs-Max. 865µs.

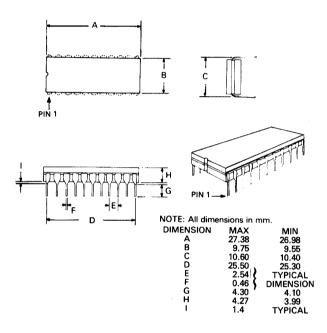

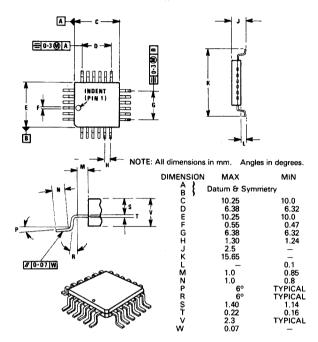

#### Padden Conserve

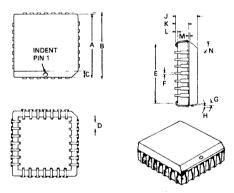

The FX419J, the cerdip package, is illustrated in *Figure 8*. The 'LG' version is shown in *Figure 9*, and the 'LH' version in *Figure 10*. Both 'LG' and 'LH' packages are supplied in conductive trays for handling convenience. To allow complete identification, the FX419LG and LH packages have an indent spot adjacent to Pin 1 and a chamfered corner between Pins 3 and 4 for LG package, between Pins 4 and 5 for LH package. Pins number anti-clockwise when viewed from the top (indent side).

- FX419J 22-pin Cerdip DIL FX419LG 24-pin quad plastic encapsulated, bent and cropped.

- FX419LH 28-lead Plastic leaded chip carrier.

#### Planting Pressentions

The FX419J/LG/LH is a CMOS LSI circuit which includes input protection. However, precautions should be taken to prevent static discharges which may cause damage.

- Fride Alexandre Ale

NOTE: All dimensions in mm. Angles in degrees.

| DIMENSION | MAX.      | MIN.    |  |  |

|-----------|-----------|---------|--|--|

| A         | 11.6      | 11.4    |  |  |

| в         | 12.6      | 12.3    |  |  |

| č         | 1.1 x 45° | TYPICAL |  |  |

| Ď         | 1.3       | TYPICAL |  |  |

| E         | 10.8      | 10.0    |  |  |

| F         | 0.46      | TYPICAL |  |  |

| G         | 7°        | 3°      |  |  |

| Ĥ         | 7°        | 30      |  |  |

| Ĵ         | 4.5       | 4.3     |  |  |

| ĸ         | 2.5       | TYPICAL |  |  |

| i.        | 1.1       | 0.5     |  |  |

| M         | 0.59      | TYPICAL |  |  |

| N         | 45°       | TYPICAL |  |  |

|           |           |         |  |  |

CML does not assume any responsibility for the use of any circuitry described. No circuit patent licences are implied and CML reserves the right at any time without notice to change the said circuitry.

### **CML Product Data**

In the process of creating a more global image, the three standard product semiconductor companies of CML Microsystems Plc (*Consumer Microcircuits Limited (UK), MX-COM, Inc (USA) and CML Microcircuits (Singapore) Pte Ltd)* have undergone name changes and, whilst maintaining their separate new names (*CML Microcircuits (UK) Ltd, CML Microcircuits (USA) Inc and CML Microcircuits (Singapore) Pte Ltd*), now operate under the single title CML Microcircuits.

These companies are all 100% owned operating companies of the CML Microsystems Plc Group and these changes are purely changes of name and do not change any underlying legal entities and hence will have no effect on any agreements or contacts currently in force.

#### **CML Microcircuits Product Prefix Codes**

Until the latter part of 1996, the differentiator between products manufactured and sold from MXCOM, Inc. and Consumer Microcircuits Limited were denoted by the prefixes MX and FX respectively. These products use the same silicon etc. and today still carry the same prefixes. In the latter part of 1996, both companies adopted the common prefix: CMX.

This notification is relevant product information to which it is attached.

Company contact information is as below:

Oval Park, Langford, Maldon, Essex, CM9 6WG, England Tel: +44 (0)1621 875500 Fax: +44 (0)1621 875600 uk.sales@cmlmicro.com www.cmlmicro.com

COMMUNICATION SEMICONDUCTORS

4800 Bethania Station Road, Winston-Salem, NC 27105, USA Tel: +1 336 744 5050, 0800 638 5577 Fax: +1 336 744 5054 us.sales@cmlmicro.com www.cmlmicro.com

No 2 Kallang Pudding Road, 09-05/ 06 Mactech Industrial Building, Singapore 349307 Tel: +65 7450426 Fax: +65 7452917 sg.sales@cmlmicro.com www.cmlmicro.com