## **User's Guide**

# GDM12864A LCM

(Liquid Crystal Display Module)

XIAMEN OCULAR LCD DEVICES CO., LTD. ?????????????

South 5F., Guang Xia Bldg. Torch Hi-tech Develop. Area, Xiamen, China 361006 Tel: (0592)6026045 Fax: (0592)6026021

## **Contents**

| Chapter 1. Introduction to ITM 1            | -1286      | 64A LCI | VI       |     |    |

|---------------------------------------------|------------|---------|----------|-----|----|

| Features                                    |            |         |          | 1   |    |

| Mechanical Specifications                   |            |         | 1        | -   |    |

| Temperature Characteristics                 |            |         | -        | 1   |    |

| External Dimensions                         |            |         | 2        |     |    |

| Application Diagram                         |            |         | 3        |     |    |

| Electro- Optical characteristics            |            |         | 4        |     |    |

| Interface Pin Connections                   |            |         | 5        |     |    |

| Electrical Absolute Maximum Ratin           | ng (KS     | (0107B) | 6        |     |    |

| DC Electrical Characteristics (KS0)         |            |         | 6        |     |    |

| Electrical Absolute Maximum Ratin           |            |         | 7        |     |    |

| DC Electrical Characteristics (KS0)         |            | 01002)  | 7        |     |    |

| Chapter 2. Driver IC (KS0107B) Introduction | ) Fun<br>8 | ction D | escript) | ion | 8  |

| AC Characteristics                          | 9          |         |          |     |    |

| Master Mode                                 |            | 9       |          |     |    |

| Slave Mode                                  | 10         |         |          |     |    |

| Functional Description                      |            | 11      |          |     |    |

| RC Oscillator                               | 11         |         |          |     |    |

| Timing Generation Circuit                   | 11         |         |          |     |    |

| Data Shift & Phase Select Control           | 12         |         |          |     |    |

| Chapter 3. Driver IC (KS0108B)              | ) Fun      | ction D | escript  | ion | 13 |

| Introduction                                | 13         |         |          |     |    |

| AC Characteristics                          | 13         |         |          |     |    |

16

19

Operating Principles & Methods

Display Control Instruction

#### CHAPTER 1

## Introduction to ITM-12864A LCM

ITM-12864A is a dot matrix graphic LCD module which is fabricated by low power COMS technology. It can display 128\*64 dots size LCD panel using a 128\*64 bit-mapped Display Data RAM (DDRAM). It interfaces with an 8-bit microprocessor.

#### **Features**

Display format: 128\*64 dots matrix graphic

STN yellow-green mode

Easy interface with 8-bit MPU

Low power consumption

LED back-light

Viewing angle: 6 O'clock

Driving method: 1/64 duty, 1/6.7 bias LCD driver IC: KS0108B(2?)? KS0107B

Connector: Zebra

### **Mechanical Specifications**

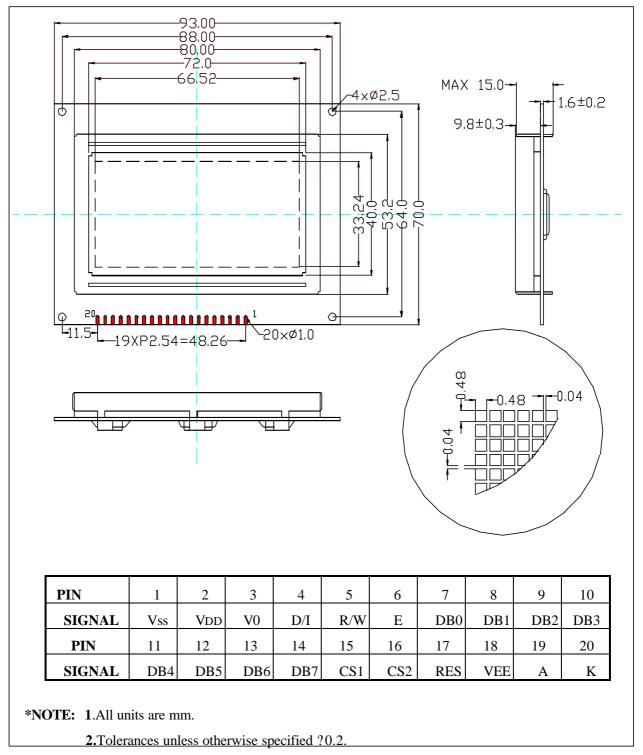

| Item                 | Dimension      | Unit |

|----------------------|----------------|------|

| Module Size(W*H*T)   | 93.0*70.0*10.0 | mm   |

| Viewing Area(W*H)    | 72.0*40.0      | mm   |

| Number of Dots       | 128.0*64.0     | PCS  |

| Dot Size(W*H)        | 0.48*0.48      | mm   |

| Dot Pitch(W*H)       | 0.52*0.52      | mm   |

| Module Size With B/L | 93.0*70.0*15.0 | mm   |

## **Temperature Characteristics**

| Parameter             | Symbol | Rating    | Unit |

|-----------------------|--------|-----------|------|

| Operating temperature | Topr   | 0 ~ +50   | ?    |

| Storage temperature   | Tstg   | -20 ~ +70 | ?    |

**Figure 1. External Dimensions**

INTECH LCD MODULE ITM-12864A

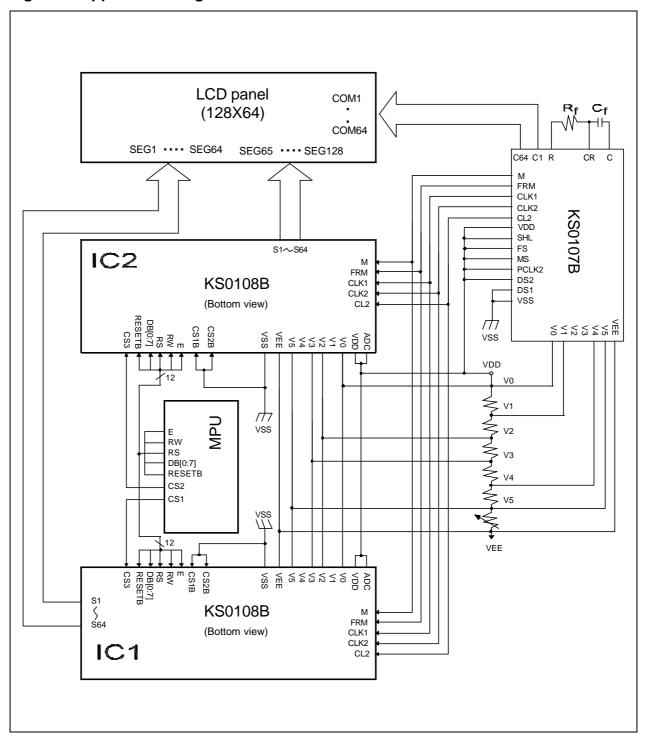

Figure 2. Application Diagram

#### \*Note

1/64 duty, 1/6.7 bias  $V_{DD} > V1 > V2 > V3 > V4 > V5 > V_{EE}$

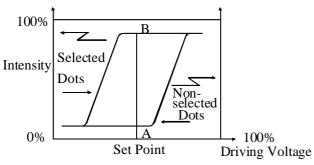

## **Electro-Optical characteristics**

TN Type (Twisted Nematic )

| Item                 | Symbol                         | Min. | Typ. | Max. | Unit | Condition                  | Note |

|----------------------|--------------------------------|------|------|------|------|----------------------------|------|

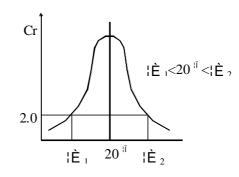

| Viewing Angle        | ? <sub>2</sub> -? <sub>1</sub> | 40   | -    | -    | deg. | Cr = 2.0                   | 1,2  |

| Contrast Ratio       | Cr                             | -    | 4    | -    | -    | ?= $20^{?}$<br>f = $0^{?}$ | 3    |

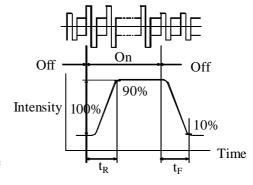

| Response Time (rise) | $t_{R}$                        | -    | 110  | -    | ms   | ?=20?<br>f = 0?            | 4    |

| Response Time (fall) | $t_{\mathrm{F}}$               | -    | 110  | -    | ms   | ?=20?<br>f = 0?            | 4    |

STN Type (Super Twisted Nematic )

| STIV Type (Super Twisted Remaile) |                                |           |      |      |      |                 |      |  |

|-----------------------------------|--------------------------------|-----------|------|------|------|-----------------|------|--|

| Item                              | Symbol                         | Min.      | Typ. | Max. | Unit | Condition       | Note |  |

| Viewing Angle                     | ? <sub>2</sub> -? <sub>1</sub> | 70<br>-90 | -    | +90  | deg. | Cr = 2.0        | 1,2  |  |

| Contrast Ratio                    | Cr                             | -         | 4    | -    | -    | ?=20?<br>f = 0? | 3    |  |

| Response Time (rise)              | $t_R$                          | -         | 110  | -    | ms   | ?=20?<br>f = 0? | 4    |  |

| Response Time (fall)              | $t_{\mathrm{F}}$               | -         | 110  | -    | ms   | ?=20?<br>f = 0? | 4    |  |

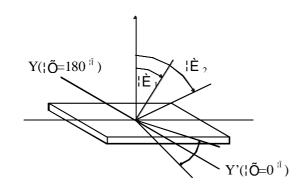

## 1. Definition of angle ¦È& ¦Õ

## 2. Definition of viewing angle |È 1 & |Õ 2

## 3. Definition of contrast Cr

## 4. Definition of optical response

$Cr = (A/B)^p$  Negative : P = -1Positive : P = +1

## **Interface Pin Connections**

| Pin      | Symbol     | I/O Type             | Descrip                                                                                                               | tion                                             |                             |                                                                                                       |  |  |  |  |

|----------|------------|----------------------|-----------------------------------------------------------------------------------------------------------------------|--------------------------------------------------|-----------------------------|-------------------------------------------------------------------------------------------------------|--|--|--|--|

| No.      | Symbol     | 1/O Type             | Descrip                                                                                                               | поп                                              |                             |                                                                                                       |  |  |  |  |

| 1        | VSS        | Supply               | Ground                                                                                                                |                                                  |                             |                                                                                                       |  |  |  |  |

| 2        | VDD        | Supply               | Power supply                                                                                                          |                                                  |                             |                                                                                                       |  |  |  |  |

| 3        | V0         | Supply               |                                                                                                                       | LCD driver supply voltage                        |                             |                                                                                                       |  |  |  |  |

| 4        | D/I        | ~ <sub>F</sub> F - J |                                                                                                                       | Data input/output pin of internal shift register |                             |                                                                                                       |  |  |  |  |

|          |            |                      | MS                                                                                                                    | SHL                                              | DIO1                        | DIO2                                                                                                  |  |  |  |  |

|          |            |                      | Н                                                                                                                     | Н                                                | Output                      | Output                                                                                                |  |  |  |  |

|          |            |                      | Н                                                                                                                     | L                                                | Output                      | Output                                                                                                |  |  |  |  |

|          |            |                      | L                                                                                                                     | Н                                                | Input                       | Output                                                                                                |  |  |  |  |

|          |            |                      | L                                                                                                                     | L                                                | Output                      | Input                                                                                                 |  |  |  |  |

| 5        | R/W        |                      | Read or                                                                                                               | Write                                            | -                           | -                                                                                                     |  |  |  |  |

|          |            |                      | RW<br>H<br>L                                                                                                          | Data ap<br>E= H C<br>Display                     | CS1B=L,CS2B<br>data DB[7:0] | :0] and can be read by the CPU while =L and CS3=H. can be written at falling edge of E B=L and CS3=H. |  |  |  |  |

| 6        | Е          |                      | Enable s                                                                                                              |                                                  | ,                           |                                                                                                       |  |  |  |  |

|          |            |                      | E Description H Read data in DB[7:0] appears while E= "High". L Display data DB[7:0] is latched at falling edge of E. |                                                  |                             |                                                                                                       |  |  |  |  |

| 7        | DB0        | I/O                  | Data bus                                                                                                              | 5 [0~7]                                          |                             |                                                                                                       |  |  |  |  |

| 8        | DB1        |                      | Bi-directio                                                                                                           | nal data bu                                      | S                           |                                                                                                       |  |  |  |  |

| 9        | DB2        |                      |                                                                                                                       |                                                  |                             |                                                                                                       |  |  |  |  |

| 10       | DB3        |                      |                                                                                                                       |                                                  |                             |                                                                                                       |  |  |  |  |

| 11       | DB4        |                      |                                                                                                                       |                                                  |                             |                                                                                                       |  |  |  |  |

| 12       | DB5        |                      |                                                                                                                       |                                                  |                             |                                                                                                       |  |  |  |  |

| 13       | DB6        |                      |                                                                                                                       |                                                  |                             |                                                                                                       |  |  |  |  |

| 14       | DB7        | I                    | Chin cole                                                                                                             | ation                                            |                             |                                                                                                       |  |  |  |  |

| 15<br>16 | CS1<br>CS2 | 1                    | Chip sele                                                                                                             | ection                                           |                             |                                                                                                       |  |  |  |  |

| 10       | C52        |                      | When C                                                                                                                | S1=H,CS                                          | S2=L, select                | IC1                                                                                                   |  |  |  |  |

|          |            |                      | When C                                                                                                                | S1=L,CS                                          | 2=H, select                 | : IC2                                                                                                 |  |  |  |  |

| 17       | RESETB     | I                    | Reset sig                                                                                                             |                                                  |                             |                                                                                                       |  |  |  |  |

|          |            |                      | When R                                                                                                                | STB=L                                            |                             |                                                                                                       |  |  |  |  |

|          |            |                      | ? 1? ON/                                                                                                              | OFF regi                                         | ster become                 | es set by 0.(display off)                                                                             |  |  |  |  |

|          |            |                      | ? 2? displa                                                                                                           | ıy start line                                    | register becor              | nes set by 0 (Z-address 0 set, display                                                                |  |  |  |  |

|          |            |                      | fro                                                                                                                   | m line 0)                                        |                             |                                                                                                       |  |  |  |  |

|          |            |                      | ? 3? After                                                                                                            | releasing r                                      | eset, this cond             | lition can be changed only by                                                                         |  |  |  |  |

|          |            |                      | ins                                                                                                                   | struction.                                       |                             |                                                                                                       |  |  |  |  |

| 18       | VEE        | Power                | VEE                                                                                                                   | is connec                                        | ted by the sam              | e voltage.                                                                                            |  |  |  |  |

| 19       | A          |                      | Bacl                                                                                                                  | k-light anoc                                     | le                          |                                                                                                       |  |  |  |  |

| 20       | K          |                      | Bacl                                                                                                                  | k-light cath                                     | ode                         |                                                                                                       |  |  |  |  |

|          |            |                      |                                                                                                                       |                                                  |                             |                                                                                                       |  |  |  |  |

## **Electrical Absolute Maximum Ratings (KS0107B)**

| Parameter             | Symbol            | Rating                         | Unit | Note |

|-----------------------|-------------------|--------------------------------|------|------|

| Operating voltage     | $V_{\mathrm{DD}}$ | -0.3 ~ +7.0                    | V    | *1   |

| Supply voltage        | $V_{EE}$          | $V_{DD}$ -19.0 ~ $V_{DD}$ +0.3 | V    | *4   |

| Driver supply voltage | $V_{\rm B}$       | $-0.3 \sim V_{DD} + 0.3$       | V    | *1,2 |

|                       | $V_{ m LCD}$      | $V_{EE}$ -0.3 ~ $V_{DD}$ +0.3  | V    | *3,4 |

#### \*Notes:

- \*1. Based on  $V_{SS} = 0V$

- \*2. Applies to input terminals and I/O terminals at high impedance. (Except V0L, V1L, V4L, and V5L)

- \*3. Applies to V0L, V1L, V4L, and V5L.

- \*4. Voltage level:  $V_{DD}$ =V0=V1=V2=V3=V4=V5= $V_{EE}$

### DC Electrical Characteristics(KS0107B)

(VDD= 4.5 to 5.5V, VSS=0V, VDD-VEE=8~17V, Ta= -30 to +85?)

| Item                  | Symbo             | Condition                                     | Min.                 | Typ. | Max.              | Unit | Note |

|-----------------------|-------------------|-----------------------------------------------|----------------------|------|-------------------|------|------|

|                       | 1                 |                                               |                      |      |                   |      |      |

| Operating voltage     | $V_{\mathrm{DD}}$ | -                                             | 4.5                  | -    | 5.5               | V    |      |

| Input voltage         | $V_{IH}$          | -                                             | $0.7_{\mathrm{VDD}}$ | -    | $V_{\mathrm{DD}}$ |      | *1   |

|                       | $V_{IL}$          | -                                             | Vss                  | -    | $0.3V_{D}$        |      |      |

|                       |                   |                                               |                      |      | D                 | _    |      |

| output voltage        | $V_{OH}$          | $I_{OH}$ = -0.4mA                             | VDD-0.4              | -    | -                 | _    | *2   |

|                       | $V_{OL}$          | $I_{OL} = 0.4 \text{mA}$                      | -                    | -    | 0.4               |      |      |

| Input leakage current | $I_{LKG}$         | $V_{IN} = V_{DD} \sim V_{SS}$                 | -1.0                 | -    | +1.0              | ⊳A   | *1   |

| OSC Frequency         | fosc              | Rf=47k <b>O±</b> 2%                           | 315                  | 450  | 585               | kHz  |      |

|                       |                   | Cf=20pF±5%                                    |                      |      |                   |      | _    |

| On Resistance         | $R_{ONS}$         | $V_{\mathrm{DD}}$ - $V_{\mathrm{EE}}$ =17 $V$ | -                    | -    | 1.5               | kO   |      |

| (Vdiv-Ci)             |                   | Load current±150⊳A                            |                      |      |                   |      |      |

| Operating current     | $I_{DD1}$         | Master mode                                   | -                    | -    | 1.0               | mA   | *3   |

|                       |                   | 1/128 Duty                                    |                      |      |                   | _    |      |

|                       | $I_{DD2}$         | Master mode                                   | -                    | -    | 0.2               |      | *4   |

|                       |                   | 1/128 Duty                                    |                      |      |                   | _    |      |

| Supply Current        | IEE               | Master mode                                   | -                    | -    | 0.1               |      | *5   |

|                       |                   | 1/128 Duty                                    |                      |      |                   |      |      |

| Operating             | fop1              | Master mode                                   | 50                   | -    | 600               | kHz  |      |

|                       |                   | External Duty                                 |                      |      |                   |      | _    |

| Frequency             | fop2              | Slave mode                                    | 0.5                  | -    | 1500              |      |      |

#### **Notes**

- \*1. Applies to input terminals FS, DS1, DS2, CR, SHL, MS and PCLK2 and I/O terminals DIO1, DIO2, M, and CL2 in the input state.

- \*2. Applies to output terminals CLK1, CLK2 and FRM and I/O terminals DIO1, DIO2, M , and CL2 in the output state.

- \*3. This value is specified about current flowing through Vss.

Internal oscillation circuit: Rf=47kO, cf=20pF

Each terminals of DS1, DS2, FS, SHL, and MS is connected to VDD and out is no load.

\*4. This value is specified about current flowing through Vss.

Each terminals is DS1, DS2, FS, SHL, PCLK2 and CR is connected to VDD,MS is connected to Vss and CL2, M, DIO1 is external clock.

\*5. This value is specified about current flowing through VEE, Don't connect to VLCD (V1~V5).

## **Electrical Absolute Maximum Ratings(KS0108B)**

| Parameter             | Symbol            | Rating                         | Unit | Note |

|-----------------------|-------------------|--------------------------------|------|------|

| Operating voltage     | $V_{\mathrm{DD}}$ | -0.3 ~ +7.0                    | V    | *1   |

| Supply voltage        | $V_{EE}$          | $V_{DD}$ -19.0 ~ $V_{DD}$ +0.3 | V    | *4   |

| Driver supply voltage | $V_{\mathrm{B}}$  | $-0.3 \sim V_{DD} + 0.3$       | V    | *1,3 |

|                       | $V_{ m LCD}$      | $V_{EE}$ -0.3 ~ $V_{DD}$ +0.3  | V    | *2   |

#### \*Notes:

- \*1. Based on  $V_{SS} = 0V$

- \*2. Applies the same supply voltage to VEE. VLCD=VDD-VEE.

- \*3. Applies to M, FRM, CLK1,CLK2, CL, RESETB, ADC, CS1B, CS2B,CS3, E, R/W, RS and DB0~DB7.

- \*4. Applies V0L, V2L, V3L and V5L.

Voltage level:  $V_{DD}=V0=V1=V2=V3=V4=V5=V_{EE}$

### DC Electrical Characteristics(KS0108B)

(VDD= 4.5 to 5.5V, VSS=0V, VDD-VEE=8~17V, Ta= -30 to +85?)

| Item                  | Symbol             | Condition                     | Min.                 | Тур. | Max.              | Unit | Note |

|-----------------------|--------------------|-------------------------------|----------------------|------|-------------------|------|------|

| Operating voltage     | $V_{\mathrm{DD}}$  | -                             | 4.5                  | -    | 5.5               | V    |      |

| Input High voltage    | $V_{\rm IH1}$      | -                             | $0.7_{\mathrm{VDD}}$ | -    | $V_{\mathrm{DD}}$ | _    | *1   |

|                       | $V_{\rm IH2}$      | -                             | 2.0                  | -    | $V_{\mathrm{DD}}$ | _    | *2   |

| Input Low voltage     | $V_{\rm IL1}$      | -                             | 0                    | -    | $0.3V_{\rm D}$    | _    | *1   |

|                       |                    |                               |                      |      | D                 | _    |      |

|                       | $V_{\rm IL2}$      | -                             | 0                    | -    | 0.8               |      | *2   |

| Output High Voltage   | $V_{OH}$           | $I_{OH}$ = -0.2mA             | 2.4                  | -    | -                 | _    | *3   |

| Output Low Voltage    | $V_{OL}$           | $I_{OL} = 1.6 \text{mA}$      | -                    | -    | 0.4               |      | *3   |

| Input leakage current | $I_{LKG}$          | $V_{IN} = V_{SS} \sim V_{DD}$ | -1.0                 | -    | +1.0              | ⊳A   | *4   |

| Three-state (OFF)     | Itsl               | $V_{IN} = V_{SS} \sim V_{DD}$ | -5.0                 | -    | 5.0               |      | *5   |

| Input Current         |                    |                               |                      |      |                   |      |      |

| Driver Input leakage  | Idil               | $V_{IN} = V_{EE} \sim V_{DD}$ | -2.0                 |      | 2.0               |      | *6   |

| current               |                    |                               |                      |      |                   |      |      |

| On Resistance         | $R_{ONS}$          | $V_{DD}$ - $V_{EE}$ =15 $V$   | -                    | -    | 7.5               | kO   | *8   |

| (Vdiv-Ci)             |                    | Load current±100⊳A            |                      |      |                   |      |      |

| Operating current     | $I_{DD1}$          | During Display                | -                    | -    | 0.1               | mA   | *7   |

|                       | $I_{\mathrm{DD2}}$ | During Access                 | -                    | -    | 0.5               |      | *7   |

|                       |                    | Access Cycle=1MHz             |                      |      |                   |      |      |

#### **Notes**

- \*1. CL, FRM, M, RSTB, CLK1, CLK2

- \*2. CS1B, CS2B, CS3, E, R/W, RS, DB0~DB7

- \*3. DB0~DB7

- \*4. Except DB0~DB7

- \*5. DB0~DB7 at high impedance

- \*6. V0, V1, V3, V3, V4, V5

- \*7. 1/64 duty, FCLK=250KHZ, Frame Frequency=70HKZ, Output: No Load

- \*8. VDD-VEE=15.5V V0L>V2L>= VDD-2/7(VDD-VEE)>V3L= VEE+2/7(VDD-VEE)>V5L

**CHAPTER 2**

## **Driver IC Function Description**

KS0107 Driver IC 64COM graphic driver for dot matrix LCD

#### Introduction

The KS0107B is an :CD driver LSI with 64 channel outputs for dot matrix liquid crystal graphic display systems.

This device provides 64 shift registers and 64 output drivers.

It generates the timing signal to control the KS0108B (64 channel segment drover.).

The KS0107B is fabricated by low power CMOS high voltage process technology, and is composed of the liquid crystal display system in combination with the KS0108B (64 channel segment drover.).

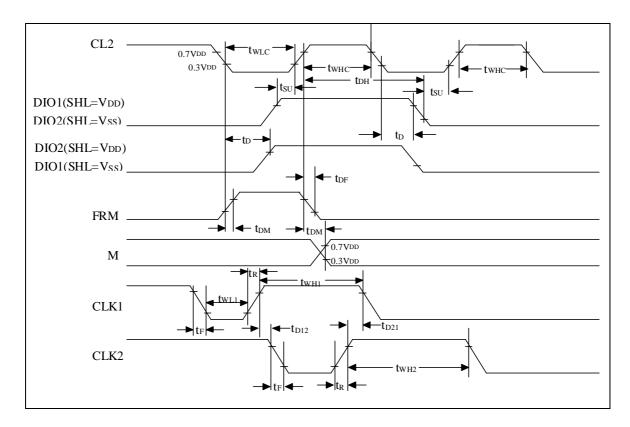

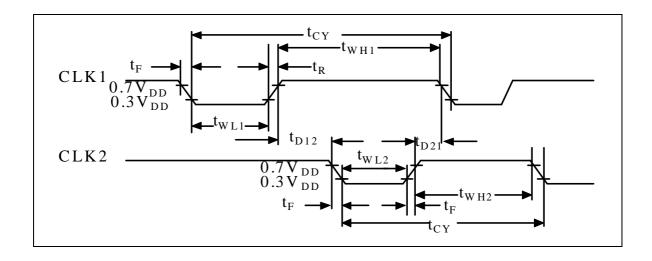

## AC Characteristics (VDD=4.5~5.5V, Ta=-30?~+85?)

## 1. Master mode (MS=VDD, PCLK2=VDD, Cf=20pF, Rf=47KO)

| Characteristic             | Symbol                         | Min  | Тур | Max | Unit |

|----------------------------|--------------------------------|------|-----|-----|------|

| Data Setup Time            | t <sub>SU</sub>                | 20   | -   | -   |      |

| Data Hold Time             | $t_{DH}$                       | 40   | -   | -   | _    |

| Data Delay Time            | $t_D$                          | 5    | -   | -   | _    |

| FRM Delay Time             | $t_{DF}$                       | -2   | -   | 2   | ⊳s   |

| M Delay Time               | $t_{DM}$                       | -2   | -   | 2   | _    |

| CL2 Low Level Width        | $t_{WLC}$                      | 35   | -   | -   | _    |

| CL2 High Level Width       | $t_{WHC}$                      | 35   | -   | -   |      |

| CLK1 Low Level Width       | $t_{WL1}$                      | 700  | -   | -   | _    |

| CLK2 Low Level Width       | $t_{WL2}$                      | 700  | -   | -   | _    |

| CLK1 High Level Width      | $t_{WH1}$                      | 2100 | -   | -   | _    |

| CLK2 High Level Width      | $t_{WH2}$                      | 2100 | -   | -   | ns   |

| CLK1-CLK2 Phase Difference | t <sub>D12</sub>               | 700  | -   | -   | _    |

| CLK2-CLK1 Phase Difference | t <sub>D21</sub>               | 700  | -   | -   | _    |

| CLK1,CLK2 Rise/Fall Time   | t <sub>R</sub> /t <sub>F</sub> | -    | -   | 150 |      |

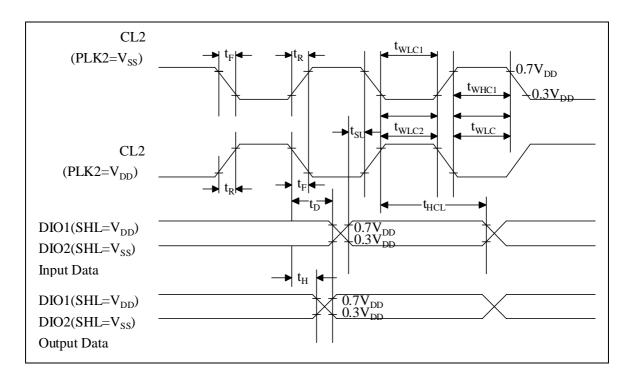

## Slave mode (MS=V<sub>SS</sub>)

| Characteristics       | Symbol                | Min | Тур | Max | Unit    | Note                  |

|-----------------------|-----------------------|-----|-----|-----|---------|-----------------------|

| CL2 Low Level Width   | t <sub>WLC1</sub>     | 450 | -   | -   |         | PCLK2=V <sub>SS</sub> |

| CL2 High Level Width  | t <sub>WHC1</sub>     | 150 | -   | -   |         | PCLK2=V <sub>SS</sub> |

| CL2 Low Level Width   | $t_{WLC2}$            | 150 | -   | -   |         | PCLK2=V <sub>DD</sub> |

| CL2 High Level Width  | $t_{ m WHL}$          | 450 | -   | -   | ns      | PCLK2=V <sub>DD</sub> |

| Data Setup Time       | $t_{SU}$              | 100 | -   | -   |         |                       |

| Data Hold Time        | $t_{ m DH}$           | 100 | -   | -   |         |                       |

| Data Delay Time       | $t_{\mathrm{D}}$      | -   | -   | 200 | _       | *1                    |

| Output Data Hold Time | $t_{H}$               | 10  | -   | -   | <u></u> |                       |

| CL2 Rise/Fall Time    | $t_{\rm R}/t_{\rm F}$ | -   | -   | 30  |         |                       |

#### \*1: Connect load CL=30pF

## **FUNCTIONAL DESCRIPTION**

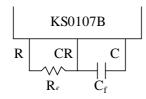

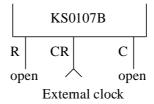

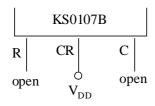

#### 1.RC Oscillator

The RC Oscillator generates CL2, M, FRM, of the KS0107B and CLK1, CLK2 of the KS0107B by the oscillation resister R and capacitor C.

When selecting the master/slave, oscillation circuit is as following:

#### 1) Master Mode

#### 2) Slave Mode

#### 2. Timing Generation circuit

It generates CL2, M, FRM, CLK1, and CLK2 by the frequency from oscillation circuit.

- Selection of Master/Slave (M/S)

When M/S is "H", it generates CL2, M, FRM, CLK1, and CLK2 internally. When M/S is "L",

it operates by receiving M, CLK2 from master device.

- 2) Frequency Selection (FS)

To adjust FRM by 70Hz, the oscillation frequency should be as following:

| FS | Oscillation Frequency    |

|----|--------------------------|

| Н  | f <sub>OSC</sub> =430KHz |

| L  | f <sub>OSC</sub> =215KHz |

In the slave mode, it is connected to  $V_{DD}$ .

#### **Duty Selection (DS1, DS2)** 3)

It provides various duty selection according to DS1, DS2.

| DS1 | DS2 | DUTY  |

|-----|-----|-------|

| L   | L   | 1/48  |

|     | Н   | 1/64  |

| Н   | L   | 1/96  |

|     | Н   | 1/128 |

#### Data shift & Phase Select Control

#### Phase Selection 1)

It is a circuit to shift data on synchronization or rising edge or falling edge of the CL2 according to PCLK2.

| PCLK2 | Phase Selection                   |  |  |  |  |  |  |  |

|-------|-----------------------------------|--|--|--|--|--|--|--|

| Н     | Data shift on rising edge of CL2  |  |  |  |  |  |  |  |

| L     | Data shift on falling edge of CL2 |  |  |  |  |  |  |  |

#### Data shift Direction Selection

When M/S is connected to VDD, DIO1 and DIO2 terminal is only output.

When M/S is connected to VSS, it depends on the SHL.

| MS | SHL | DIO1   | DIO2   | <b>Direction of Data</b> |

|----|-----|--------|--------|--------------------------|

| Н  | Н   | Output | Output | C1~C64                   |

|    | L   | Output | Output | C64~C1                   |

| L  | Н   | Input  | Output | DIO1~C1~C64~DIO2         |

|    | L   | Output | Input  | DIO2~C64~C1~DIO1         |

#### CHAPTER 3

## **Driver IC Function Description**

KS0108 Driver IC 64 SEG graphic driver for dot matrix LCD

#### Introduction

The KS0108B is an LCD driver LSI with 64 channel outputs for dot matrix liquid crystal graphic display systems. This device consists of the display RAM, 64 bit data latch 64 bit drivers and decoder logics. It has the internal display RAM for storing the display data transferred from a 8 bit micro controller and generates the dot matrix liquid crystal driving signals corresponding to stored data. The KS0108B composed of the liquid crystal display system in combination with the KS0107B(64 common driver).

## AC Characteristics ( $V_{DD}=4.5\sim5.5V$ , $V_{SS}=0V$ , $Ta=-30?\sim+85?$ )

#### (1) Clock Timing

| Characteristic             | Symbol             | Min  | Typ | Max | Unit |

|----------------------------|--------------------|------|-----|-----|------|

| CLK1. CLK2 Cvcle Time      | tov                | 2.5  | -   | 20  | ⊳s   |

| CLK1'LOW'Level Width       | $t_{\mathrm{WL1}}$ | 625  | -   | -   |      |

| CLK2'LOW'Level Width       | $t_{WL2}$          | 625  | -   | -   |      |

| CLK1'HIGH'Level Width      | $t_{ m WH1}$       | 1875 | -   | -   | _    |

| CLK2'HIGH'Level Width      | $t_{ m WH2}$       | 1875 | -   | -   | ns   |

| CLK1-CLK2 Phase Difference | $t_{\mathrm{D}12}$ | 625  | -   | -   | _    |

| CLK2-CLK1 Phase Difference | $t_{D21}$          | 625  | -   | -   | _    |

| CLK1, CLK2 Rise Time       | $t_R$              | -    | -   | 150 | _    |

| CLK1, CLK2 Fall Time       | $t_{\mathrm{F}}$   | -    | -   | 150 | _    |

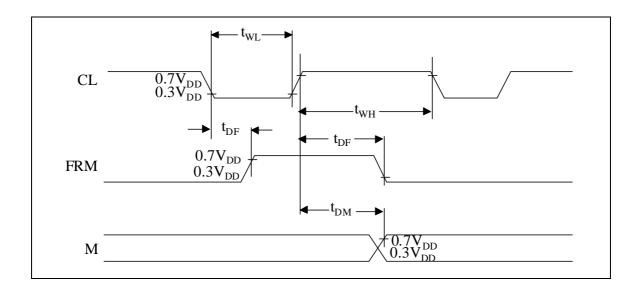

## (2) .Display Control Timing

| Characteristic      | Symbol       | Min | Typ | Max | Unit |

|---------------------|--------------|-----|-----|-----|------|

| FRM Delay Time      | tne          | -2  | -   | 2   | _    |

| M Delay Time        | $t_{\rm DM}$ | -2  | -   | 2   | us   |

| CL 'LOW'Level Width | $t_{ m WL}$  | 35  | -   | -   | _    |

| CL'HIGH'Level Width | $t_{WH}$     | 35  | -   | -   | _    |

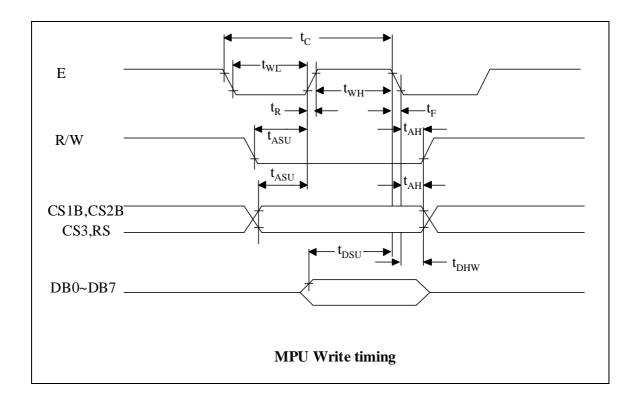

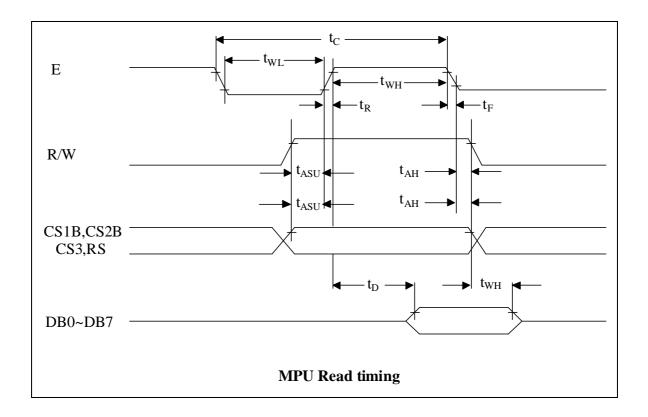

## (3) . MPU Interface

| Characteristic         | Symbol             | Min  | Typ | Max | Unit          |

|------------------------|--------------------|------|-----|-----|---------------|

| E Cvcle                | tc                 | 1000 | -   | -   | _             |

| E High Level Width     | $t_{WH}$           | 450  | -   | -   | _             |

| E Low Level Width      | $t_{ m WL}$        | 450  | -   | -   | <del></del> - |

| E Rise Time            | t <sub>R</sub>     | -    | -   | 25  | _             |

| E Fall Time            | $t_{\mathrm{F}}$   | -    | -   | 25  | _             |

| Address Set-Up Time    | $t_{ASU}$          | 140  | -   | -   | ns            |

| Address Hold Time      | $t_{AH}$           | 10   | -   | -   | _             |

| Data Set-Up Time       | $t_{ m SU}$        | 200  | -   | -   | _             |

| Data Delay Time        | $t_{\mathrm{D}}$   | -    | -   | 320 |               |

| Data Hold Time (Write) | $t_{\mathrm{DHW}}$ | 10   | -   | -   | _             |

| Data Hold Time (Read)  | $t_{\mathrm{DHR}}$ | 20   | -   | -   |               |

#### **OPERATING PRINCIPLES & METHODS**

#### 1. I/O Buffer

Input buffer controls the status between the enable and disable of chip. Unless the CS1B to CS3 is in active mode, Input or output of data and instruction does not execute. Therefore internal state is not change. But RSTB and ADC can operate regardless CS!B-CS3.

#### 2. Input register

Input register is provided to interface with MPU which is different operating frequency. Input register stores the data temporarily before writing it into display RAM.

When CS1B to CS3 are in the active mode, R/W and RS select the input register. The data from MPU is written into input register. Then writing it into display RAM. Data latched for falling of the E signal and write automatically into the display data RAM by internal operation.

#### 3. Output register

Output register stores the data temporarily from display data RAM when CS1B, CS2B and CS3 are in active mode and R/W and RS=H, stored data in display data RAM is latched in output register. When CS1B to CS3 is in active mode and R/W=H, RS=L, status data (busy check) can read out.

To read the contents of display data RAM, twice access of read instruction is needed. In first access, data in display data RAM is latched into output register. In second access, MPU can read data which is latched. That is to read the data in display data RAM, it needs dummy read. But status read is not needed dummy read.

| RS | R/W | Function                                             |

|----|-----|------------------------------------------------------|

| L  | L   | Instruction                                          |

|    | Н   | Status read (busy check)                             |

| Н  | L   | Data write (from input register to display data RAM) |

|    | Н   | Data read (from display data RAM to output register) |

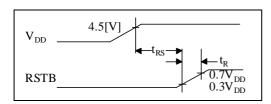

#### 4. Reset

The system can be initialized by setting RSTB terminal at low level when turning power on, receiving instruction from MPU. When RSTB becomes low, following procedure is occurred.

- 1. Display off

- 2. Display start line register become set by 0.(Z-address 0)

While RSTB is low, No instruction except status read can by accepted. Therefore, execute other instructions after making sure that DB4= (clear RSTB) and DB7=0 (ready) by status read instruction. The conditions of power supply at initial power up are shown in table 1.

Table 1. Power Supply Initial Conditions

| Item       | Symbol   | Min | Тур | Max | Unit |

|------------|----------|-----|-----|-----|------|

| Reset Time | $t_{RS}$ | 1.0 | -   | -   | us   |

| Rise Time  | $t_{R}$  | -   | -   | 200 | ns   |

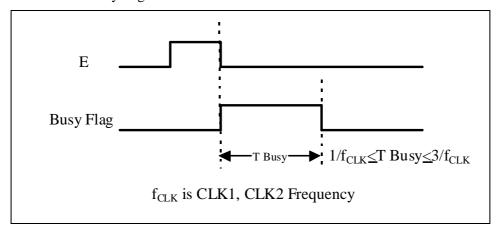

#### 5. Busy flag

Busy flag indicates that KS0108B is operating or no operating. When busy flag is high, KS0108B is in internal operating .

When busy flag is low, KS0108B can accept the data or instruction.

DB7indicates busy flag of the KS0108B.

#### 6. Display On/Off Flip-Flop

The display on/off flip-flop makes on/off the liquid crystal display. When flip-flop is reset (logical low), selective voltage or non selective voltage appears on segment output terminals. When flip-flop is set (logic high), non selective voltage appears on segment output terminals regardless of display RAM data. The display on/off flip-flop can changes status by instruction. The display data at all segment disappear while RSTB is low.

The status of the flip-flop is output to DB5 by status read instruction.

The display on/off flip-flop synchronized by CL signal.

#### 7. X Page Register

X page register designates pages of the internal display data RAM. Count function is not available. An address is set by instruction.

#### 8. Y address counter

Y address counter designates address of the internal display data RAM. An address is set by instruction and is increased by 1 automatically by read or write operations of display data.

#### 9. Display Data RAM

Display data RAM stores a display data for liquid crystal display. To indicate on state dot matrix of liquid crystal display , write datra1. The other way , off state, writes 0.

Display data RAM address and segment output can be controlled by ADC signal.

ADC=H => Y-address 0: S1~Y address 63: S64

ADC=L => Y-address 0: S64~Yaddress 63: S1

ADC terminal connect the  $V_{DD}$  or  $V_{SS}$ .

#### 10. Display Start Line Register

The display start line register indicates of display data RAM to display top line of liquid crystal display. Bit data (DB<0.5>) of the display start line set instruction is latched in display start line register. Latched data is transferred to the Z address counter while FRM is high, presetting the Z address counter.

It is used for scrolling of the liquid crystal display screen.

## **Display Control Instruction**

The display control instructions control the internal state of the KS0108B. Instruction is received from MPU to KS0108B for the display control. The following table shows various instructions.

| Instruction    | RS | RW | DB7  | DB6 | DB5 | DB4   | DB3       | DB2         | DB1                       | DB0 | Function                     |               |  |          |  |  |  |  |                |  |  |           |

|----------------|----|----|------|-----|-----|-------|-----------|-------------|---------------------------|-----|------------------------------|---------------|--|----------|--|--|--|--|----------------|--|--|-----------|

| Read Display   |    |    |      |     |     |       |           |             | Reads data (DB[7:0]) from |     |                              |               |  |          |  |  |  |  |                |  |  |           |

| Date           | 1  | 1  |      |     |     | Read  | l data    |             |                           |     | display data RAM to the      |               |  |          |  |  |  |  |                |  |  |           |

|                |    |    |      |     |     |       |           |             |                           |     | data bus.                    |               |  |          |  |  |  |  |                |  |  |           |

|                |    |    |      |     |     |       |           |             |                           |     | Writes data (DB[7:0]) into   |               |  |          |  |  |  |  |                |  |  |           |

| Write Display  |    |    |      |     |     |       |           |             |                           |     | the DDRAM. After writing     |               |  |          |  |  |  |  |                |  |  |           |

| Date           | 1  | 0  |      |     |     | Write | e data    |             |                           |     | instruction, Y address is    |               |  |          |  |  |  |  |                |  |  |           |

| Dute           |    |    |      |     |     |       |           |             |                           |     | incriminated by 1            |               |  |          |  |  |  |  |                |  |  |           |

|                |    |    |      |     |     |       |           |             |                           |     | automatically                |               |  |          |  |  |  |  |                |  |  |           |

|                |    |    |      |     |     |       |           |             |                           |     | Reads the internal status    |               |  |          |  |  |  |  |                |  |  |           |

|                |    |    |      |     |     |       |           |             |                           |     | BUSY                         |               |  |          |  |  |  |  |                |  |  |           |

|                |    |    |      |     |     |       |           |             |                           |     |                              |               |  | 0: Ready |  |  |  |  |                |  |  |           |

|                | 0  |    |      |     |     |       |           |             | 0                         |     | 1: In operation              |               |  |          |  |  |  |  |                |  |  |           |

| Status Read    |    | 1  | Busy | 0   | ON/ | Re-   | 0         | 0           |                           | 0   | ON/OFF                       |               |  |          |  |  |  |  |                |  |  |           |

| Status Read    | U  | 1  | Dusy | U   | OFF | set   |           |             |                           | O   |                              | 0: Display ON |  |          |  |  |  |  |                |  |  |           |

|                |    |    |      |     |     |       |           |             |                           |     |                              |               |  |          |  |  |  |  | 1: Display OFF |  |  |           |

|                |    |    |      |     |     |       |           |             |                           |     |                              |               |  |          |  |  |  |  |                |  |  | RESET     |

|                |    |    |      |     |     |       |           |             |                           |     |                              |               |  |          |  |  |  |  |                |  |  | 0: Normal |

|                |    |    |      |     |     |       |           |             |                           |     | 1: Reset                     |               |  |          |  |  |  |  |                |  |  |           |

| Set Address    | 0  | 0  | 0    | 1   |     |       | V addrag  | ss (0~63)   | `                         |     | Sets the Y address at the    |               |  |          |  |  |  |  |                |  |  |           |

| (Y address)    | U  | U  | U    | 1   |     |       | 1 addres  | ss (0~03)   | ,                         |     | column address counter       |               |  |          |  |  |  |  |                |  |  |           |

| Set Display    |    |    |      |     |     |       |           |             |                           |     | Indicates the Display Data   |               |  |          |  |  |  |  |                |  |  |           |

| Start Line     | 0  | 0  | 1    | 1   |     | Dis   | play star | t line (0~  | -63)                      |     | RAM displayed at the top of  |               |  |          |  |  |  |  |                |  |  |           |

| Start Line     |    |    |      |     |     |       |           | the screen. |                           |     |                              |               |  |          |  |  |  |  |                |  |  |           |

| Set Address (X | 0  | 0  | 1    | 0   | 1   | 1     | 1         | Page (0~7)  |                           | 7)  | Sets the X address at the X  |               |  |          |  |  |  |  |                |  |  |           |

| address)       | U  | U  | 1    | U   | 1   | 1     | 1         |             |                           | ')  | address register.            |               |  |          |  |  |  |  |                |  |  |           |

|                |    |    |      |     |     |       |           |             |                           |     | Controls the display ON or   |               |  |          |  |  |  |  |                |  |  |           |

|                |    |    |      |     |     |       |           |             |                           |     | OFF. The internal status and |               |  |          |  |  |  |  |                |  |  |           |

| Display On/off | 0  | 0  | 0    | 0   | 1   | 1     | 1         | 1           | 1                         | 0/1 | the DDRAM data is not        |               |  |          |  |  |  |  |                |  |  |           |

|                |    |    |      |     |     |       |           |             |                           |     | affected.                    |               |  |          |  |  |  |  |                |  |  |           |

|                |    |    |      |     |     |       |           |             |                           |     | 0: OFF, 1: ON                |               |  |          |  |  |  |  |                |  |  |           |

#### 1. Display On/Off

The display data appears when D is 1 and disappears when D is 0.

Though the data is not on the screen with D=0, it remains in the display data RAM.

Therefore, you can make it appear by changing D=0 into D=1.

| RS | R/W | DB7 | DB6 | DB5 | DB4 | DB3 | DB2 | DB1 | DB0 |

|----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| 0  | 0   | 0   | 0   | 1   | 1   | 1   | 1   | 1   | D   |

#### 2. Set Address (Y Address)

Y address (AC0~AC5) of the display data RAM is set in the Y address counter. An address is set by instruction and increased by 1 automatically by read or write operations of display data.

| RS | R/W | DB7 | DB6 | DB5 | DB4 | DB3 | DB2 | DB1 | DB0 |

|----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| 0  | 0   | 0   | 1   | AC5 | AC4 | AC3 | AC2 | AC1 | AC0 |

#### 3. Set Page (X Address)

X address (AC0~AC2) of the display data RAM is set in the X address register.

Writing or reading to or from MPU is executed in this specified page until the next page is set.

|   | RS | R/W | DB7 | DB6 | DB5 | DB4 | DB3 | DB2 | DB1 | DB0 |

|---|----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| ľ | 0  | 0   | 1   | 0   | 1   | 1   | 1   | AC2 | AC1 | AC0 |

#### 4. Display Start Line (Z Address)

Z address (AC0~AC5) of the display data RAM is set in the display start line register and displayed at the top of the screen.

When the display duty cycle is 1/64 or others (1/32~1/64), the data of total line number of LCD screen, from the line specified by display start line instruction, is displayed.

| RS | R/W | DB7 | DB6 | DB5 | DB4 | DB3 | DB2 | DB1 | DB0 |

|----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| 0  | 0   | 1   | 1   | AC5 | AC4 | AC3 | AC2 | AC1 | AC0 |

#### 5. Status Read

| RS | R/W | DB7      | DB6 | DB5    | DB4   | DB3 | DB2 | DB1 | DB0 |

|----|-----|----------|-----|--------|-------|-----|-----|-----|-----|

| 1  | 0   | BUS<br>Y | 0   | ON/OFF | RESET | 0   | 0   | 0   | 0   |

**EX** BUSY

When BUSY is 1, the Chip is executing internal operation and no instructions are accepted. When BUSY is 0, the Chip is ready to accept any instructions.

SS ON/OFF

When ON/OFF is 1, the display is on.

When ON/OFF is 0, the display is off.

**EXE** RESET

When RESET is 1, the system is being initialized.

In this condition, no instructions except status read can be accepted.

When RESET is 0, initializing has finished and the system is in the usual operation condition.

#### 6. Write Display Data

Writes data (D0~D7) into the display data RAM.

After writing instruction, Y address is increased by 1 automatically.

| RS | R/W | DB7 | DB6 | DB5 | DB4 | DB3 | DB2 | DB1 | DB0 |

|----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| 0  | 1   | D7  | D6  | D5  | D4  | D3  | D2  | D1  | D0  |

#### 7. Read Display Data

Reads data (D0~D7) from the display data RAM.

After reading instruction, Y address is increased by 1 automatically.

| RS | R/W | DB7 | DB6 | DB5 | DB4 | DB3 | DB2 | DB1 | DB0 |

|----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| 1  | 1   | D7  | D6  | D5  | D4  | D3  | D2  | D1  | D0  |