Data Sheet April 12, 2007 FN3690.10

#### 64ns Sample and Hold Amplifier

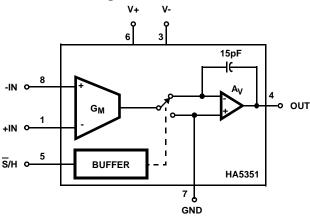

The HA5351 is a fast acquisition, wide bandwidth sample and hold amplifier, built with the Intersil HBC-10 BiCMOS process. This sample and hold amplifier offers a combination of desirable features; fast acquisition time (70ns to 0.01% maximum), excellent DC precision and extremely low power dissipation, making it ideal for use in systems that sample multiple signals and require low power.

The HA5351 is in an open loop configuration with fully differential inputs providing flexibility for user defined feedback. In unity gain the HA5351 is completely self-contained and requires no external components. The on-chip 15pF hold capacitor is completely isolated to minimizing droop rate and reducing sensitivity to pedestal error. The HA5351 is available in 8 lead SOIC package for minimizing board space and ease of layout.

### **Ordering Information**

| PART<br>NUMBER      | PART<br>MARKING | TEMP.<br>RANGE (°C) | PACKAGE                | PKG.<br>DWG. # |

|---------------------|-----------------|---------------------|------------------------|----------------|

| HA5351IB            | 5351 I          | -40 to +85          | 8 Ld SOIC              | M8.15          |

| HA5351IBZ<br>(Note) | 5351 IBZ        | -40 to +85          | 8 Ld SOIC<br>(Pb-free) | M8.15          |

NOTE: Intersil Pb-free plus anneal products employ special Pb-free material sets; molding compounds/die attach materials and 100% matte tin plate termination finish, which are RoHS compliant and compatible with both SnPb and Pb-free soldering operations. Intersil Pb-free products are MSL classified at Pb-free peak reflow temperatures that meet or exceed the Pb-free requirements of IPC/JEDEC J STD-020.

#### Functional Diagram

#### **Features**

| • Fast Acquisition to 0.01%70ns (Max)                                                                               |

|---------------------------------------------------------------------------------------------------------------------|

| Low Offset Error                                                                                                    |

| Low Pedestal Error                                                                                                  |

| Low Droop Rate 2μV/μs (Max)                                                                                         |

| Wide Unity Gain Bandwidth 40MHz                                                                                     |

| Low Power Dissipation                                                                                               |

| <ul> <li>Total Harmonic Distortion (Hold Mode)72dBc</li> <li>(V<sub>IN</sub> = 5V<sub>P-P</sub> at 1MHz)</li> </ul> |

- · Fully Differential Inputs

- · On Chip Hold Capacitor

- Pb-Free Plus Anneal Available (RoHS Compliant)

## **Applications**

- Synchronous Sampling

- Wide Bandwidth A/D Conversion

- Deglitching

- Peak Detection

- High Speed DC Restore

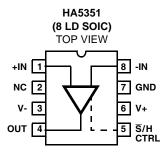

#### **Pinout**

#### **Absolute Maximum Ratings**

# Voltage Between V+ and V- Terminals ... +11V Differential Input Voltage ... 6V Voltage Between Sample and Hold Control and Ground ... +5.5V Output Current, Continuous ... ±37mA

#### **Operating Conditions**

#### **Thermal Information**

| Thermal Resistance (Typical, Note 1)             | θ <sub>JA</sub> (°C/W) |

|--------------------------------------------------|------------------------|

| SOIC Package                                     | 160                    |

| Maximum Junction Temperature (Plastic Package)   | +150°C                 |

| Maximum Storage Temperature Range65              | °C to +150°C           |

| Pb-free reflow profile                           | see link below         |

| http://www.intersil.com/pbfree/Pb-FreeReflow.asp |                        |

CAUTION: Stresses above those listed in "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress only rating and operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

#### NOTE:

1.  $\theta_{\mbox{\scriptsize JA}}$  is measured with the component mounted on an evaluation PC board in free air.

#### **Electrical Specifications**

Test Conditions:  $V_{SUPPLY} = \pm 5V$ ;  $C_H = Internal = 15pF$ , Digital Input:  $V_{IL} = 0V$  (Sample),  $V_{IH} = 4.0V$  (Hold). Non-Inverting Unity Gain Configuration (Output Tied to -Input),  $C_L = 5pF$ , Unless Otherwise Specified

| PARAMETER                              | TEST CONDITIONS                  | TEMP.<br>(°C) | MIN  | TYP  | MAX         | UNITS             |

|----------------------------------------|----------------------------------|---------------|------|------|-------------|-------------------|

| INPUT CHARACTERISTICS                  | <u> </u>                         | <b>'</b>      | 1    | "    | "           | <u>'</u>          |

| Input Voltage Range                    |                                  | Full          | -2.5 | -    | +2.5        | V                 |

| Input Resistance (Note 2)              |                                  | 25            | 100  | 500  | -           | kΩ                |

| Input Capacitance                      |                                  | 25            | -    | -    | 5           | pF                |

| Input Offset Voltage                   |                                  | 25            | -2   | -    | 2           | mV                |

| Offset Voltage Temperature Coefficient |                                  | Full          | -3.0 |      | 3.0         | mV<br>μV/°C       |

| Bias Current                           |                                  | -             | _    |      | 5           | μΑ                |

| Offset Current                         |                                  | -             | -1.5 |      |             | μΑ                |

| Common Mode Range                      |                                  | -             | _    |      | _           | V                 |

| Common Mode Rejection Ratio            | ±2.5V, Note 3                    | Full          |      |      |             | dB                |

| TRANSFER CHARACTERISTICS               | ±2.5 V, 140to 0                  | ı un          | - 00 | 00   |             | ub.               |

| Large Signal Voltage Gain              | V <sub>OUT</sub> = ±2.5V         | 25            | 95   | 108  | -           | dB                |

|                                        | 001                              | Full          | 85   | -    | -           | dB                |

| Unity Gain -3dB Bandwidth              |                                  | 25            | -    | 40   | -           | MHz               |

| TRANSIENT RESPONSE                     |                                  | <b>"</b>      |      |      |             |                   |

| Rise Time                              | 200mV Step                       | 25            | -    | 8.5  | -           | ns                |

| Overshoot                              | 200mV Step                       | 25            | 0    | -    | 30          | %                 |

| Slew Rate                              | 5V Step                          | Full          | 88   | 105  | -           | V/µs              |

| DIGITAL INPUT CHARACTERISTICS          |                                  |               | 1    |      |             |                   |

| Input Voltage                          | V <sub>IH</sub>                  | 25, 85        | 2.1  | -    | 5.0         | V                 |

|                                        |                                  | -40           | 2.4  | -    | 5.0         | V                 |

|                                        | V <sub>IL</sub>                  | Full          | 25   | -    | 0.8         | V                 |

| Input Current                          | $V_{IL} = 0V$                    | Full          | -1.0 | -    | 1.0         | μΑ                |

|                                        | V <sub>IH</sub> = 5V             | Full          | -1.0 | -    | 1.0         | μΑ                |

| OUTPUT CHARACTERISTICS                 |                                  |               |      |      |             |                   |

| Output Voltage                         | $R_L = 510\Omega$                | Full          | -3.0 | -    | +3.0        | V                 |

| Output Current                         | $R_L = 100\Omega$                | 25, 85        | 20   | 25   | -           | mA                |

|                                        |                                  | -40           | 15   | -    | - +2.5  500 | mA                |

| Full Power Bandwidth                   | $5V_{P-P}$ , $A_V = +1$ , $-3dB$ | Full          | -    | 13   | -           | MHz               |

| Output Resistance                      | Hold Mode                        | 25            | -    | 0.02 | -           | Ω                 |

| Total Output Noise                     | Sample Mode                      | 25            | -    | 325  | -           | μV <sub>RMS</sub> |

| (DC to 10MHz)                          | Hold Mode                        | 25            | -    | 325  | -           | μV <sub>RMS</sub> |

FN3690.10 April 12, 2007

#### **Electrical Specifications**

Test Conditions:  $V_{SUPPLY} = \pm 5V$ ;  $C_H = Internal = 15pF$ , Digital Input:  $V_{IL} = 0V$  (Sample),  $V_{IH} = 4.0V$  (Hold). Non-Inverting Unity Gain Configuration (Output Tied to -Input),  $C_L = 5pF$ , Unless Otherwise Specified **(Continued)**

| PARAMETER                                       | TEST CONDITIONS                                                  | TEMP.<br>(°C) | MIN | TYP | MAX   | UNITS |

|-------------------------------------------------|------------------------------------------------------------------|---------------|-----|-----|-------|-------|

| DISTORTION CHARACTERISTICS                      | ·                                                                |               |     |     |       | •     |

| SAMPLE MODE                                     |                                                                  |               |     |     |       |       |

| Total Harmonic Distortion                       | $V_{IN} = 4.5V_{P-P}, f_{IN} = 100kHz$                           | 25            | -   | -80 | -     | dBc   |

|                                                 | $V_{IN} = 5V_{P-P}$ , $f_{IN} = 1MHz$                            | 25            | -   | -74 | -80 - | dBc   |

|                                                 | $V_{IN} = 1V_{P-P}$ , $f_{IN} = 10MHz$                           | 25            | -   | -57 |       | dBc   |

| Signal to Noise Ratio (RMS Signal to RMS Noise) | $V_{IN} = 4.5V_{P-P}, f_{IN} = 100kHz$                           | 25            | -   | 73  | -     | dB    |

| HOLD MODE (50% Duty Cycle S/H)                  |                                                                  | •             | •   |     |       |       |

| Total Harmonic Distortion                       | $V_{IN} = 4.5V_{P-P}$ , $f_{IN} = 100kHz$ , $f_{S} \cong 100kHz$ | 25            | -   | -78 | -     | dBc   |

|                                                 | $V_{IN} = 5V_{P-P}, f_{IN} = 1MHz,$<br>$f_S \cong 1MHz$          | 25            | -   | -72 | -     | dBc   |

|                                                 | $V_{IN} = 1V_{P-P}$ , $f_{IN} = 10MHz$ , $f_S \cong 1MHz$        | 25            | -   | -51 | -     | dBc   |

| Signal to Noise Ratio (RMS Signal to RMS Noise) | $V_{IN} = 4.5V_{P-P}$ , $f_{IN} = 100kHz$ , $f_{S} \cong 100kHz$ | 25            | -   | 70  | -     | dB    |

| SAMPLE AND HOLD CHARACTERISTIC                  | cs                                                               | •             | •   |     |       |       |

| Acquisition Time                                | 0V to 2.0V Step to ±1mV                                          | 25            | -   | 53  | -     | ns    |

|                                                 | 0V to 2.0V Step to 0.01% (±200μV)                                | 25            | -   | 64  | 70    | ns    |

|                                                 | -2.5V to +2.5V Step to 0.01% (±500μV)                            | 25            | -   | 90  | 100   | ns    |

| Droop Rate                                      |                                                                  | 25            | -   | 0.3 | -     | μV/μs |

|                                                 |                                                                  | Full          | -2  | -   | 2     | μV/μs |

| Hold Step Error                                 | $V_{IL} = 0V, V_{IH} = 4.0V, t_R = 5ns$                          | Full          | -10 | -   | +10   | mV    |

| Hold Mode Settling Time                         | To ±1mV                                                          | 25            | -   | 50  | -     | ns    |

| Hold Mode Feedthrough                           | 5V <sub>P-P</sub> , 500kHz, Sine                                 | 25            | -   | 72  | -     | dB    |

| EADT (Effective Aperture Delay Time)            |                                                                  | 25            | -   | +1  | -     | ns    |

| Aperture Time (Note 2)                          |                                                                  | 25            | -   | 10  | -     | ns    |

| Aperture Uncertainty                            |                                                                  | 25            | -   | 10  | 20    | ps    |

| POWER SUPPLY CHARACTERISTICS                    |                                                                  |               |     |     |       |       |

| Positive Supply Current                         |                                                                  | Full          | -   | 20  | 22    | mA    |

| Negative Supply Current                         |                                                                  | Full          | -   | 20  | 22    | mA    |

| PSRR                                            | 10% Delta                                                        | Full          | 60  | 74  | -     | dB    |

#### NOTES:

- 2. Derived from Computer Simulation only, not tested.

- 3. +CMRR is measured from 0V to +2.5V, -CMRR is measured from 0V to -2.5V.

FN3690.10 April 12, 2007

3

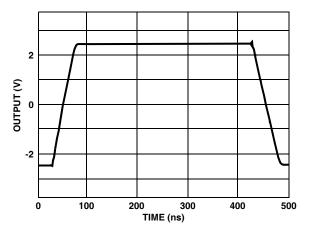

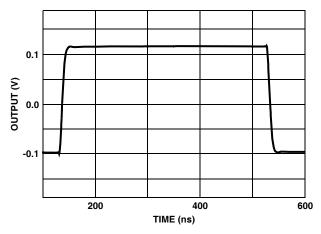

# **Typical Performance Curves**

FIGURE 1. LARGE SIGNAL RESPONSE

FIGURE 2. SMALL SIGNAL RESPONSE

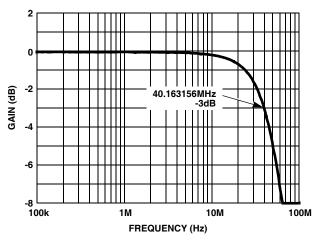

FIGURE 3. UNITY GAIN FREQUENCY RESPONSE

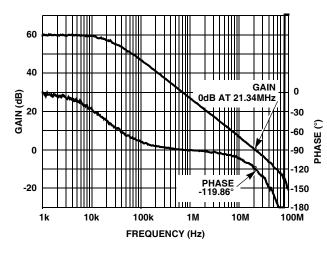

FIGURE 4. CLOSED LOOP GAIN/PHASE A<sub>V</sub> = +1000

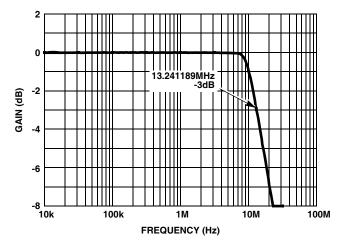

FIGURE 5. 5V<sub>P-P</sub> FULL POWER FREQUENCY RESPONSE

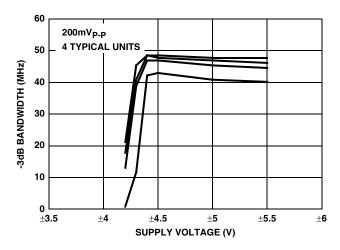

FIGURE 6. -3dB BANDWIDTH vs SUPPLY VOLTAGE

intersil FN3690.10 April 12, 2007

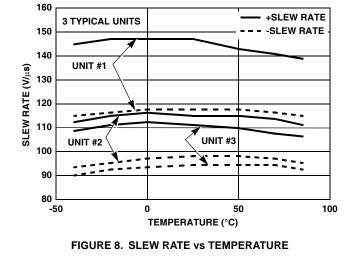

## Typical Performance Curves (Continued)

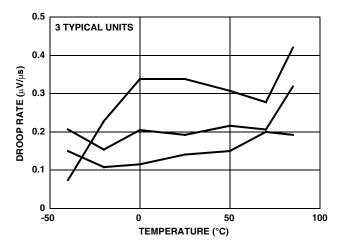

FIGURE 7. DROOP RATE vs TEMPERATURE

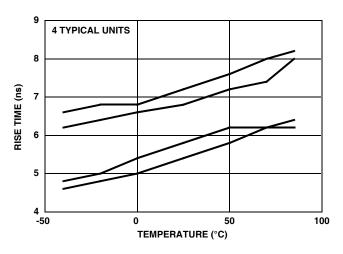

FIGURE 9. RISE TIME vs TEMPERATURE

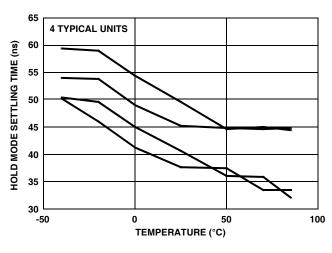

FIGURE 10. HOLD MODE SETTLING vs TEMPERATURE

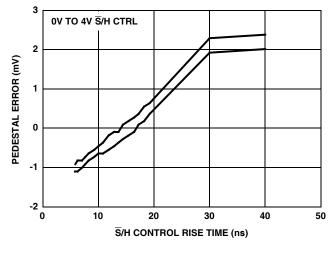

FIGURE 11. PEDESTAL vs S/H CONTROL RISE TIME

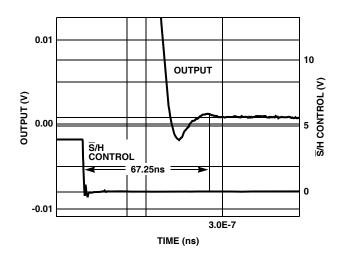

FIGURE 12. ACQUISITION TIME (0.01%, 0V TO 2V STEP)

intersil FN3690.10 April 12, 2007

# Typical Performance Curves (Continued)

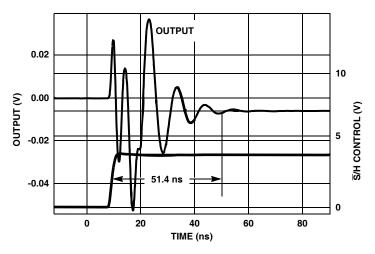

FIGURE 13. HOLD MODE SETTLING TIME ( $\pm 200 \mu V$ )

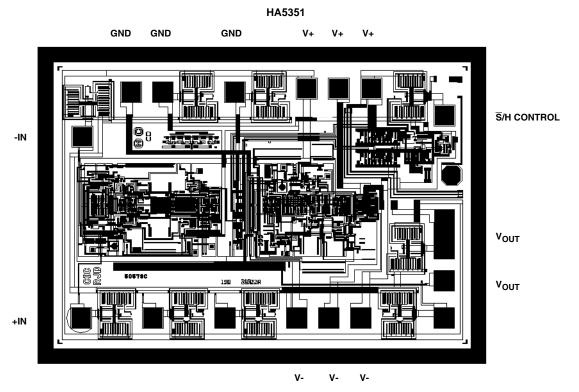

## Die Characteristics

**SUBSTRATE POTENTIAL:**

V-

TRANSISTOR COUNT:

156

# Metallization Mask Layout

<u>intersil</u>

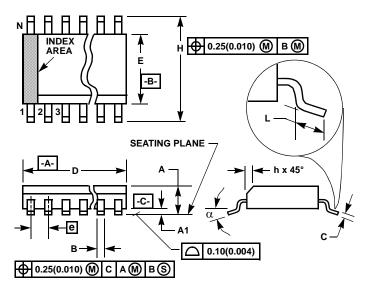

## Small Outline Plastic Packages (SOIC)

#### NOTES:

- Symbols are defined in the "MO Series Symbol List" in Section 2.2 of Publication Number 95.

- 2. Dimensioning and tolerancing per ANSI Y14.5M-1982.

- Dimension "D" does not include mold flash, protrusions or gate burrs. Mold flash, protrusion and gate burrs shall not exceed 0.15mm (0.006 inch) per side.

- Dimension "E" does not include interlead flash or protrusions. Interlead flash and protrusions shall not exceed 0.25mm (0.010 inch) per side

- 5. The chamfer on the body is optional. If it is not present, a visual index feature must be located within the crosshatched area.

- 6. "L" is the length of terminal for soldering to a substrate.

- 7. "N" is the number of terminal positions.

- 8. Terminal numbers are shown for reference only.

- The lead width "B", as measured 0.36mm (0.014 inch) or greater above the seating plane, shall not exceed a maximum value of 0.61mm (0.024 inch).

- Controlling dimension: MILLIMETER. Converted inch dimensions are not necessarily exact.

M8.15 (JEDEC MS-012-AA ISSUE C)

8 LEAD NARROW BODY SMALL OUTLINE PLASTIC PACKAGE

|        | INCHES |           | MILLIN |          |       |

|--------|--------|-----------|--------|----------|-------|

| SYMBOL | MIN    | MAX       | MIN    | MAX      | NOTES |

| Α      | 0.0532 | 0.0688    | 1.35   | 1.75     | -     |

| A1     | 0.0040 | 0.0098    | 0.10   | 0.25     | -     |

| В      | 0.013  | 0.020     | 0.33   | 0.51     | 9     |

| С      | 0.0075 | 0.0098    | 0.19   | 0.25     | -     |

| D      | 0.1890 | 0.1968    | 4.80   | 5.00     | 3     |

| Е      | 0.1497 | 0.1574    | 3.80   | 4.00     | 4     |

| е      | 0.050  | 0.050 BSC |        | 1.27 BSC |       |

| Н      | 0.2284 | 0.2440    | 5.80   | 6.20     | -     |

| h      | 0.0099 | 0.0196    | 0.25   | 0.50     | 5     |

| L      | 0.016  | 0.050     | 0.40   | 1.27     | 6     |

| N      | 8      | 3         | 8      |          | 7     |

| α      | 0°     | 8°        | 0°     | 8°       | -     |

Rev. 1 6/05

All Intersil U.S. products are manufactured, assembled and tested utilizing ISO9000 quality systems. Intersil Corporation's quality certifications can be viewed at www.intersil.com/design/quality

Intersil products are sold by description only. Intersil Corporation reserves the right to make changes in circuit design, software and/or specifications at any time without notice. Accordingly, the reader is cautioned to verify that data sheets are current before placing orders. Information furnished by Intersil is believed to be accurate and reliable. However, no responsibility is assumed by Intersil or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Intersil or its subsidiaries.

For information regarding Intersil Corporation and its products, see www.intersil.com

FN3690.10 April 12, 2007