#### 25-Mbps VFO with Built-in 1-7 Encoder/Decoder

#### Description

The HD153021F is a 25-Mbps VFO with built-in 1-7 run-length-limit encoder/decoder developed for use in magnetic disk drives. In read mode it decodes 1-7 RLL encoded data from the magnetic disk to an NRZ signal, which it outputs in synchronization with a read clock. In write mode it encodes an NRZ signal to 1-7 RLL data. The HD153021F supports zone bit recording and has circuits for generating the necessary write clock.

#### **Features**

- Maximum data transfer rate: 25 Mbps

- Data transfer clock frequency: 1.5 × data transfer rate

- Encoding and decoding: IBM 1-7 RLL code

- Settings are microcontroller-programmable

- · Supports zone bit recording

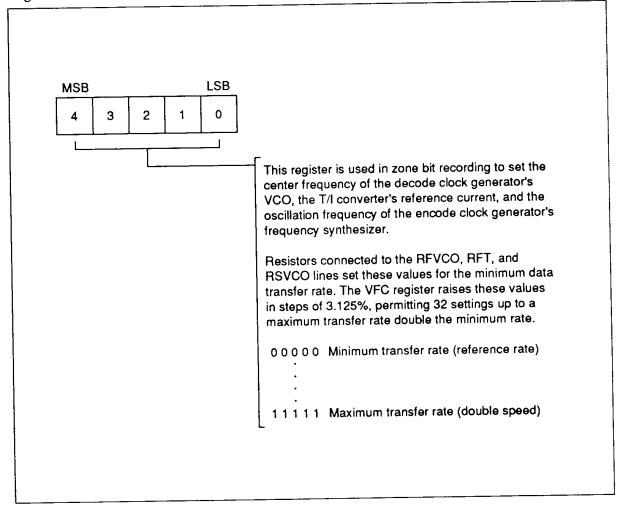

- On-chip frequency synthesizer generates encode clock (32 frequencies, 3.125% steps)

- Window centering adjustment (rough and fine) and window monitoring functions

- Programmable write precompensation table and delay

- The following are programmable for zone bit recording: VCO center frequency (32 settings), loop filter constant (2 settings), charge pump current (2 settings), and T/I converter output current (8 settings).

- Supports both hard sectoring and soft sectoring (DC erase)

- Detects sync field (3T)

- Hi-BiCMOS process achieves high speed with lower power dissipation

- · Standby function

- QFP80 package suitable for compact surface mounting (resin size: 14 mm<sup>2</sup>)

- Convenient single 5-V power supply

#### **Ordering Information**

| Type No.  | Package |

|-----------|---------|

| HD153021F | FP-80A  |

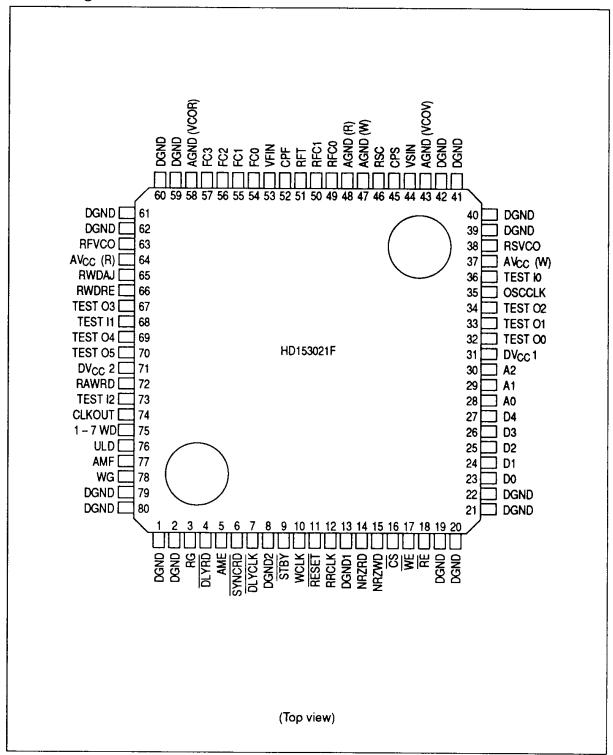

#### Pin Arrangement

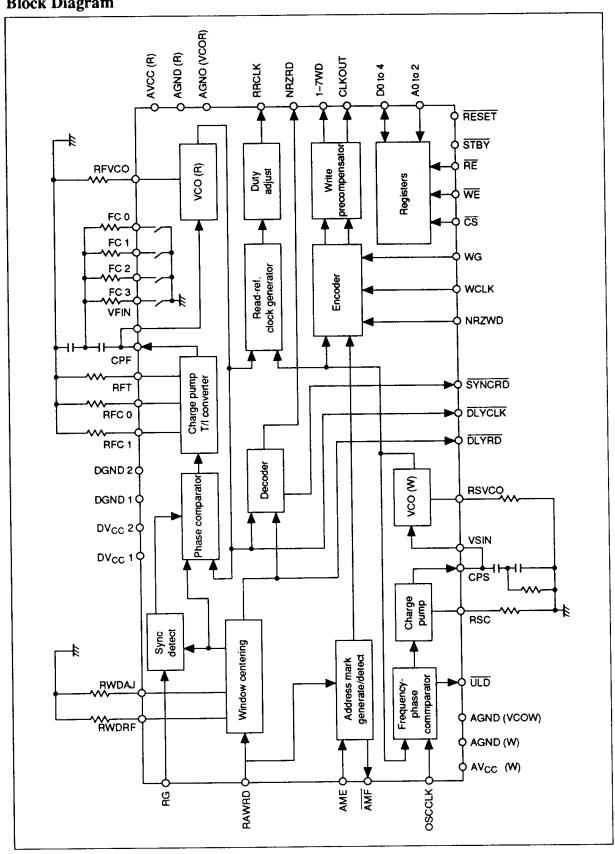

### **Block Diagram**

### **Pin Functions**

| Pin Name                        | Pin No. | Туре | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

|---------------------------------|---------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

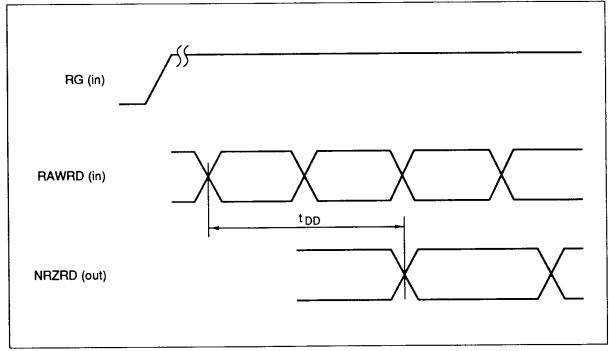

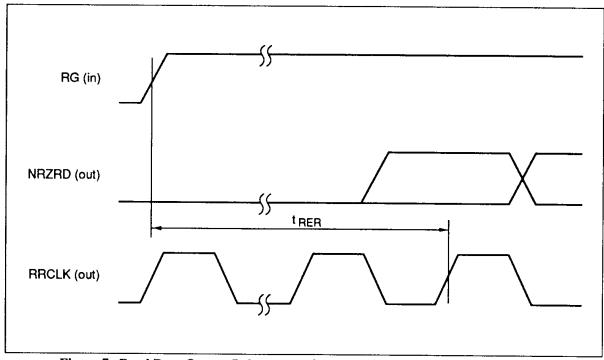

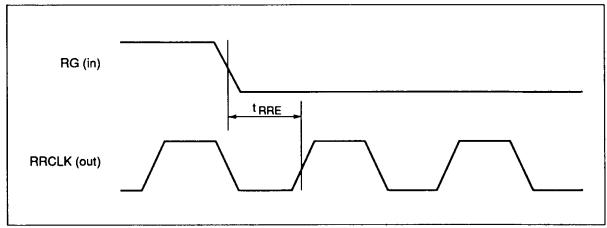

| RG<br>(Read gate)               | 3       | In   | High input selects read mode, in which 1-7 encoded data read from disk are converted to an NRZ signal and output. This signal switches the clock for counters and internal circuits, starts NRZ signal output, and begins phase synchronization of the decode clock generator's VFO with the 1-7 coded data. When bit 4 in register MDC is set to 1, the sync field detect circuit is activated and the internal RG signal is delayed until after sync detection. |  |

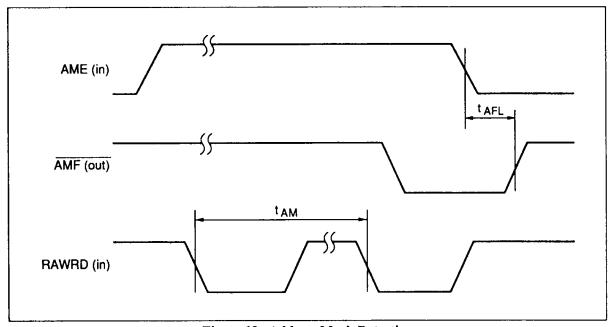

| AME<br>(Address<br>mark enable) | 5       | In   | Used for soft sector formats. Drive this line high to generate or detect address marks.  For address mark generation, drive this line high for 1 to 3 bytes when WG is high to write a fixed-length address-mark pattern (8T, 8T, 11T, 11T).  For address mark detection, drive this line high when WG is low. An AMF signal will be output when an address mark is detected. When the AMF signal is output, the disk controller should drive AME low.            |  |

| STBY<br>(Standby)               | 9       | In   | Low input selects standby mode, reducing power dissipation. Internal circuits are initialized. Keep this line high during normal operation.                                                                                                                                                                                                                                                                                                                       |  |

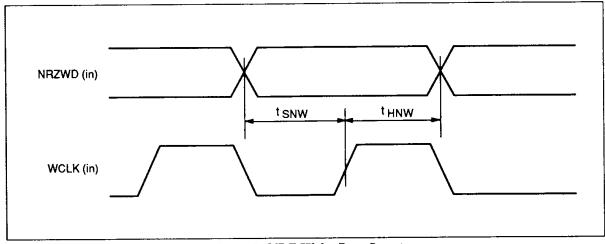

| WCLK<br>(Write clock)           | 10      | In   | Apply a clock signal synchronized with the NRZ write data signal input to NRZWD.  If the connected disk controller provides write clock output, connect the write clock directly to this input line.  If the disk controller does not provide write clock output, connect this input line to the RRCLK output line from this IC. The signal input to NRZWD must then be synchronized with the RRCLK output.                                                       |  |

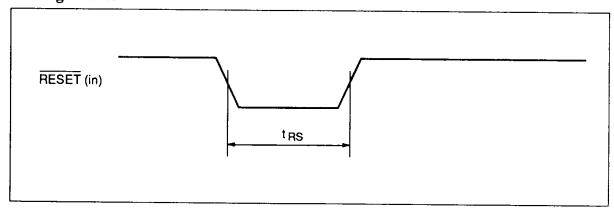

| RESET                           | 11      | In   | Low input initializes internal circuits. Drive this line low at power-up. Low input also locks the two built-in VCOs to their center frequencies.  Keep this line high during normal operation.                                                                                                                                                                                                                                                                   |  |

| NRZWD<br>(NRZ write<br>data)    | 15      | In   | NRZ signal to be written to disk. Must be synchronized with the clock signal input to WCLK. Input on this line is inverted on-chip, then converted to 1-7 code.                                                                                                                                                                                                                                                                                                   |  |

| CS<br>(Chip select)             | 16      | In   | Register control input. On-chip registers connected to the microcontroller's bus are selected when this line is driven low.                                                                                                                                                                                                                                                                                                                                       |  |

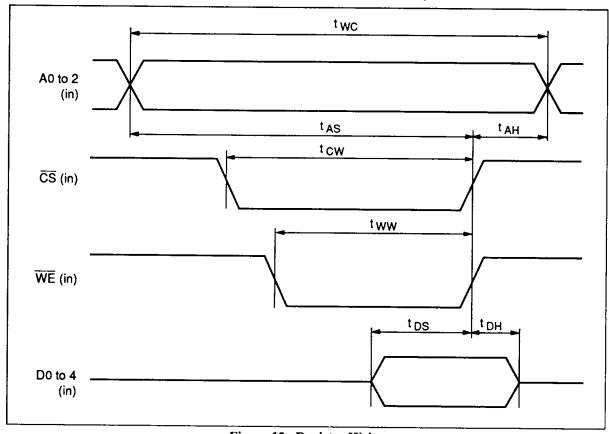

| WE<br>(Write enable)            | 17      | In   | Register control input.  Data on the microcontroller's bus are written on the rising edge of WE to the on-chip register selected by address input. CS must be low.                                                                                                                                                                                                                                                                                                |  |

| Pin Name                                | Pin No. | Type   | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|-----------------------------------------|---------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

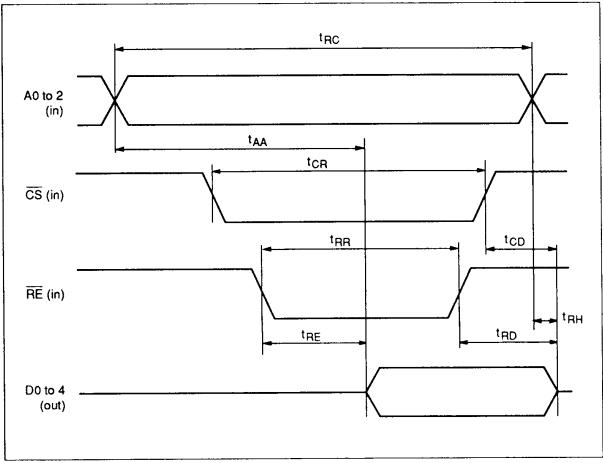

| RE<br>(Read enable)                     | 18      | În     | Register control input.  While this line is low, contents of the on-chip register selected by address input are output on the microcontroller's bus, permitting register contents to be verified. CS must be low.                                                                                                                                                                                                                                                                                                                                                                                         |

| D0 to D4<br>(Data 0 to<br>data 4)       | 23 – 27 | In/Out | Register data lines, normally connected to the microcontroller's data bus. Input lines when RE is high. Output lines when RE is low.                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| A0 to A2<br>(Address 0 to<br>address 2) | 28 – 30 | In     | Register address input lines, normally connected to the microcontroller's address bus.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| OSCCLK<br>(Oscillator<br>clock)         | 35      | In     | Reference clock input. The encode clock generator's on-chip frequency synthesizer generates encode clock frequencies from the clock input on this line. Data writing is synchronized with the encode clock. When not reading data, the decode clock generator's VFO is also synchronized with the encode clock. Apply a clock signal with frequency frequency 1.5/8 times the minimum data transfer rate. If not using the encode clock generator's on-chip frequency synthesizer, apply an encode clock at 1.5 times the transfer rate directly to OSCCLK. Bit 4 of register WPC1 must then be set to 1. |

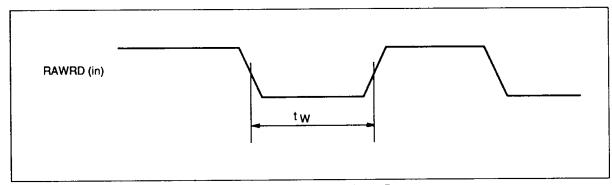

| RAWRD<br>(Raw read<br>data)             | 72      | In     | Input line for 1-7 encoded data read from disk. The leading edge of the input signal is timed with magnetic reversal. Leading edge polarity can be selected by bit 3 in register WPC0. The decode clock generator's VFO is phase-synchronized with this leading edge.                                                                                                                                                                                                                                                                                                                                     |

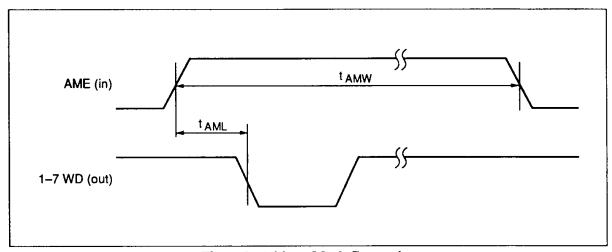

| WG<br>(Write gate)                      | 78      | In     | High input selects write mode, in which the NRZ write data signal is converted to 1-7 code and output.  Drive this line high to generate a soft sector address mark, and low to detect address marks.                                                                                                                                                                                                                                                                                                                                                                                                     |

| DLYRD<br>(Delay read<br>data)           | 4       | Out    | Window adjustment monitor output.  Low output on this line corresponds to 1s in 1-7 code read from disk.  In window adjustment, center the falling edge of the output on this line halfway between the falling and rising edges of the output at DLYCLK.  Bit 0 of register MDC must be set to 1. If MDC bit 0 is cleared to 0, DLYRD is always high.                                                                                                                                                                                                                                                     |

| Pin Name                              | Pin No. | Туре | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

|---------------------------------------|---------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| SYNCRD<br>(Sync. read<br>data)        | 6       | Out  | Window adjustment monitor output.  1-7 codes read from the disk are latched on the decode clock and output on this line. SYNCRD output is equivalent to capturing the 1-7 codes output from DLYRD on the DLYCLK output.  Use this line to monitor window margin tests.  Bit 0 of the MDC register must be set to 1. If MDC bit 0 is cleared to 0, SYNCRD is always high.                                                                                                                                                                                                                                                  |  |

| DLYCLK<br>(Delay clock)               | 7       | Out  | Window adjustment monitor output.  Provides decode clock output synchronized with the 1-7 codes read from disk. The 1-7 codes can be latched on this clock.  In window adjustment, center the falling edge of the DLYRD output halfway between the falling and rising edges of the DLYCLK output. Bit 0 of register MDC must be set to 1. If MDC bit 0 is cleared to 0, DLYCLK is always high.                                                                                                                                                                                                                            |  |

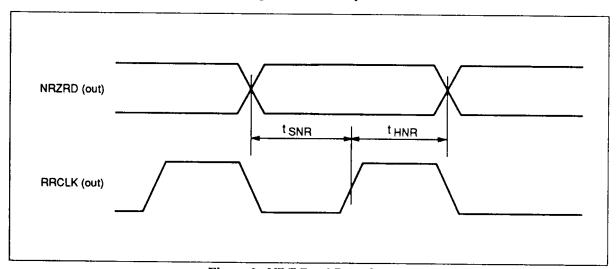

| RRCLK<br>(Read<br>reference<br>clock) | 12      | Out  | In read mode, a clock signal synchronized with the converted NRZ read data is output on this line. At other times, a reference clock is output for input by the disk controller. In read mode, the disk controller should latch the NRZ read data on the RRCLK output. If the connected disk controller does not provide write clock output, connect RRCLK to WCLK on this IC. The signal input at NRZWD must then be synchronized with the RRCLK output. The RRCLK clock output is free of glitches at clock switchover. The duty cycle of the clock output on this line can be selected by bits 0 to 3 in register DTC. |  |

| NRZRD<br>(NRZ read<br>data)           | 14      | Out  | 1-7 codes read from the disk are converted to an NRZ signal and output on this line.  The NRZRD signal is synchronized with the RRCLK signal.                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

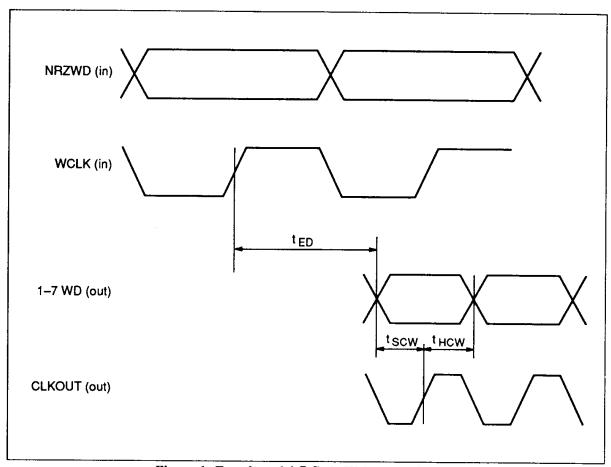

| CLKOUT<br>(Clock out)                 | 74      | Out  | Clock output used for external write phase compensation (write precompensation).  The clock signal output on this line is synchronized with the 1-7WD output.  Bit 3 of register WPC3 must be set to 1. If WPC3 bit 3 is cleared to 0, CLKOUT is always high.                                                                                                                                                                                                                                                                                                                                                             |  |

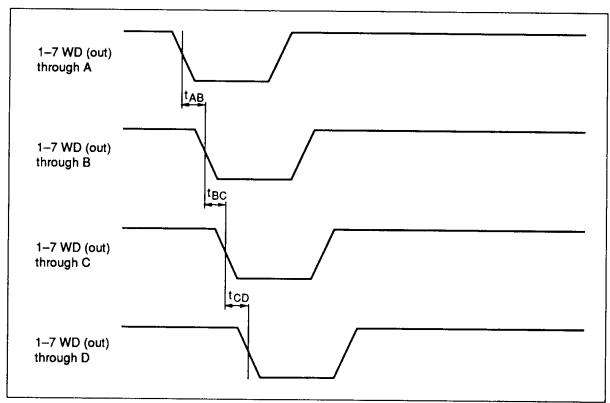

| 1-7WD<br>(1-7 write<br>data)          | 75      | Out  | Output signal to be written to disk, consisting of 1-7 codes obtained by encoding the NRZ signal.  The polarity of the output on this line can be switched by bit 4 of register WPC1.  For external write precompensation, use the CLKOUT clock output, which is synchronized with the 1-7WD output.                                                                                                                                                                                                                                                                                                                      |  |

| Pin Name                       | Pin No. | Туре                          | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

|--------------------------------|---------|-------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| ULD<br>(Unlock<br>detect)      | 76      | Out                           | Error output from the encode clock generator's frequency synthesizer.  UED goes low to indicate that the PLL in the encode clock generator's frequency synthesizer has lost lock.  The disk controller should immediately halt write operations. Data must be written again from the beginning.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

| AMF<br>(Address<br>mark found) | 77      | Out                           | Soft sector address mark detect output. If AME input is high and WG input is low, AMF goes low whenever an address mark pattern is detected. The disk controller should then drive AME low, to clear the AMF output to high.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |

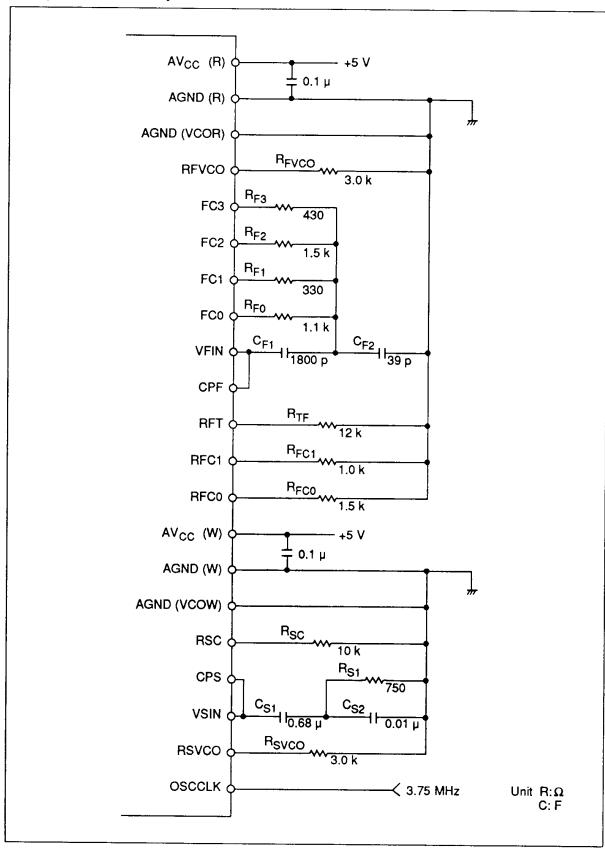

| RSVCO                          | 38      | External component connection | Connect a resistor to set the center frequency of the VCO in the encode clock generator's frequency synthesizer.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |

| VSIN                           | 44      | External component connection | Voltage input controlling the VCO in the encode clock generator's frequency synthesizer. Reset causes a VCO bias voltage generated on-chip to be applied to VSIN through an analog switch, making the VCO oscillate at its center frequency. Normally this line should be connected to CPS.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

| CPS                            | 45      | External component connection | Current output to an external loop filter.  Normally this line should be connected to VSIN as well as to the loop filter.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

| RSC                            | 46      | External component connection | Connect a resistor to set the charge pump output current for the encode clock generator's frequency synthesizer.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |

| RFC0                           | 49      | External component connection |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

| RFC1                           | 50      | External component connection |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

| RFT                            | 51      | External component connection | and the contract of the contra |  |

| CPF                            | 52      | External component connection | Current output to external loop filter.  Normally this line should be connected to VFIN as well as to the loop filter.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

| Pin Name            | Pin No | . Туре                        | Function                                                                                                                                                                                                                                                                   |  |

|---------------------|--------|-------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| VFIN                | 53     | External component connection | Voltage input controlling the VCO in the decode clock generator's VFO. Reset causes a VCO bias voltage generated on-chip to be applied to VFIN through an analog switch, making the VCO oscillate at its center frequency.  Normally this line should be connected to CPF. |  |

| FC0                 | 54     | External component connection | Connect a loop filter resistor to set the attenuation $\zeta$ of the PLL. This line is grounded through an MOS switch when bit 3 of register GAC is set to 1, and is internally disconnected when bit 3 is cleared to 0.                                                   |  |

| FC1                 | 55     | External component connection | Connect a loop filter resistor to set the attenuation $\zeta$ of the PLL. This line is grounded through an MOS switch in high gain mode when bit 3 of register GAC is set to 1, and is internally disconnected at other times.                                             |  |

| FC2                 | 56     | External component connection | Connect a loop filter resistor to set the attenuation $\zeta$ of the PLL. This line is grounded through an MOS switch when bit 3 of register GAC is cleared to 0, and is internally disconnected when bit 3 is set to 1.                                                   |  |

| FC3                 | 57     | External component connection | Connect a loop filter resistor to set the attenuation ζ of the PLL. This line is grounded through an MOS switch in high gain mode when bit 3 of register GAC is cleared to 0, and is internally disconnected at other times.                                               |  |

| RFVCO               | 63     | External component connection | Connect a resistor to set the center frequency of the VCO in the decode clock generator's VFO.                                                                                                                                                                             |  |

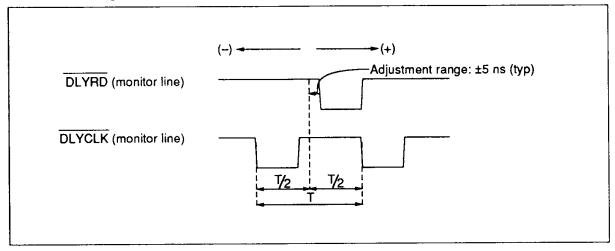

| RWDAJ               | 65     | External component connection | Connect a resistor for fine adjustment of window centering. Fine adjustment is determined by the relative values of this resistor and the reference resistor connected to RWDRF                                                                                            |  |

| RWDRF               | 66     | External component connection | Connect a reference resistor for fine adjustment of window centering.                                                                                                                                                                                                      |  |

| DV <sub>CC1</sub>   | 31     | Power                         | Digital V <sub>CC</sub> power supply.                                                                                                                                                                                                                                      |  |

| DV <sub>CC2</sub>   | 71     | Power                         | Digital V <sub>CC</sub> power supply.                                                                                                                                                                                                                                      |  |

| DGND1               | 13     | Power                         | Digital ground.                                                                                                                                                                                                                                                            |  |

| DGND2               | 8      | Power                         | Digital ground.                                                                                                                                                                                                                                                            |  |

| AV <sub>CC(R)</sub> | 64     | Power                         | Analog V <sub>CC</sub> power supply.  Powers analog circuits in the decode clock generator.                                                                                                                                                                                |  |

| Pin Name            | Pin No.                                         | Туре  | Function                                                                                                                                                                                                                                                                            |  |

|---------------------|-------------------------------------------------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| AV <sub>CC(W)</sub> | 37                                              | Power | Analog V <sub>CC</sub> power supply.  Powers analog circuits in the encode clock generator.                                                                                                                                                                                         |  |

| AGND(R)             | 48                                              | Power | Analog ground. Powers analog circuits in the decode clock generator.                                                                                                                                                                                                                |  |

| AGND(W)             | 47                                              | Power | Analog ground.  Powers analog circuits in the encode clock generator.                                                                                                                                                                                                               |  |

| AGND(VCOR)          | 58                                              | Power | Grounds the decode clock generator's VCO.                                                                                                                                                                                                                                           |  |

| AGND(VCOW)          | 43                                              | Power | Grounds the encode clock generator's VCO.                                                                                                                                                                                                                                           |  |

| DGND                | 1, 2<br>19 - 22<br>39 - 42<br>59 - 62<br>79, 80 | 2     | Ground lines for cooling.                                                                                                                                                                                                                                                           |  |

| TESTI0              | 36                                              | In    | Test input line. Drive this line high at all times.                                                                                                                                                                                                                                 |  |

| TESTI1              | 68                                              | in    | Test input line. Drive this line low in test mode to monitor clock output from the encode clock generator's frequency synthesizer and decode clock generator's VFO.  If RESET is also driven low, the output clocks are locked at center frequency.  Normally, keep this line high. |  |

| TESTI2              | 73                                              | În    | Test input line. Drive this line high at all times.                                                                                                                                                                                                                                 |  |

| TESTO0              | 32                                              | Out   | Test output line. In test mode, this line outputs the clock signal created by the encode clock generator's frequency synthesizer. Normally, leave this line unconnected.                                                                                                            |  |

| TESTO1              | 33                                              | Out   | Test output line. Leave unconnected.                                                                                                                                                                                                                                                |  |

| TESTO2              | 34                                              | Out   | Test output line. Leave unconnected.                                                                                                                                                                                                                                                |  |

| TESTO3              | 67                                              | Out   | Test output line. In test mode, this line outputs the clock signal created by the decode clock generator's VFO.  Normally, leave this line unconnected.                                                                                                                             |  |

| TESTO4              | 69                                              | Out   | Test output line. Leave unconnected.                                                                                                                                                                                                                                                |  |

| TESTO5              | 70                                              | Out   | Test output line. Leave unconnected.                                                                                                                                                                                                                                                |  |

### Registers

The HD153021F has eight 5-bit registers that control the center frequency of the decode clock generator's VFO and the frequency of the encode

clock generator's frequency synthesizer, adjust the decode window, adjust the write precompensation, control the duty cycles of the read clock and reference clock signals output to the disk controller, and select various modes.

#### Registers

| Name                                     | Abbreviation                                                                                                                                                                                                                              |

|------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VCO center frequency control register    | VFC register                                                                                                                                                                                                                              |

| Gain control register                    | GAC register                                                                                                                                                                                                                              |

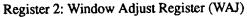

| Window adjust register                   | WAJ register                                                                                                                                                                                                                              |

| Duty control register                    | DTC register                                                                                                                                                                                                                              |

| Write precompensation control register 0 | WPC0 register                                                                                                                                                                                                                             |

| Write precompensation control register 1 | WPC1 register                                                                                                                                                                                                                             |

| Write precompensation control register 2 | WPC2 register                                                                                                                                                                                                                             |

| Mode control register                    | MDC register                                                                                                                                                                                                                              |

|                                          | VCO center frequency control register  Gain control register  Window adjust register  Duty control register  Write precompensation control register 0  Write precompensation control register 1  Write precompensation control register 2 |

Note: The registers are initialized to 0 by a low input on the RESET line or STBY line.

#### **Register Descriptions**

Register 0: VCO Center Frequency Control Register (VFC)

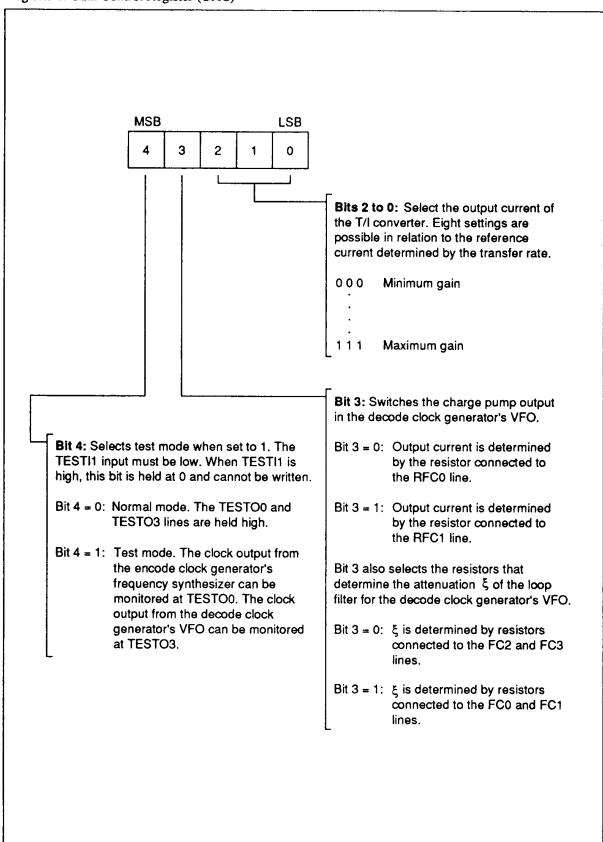

Register 1: Gain Control Register (GAC)

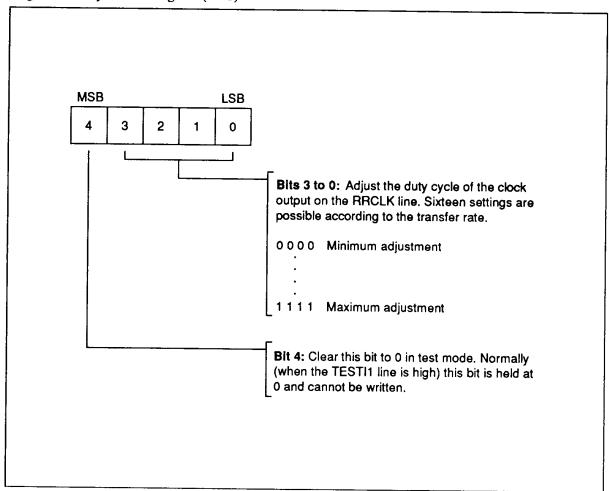

Register 3: Duty Control Register (DTC)

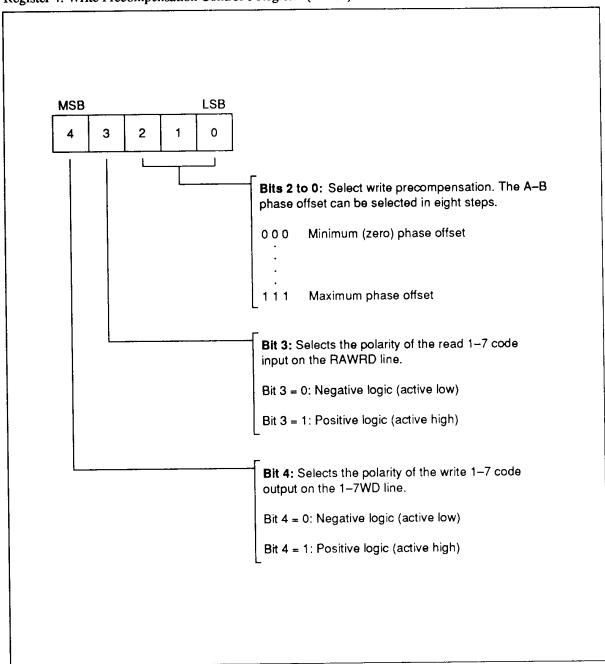

Register 4: Write Precompensation Control 0 Register (WPC0)

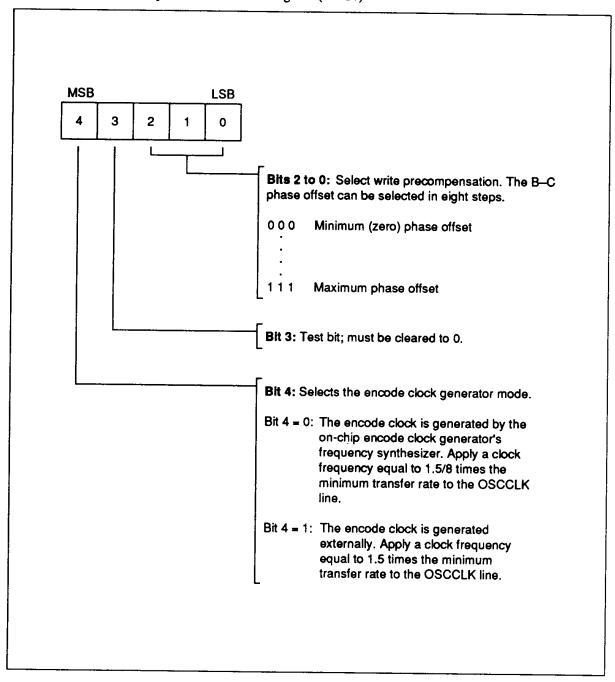

Register 5: Write Precompensation Control 1 Register (WPC1)

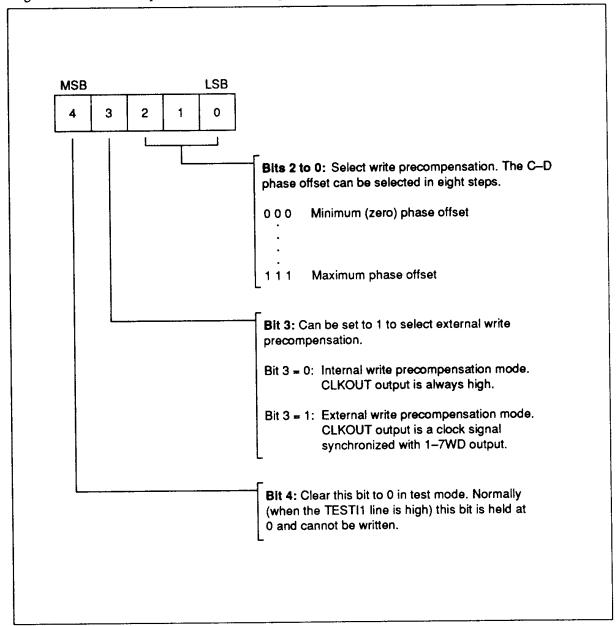

Register 6: Write Precompensation Control 2 Register (WPC2)

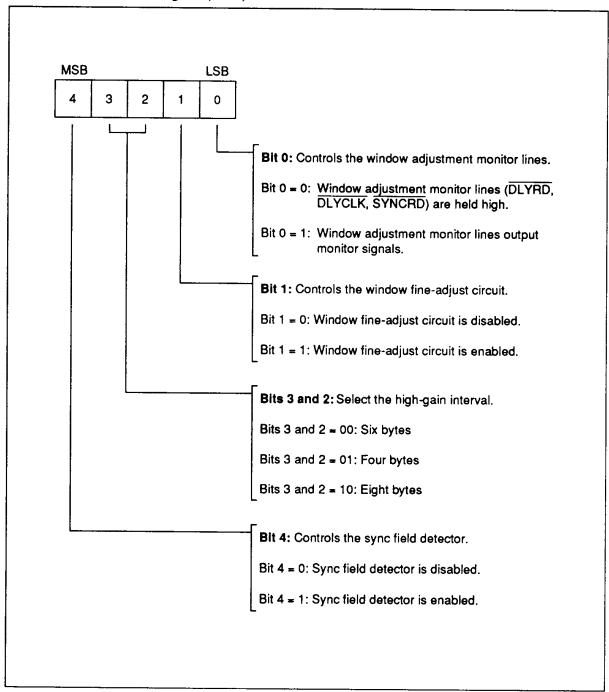

Register 7: Mode Control Register (MDC)

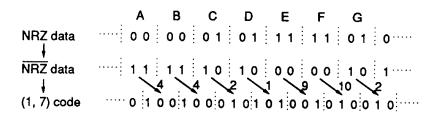

#### 1-7 Encoder/Decoder

The encoder converts an NRZ signal to 1-7 coded data. The decoder converts 1-7 coded data to an NRZ signal. See the conversion table.

The NRZ signal is inverted before conversion to

1-7 code. The disk controller must write 0000... in the sync area. The 3T pattern written in the sync area (100100...) will be decoded to 0000....

The polarity of the 1-7 code can be selected by bit 3 in register WPC0.

#### **Conversion Table**

| Last bit of      | Data bits | Code |      |

|------------------|-----------|------|------|

| previous<br>code | Current   | Next | bits |

| 0                | 10        | 0x   | 101  |

| 0                | 10        | 1x   | 010  |

| 0                | 11        | 00   | 010  |

| 0                | 11        | 00   | 100  |

| 0                | 00        | 0x   | 001  |

| 0                | 00        | 1x   | 000  |

| Last bit of      | Data bits | Code |      |

|------------------|-----------|------|------|

| previous<br>code | Current   | Next | bits |

| 0                | 01        | 0x   | 001  |

| 0                | 01        | 1x   | 000  |

| 1                | 00        | 0x   | 001  |

| 1                | 00        | 1x   | 010  |

| 1                | 01        | 00   | 010  |

| 1                | 01        | 00   | 000  |

00: Not 00 x: Don't care

#### 1-7 Code Polarity Selection

1-7 Code Input Polarity Selection

#### **WPC0 Register**

| 4           | 3 | 2           | 1           | 0   | 1-7 code input on RAWRD line |

|-------------|---|-------------|-------------|-----|------------------------------|

| <del></del> | 0 | <del></del> | _           | _   | Negative logic (active low)  |

| _           | 1 | <del></del> | <del></del> |     | Positive logic (active high) |

| MSB         |   |             |             | LSB |                              |

1-7 Code Output Polarity Selection

#### **WPC0 Register**

| 4   | 3        | 2 | 1           | 0   | 1-7 code output on 1-7WD line |

|-----|----------|---|-------------|-----|-------------------------------|

| 0   |          |   |             |     | Negative logic (active low)   |

| 1   | <u> </u> |   | <del></del> |     | Positive logic (active high)  |

| MSB |          |   |             | LSB |                               |

An example of the conversion of an NRZ signal to (1, 7) coded data is given below.

The NRZ data is inverted before it is converted into (1, 7) code. For example, when the above NRZ B data ('00') is converted, it is first inverted to give the NRZ data '11', then the last bit ('0') of

the result of converting A ('100') and the next NRZ data status C '01' (C = '10') dictate that 4 is selected from the conversion table, so that the B data '00' is converted into the (1, 7) code '100'.

#### **Conversion Table**

#### 1, 7 code bits

| No. | Previous   | Current | Next         | <br>NRZ data bits |  |  |

|-----|------------|---------|--------------|-------------------|--|--|

| 1   | X 1 0      | 000     | xxx          | 0 0               |  |  |

| 2   | X 0 0      | 000     | xxx          | 0 1               |  |  |

| 3   | XXX        | 100     | xxx          | 1 1               |  |  |

| 4   | XXO        | 010     | 00X          | 1 0               |  |  |

| 5   | XX0 010    |         | 0 0 X        | 11                |  |  |

| 6   | X X X 1 01 |         | xxx          | 10                |  |  |

| 7   | X 0 0      | 001     | xxx          | 0 1               |  |  |

| 8   | X 1 0      | 001     | xxx          | 0 0               |  |  |

| 9   | X X 1      | 001     | xxx          | 0 0               |  |  |

| 10  | XX1 010    |         | <u>0 0 X</u> | 0 0               |  |  |

| 11  | XX1 010    |         | 0 0 X        | 01                |  |  |

| 12  | X X 1      | 000     | xxx          | 01                |  |  |

x: Don't care 0 0: Not 0 0

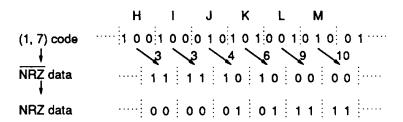

An example of the conversion of (1, 7) coded data to an NRZ signal is given below.

For example, when the above (1, 7) coded I = 100 data is converted into NRZ data, the previous status H = 100 and the next status J = 100

dictate that 3 is selected from the conversion table, so the data is converted into the NRZ data '11'. This is inverted and output as the NRZ data '00'

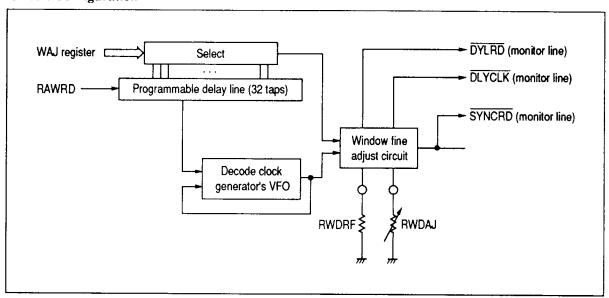

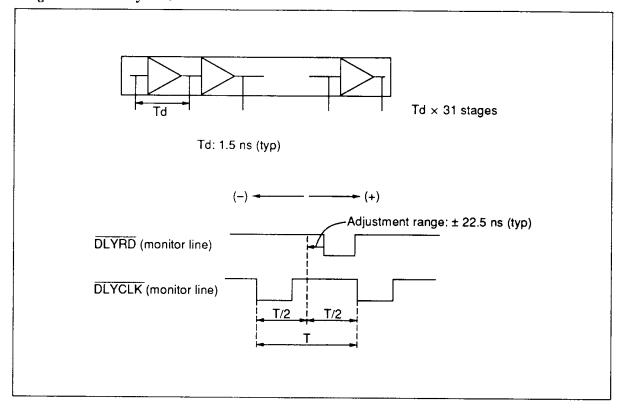

#### Window Adjust Circuit

The decode window is centered by means of a programmable, on-chip delay line. The centering is adjusted by setting one of 32 values in the WAJ

register. This can be done under microcontroller control for automatic centering. If more precise adjustment is required, the window fine-adjust circuit enables you to perform continuous adjustment while monitoring the signal waveform.

#### **Circuit Configuration**

#### Programmable Delay Line

| WA | J Regis | ter | Dolov line ton |   |                                          |

|----|---------|-----|----------------|---|------------------------------------------|

| 4  | 3       | 2   | 1 0            |   | <ul><li>Delay line tap<br/>No.</li></ul> |

| 1  | 1       | 1   | 1              | 1 | -16                                      |

|    |         |     | ţ              |   | I                                        |

| 1  | 0       | 0   | 0              | 1 | -2                                       |

| 1  | 0       | 0   | 0              | 0 | -1                                       |

| 0  | 0       | 0   | 0              | 0 | 0                                        |

|   |   | Delay line to |       |                                                 |

|---|---|---------------|-------|-------------------------------------------------|

| 3 | 2 | 1             | 0     | <ul> <li>Delay line tap</li> <li>No.</li> </ul> |

| 0 | 0 | 0             | 1     | +1                                              |

| 0 | 0 | 1             | 0     | +2                                              |

|   |   | I             |       | l                                               |

| 1 | 1 | 1             | 1     | +15                                             |

|   | 0 | 0 0           | 0 0 0 | 0 0 0 1                                         |

#### Window Fine-Adjust Circuit

| Line  | Resistance              |

|-------|-------------------------|

| RWDRF | 10 – 20 kΩ (reference)  |

| RWDAJ | 10 – 20 kΩ (adjustment) |

Notes: 1. The adjustment is determined by the relative resistances of the resistor connected to the RWDRF line and the resistor connected to the RWDAJ line. Any combination of resistances can be used.

2. When the adjustment exceeds the tap interval (1.6 ns) on the delay line, stability can be improved by changing the delay line tap selection and reducing the adjustment.

#### Window Adjustment Mode

#### **MDC Register**

| 4   | 3 | 2                                     | 1 | 0   | Window adjustment mode                                    |

|-----|---|---------------------------------------|---|-----|-----------------------------------------------------------|

|     | _ | _                                     | 0 | 0   | Delay line only, monitor lines off                        |

| _   | _ | · · · · · · · · · · · · · · · · · · · | 0 | 1   | Delay line only, monitor lines on                         |

| _   |   |                                       | 1 | 0   | Delay line and fine-adjustment circuit, monitor lines off |

| _   | _ | _                                     | 1 | 1   | Delay line and fine-adjustment circuit, monitor lines on  |

| MSB | · |                                       |   | LSB |                                                           |

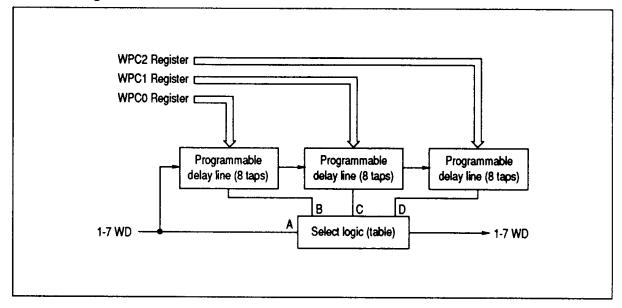

#### Write Precompensation Circuit

The write precompensation circuit contains data divided into four blocks according to combinations of the number of 0 bits between adjacent 1 bits. Settings in registers WPC0, WPC1, and WPC2 can

establish phase offsets of up to 10 ns (typ) between the blocks, in eight steps each.

Write precompensation can also be performed externally, using a clock signal output on the CLKOUT line in synchronization with the output on the 1-7WD line.

#### **Circuit Configuration**

#### Table

| <sup>2</sup> | 1 | 2 | 3 | 4 | 5 | 6 | 7 |

|--------------|---|---|---|---|---|---|---|

| 1            | C |   |   | - | 4 |   |   |

| 2            |   |   |   |   |   |   |   |

| 3            |   |   |   |   |   |   |   |

| 4            | D |   |   |   | 3 |   |   |

| 5            |   |   |   | • |   |   |   |

| 6            |   |   |   |   |   |   |   |

|              |   |   |   |   |   |   |   |

$$\begin{array}{ccccc}

& n & m \\

\hline

& 10 \cdots 0 & 1 & 0 \cdots 01 \\

& Last & This & Next \\

& 3 & 4 & 5

\end{array}$$

n: Number of 0s between this 1 bit and last 1 bit m: Number of 0s between this 1 bit and next 1 bit

#### Programmable Delay Line

#### WPC0 register

| 4   | 3 | 2           | 1           | 0   | A-B phase offset (unit: Td) |

|-----|---|-------------|-------------|-----|-----------------------------|

|     | _ | 0           | 0           | 0   | 0                           |

|     |   | ļ           |             |     | 1                           |

|     | _ | 1           | 1           | 1   | 7                           |

| MSB |   | <del></del> | <del></del> | LSB |                             |

#### HD153021F WPC1 register 3 2 B-C phase offset (unit: Td) 1 0 0 0 0 0 1 1 1 7 **MSB** LSB

#### WPC2 register

| 4   | 3 | 2 | 1 | 0   | C-D phase offset (unit: Td) |  |  |  |

|-----|---|---|---|-----|-----------------------------|--|--|--|

| _   |   | 0 | 0 | 0   | 0                           |  |  |  |

|     |   | 1 |   |     | I                           |  |  |  |

| _   | _ | 1 | 1 | 1   | 7                           |  |  |  |

| MSB |   |   |   | LSB |                             |  |  |  |

#### **External Write Precompensation Mode**

The external write precompensation mode is selected by setting bit 3 of the WPC2 register to 1.

A clock signal synchronized with the 1-7WD output is then output on the CLKOUT line.

#### WPC2 register

| 4   | 3 | 2                   | 1           | 0   | Write precompensation mode                       |

|-----|---|---------------------|-------------|-----|--------------------------------------------------|

|     | 0 |                     | <del></del> |     | Internal write precompensation mode (CLKOUT off) |

| _   | 1 |                     |             | _   | External write precompensation mode (CLKOUT on)  |

| MSB |   | <del> · · · ·</del> |             | LSB |                                                  |

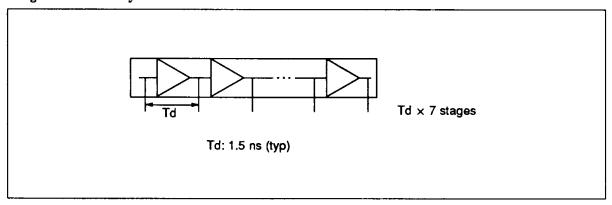

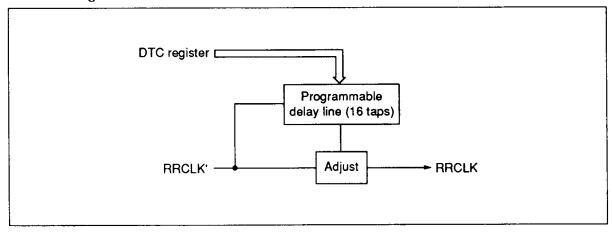

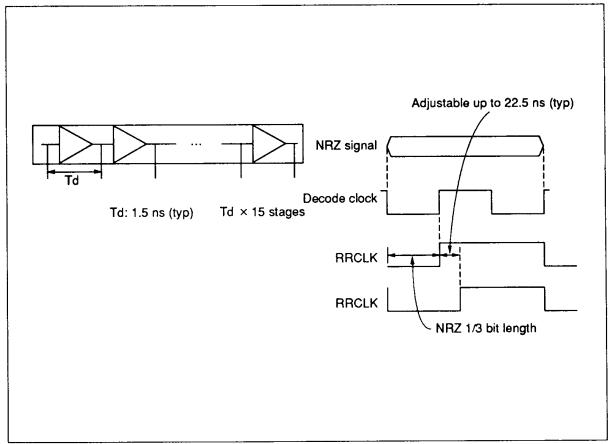

### **Duty Adjustment Circuit**

The read clock and reference clock output to the disk controller are multiplexed and output on the RRCLK line. The duty cycle of the clock output on

the RRCLK line can be adjusted by setting the DTC register.

#### **Circuit Configuration**

#### Programmable Delay Line

#### **DTC register**

| 4   | 3 | 2 | 1 | 0   | Adjustment (unit: Td) |  |  |

|-----|---|---|---|-----|-----------------------|--|--|

|     | 0 | 0 | 0 | 0   | 0                     |  |  |

|     |   |   | l |     | 1                     |  |  |

| _   | 1 | 1 | 1 | 1   | 15                    |  |  |

| MSB |   |   |   | LSB |                       |  |  |

#### **Adjustment Examples**

Table 11 shows adjustment values (n0) that minimize |Derror| (defined below) for several transfer rates in the vicinity of a 50% duty cycle.

$$Derror = \frac{T}{6} - 1.5 \times n0$$

T: Length of 1 NRZ bit

| Transfer rate | NRZ Bit<br>length | Adjustment<br>value | Adjustment size (typ) | DT | °C re | gist | Duty |                |

|---------------|-------------------|---------------------|-----------------------|----|-------|------|------|----------------|

| (Mbps)        | T (ns)            | n0                  | (ns)                  | 3  | 2     | 1    | 0    | - cycle<br>(%) |

| 10            | 100.0             | 11                  | 16.5                  | 1  | 0     | 1    | 1    | 50.2           |

| 15            | 66.7              | 7                   | 10.5                  | 0  | 1     | 1    | 1    | 50.9           |

| 20            | 50.0              | 6                   | 9.0                   | 0  | 1     | 1    | 0    | 48.7           |

| 30            | 33.3              | 3                   | 4.5                   | 0  | 0     | 1    | 1    | 51.7           |

#### **Address Mark Generator and Detector**

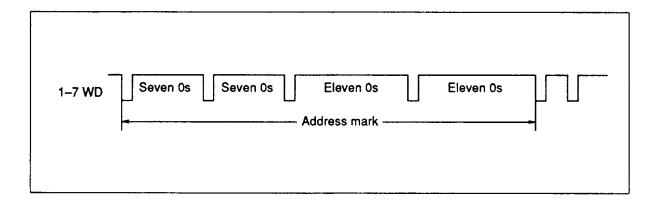

For soft sectoring, on-chip circuits can generate and detect address marks. Address marks are written at the beginning of sectors.

#### **Address Mark Generation**

- When the WG line is high, if the AME line is driven high for 1 to 3 byte lengths, the address mark pattern shown below is output on the 1-7WD line.

- Input on the NRZWD line should be 00....

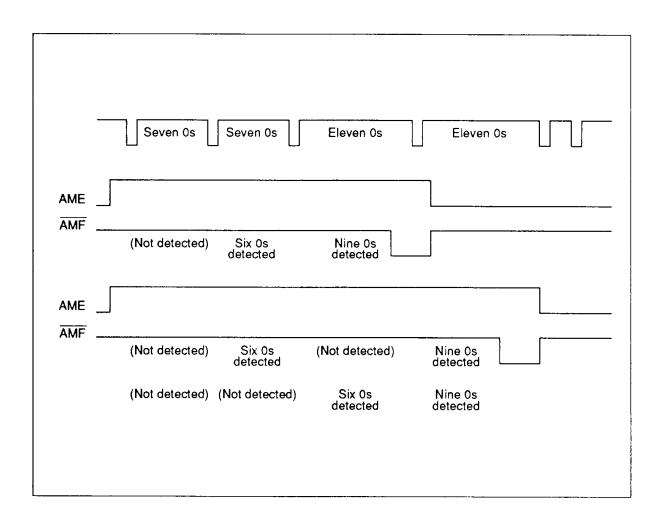

#### Address Mark Detection

- When the WG line is low, address mark detection begins when the AME line is driven high.

- When six consecutive 0 bits are detected, the detector next looks for nine consecutive 0 bits.

- When nine consecutive 0 bits are detected, the AMF line is driven low.

- When the AMF line goes low, the disk controller should drive AME low to reset the AMF line to the high state.

- After six consecutive 0 bits are detected, if five 1 bits are input before nine consecutive 0 bits are detected, the detector starts looking for six consecutive 0 bits again.

- The AMF signal may be output at either of two times, as shown below.

#### **Sync Field Detector**

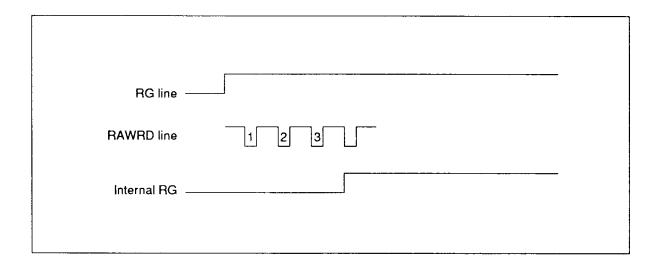

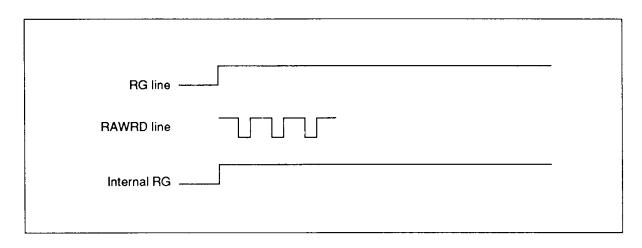

An on-chip sync field detector can ensure that read gating begins in a sync field. After the RG line goes high, the sync field detector waits until three consecutive 3T patterns are detected, then activates the internal RG line.

The RG detector should be enabled whenever soft sectoring is used. Set bit 4 in the MDC register. The high-gain period can be set to last four, six, or eight bytes after the internal RG signal is goes active. Bits 2 and 3 in register MDC select the high-gain period.

#### Sync Field Detector Enabled

#### **MDC** register

| 4   | 3 | 2 | 1 | 0   | Format                                       |

|-----|---|---|---|-----|----------------------------------------------|

| 1   | _ | _ |   | _   | Hard-sectored format or soft-sectored format |

| MSB |   |   |   | LSB |                                              |

#### Sync Field Detector Disabled

#### **MDC** register

| 4   | 3 | 2 | 1 | 0   | Format               |  |

|-----|---|---|---|-----|----------------------|--|

| 0   | _ | _ | _ |     | Hard-sectored format |  |

| MSB |   |   |   | LSB |                      |  |

#### **High-Gain Period**

#### **MDC** register

| 4   | 3 | 2 | 1 | 0   | High-gain period |

|-----|---|---|---|-----|------------------|

|     | 0 | 0 | _ |     | 6 Bytes          |

| _   | 0 | 1 |   | _   | 4 Bytes          |

|     | 1 | 0 |   |     | 8 Bytes          |

| MSB |   |   |   | LSB |                  |

#### **Test Mode**

The clock signals output by the encode clock generator's frequency synthesizer and the decode clock generator's VFO can be monitored directly by setting the chip to test mode. (In normal mode, these clock signals are divided and output from RRCLK.) The clock signals can be locked to the VCO center frequencies set by the resistors connected to the RSVCO and RFVCO lines by driving the RESET line low. The monitored clock frequency is 1.5 times the data transfer rate.

#### **Setting Procedure**

- · Drive the TESTI1 line low.

- Set bit 4 in the GAC register to 1. This causes the clock signal from the encode clock generator's frequency synthesizer to be output on the TESTOO line, and the clock signal from the decode clock generator's VFO on the TESTO3 line.

- Bit 4 in the DTC register and bit 4 in the WPC2 register must be cleared to 0. (See note)

- Drive the RESET line low. The encode clock output on the TESTOO line will be locked to the center frequency set for the minimum data transfer rate by the resistor connected to the RSVCO line. The decode clock output on the TESTO3 line will be locked to the center frequency set for the minimum data transfer rate by the resistor connected to the RFVCO line.

- When the TESTI1 line is driven high, bit 4 in the GAC register is reset and normal mode resumes.

Note: During normal operation (when the TESTI1 line is high), bit 4 of these registers is held at 0 and cannot be written.

| GAC register |    |    |    |     |  |  |

|--------------|----|----|----|-----|--|--|

| D4           | D3 | D2 | D1 | D0  |  |  |

| 1            | _  | _  |    | _   |  |  |

| MSB          |    |    |    | LSB |  |  |

| WPC2 register |    |          |    |     |  |  |

|---------------|----|----------|----|-----|--|--|

| D4            | D3 | D2       | D1 | D0  |  |  |

| 0             | _  | <u>-</u> |    |     |  |  |

| MSB           |    |          |    | LSB |  |  |

#### **DTC** register

| D4  | D3 | D2 | D1 | D0  |

|-----|----|----|----|-----|

| 0   |    | _  |    | _   |

| MSB |    |    |    | LSB |

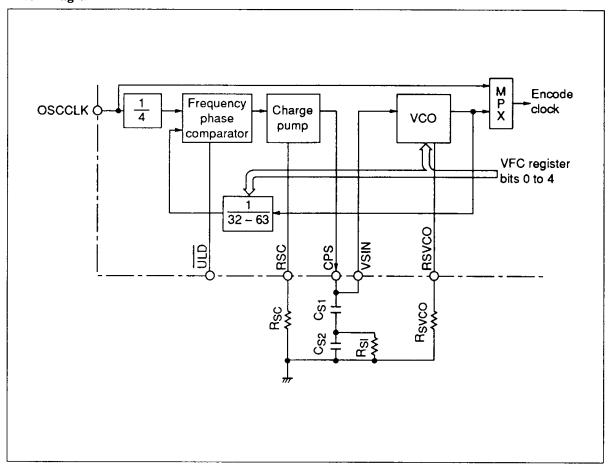

### **Encode Clock Generator's Frequency Synthesizer**

### **Block Diagram**

#### **Function**

- A PLL-type frequency synthesizer generates the encode clock.

- The encode clock frequency can be set by bits 0 to 4 of register VFC to a value N/32 times the minimum data transfer rate (innermost track on the disk), where 32 ≤ N ≤ 63.

- The lock/unlock function (ULD line) can prevent data from being written when a drive fault occurs.

- Direct, external input of the encode clock (at 1.5 times the transfer rate) is also possible without using the on-chip frequency synthesizer.

- The VCO center frequency can be selected by bits 0 to 4 of register VFC, so a single external resistor covers the entire setting range.

#### Operation

- Input a reference clock to OSCCLK at 1.5/8 times the drive's minimum transfer rate.

- This signal is internally divided by four and input to the frequency-phase comparator at 1/32 the normally required encoder clock rate.

- The VCO clock is divided by 1/32 to 1/63, depending on bits 0 to 4 of register VFC, and input to the frequency-phase comparator.

$$f_{VCO(W)} = \frac{N}{32} \times f_{LOW}$$

$32 \le N \le 63$

$f_{VCO(W)}$ : VCO output frequency f<sub>LOW</sub>: Encoder clock frequency

corresponding to minimum transfer rate

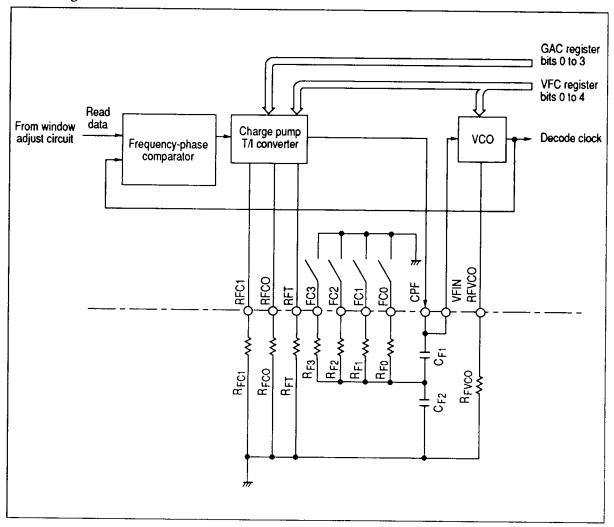

#### **Decode Clock Generator's VFO**

#### **Block Diagram**

#### **Function**

- The phase of the VCO clock is synchronized with the read data from the window adjust circuit.

- The frequency-phase comparator operates in the frequency-phase comparison mode while acquiring phase lock in the sync field, and in phase comparison mode during synchronization in the data field.

- The charge pump and T/I converter circuits both operate while phase lock is being acquired.

During synchronization, only the T/I converter operates.

- The VFO is synchronized with the encode clock until the read gate signal (RG) is asserted.

- The VCO center frequency can be changed by rewriting bits 0 to 4 of the VFC register, so zone bit recording can be implemented with only a single external resistor.

- The charge pump can provide two output currents, the values of which are controlled by external resistors R<sub>FC0</sub> and R<sub>FC1</sub>. Bit 3 in register GAC selects either of these two currents.

- The T/I converter provides one of eight output currents as selected by bits 0 to 2 of register GAC.

- The loop filter attenuation ζ can be selected by bit 3 of register GAC (two selections).

Independent settings can be made for high gain and normal gain.

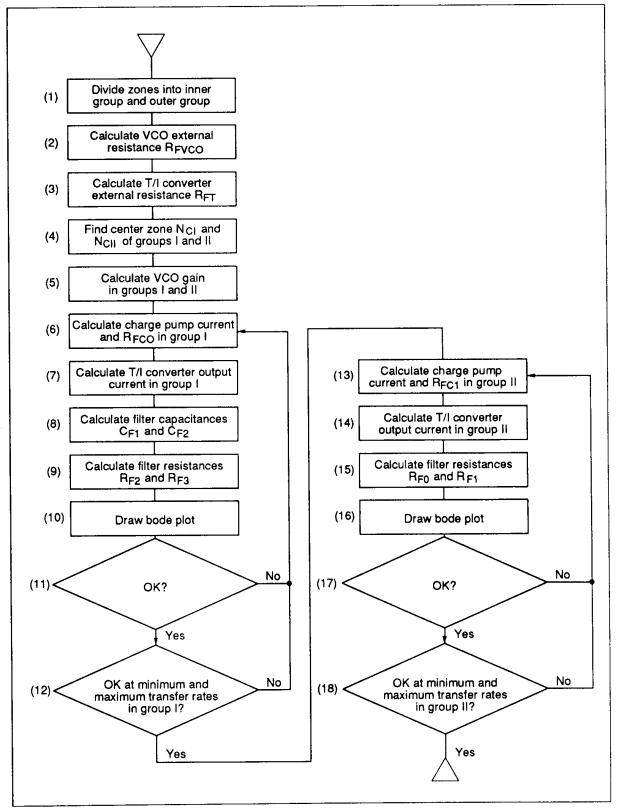

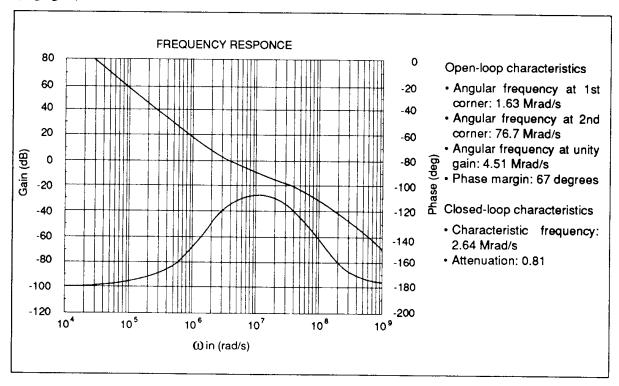

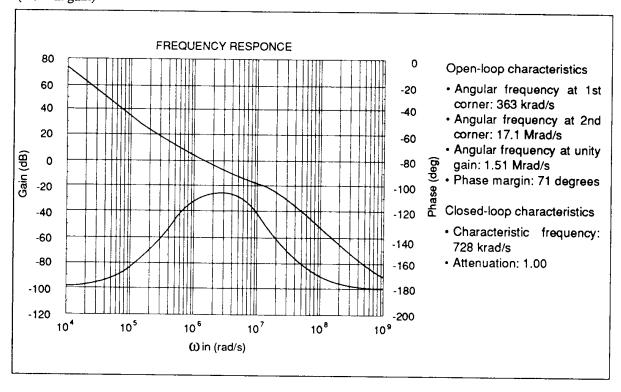

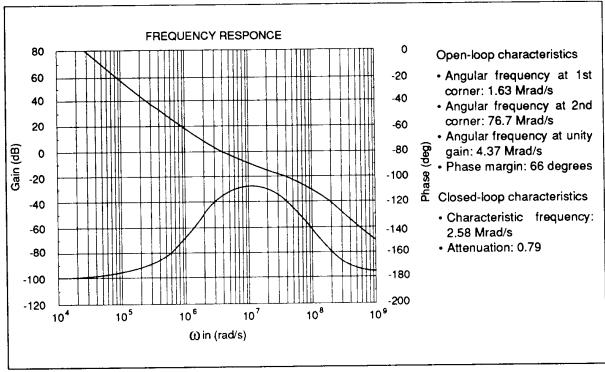

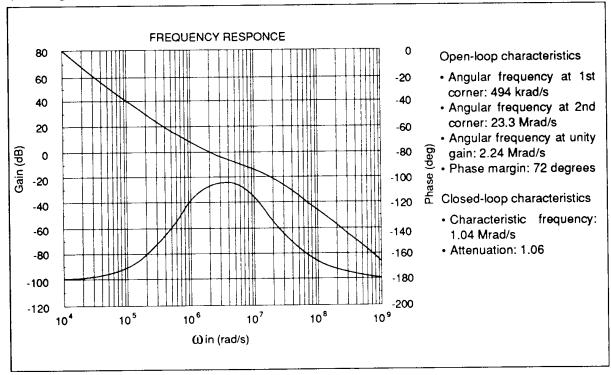

#### Calculation of PLL Constants

#### I. Encode Clock Generator's Frequency Synthesizer

1. VCO center frequency fow

$$f_{OW} = \frac{(2.8125 \times 10^9) \cdot N}{R_{SVCO}}$$

(Hz) .....(I.1)

2. VCO gain KOW

$$K_{OW} = (5.215 \times 10^8) - \sqrt{\frac{N}{R_{SVCO}}} \qquad \left(\frac{rad}{s \cdot V}\right) \qquad (I.2)$$

3. Charge pump current I<sub>CW</sub>

$$I_{CW} = \frac{1.0}{R_{SC}}$$

(A) (I.3)

4. Characteristic frequency ω<sub>nW</sub>

$$\omega_{nW} = \sqrt{\frac{K_{OW} \ge I_{CW}}{2\pi N \cdot C_{S1}}} \qquad \left(\frac{rad}{s}\right) \qquad (1.4)$$

5. Attenuation ζw

$$\zeta_{W} = \frac{(C_{S1} + C_{S2})}{2} \cdot R_{S1} \cdot \omega_{nW}$$

(I.5)

#### II. Decode Clock Generator's VFO

1. VCO center frequency f<sub>OR</sub>

$$f_{OR} = \frac{(2.8125 \times 10^9) \cdot N}{R_{FVCO}}$$

(Hz) (II.1)

2. VCO gain KOR

$$K_{OR} = (1.015 \times 10^9) \cdot \sqrt{\frac{N}{R_{FVCO}}} \quad \left(\frac{rad}{s \cdot V}\right)$$

(II.2)

3. Charge pump current I<sub>CR</sub>

$$I_{CR} = \frac{3.0}{R_{FC}} \qquad (A) \tag{II.3}$$

where  $R_{FC} = RFC0$  when GAC register bit 3 = 0RFC1 when GAC register bit 3 = 1

4. T/I converter external resistance RFT

$$R_{FT} = 4 \cdot R_{FVCO}$$

(II.4)

5. T/I converter current I<sub>TR</sub>

$$I_{TR} = (1.5625 \times 10^{-3}) \cdot \frac{N \cdot L}{R_{FT}}$$

(A) (II.5)

where  $1 \le L \le 8$

6. Characteristic frequency (high gain)  $\omega_{nRH}$

$$\omega_{nRH} = \sqrt{\frac{K_{OR} \cdot \left(\frac{I_{CR}}{6} + I_{TR}\right)}{\pi \cdot C_{F1}}} \quad \left(\frac{rad}{s}\right) \quad (II.6)$$

7. Characteristic frequency (normal gain)  $\omega_{nRN}$