## 12-Bit Deglitched Voltage Out D/A Converter

NATIONS

206

HOLD

12 1.581

HDD-1206 FUNCTIONAL BLOCK DIAGRAM

DIRRENT DUTPUT

1

1.

DESIG

INPUT REGISTER

TIMENG

LOLIUST (F

TEST POINT

# HDD-1206

41

ST BIPCLAS

#### FEATURES

Registers, D/A, Amplifier in Single Hybrid Deglitched Voltage Output 6MHz Update Rate

APPLICATIONS Vector Scan Displays Analytical Instrumentation Digital VCOs Military Systems

GENERAL DESCRIPTION

The Analog Devices HDD-1206 D/A converter combines innovative design techniques with remarkable hybrid construction to achieve deglitched voltage outputs at digital update rates as high as 6MHz.

Despite its small size and low power, the HDD-1206 provides the user with a complete solution to demanding applications which require the conversion of high-speed digital inputs into deglitched analog output voltages.

The unit is housed in an industry standard 32-pin hybrid and contains all the necessary circuit components to provide analog outputs at high update rates without the need for designing external circuits. Input registers, current-output D/A, deglitching circuits, and an output amplifier are all included inside the HDD-1206.

With the deglitching problem solved in a single package, the user of the HDD-1206 is able to incorporate the solution into his system with a minimum of design effort. User involvement is limited to the simple task of establishing the "hold" time for an optimum value by selecting the correct resistor value.

After that step is accomplished, the addition of a low-pass filter at the output of the D/A assures a "clean" voltage representation of the 12 bits of digital information applied to the inputs at video update rates.

The HDD-1206 is available in 32-pin dual in-line ceramic packages.

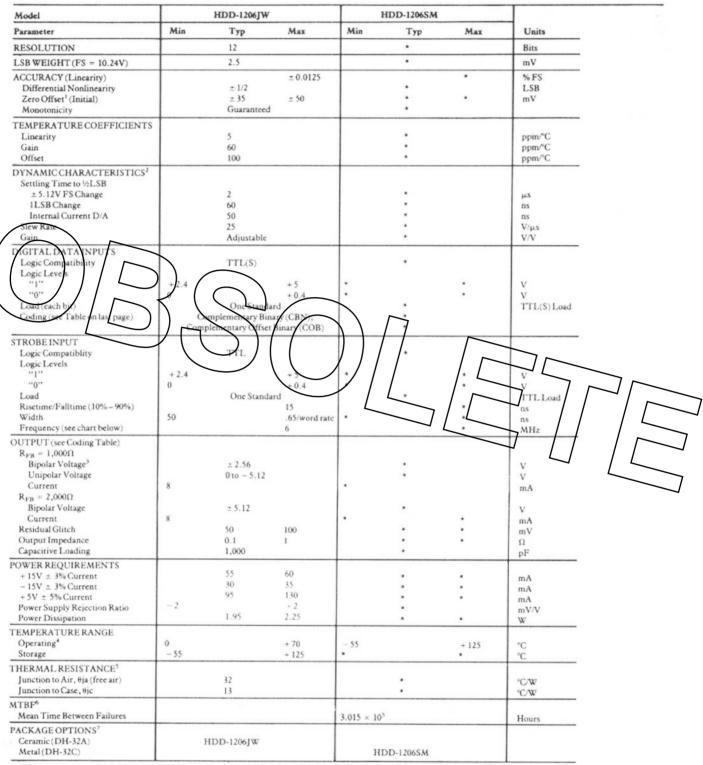

## SPECIFICATIONS (typical @ + 25°C with nominal power supplies and 1kΩ output load unless otherwise noted)

NOTES

Adjustable to zero

Adjustatic to zero. Adjustatic to zero. All dynamic characteristics are based on FS =  $\pm 5.12$ V; R<sub>FR</sub> = 2,000Ω. With R<sub>FR</sub> = 1k, analog output voltages are half those shown in Table on last page \*Case Temperature.

<sup>5</sup>Maximum junction temperature is 150°C.

<sup>5</sup> Makimum Junctoni temperature is 130°C. <sup>6</sup> Calculated per MIL-HDBR 217, Ground, Fixed; Case Temperature. = 60°C. <sup>7</sup> See Section 14 for package outline information.

\*Specifications same as HDD-1206JW.

Specifications subject to change without notice

### Theory of Operation - HDD-1206

#### THEORY OF OPERATION

The equivalent circuit for the for the HDD-1206 D/A converter is shown in functional block diagram.

The unit consists of input registers, fast-settling current output D/A, output amplifier, timing generator, and associated circuits.

The purpose of the input register circuits is to de-skew the input bits and assure their simultaneous arrival at the input of the current D/A. This is critical because time skew on the input data bits is a major contributor to discontinuities, or "glitches," in the analog output of a D/A.

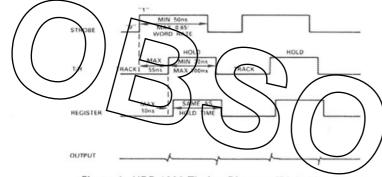

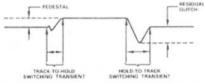

The Timing Generator includes a Track & Hold circuit and generates the required internal pulses for operation whenever it receives a Strobe input pulse. See Figure 1, the HDD-1206 timing diagram.

Figure 1. HDD-1206 Timing Diagram (Digital Inputs not Changing)

As shown, the Strobe pulse is a positive-going TTL pulse supplied by the user of the HDD-1206. Internal timing circuits establish the maximum 55ns delay from the leading edge of the Strobe pulse to the leading edge of the T/H (Track/Hold) pulse; and the maximum 10ns delay from the leading edge of the T/H pulse to the leading edge of the Register pulse. The data from the input registers are strobed into the current D/A at the end of this 65ns interval, so they must be valid by that time.

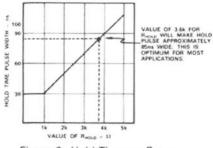

The user determines the width of the T/H pulse (and the Register pulse) by selecting the value of the  $R_{HOLD}$  resistor. See Figures 1 and 2. As shown, the width of the Hold pulse can vary from approximately 30ns to approximately 100ns by using resistor values from 1k to 5k, respectively.

For most applications, a value of  $3.6k\Omega$  and a pulse width of approximately 85ns is the optimum choice. This pulse width will "hold" the analog output of the HDD-1206 D/A until the "glitch" resulting from the most recent update has passed, without infringing on the word rate capabilities of the HDD-1206.

#### **CURRENT-OUTPUT D/A CONVERTERS**

A brief review of the salient characteristics of current D/A converters may be a useful approach to understanding the operation of the HDD-1206 unit.

Current-switching D/A converters are inherently faster than voltage-output types because of the absence of an output amplifier. This means current-switching converters have no slew rate limitation which can slow settling; nor are they subject to the overshoot and ringing problems often associated with feedback amplifiers.

Both current-switching and voltage-output converters display a discontinuity, or "glitch," in their analog outputs because of the basic characteristic of saturated logic (TTL is an example) which causes the propagation delay to be less for negative-going inputs than it is for positive-going inputs.

This difference in propagation delay manifests itself as a "worst case glitch" at the major carry point, or mid-scale, of the output range of the current converter. This is the point at which nearly equal and opposite currents are being switched within the converter.

The "glitch" at mid-scale, the switching point of the Most Significant Bit (MSB), will be halved at the ¼ and ¼ points; halved again at the ¼ and ¾ points, etc. The amplitude of the "glitch," therefore is a function of signal dynamics and cannot be eliminated with filtering.

The variations in glitch amplitude daused by signal dynamics create a multitude of intermodulation (HM) products, some of which fall into the video pass-band as spurious signals, and increased noise level. These HM products are also relatively immune to eligination by filtering.

The amplitude of the glitch can be reduced by de-thewing the input bits; but no amount of de-skewing or filtering can negate the physics of saturated logic which cause the glitch to be generated initially.

The best solution, then, is to cause the glitch to remain a constant across the entire output range of the converter. The efficiencies of the circuit will be enhanced if the solution can also permit using the full drive capabilities of the current-output D/A in either unipolar or bipolar modes of operation.

The design approach used in the Analog Devices HDD-1206 D/A converter accomplishes these desired goals and provides voltage outputs at high update rates.

#### NOTES ON DEGLITCHING

Refer again to the equivalent circuit for the HDD-1206. The data bits are applied through the input register to the current-output D/A converter, which is capable of supplying up to 5.12mA of output current.

The output of the current D/A, in turn, is applied to the input of the output amplifier via strapping external to the HDD-1206. The Timing Generator supplies the necessary pulses and timing to apply signals to the current D/A and output amplifier after the initial glitch caused by the digital inputs has subsided.

The digital "1" (Hold) level of the T/H pulse causes the switch at the input of the amplifier to open, holding the last value of the current D/A converter. During this hold interval, the switching transients caused by updating digital inputs are masked from the amplifier, thereby avoiding HDD-1206 output discontinuities whose amplitude would be a function of signal dynamics.

Ten nanoseconds after the T/H pulse goes to the digital "1" level, the register pulse also changes state from "0" to "1".

This transition moves the output of the current D/A to the new value established by the most recent digital inputs applied to the HDD-1206.

Any change in the current D/A output has stablized by the time the T/H pulse returns to the digital "0" (Track) level. Re-establishing the track mode closes the switch at the input of the amplifier and the output of the HDD-1206 moves to the new analog value dictated by the digital input word.

As shown in Figure 1, the output of the HDD-1206 will contain switching transients associated with the T/H pulse. But these "glitches" will be constant in amplitude and duration and will occur at the update rate, since they are a function of the strobe pulse applied by the user.

These switching transients will settle out in approximately 500ns, and will have uniform amplitude over the complete analog output range of the D/A. For strobe rates of 2MHz and above, the settling interval switching from "hold" to "track", and vice versa, will produce a constant dc offset on the output. The HOD-1206 is not intervaled to get rid of all glitches per se; it is

designed o provide a constant amplitude glitch.

When the der the transies are u t cur e is held onstant, the a single-line frequenc ctrum of the glitch is a fine tine SD e sample i tte fr of the trum at the quen nd harm nics mole equer

The HDD-12 ffectively elin inates the IM i d cussed above. When it does, the signal-to noise (S/N ppr aches rat that of an ideally-quantized signal, where the rm n p.  $q/\sqrt{12}$ , when frequencies above Nyquist are filtered of

#### GLITCH VS. PEDESTAL

In addition to the "glitch" which is a characteristic of current D/As, the track & hold used in the HDD-1206 also contributes an anomaly to the output signal.

Refer to Figure 3. This diagram compares the "glitch" created by the HDD-1206 to the pedestal created by the internal T/H circuits.

Figure 3. Pedestal/Glitch Relationship

As shown, the "glitch" is a transient signal which remains constant in width and amplitude over the entire output range, at all update rates. The pedestal, on the other hand, is an offset signal whose amplitude can vary (because of switching transient settling) as a function of hold time and word rate.

This pedestal is caused by charge transfer associated with the hold capacitor; the transfer occurs when the HDD-1206 circuits are switched from a "track" to "hold" condition. The pedestal is basically an offset error in the HDD-1206 output and can be compensated with the Offset Adjust when the unit is installed in the user's system.

Figure 3 is not drawn to scale; there is no attempt to imply the identified elements have precisely that relationship to one another. They are exaggerated for illustrative purposes.

### Applications

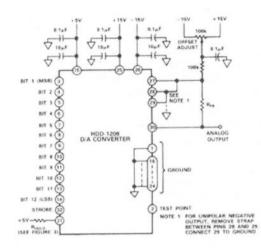

Bipolar connections for the HDD-1206 D/A converter are shown in Figure 4. As indicated, a unipolar negative output is accomplished by connecting Bipolar Pin 29 to ground, instead of to Pins 27 and 28.

Figure 4. HDD-1206 Bipolar Connections

The output voltage swing is established by the value of feedback resistor  $R_{FB}$ . The table below indicates output levels for both unipolar and bipolar operation, with feedback resistors of either 1,000 $\Omega$  or 2,000 $\Omega$ .

Hold resistor  $R_{HOLD}$  connected between the +5V supply and in 31 year the width of the Hold mode of the T/H pulse. Test Paint I in 2 is used for observing the pulse.

T Adjust potentiometer is ffse used to set the desired analog t of the HDD-1206 and can be used to help assure correct 01 tp olt ire present w ien he D/A is ins lled in the me-4 W en operated in a u lar mode with digit to nip tinu ous strobe pulses an plie , the Of all inputs but no con set Adjust is set for an analog output of -5.12 / or less 1LS 1k for the value of RFB (NOTE: At least one strobe pu se needs to be applied to latch the input data into the regi ster If the HDD-1206 is installed in a system and the strob pu applied continuously, the Offset Adjust is calibrated for desired output value with a digital "0" applied to all input pins.

#### HDD-1206 ANALOG OUTPUT WITH 1kΩ LOAD

| Digital<br>Inputs | Complementary<br>Offset Binary (COB)<br>Bipolar Output<br>R <sub>FB</sub> = 2k | $\begin{array}{l} Complementary  Binary  (CBN) \\ Unipolar  Negative  Output \\ R_{FB} =  1k \end{array}$ |

|-------------------|--------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|

| 111111            | + 5.12 (+ FS)                                                                  | 0.0000(0)                                                                                                 |

| 111110            | + 5.1175                                                                       | - 0.00125(+1LSB)                                                                                          |

| 110000            | + 2.5625 ( + 1/2FS)                                                            | - 1.27875                                                                                                 |

| 101111            | + 2.56                                                                         | - 1.28(1/4)                                                                                               |

| 100000            | +0.0025(+1LSB)                                                                 | - 2.55875                                                                                                 |

| 011111            | 0.0000                                                                         | - 2.56(1/2)                                                                                               |

| 010000            | -2.5575(-1/2FS)                                                                | - 3.83875                                                                                                 |

| 001111            | -2.56                                                                          | - 3.84(3/4)                                                                                               |

| 000001            | - 5.1150                                                                       | - 5.1175                                                                                                  |

| 000000            | -5.1175(-FS-1LSB)                                                              | - 5.11875 (FS - 1LSB)                                                                                     |

#### ORDERING INFORMATION

Model HDD-1206JW D/A converter is housed in a ceramic package, the model HDD-1206SM is a hermetically sealed version; outline dimensions are shown elsewhere.

Mating individual pin sockets are available from AMP. Part number 6-330808-0 are knockout end type; 6-330808-3 are open end type.