### **General Description**

variation.

The HM1460 is a voltage mode, fixed 300kHz switching frequency, synchronous buck converter. The HM1640 allows wide input voltage that is either a single 5~12V or two supply voltage(s) for various applications. A power-on-reset (POR) circuit monitors the VCC supply voltage to prevent wrong logic controls. A builtin soft-start circuit prevents the output voltages from overshoot as well as limits the input current. An internal 0.8V temperature-compensated reference voltage with high accuracy is designed to meet the requirement of low output voltage applications. The HM1640 provides excellent output voltage regulations against load current

The controller's over-current protection monitors the output current by using the voltage drop across the RDS(ON) of low-side MOSFET, eliminating the need for a current sensing resistor that features high efficiency and low cost. In addition, the HM1460 also integrates excellent protection functions: The over-voltage protection (OVP), under-voltage protection (UVP). OVP circuit which monitors the FB voltage to prevent the PWM output from overvoltage, and UVP circuit which monitors the FB voltage to prevent the PWM output from under-voltage or short-circuit. The HM1640 is available in SOP-8P and TDFN3x3-10 packages.

#### **Features**

- Wide 5V to 12V Supply Voltage

- Power-On-Reset Monitoring on VCC

- Excellent Output Voltage Regulations 0.8V Internal Reference ±1% Over-Temperature Range

- Integrated Soft-Start

- Voltage Mode PWM Operation with External Compensation

- Up to 90% Duty Ratio for Fast Transient Response

- Constant Switching Frequency 300kHz ±10%

- Drive Dual Low Cost N-MOSFETs with Adaptive Dead-Time Control

- 50% Under-Voltage Protection

- 125% Over-Voltage Protection

- Adjustable Over-Current Protection Threshold Using the RDS(ON) of Low-Side MOSFET

- Shutdown Control by COMP

- Power Good Monitoring (TDFN-10 3mmx3mm Package Only)

- SOP-8P and TDFN3x3-10 Packages

- Lead Free and Green Devices Available (RoHS Compliant)

### **Applications**

- Graphic Cards

- DSL, Switch HUB

- Wireless Lan

- Notebook Computer

- Mother Board

- LCD Monitor/TV

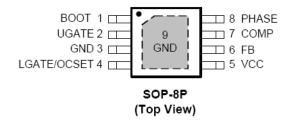

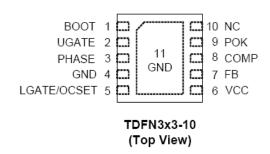

## **Pin Assignments**

| PIN           |                          |       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |

|---------------|--------------------------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| NO.<br>SOP-8P | NO. SOP-8P TDFN3x3-10 N. |       | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |

| 1             | 1                        | воот  | This pin provides the bootstrap voltage to the high-side gate driver for driving the N-channel MOSFET. An external capacitor from PHASE to BOOT, an internal diode, generates the bootstrap voltage for the high-side                                                                                                                                                                                                                                                                                      |  |

| 2             | 2                        | UGATE | High-side Gate Driver Output. This pin is the gate driver for high-side                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

| 3             | 4                        | GND   | Signal and Power ground. Connecting this pin to system ground.                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

| 4             | 5                        | LGATE | Low-side Gate Driver Output and Over-Current Setting Input. This pin is the gate driver for low-side MOSFET. It also used to set the maximum inductor current. Refer to the section in "Function Description" for detail.                                                                                                                                                                                                                                                                                  |  |

| 5             | 6                        | vcc   | Power Supply Input. Connect a nominal 5V to 12V power supply voltage to this pin. A power-on-reset function monitors the input voltage at this pin. It is recommended that a decoupling capacitor (1 to 10 F) is connected to GND for noise decoupling.                                                                                                                                                                                                                                                    |  |

| 6             | 7                        | FB    | Feedback Input of Converter. The converter senses feedback voltage via FB and regulates the FB voltage at 0.8V. Connecting FB with a resistor-divider from the output sets the output voltage of the converter.                                                                                                                                                                                                                                                                                            |  |

| 7             | 8                        | СОМР  | This is a multiplexed pin. During soft-start and normal converter operation, this pin represents the output of the error amplifier. It is used to compensate the regulation control loop in combination with the FB pin. Pulling COMP low ( $V_{DISABLE} = 0.4V$ max.) will shut down the controller. When the pull-down device is released, the COMP pin will start to rise. When the COMP pin rises above the $V_{DISABLE}$ trip point, the HM1640 will begin a new initialization and soft-start cycle. |  |

HM1460

| 8                 | 3                  | PHASE | This pin is the return path for the high-side gate driver. Connecting this pin to the high-side MOSFET source and connect a capacitor to BOOT for the bootstrap voltage. This pin is also used to monitor the voltage drop across the low-side MOSFET for over-current protection. |

|-------------------|--------------------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 9(Exposed<br>Pad) | 11(Exposed<br>Pad) | IGND  | Thermal Pad. Connect this pad to the system ground plan for good thermal conductivity.                                                                                                                                                                                             |

| _                 | 9                  | IPOK  | POK is an open drain output used to indicate the status of the output voltage. Connect the POK pin to 5 to 12V through a pull-high resistor.                                                                                                                                       |

| _                 | 10                 | NC    | No Connect                                                                                                                                                                                                                                                                         |

## **Ordering Information**

|                | fl! |                                              |

|----------------|-----|----------------------------------------------|

| Circuit Type — |     | — Packing:<br>Blank: Tube<br>R:Type and Reel |

| Package        |     |                                              |

| E:SOP8-PP      |     |                                              |

| D:TDFN         |     |                                              |

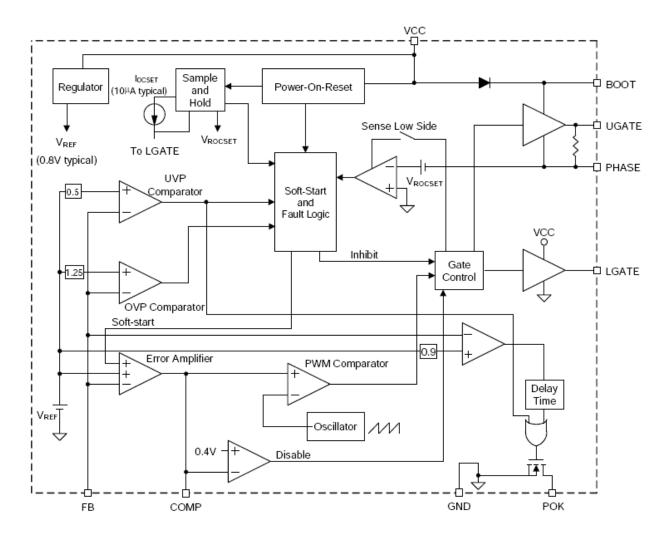

## **Functional Block Diagram**

Functional Block Diagram of fl!

### **Absolute Maximum Ratings**

| Symbol             | Parameter                                      | Rating                    | Unit                          |    |

|--------------------|------------------------------------------------|---------------------------|-------------------------------|----|

| V <sub>VCC</sub>   | VCC Supply Voltage (VCC to GND)                |                           | -0.3 ~ 16                     | V  |

| V <sub>BOOT</sub>  | BOOT Supply Voltage (BOOT to PHASE)            |                           | -0.3 ~ 16                     | V  |

| VBOOT              | BOOT Supply Voltage (BOOT to GND)              |                           | -0.3 ~ 30                     | V  |

| $V_{UGATE}$        |                                                | > 20ns                    | -0.3 ~ V <sub>воот</sub> +0.3 | V  |

| V UGATE            | UGATE Voltage (UGATE to PHASE)                 | < 20ns                    | -5 ∼ V <sub>воот</sub> +5     | V  |

| V <sub>LGATE</sub> |                                                | > 20ns                    | -0.3 ~ V <sub>vcc</sub> +0.3  | V  |

| V LGATE            | LGATE Voltage (LGATE to GND)                   | < 20ns                    | -5~ V <sub>vcc</sub> +5       | V  |

| V <sub>PHASE</sub> |                                                | > 20ns                    | -0.3 ~ 16                     | V  |

| V PHASE            | PHASE Voltage (PHASE to GND)                   | < 20ns                    | -8 ~ 30                       | V  |

|                    | FB and COMP to GND                             |                           | -0.3 ~ 7                      | V  |

|                    | POK to GND                                     | -0.3~V <sub>cc</sub> +0.3 | V                             |    |

| TJ                 | Maximum Junction Temperature                   | 150                       | °C                            |    |

| T <sub>STG</sub>   | Storage Temperature                            | -65 ~ 150                 | °C                            |    |

| $T_{SDR}$          | Maximum Lead Soldering Temperature, 10 Seconds |                           | 260                           | °C |

Note: Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any other conditions beyond those indicated under "recom- mended operating conditions" is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device <u>reliability</u>.

### **Recommended Operating Conditions**

| Symbol | Parameter                | Range      | Unit |

|--------|--------------------------|------------|------|

| VIN    | VIN Supply Voltage       | 3.3 ~ 13.2 | V    |

| VVCC   | VCC Supply Voltage       | 4.5 ~ 13.2 | V    |

| VOUT   | Converter Output Voltage | 0.8 ~ 5.5  | V    |

| IOUT   | Converter Output Current | 0 ~ 20     | Α    |

| Тд     | Ambient Temperature      | -40 ~ 85   | °C   |

| TJ     | Junction Temperature     | -40 ~ 125  | °C   |

Note: Refer to the application circuit for further information.

### **Thermal Characteristics**

| Symbol | Parameter                                        | Typical Value | Unit |

|--------|--------------------------------------------------|---------------|------|

|        | Thermal Resistance -Junction to Ambient (Note 2) |               |      |

| JA     | SOP-8P                                           | 60            | °C/W |

Note :is measured with the component mounted on a high effective thermal conductivity test board in free air.

### **Electrical Characteristics**

Refer to the typical application circuit. These specifications apply over  $V_{VCC} = 12V$ ,  $T_A = -40$ °C to 85°C, unless otherwise noted. Typical values are at  $T_A = 25$ °C.

| Symbol  | Parameter                             | Test Conditions                      | < A % (\$ |      |       |      |

|---------|---------------------------------------|--------------------------------------|-----------|------|-------|------|

|         |                                       |                                      | Min.      | Тур. | Max.  | Unit |

| INPUT S | SUPPLY VOLTAGE AND CURREN             | Т                                    |           |      |       | •    |

| IVCC    | VCC Supply Current (Shutdown          | UGATE and LGATE open                 | ; -       | -    | 700   | uA   |

|         | Mode)                                 | COMP=GND                             |           |      |       |      |

|         | VCC Supply Current                    | UGATE and LGATE open                 | _         | 2    | 3     | mΑ   |

| POWER   | -ON-RESET(POR)                        |                                      |           |      |       |      |

|         | Rising VCC POR Threshold              |                                      | 3.8       | 4.1  | 4.4   | V    |

|         | VCC POR Hysteresis                    |                                      | 0.3       | 0.5  | 0.6   | V    |

| OSCILL  | ATOR                                  |                                      |           |      |       |      |

| FOSC    | Oscillator Frequency                  |                                      | 270       | 300  | 330   | kHz  |

| Vosc    | (Note 4)                              | (1.2V~2.7V typical)                  | _         | 1.5  | _     | V    |

| DMAX    | Maximum Duty Cycle                    |                                      | -         | -    | 90    | %    |

| REFERI  | ENCE                                  |                                      |           |      |       |      |

| VREF    | Reference Voltage                     | TA = -40 ~ 85°C                      | 0.792     | 8.0  | 0.808 | V    |

|         | Converter Line/Load Regulation        | $VCC=4.5\sim13.2V$ , $IOUT = 0 \sim$ | -0.2      | -    | 0.2   | %    |

| ERROR   | AMPLIFIER                             |                                      |           |      |       |      |

| gm      | Transconductance (Note)               |                                      | -         | 667  | -     | A/V  |

|         | Open-Loop Bandwidth <sup>(Note)</sup> | RL = 10k , CL = 10pF                 | _         | 20   | -     | MHz  |

|         | FB Input Leakage Current              | VFB = 0.8V                           | _         | -    | 0.1   | uA   |

|         | COMP High Voltage                     | RL = OPEN                            | -         | 3    |       |      |

|         | COMP Low Voltage                      | RL = OPEN                            | -         | 1.5  | -     | V    |

|         | Maximum COMP Source Current           | VCOMP = 2V                           | -         | 200  | -     | uA   |

|         | Maximum COMP Sink Current             | VCOMP = 2V                           | _         | 200  | _     |      |

## **Electrical Characteristics(Cont.)**

Refer to the typical application circuit. These specifications apply over  $V_{VCC}$  = 12V,  $T_A$  = -40°C to 85°C, unless otherwise noted. Typical values are at  $T_A$  = 25°C.

| Symbol                  | Parameter                               | Test Conditions                                                   | HM1640 |      |      |      |

|-------------------------|-----------------------------------------|-------------------------------------------------------------------|--------|------|------|------|

|                         |                                         |                                                                   | Min.   | Тур. | Max. | Unit |

| GATE DR                 | RIVERS                                  |                                                                   |        |      |      |      |

|                         | High-Side Gate Driver Source            | $V_{BOOT-GND}$ = 12V, $V_{UGATE-PHASE}$ = 6V                      | -      | 1.0  | _    |      |

|                         | High-Side Gate Driver Sink Current      | $V_{BOOT-GND} = 12V_{UGATE-PHASE} = 6V$                           | -      | 1.1  | _    | А    |

|                         | Low-Side Gate Driver Source             | $V_{\text{VCC}} = 12 \text{V}, V_{\text{LGATE-GND}} = 6 \text{V}$ | -      | 1.5  | _    |      |

|                         | Low-Side Gate Driver Sink Current       | $V_{\text{VCC}} = 12V$ , $V_{\text{LGATE-GND}} = 6V$              | =      | 1.8  | -    | А    |

| T□                      | Dead-Time (Note 4)                      |                                                                   | =      | 30   | _    | ns   |

| PROTEC <sup>*</sup>     | TIONS                                   |                                                                   |        |      |      |      |

| $V_{\text{FB\_UV}}$     | FB Under-Voltage Protection Trip        | Percentage of V <sub>REF</sub>                                    | 40     | 45   | 50   | %    |

|                         | Under-Voltage Debounce Interval         |                                                                   | -      | 2    | _    | s    |

|                         | Under-Voltage Protection Enable         | The same as soft -start interval                                  |        |      |      |      |

|                         | Delay                                   |                                                                   | 1      | 1.5  | 2    | ms   |

| $V_{\text{FB\_OV}}$     | FB Over-Voltage Protection Trip         | V <sub>FB</sub> rising                                            | 115    | 125  | 135  | %    |

|                         | FB Over-Voltage Protection              |                                                                   | -      | 5    | _    | %    |

|                         | Over-Voltage Debounce Interval          |                                                                   | -      | 2    | _    | S    |

| $V_{\text{OCP\_MAX}}$   | Built-in Maximum OCP Voltage            |                                                                   | 350    | =    | _    | mV   |

| OCSET                   | OCSET Current Source                    |                                                                   | 9      | 10   | 11   | uA   |

| SOFT-ST                 | ART                                     |                                                                   |        |      |      |      |

| $V_{\text{DISABLE}}$    | Shutdown Threshold of V <sub>COMP</sub> |                                                                   | -      | =    | 0.4  | V    |

| $T_{ss}$                | Internal Soft-Start Interval (Note 4)   |                                                                   | 1      | 1.5  | 2    | ms   |

| POWER                   | OK INDICATOR (POK) (ONLY FOR TDI        | FN3X3-10 PACKAGE)                                                 |        |      |      |      |

| <b>I</b> <sub>POK</sub> | POK Leakage Current                     | V <sub>POK</sub> =5V                                              | -      | 0.1  | 1    | uA   |

|                         |                                         | VFB is from low to target value                                   |        |      |      |      |

|                         |                                         | (POK Goes High)                                                   | 85     | 90   | 95   | %    |

| $V_{POK}$               | POK Threshold                           | VFB Falling, POK Goes Low                                         | 45     | 50   | 55   | %    |

|                         |                                         | VFB Rising, POK Goes Low                                          | 120    | 125  | 130  | %    |

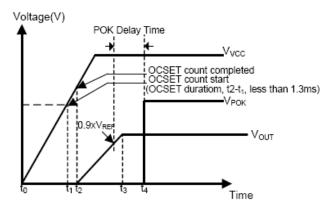

|                         | POK Delay Time                          |                                                                   | 1      | 3    | 5    | ms   |

Note 4: Guaranteed by design, not production tested.

### **Typical Operating Characteristics**

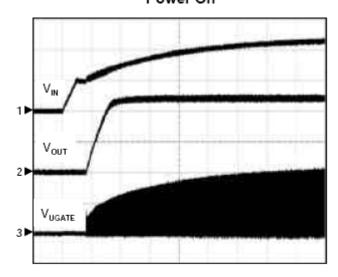

### Power On

CH1: V<sub>IN</sub>, 5V/Div CH2: V<sub>OUT</sub>, 500mV/Div CH3: V<sub>USATE</sub>, 10V/Div TIME: 1ms/Div

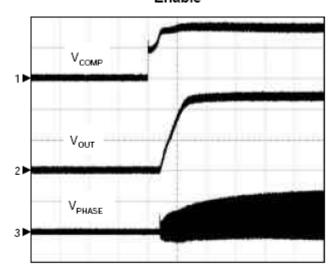

#### Enable

CH1: V<sub>COMP</sub>, 1V/Div CH2: V<sub>OUT</sub>, 500mV/Div CH3: V<sub>PHASE</sub>, 10V/Div TIME: 1ms/Div

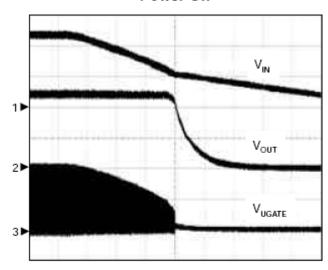

#### Power Off

CH1: V<sub>IN</sub>, 5V/Div CH2: V<sub>OUT</sub>, 500mV/Div CH3: VU<sub>GATE</sub>, 10V/Div TIME: 2ms/Div

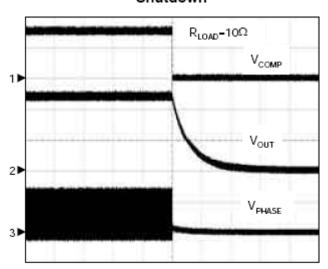

#### Shutdown

CH1: V<sub>COMP</sub>, 1V/Div CH2: V<sub>OUT</sub>, 500mV/Div CH3: V<sub>PHASE</sub>, 10V/Div TIME: 2ms/Div

### **Typical Operating Characteristics(Cont.)**

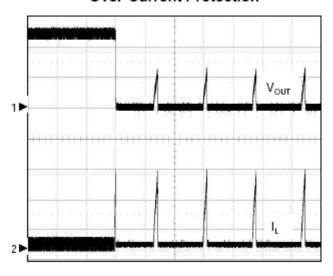

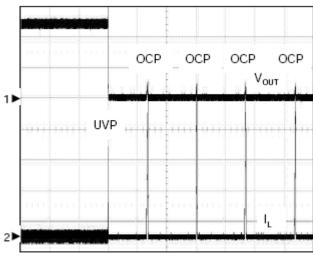

#### **Over-Current Protection**

CH1: V<sub>out</sub>, 500mV/Div CH2: I<sub>L</sub>,10A/Div TIME: 5ms/Div

### Under-Voltage Protection

CH1: V<sub>our</sub>, 500mV/Div CH2: I<sub>L</sub>,10A/Div TIME: 5ms/Div

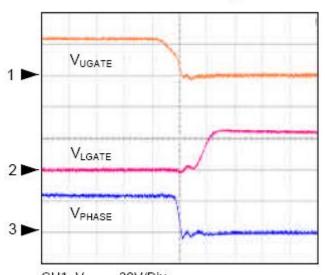

#### **UGATEFalling**

CH1: V<sub>UGATE</sub>, 20V/Div CH2: V<sub>LGATE</sub>, 10V/Div CH3: V<sub>PHASE</sub>, 10V/Div TIME: 50ns/Div

#### **UGATERising**

CH1: V<sub>USATE</sub>, 20V/Div CH2: V<sub>LGATE</sub>,10V/Div CH3: V<sub>PHASE</sub>,10V/Div TIME: 50ns/Div

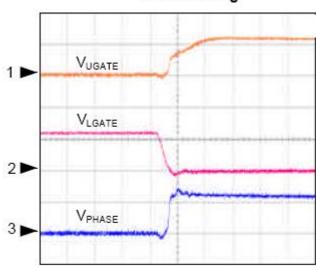

## **Typical Operating Characteristics(Cont.)**

CH1: V<sub>OUT</sub>, 500mV/Div CH2: V<sub>POK</sub>, 5V/Div TIME: 1ms/Div

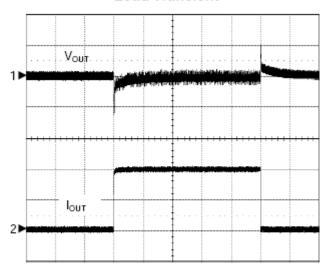

#### **Load Transient**

CH1: V<sub>оит</sub>, 50mV/Div, AC

CH2: I<sub>ουτ</sub>, 5A/Div TIME: 200μs/Div

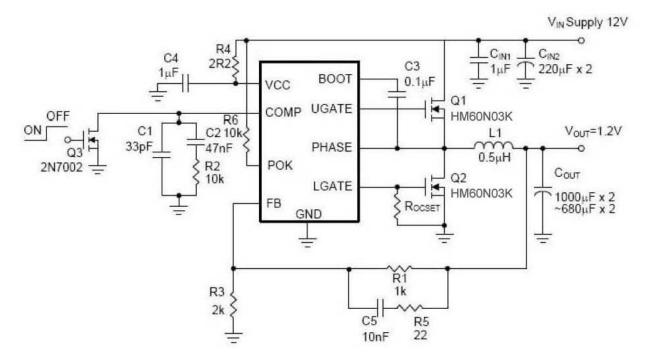

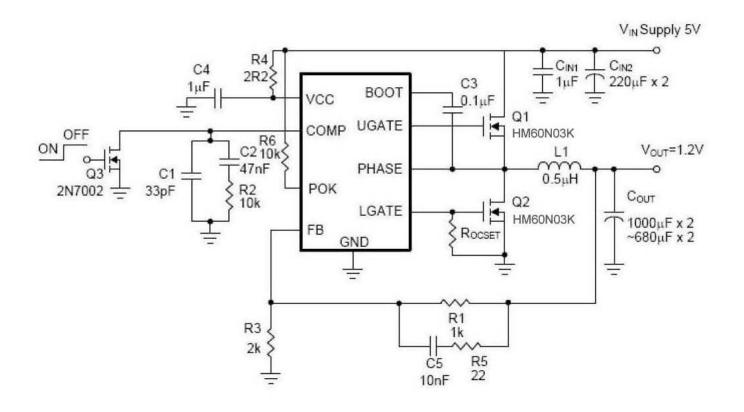

### **Typical Application Circuit**

#### =U 12V Application Circuit

#### =U 5V Application Circuit

### **Function Description**

#### Power-On-Reset (POR)

The Power-On-Reset (POR) function of HM1460 continually monitors the input supply voltage (VCC) and ensures that the IC has sufficient supply voltage and can work well. The POR function initiates a soft-start process while the VCC voltage just exceeds the POR threshold; the POR function also inhibits the operations of the IC while the VCC voltage falls below the POR threshold.

#### Soft-Start

The HM1460 builds in a soft-start function about 1.5ms (Typ.) interval, which controls the output voltage rising as well as limiting the current surge at the start-up. During soft-start, an internal ramp voltage connected to the one of the positive inputs of the error amplifier replaces the reference voltage (0.8V typical) until the ramp voltage reaches the reference voltage. The soft-start circuit interval is shown as figure 1. The UVP function enable delay is from t2 to t3.

#### **Over-Current Protection of the PWM Converter**

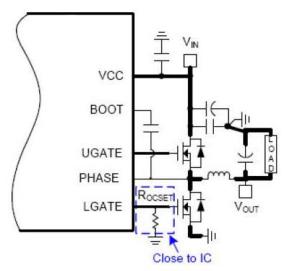

The over-current function protects the switching converter against over-current or short-circuit conditions. The controller senses the inductor current by detecting the drainto-source voltage which is the product of the inductor's current and the on-resistance of the low-side MOSFET during it's on-state. This method enhances the converter's efficiency and reduces cost by eliminating a current sensing resistor required.

A resistor (Rocset), connected from the LGATE/OCSET to GND, programs the over-current trip level. Before the IC initiates a soft-start process, an internal current source, locset ( $10\mu$ A typical), flowing through the Rocset develops a voltage (Vrocset) across the Rocset. The device holds Vrocset and stops the current source locset during normal operation. When the voltage across the low-side MOSFET exceeds the Vrocset, the HM1460 turns off the highside and low-side MOSFET, and the device will enters hiccup mode until the over-current phenomenon is released.

The HM1460 has an internal OCP voltage, VocP\_MAX, and the value is 0.35V (minimum). When the Rocset x locset exceed 0.35V or the Rocset is floating or not connected, the VROCSET will be the default value 0.35V. The over current threshold would be 0.35V across low-side MOSFET. The threshold of the valley inductor current-limit is therefore given by:

$$I_{LIMIT} = \frac{I_{OCSET} \times R_{OCSET}}{R_{DS(ON)}(low - side)}$$

For the over-current is never occurred in the normal operating load range, the variation of all parameters in the above equation should be considered:

- The  $R_{DS(ON)}$  of low-side MOSFET is varied by temperature and gate to source voltage. Users should determine the maximum  $R_{DS(ON)}$  by using the manufacturer's datasheet.

- The minimum  $I_{\text{OCSET}}(9\mu\text{A})$  and minimum  $R_{\text{OCSET}}should$  be used in the above equation.

- Note that the ILIMIT is the current flow through the lowside MOSFET; ILIMIT must be greater than valley inductor current which is output current minus the half of inductor ripple current.

$$I_{LIMIT} > I_{OUT(MAX)} - \frac{\Delta I}{2}$$

Where  $\Delta I$  = output inductor ripple current

The overshoot and transient peak current also should be considered.

### **Function Description(Cont.)**

#### **Under-Voltage Protection**

The under-voltage function monitors the voltage on FB ( $V_{FB}$ ) by Under-Voltage (UV) comparator to protect the PWM converter against short-circuit conditions. When the  $V_{FB}$  falls below the falling UVP threshold (50%  $V_{REF}$ ), a fault signal is internally generated and the device turns off highside and low-side MOSFETs. The device will enters hiccup mode until the under-voltage phenomenon is released.

#### Over-Voltage Protection (OVP) of the PWM Converter

The over-voltage protection monitors the FB voltage to prevent the output from over-voltage condition. When the output voltage rises above 125% of the nominal output voltage, the HM1460 turns off the high-side MOSFET and turns on the low-side MOSFET until the output voltage falls below the falling OVP threshold.

#### **Shutdown and Enable**

The HM1460 can be shut down or enabled by pulling low the voltage on COMP. The COMP is a dual-function pin. During normal operation, this pin represents the output of the error amplifier. It is used to compensate the regulation control loop in combination with the FB pin. Pulling the COMP low (VDISABLE = 0.4V maximum) places the controller into shutdown mode which UGATE and LGATE are pulled to PHASE and GND respectively. When the pull-down device is released, the COMP voltage will start to rise. When the COMP voltage rises above the VDISABLE threshold, the HM1460 will begin a new initialization and soft-start process.

#### **Adaptive Shoot-Through Protection of the PWM Converter**

The gate drivers incorporate an adaptive shoot-through protection to prevent high-side and low-side MOSFETs from conducting simultaneously and shorting the input supply. This is accomplished by ensuring the falling gate has turned off one MOSFET before the other is allowed to rise.

During turn-off the low-side MOSFET, the LGATE voltage is monitored until it is below 1.5V threshold, at which time the UGATE is released to rise after a constant delay. During turn-off of the high-side MOSFET, the UGATE-to-PHASE voltage is also monitored until it is below 1.5V threshold, at which time the LGATE eleased to rise after a constant delay.

#### **Power OK Indicator**

The HM1460 features an open-drain POK output pin to indicate one of the IC's working statuses including soft-start, under-voltage fault, over-current fault. In normal operation, when the output voltage rises 90% of its target value, the POK goes high. When the output voltage outruns 50% or 125% of the target voltage, POK signal will be pulled low immediately.

### **Application Information**

#### **Output Voltage Selection**

The output voltage can be programmed with a resistive divider. Use 1% or better resistors for the resistive divider is recommended. The FB pin is the inverter input of the error amplifier, and the reference voltage is 0.8V. The output voltage is determined by:

$$V_{OUT} = 0.8 \times \left(1 + \frac{R_1}{R_2}\right)$$

Where R1 is the resistor connected from  $V_{\text{OUT}}$  to FB and R2 is the resistor connected from FB to the GND.

#### **Output Capacitor Selection**

The selection of Cour is determined by the required effective series resistance (ESR) and voltage rating rather than the actual capacitance requirement. Therefore, selecting high performance low ESR capacitors is intended for switching regulator applications. In some applications.multiple capacitors have to be paralleled to achieve the desired ESR value. If tantalum capacitors are used, make sure they are surge tested by the manufactures. If in doubt,consult the capacitors manufacturer.

#### **Input Capacitor Selection**

The input capacitor is chosen based on the voltage rating and the RMS current rating. For reliable operation, select the capacitor voltage rating to be at least 1.3 times higher than the maximum input voltage. The maximum RMS current rating requirement is approximately  $l_{\text{OUT}}/2$  where  $l_{\text{OUT}}$  is the load current. During power up, the input capacitors have to handle large amount of surge current. If tantalum capacitors are used, make sure they are surge tested by the manufactures. If in doubt, consult the capacitors manufacturer. For high frequency decoupling, a ceramic capacitor between  $0.1\mu\text{F}$  to  $1\mu\text{F}$  can connect between VCC and ground pin.

#### **Inductor Selection**

The inductance of the inductor is determined by the output voltage requirement. The larger the inductance, the lower the inductor's current ripple. This will translate into lower output ripple voltage. The ripple current and ripple voltage can be approximated by:

$$I_{RIPPLE} = \frac{V_{IN} - V_{OUT}}{F_{SW} \times L} \times \frac{V_{OUT}}{V_{IN}}$$

where Fs is the switching frequency of the regulator.

$$\Delta V_{OUT} = I_{RIPPLE} \times ESR$$

A tradeoff exists between the inductor's ripple current and the regulator load transient response time. A smaller inductor will give the regulator a faster load transient response at the expense of higher ripple current and vice versa. The maximum ripple current occurs at the maximum input voltage. A good starting point is to choose the ripple current to be approximately 30% of the maximum output current.

Once the inductance value has been chosen, selecting an inductor is capable of carrying the required peak current without going into saturation. In some types of inductors, especially core that is make of ferrite, the ripple current will increase abruptly when it saturates. This will result in a larger output ripple voltage.

#### Compensation

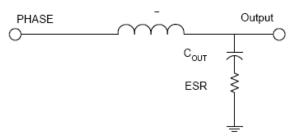

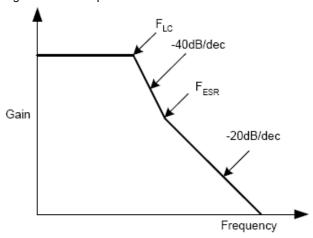

The output LC filter of a step down converter introduces a double pole, which contributes with -40dB/decade gain slope and 180 degrees phase shift in the control loop. A compensation network between COMP pin and ground should be added. The simplest loop compensation network is shown in Figure 5.The output LC filter consists of the output inductor and output capacitors. The transfer function of the LC filter is given by:

$$GAIN_{LC} = \frac{1 + s \times ESR \times C_{OUT}}{s^2 \times L \times C_{OUT} + s \times ESR \times C_{OUT} + 1}$$

The poles and zero of this transfer function are:

$$F_{LC} = \frac{1}{2 \times \pi \times \sqrt{L \times C_{OUT}}}$$

$$F_{ESR} = \frac{1}{2 \times \pi \times ESR \times C_{OUT}}$$

The FLC is the double poles of the LC filter, and FESR is the zero introduced by the ESR of the output capacitor.

### **Application Information(Cont.)**

Figure 2. The Output LC Filter

Figure 3. The LC Filter Gain & Frequency

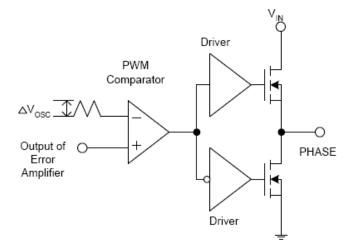

The PWM modulator is shown in Figure 4. The input is the output of the error amplifier and the output is the PHASE node. The transfer function of the PWM modulator is given by:

$$GAIN_{PWM} = \frac{V_{IN}}{\Delta V_{OSC}}$$

Figure 4. The PWM Modulator

The compensation circuit is shown in Figure 5. R2 and C2 introduce a zero and C1 introduces a pole to reduce the switching noise. The transfer function of error amplifier is given by:

$$\begin{split} \text{GAIN}_{\text{AMP}} = gm \times Z_{\text{O}} = gm \times & \left[ \left( R2 + \frac{1}{sC2} \right) \! / \! / \frac{1}{sC1} \right] \\ = gm \times & \frac{\left( s + \frac{1}{R2 \times C2} \right)}{s \times \left( s + \frac{C2 + C1}{R2 \times C1 \times C2} \right) \times C1} \end{split}$$

The pole and zero of the compensation network are:

$$F_{P} = \frac{1}{2 \times \pi \times R2 \times \frac{C1 \times C2}{C1 + C2}}$$

$$F_{Z} = \frac{1}{2 \times \pi \times R2 \times C2}$$

$$V_{OUT}$$

$$R1$$

$$FB$$

$$V_{REF}$$

$$R2$$

$$C2$$

$$C$$

$$C$$

Figure 5. Compensation Network

The closed loop gain of the converter can be written as:

$$\mathsf{GAIN}_{\mathsf{LC}} \times \mathsf{GAIN}_{\mathsf{PWM}} \times \frac{R3}{R1 + R3} \times \mathsf{GAIN}_{\mathsf{AMP}}$$

Figure 6 shows the converter gain and the following guidelines will help to design the compensation network.

1.Select the desired zero crossover frequency Fo:

$$(1/5 \sim 1/10) x F_{SW} > F_{O} > F_{Z}$$

Use the following equation to calculate R2:

$$R2 = \frac{\Delta V_{\text{OSC}}}{V_{\text{IN}}} \times \frac{F_{\text{ESR}}}{F_{\text{LC}}2} \times \frac{R1 + R3}{R3} \times \frac{F_0}{gm}$$

Where:gm =  $667\mu A/V$

### **Application Information(Cont.)**

2. Place the zero  $F_{\text{\it z}}$  before the LC filter double poles  $F_{\text{\tiny LC}}$ :

$Fz = 0.75 \times F_{LC}$

Calculate the C2 by the equation:

$$C2 = \frac{1}{2 \times \pi \times R2 \times 0.75 \times F_{LC}}$$

3. Set the pole at the half the switching frequency:

$F_P = 0.5xF_{SW}$

Calculate the C1 by the equation:

$$C1 = \frac{C2}{\pi \times R2 \times C2 \times F_{sw} - 1}$$

$$F_z = 0.75F_{LC}$$

$$20 \cdot log(gm \cdot R2)$$

$$Gain$$

$$F_{LC}$$

$$20 \cdot log \frac{V_{IN}}{\Delta V_{OSC}}$$

$$F_{ESR}$$

$$PWM & Converter Gain$$

Figure 6. Converter Gain & Frequency

#### **MOSFET Selection**

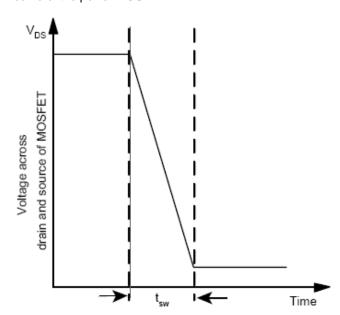

The selection of the N-channel power MOSFETs is determined by the R<sub>DS(ON)</sub>, reverse transfer capacitance (C<sub>RSS</sub>), and maximum output current requirement. The losses in the MOSFETs have two components: conduction loss and transition loss. For the upper and lower MOSFET, the losses are approximately given by the following equations:

Filter Gain

Frequency

$$\begin{split} & \text{Pupper} = \text{Iout2} \, \big( 1 + \, \text{TC} \big) \big( \text{Rds(on)} \big) D \, + \, \big( 0.5 \big) \big( \text{Iout} \big) \big( \text{Vin} \big) \big( t_{sw} \big) F_{sw} \\ & \text{Plower} = \text{Iout2} \, \big( 1 + \, \text{TC} \big) \big( \text{Rds(on)} \big) \big( 1 - D \big) \end{split}$$

where lout is the load current

TC is the temperature dependency of RDS(ON)

Fsw is the switching frequency

tsw is the switching interval

D is the duty cycle

Note that both MOSFETs have conduction losses while the upper MOSFET includes an additional transition loss. The switching internal, tsw, is the function of the reverse transfer capacitance Crss. Figure 7 illustrates the switching waveform internal of the MOSFET.

The (1+TC) term factors in the temperature dependency of the  $R_{DS(ON)}$  and can be extracted from the " $R_{DS(ON)}$  vs Temperature" curve of the power MOSFET.

Figure 7. Switching Waveform Across MOSFET

#### **Layout Consideration**

In any high switching frequency converter, a correct layout is important to ensure proper operation of the regulator. With power devices switching at 300kHz, the resulting current transient will cause voltage spike across the interconnecting impedance and parasitic circuit elements. As an example, consider the turn-off transition of the PWM MOSFET. Before turn-off, the MOSFET is carrying the full load current. During turn-off, current stops flowing in the MOSFET and is free-wheeling by the lower MOSFET and parasitic diode. Any parasitic inductance of the circuit generates a

### **Application Information(Cont)**

large voltage spike during the switching interval. In general, using short and wide printed circuit traces should minimize interconnecting imped ances and the magnitude of voltage spike. And signal and power grounds are to be kept separate till combined using ground plane construction or single point grounding. Figure 8. illustrates the layout, with bold lines indicating high current paths; these traces must be short and wide. Components along the bold lines should be placed lose together. Below is a checklist for your layout:

- Keep the switching nodes (UGATE, LGATE, and PHASE) away from sensitive small signal nodes since these nodes are fast moving signals. Therefore, keep traces to these nodes as short as possible.

- The traces from the gate drivers to the MOSFETs (UG and LG) should be short and wide.

- Place the source of the high-side MOSFET and the drain of the low-side MOSFET as close as possible. Minimizing the impedance with wide layout plane between the two pads reduces the voltage bounce of the node.

Decoupling capacitor, compensation component, the resistor dividers, and boot capacitors should be close their pins. (For example, place the decoupling ceramic capacitor near the drain of the high-side MOSFET as close as possible. The bulk capacitors are also placed near the drain).

- The input capacitor should be near the drain of the upper MOSFET; the output capacitor should be near the loads. The input capacitor GND should be close to the output capacitor GND and the lower MOSFET GND.

- The drain of the MOSFETs ( $V_{\text{IN}}$  and PHASE nodes) should be a large plane for heat sinking.

- The  $\mathsf{Rocset}$  resistance should be placed near the IC as close as possible.

Figure 8. Layout Guidelines

## **Package Information**

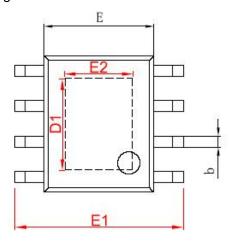

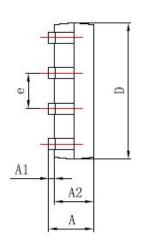

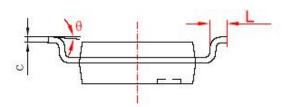

### SOP8-PP Package Outline Dimensions

|    | Dimensions I | Dimensions In Millimeters |        | In Inches |

|----|--------------|---------------------------|--------|-----------|

|    | Min          | Max                       | Min    | Max       |

| Α  | 1. 350       | 1. 750                    | 0.053  | 0.069     |

| A1 | 0.050        | 0. 150                    | 0.004  | 0.010     |

| A2 | 1. 350       | 1. 550                    | 0.053  | 0.061     |

| b  | 0. 330       | 0. 510                    | 0.013  | 0.020     |

| С  | 0. 170       | 0. 250                    | 0.006  | 0.010     |

| D  | 4. 700       | 5. 100                    | 0. 185 | 0. 200    |

| D1 | 3. 202       | 3. 402                    | 0. 126 | 0. 134    |

| E  | 3. 800       | 4. 000                    | 0. 150 | 0. 157    |

| E1 | 5. 800       | 6. 200                    | 0. 228 | 0. 244    |

| E2 | 2. 313       | 2. 513                    | 0.091  | 0.099     |

| е  | 1. 27        | 0 (BSC)                   | 0.050  | (BSC)     |

| L  | 0. 400       | 1. 270                    | 0.016  | 0.050     |

| θ  | 0°           | 8°                        | 0°     | 8°        |

## **Package Information**

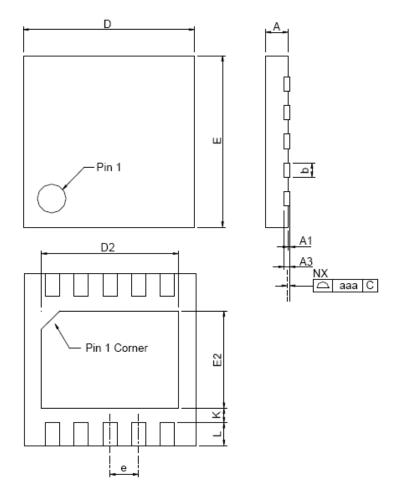

TDFN3x3-10

| ş   |        | TDFN          | 3x3-10 |       |  |

|-----|--------|---------------|--------|-------|--|

| B   | MILLIM | ETER <b>S</b> | INCHES |       |  |

| P   | MIN.   | MAX.          | MIN.   | MAX.  |  |

| Α   | 0.70   | 0.80          | 0.028  | 0.031 |  |

| A1  | 0.00   | 0.05          | 0.000  | 0.002 |  |

| А3  | 0.20   | REF           | 0.008  | REF   |  |

| b   | 0.18   | 0.30          | 0.007  | 0.012 |  |

| D   | 2.90   | 3.10          | 0.114  | 0.122 |  |

| D2  | 2.20   | 2.70          | 0.087  | 0.106 |  |

| Е   | 2.90   | 3.10          | 0.114  | 0.122 |  |

| E2  | 1.40   | 1.75          | 0.055  | 0.069 |  |

| е   | 0.50   | BSC           | 0.016  | BSC   |  |

| L   | 0.30   | 0.50          | 0.012  | 0.020 |  |

| K   | 0.20   |               | 0.008  |       |  |

| aaa | 0.0    | 08            | 0.00   | 03    |  |