# HM64YLB36514 Series

16M Synchronous Late Write Fast Static RAM (512-kword × 36-bit, Register-Latch Mode)

REJ03C0039-0001Z Preliminary Rev.0.10 May.15.2003

#### **Description**

The HM64YLB36514 is a synchronous fast static RAM organized as 512-kword  $\times$  36-bit. It has realized high speed access time by employing the most advanced CMOS process and high speed circuit designing technology. It is most appropriate for the application which requires high speed, high density memory and wide bit width configuration, such as cache and buffer memory in system. It is packaged in standard 119-bump BGA.

Note: All power supply and ground pins must be connected for proper operation of the device.

#### **Features**

- 2.5 V  $\pm$  5% operation and 1.5 V ( $V_{DDO}$ )

- 16M bit density

- Internal self-timed late write

- Byte write control (4 byte write selects, one for each 9-bit)

- Optional ×18 configuration

- HSTL compatible I/O

- Programmable impedance output drivers

- Differential pseudo-HSTL clock inputs

- Asynchronous  $\overline{G}$  output control

- Asynchronous sleep mode

- FC-BGA 119pin package with SRAM JEDEC standard pinout

- Limited set of boundary scan JTAG IEEE 1149.1 compatible

- Protocol: Single differential clock register-latch mode

Preliminary: The specifications of this device are subject to change without notice. Please contact your nearest Renesas Technology's Sales Dept. regarding specifications.

## **Ordering Information**

| Type No.          | Organization | Access time | Cycle time | Package                                         |

|-------------------|--------------|-------------|------------|-------------------------------------------------|

| HM64YLB36514BP-6H | 512k × 36    | 5.5 ns      | 6.5 ns     | 119-bump 1.27 mm<br>14 mm × 22 mm BGA (BP-119E) |

## **Pin Arrangement**

|   | 1         | 2        | 3               | 4        | 5               | 6        | 7         |

|---|-----------|----------|-----------------|----------|-----------------|----------|-----------|

| Α | $V_{DDQ}$ | SA14     | SA13            | NC       | SA6             | SA7      | $V_{DDQ}$ |

| В | NC        | SA15     | SA12            | NC       | SA5             | SA9      | NC        |

| С | NC        | SA16     | SA11            | $V_{DD}$ | SA4             | SA8      | NC        |

| D | DQc7      | DQc8     | V <sub>ss</sub> | ZQ       | V <sub>ss</sub> | DQb8     | DQb7      |

| Е | DQc5      | DQc6     | V <sub>ss</sub> | SS       | V <sub>ss</sub> | DQb6     | DQb5      |

| F | $V_{DDQ}$ | DQc4     | V <sub>ss</sub> | G        | V <sub>ss</sub> | DQb4     | $V_{DDQ}$ |

| G | DQc3      | DQc2     | SWEc            | NC       | SWEb            | DQb2     | DQb3      |

| Н | DQc1      | DQc0     | V <sub>ss</sub> | NC       | V <sub>ss</sub> | DQb0     | DQb1      |

| J | $V_{DDQ}$ | $V_{DD}$ | $V_{REF}$       | $V_{DD}$ | $V_{REF}$       | $V_{DD}$ | $V_{DDQ}$ |

| K | DQd1      | DQd0     | $V_{ss}$        | K        | V <sub>ss</sub> | DQa0     | DQa1      |

| L | DQd3      | DQd2     | SWEd            | K        | SWEa            | DQa2     | DQa3      |

| М | $V_{DDQ}$ | DQd4     | V <sub>ss</sub> | SWE      | V <sub>ss</sub> | DQa4     | $V_{DDQ}$ |

| N | DQd5      | DQd6     | V <sub>ss</sub> | SA17     | V <sub>ss</sub> | DQa6     | DQa5      |

| Р | DQd7      | DQd8     | V <sub>ss</sub> | SA0      | V <sub>ss</sub> | DQa8     | DQa7      |

| R | NC        | SA10     | M1              | $V_{DD}$ | M2              | SA1      | NC        |

| Т | NC        | NC       | SA18            | SA3      | SA2             | NC       | ZZ        |

| U | $V_{DDQ}$ | TMS      | TDI             | TCK      | TDO             | NC       | $V_{DDQ}$ |

(Top view)

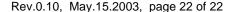

## **Block Diagram**

#### **Pin Descriptions**

| Name            | I/O type | Descriptions                                      | Notes                  |

|-----------------|----------|---------------------------------------------------|------------------------|

| $V_{DD}$        | Supply   | Core power supply                                 |                        |

| V <sub>ss</sub> | Supply   | Ground                                            |                        |

| $V_{DDQ}$       | Supply   | Output power supply                               |                        |

| $V_{REF}$       | Supply   | Input reference, provides input reference voltage |                        |

| K               | Input    | Clock input, active high                          |                        |

| K               | Input    | Clock input, active low                           |                        |

| SS              | Input    | Synchronous chip select                           |                        |

| SWE             | Input    | Synchronous write enable                          |                        |

| SAn             | Input    | Synchronous address input                         | n: 0 to 18             |

| SWEx            | Input    | Synchronous byte write enables                    | x: a to d              |

| G               | Input    | Asynchronous output enable                        |                        |

| ZZ              | Input    | Power down mode select                            |                        |

| ZQ              | Input    | Output impedance control                          | 1                      |

| DQxn            | I/O      | Synchronous data input/output                     | x: a to d<br>n: 0 to 8 |

| M1, M2          | Input    | Output protocol mode select                       |                        |

| TMS             | Input    | Boundary scan test mode select                    |                        |

| TCK             | Input    | Boundary scan test clock                          |                        |

| TDI             | Input    | Boundary scan test data input                     |                        |

| TDO             | Output   | Boundary scan test data output                    |                        |

| NC              | _        | No connection                                     |                        |

| M1              | M2       | Protocol                                | Notes |

|-----------------|----------|-----------------------------------------|-------|

| V <sub>DD</sub> | $V_{ss}$ | Synchronous register to latch operation | 2     |

Notes: 1. ZQ is to be connected to  $V_{ss}$  via a resistance RQ where 175  $\Omega \le RQ \le 300 \Omega$ . If ZQ =  $V_{DDQ}$  or open, output buffer impedance will be maximum.

<sup>2.</sup> There is 1 protocol with mode control input pins (M1, M2). These mode pins are to be tied either

$V_{\text{DD}}$  or  $V_{\text{SS}}$  respectively. These mode pins are set at power-up and will not change the states during the SRAM operates. This SRAM is tested only in the synchronous register to latch operation.

#### **Truth Table**

| ZZ | SS | G | SWE | SWEa | SWEb | SWEc | SWEd | K   | $\overline{K}$ | Operation                   | DQ (n)                               | DQ (n+1)                            |

|----|----|---|-----|------|------|------|------|-----|----------------|-----------------------------|--------------------------------------|-------------------------------------|

| Н  | ×  | × | ×   | ×    | ×    | ×    | ×    | ×   | ×              | Sleep<br>mode               | High-Z                               | High-Z                              |

| L  | Н  | × | ×   | ×    | ×    | ×    | ×    | L-H | H-L            | Dead<br>(not<br>selected)   | High-Z                               | ×                                   |

| L  | ×  | Н | Н   | ×    | ×    | ×    | ×    | ×   | ×              | Dead<br>(dummy<br>read)     | High-Z                               | High-Z                              |

| L  | L  | L | Н   | ×    | ×    | ×    | ×    | L-H | H-L            | Read                        | D <sub>OUT</sub> (a, b, c, d) 0 to 8 | ×                                   |

| L  | L  | × | L   | L    | L    | L    | L    | L-H | H-L            | Write<br>a, b, c, d<br>byte | High-Z                               | D <sub>IN</sub> (a, b, c, d) 0 to 8 |

| L  | L  | × | L   | Н    | L    | L    | L    | L-H | H-L            | Write<br>b, c, d<br>byte    | High-Z                               | D <sub>IN</sub> (b, c, d) 0 to 8    |

| L  | L  | × | L   | L    | Н    | L    | L    | L-H | H-L            | Write<br>a, c, d<br>byte    | High-Z                               | D <sub>IN</sub> (a, c, d) 0 to 8    |

| L  | L  | × | L   | L    | L    | Н    | L    | L-H | H-L            | Write<br>a, b, d<br>byte    | High-Z                               | D <sub>IN</sub> (a, b, d) 0 to 8    |

| L  | L  | × | L   | L    | L    | L    | Н    | L-H | H-L            | Write<br>a, b, c<br>byte    | High-Z                               | D <sub>IN</sub> (a, b, c) 0 to 8    |

| L  | L  | × | L   | Н    | Н    | L    | L    | L-H | H-L            | Write<br>c, d byte          | High-Z                               | D <sub>IN</sub> (c, d)<br>0 to 8    |

| L  | L  | × | L   | L    | Н    | Н    | L    | L-H | H-L            | Write<br>a, d byte          | High-Z                               | D <sub>IN</sub> (a, d)<br>0 to 8    |

| L  | L  | × | L   | L    | L    | Н    | Н    | L-H | H-L            | Write<br>a, b byte          | High-Z                               | D <sub>IN</sub> (a, b)<br>0 to 8    |

| L  | L  | × | L   | Н    | L    | L    | Н    | L-H | H-L            | Write<br>b, c byte          | High-Z                               | D <sub>IN</sub> (b, c)<br>0 to 8    |

| L  | L  | × | L   | Н    | Н    | Н    | L    | L-H | H-L            | Write<br>d byte             | High-Z                               | D <sub>IN</sub> (d)<br>0 to 8       |

| L  | L  | × | L   | Н    | Н    | L    | Н    | L-H | H-L            | Write<br>c byte             | High-Z                               | D <sub>IN</sub> (c)<br>0 to 8       |

| L  | L  | × | L   | Н    | L    | Н    | Н    | L-H | H-L            | Write<br>b byte             | High-Z                               | D <sub>IN</sub> (b)<br>0 to 8       |

| L  | L  | × | L   | L    | Н    | Н    | Н    | L-H | H-L            | Write<br>a byte             | High-Z                               | D <sub>IN</sub> (a)<br>0 to 8       |

Notes: 1. H:  $V_{IH}$ , L:  $V_{IL}$ ,  $\times$ :  $V_{IH}$  or  $V_{IL}$

2. SWE, SS, SWEa to SWEd, and SA are sampled at the rising edge of K clock.

#### **Programmable Impedance Output Drivers**

Output buffer impedance can be programmed by terminating the ZQ pin to  $V_{ss}$  through a precision resistor (RQ). The value of RQ is five times the output impedance desired. The allowable value of RQ to guarantee impedance matching with a tolerance of 15% is 250  $\Omega$ . If the status of ZQ pin is open, output impedance is maximum value. Maximum impedance also occurs with ZQ connected to  $V_{DDQ}$ . The impedance update of the output driver occurs when the SRAM is in high-Z. Write and deselect operations will synchronously switch the SRAM into and out of high-Z, therefore will trigger an update. The user may choose to invoke asynchronous  $\overline{G}$  updates by providing a  $\overline{G}$  setup and hold about the K clock, to guarantee the proper update. At power up, the output buffer is in high-Z. It will take 4,096 cycles for the impedance to be completely updated.

#### **Absolute Maximum Ratings**

| Parameter                                    | Symbol                       | Rating                          | Unit | Notes |

|----------------------------------------------|------------------------------|---------------------------------|------|-------|

| Input voltage on any pin                     | V <sub>IN</sub>              | $-0.5 \text{ to V}_{DDQ} + 0.5$ | V    | 1, 4  |

| Core supply voltage                          | V <sub>DD</sub>              | -0.5 to +3.13                   | V    | 1     |

| Output supply voltage                        | $V_{\scriptscriptstyle DDQ}$ | -0.5 to +2.1                    | V    | 1, 4  |

| Operating temperature                        | T <sub>OPR</sub>             | 0 to +85                        | °C   |       |

| Storage temperature                          | $T_{\mathtt{STG}}$           | -55 to +125                     | °C   |       |

| Output short-circuit current                 | I <sub>OUT</sub>             | 25                              | mA   |       |

| Latch up current                             | l <sub>u</sub>               | 200                             | mA   |       |

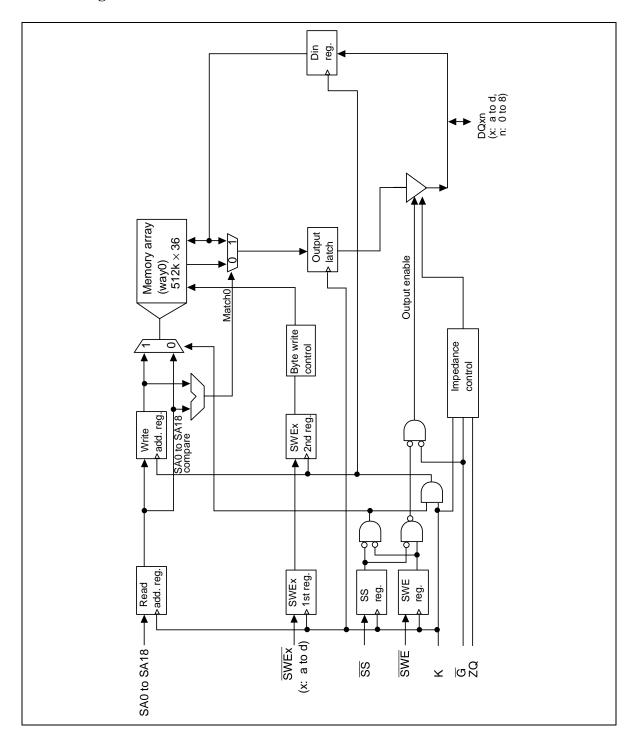

| Package junction to top thermal resistance   | θJ-top                       | 6.5                             | °C/W | 5     |

| Package junction to board thermal resistance | θJ-board                     | 12                              | °C/W | 5     |

- Notes: 1. All voltage is referenced to V<sub>ss</sub>.

- 2. Permanent device damage may occur if absolute maximum ratings are exceeded. Functional operation should be restricted the operation conditions. Exposure to higher voltages than recommended voltages for extended periods of time could affect device reliability.

- 3. These CMOS memory circuits have been designed to meet the DC and AC specifications shown in the tables after thermal equilibrium has been established.

- 4. The following supply voltage application sequence is recommended:  $V_{SS}$ ,  $V_{DD}$ ,  $V_{DDQ}$ ,  $V_{REF}$  then  $V_{IN}$ . Remember, according to the absolute maximum ratings table,  $V_{DDQ}$  is not to exceed 2.1 V, whatever the instantaneous value of  $V_{DDQ}$ .

- 5. See figure below.

#### HM64YLB36514 Series

Note: The following DC and AC specifications shown in the tables, this device is tested under the minimum transverse air flow exceeding 500 linear feet per minute.

## **Recommended DC Operating Conditions** (Ta = 0 to +85°C)

| Parameter                    | Symbol                       | Min                     | Тур  | Max                     | Unit | Notes |

|------------------------------|------------------------------|-------------------------|------|-------------------------|------|-------|

| Power supply voltage: core   | V <sub>DD</sub>              | 2.38                    | 2.50 | 2.63                    | V    |       |

| Power supply voltage: I/O    | $V_{\scriptscriptstyle DDQ}$ | 1.40                    | 1.50 | 1.60                    | V    |       |

| Input reference voltage: I/O | $V_{REF}$                    | 0.70                    | 0.75 | 0.80                    | V    | 1     |

| Input high voltage           | V <sub>IH</sub>              | V <sub>REF</sub> + 0.15 | _    | $V_{DDQ} + 0.50$        | V    | 4     |

| Input low voltage            | V <sub>IL</sub>              | -0.50                   |      | V <sub>REF</sub> - 0.15 | V    | 4     |

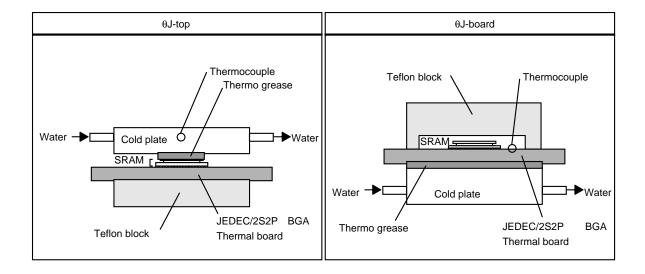

| Clock differential voltage   | $V_{DIF}$                    | 0.10                    | _    | $V_{DDQ} + 0.30$        | V    | 2, 3  |

| Clock common mode voltage    | V <sub>CM</sub>              | 0.90                    | _    | 1.30                    | V    | 3     |

Notes: 1. Peak to peak AC component superimposed on  $V_{\text{REF}}$  may not exceed 5% of  $V_{\text{REF}}$ .

- 2. Minimum differential input voltage required for differential input clock operation.

- 3. See figure below.

- 4.  $V_{REF} = 0.75 \text{ V (typ)}$ .

#### Differential Voltage / Common Mode Voltage

### **DC Characteristics** (Ta = 0 to +85°C, $V_{DD}$ = 2.5 V ± 5%)

| Parameter                                                   | Symbol            | Min | Max | Unit | Notes |

|-------------------------------------------------------------|-------------------|-----|-----|------|-------|

| Input leakage current                                       | l <sub>u</sub>    | _   | 2   | μΑ   | 1     |

| Output leakage current                                      | I <sub>LO</sub>   | _   | 5   | μΑ   | 2     |

| Standby current                                             | l <sub>SBZZ</sub> | _   | 150 | mA   | 3     |

| V <sub>DD</sub> operating current, excluding output drivers | I <sub>DD</sub>   | _   | 350 | mA   | 4     |

| Quiescent active power supply current                       | l <sub>DD2</sub>  | _   | 200 | mA   | 5     |

| Maximum power dissipation, including output drivers         | Р                 | _   | 2.3 | W    | 6     |

| Parameter                 | Symbol          | Min                             | Тур | Max                             | Unit | Notes  |

|---------------------------|-----------------|---------------------------------|-----|---------------------------------|------|--------|

| Output low voltage        | V <sub>oL</sub> | V <sub>ss</sub>                 | _   | V <sub>ss</sub> + 0.4           | V    | 7      |

| Output high voltage       | V <sub>OH</sub> | V <sub>DDQ</sub> - 0.4          | _   | V <sub>DDQ</sub>                | V    | 8      |

| ZQ pin connect resistance | RQ              | _                               | 250 | _                               | Ω    |        |

| Output "Low" current      | I <sub>OL</sub> | $(V_{DDQ}/2)/\{(RQ/5) - 15\%\}$ |     | $(V_{DDQ}/2)/\{(RQ/5) + 15\%\}$ | mΑ   | 9, 11  |

| Output "High" current     | I <sub>OH</sub> | $(V_{DDQ}/2)/\{(RQ/5) + 15\%\}$ |     | $(V_{DDQ}/2)/\{(RQ/5) - 15\%\}$ | mΑ   | 10, 11 |

Notes: 1.  $0 \le V_{IN} \le V_{DDQ}$  for all input pins (except  $V_{REF}$ , ZQ, M1, M2 pin)

- 2.  $0 \le V_{OUT} \le V_{DDQ}$ , DQ in high-Z

- 3. All inputs (except clock) are held at either  $V_{IH}$  or  $V_{IL}$ , ZZ is held at  $V_{IH}$ ,  $I_{OUT} = 0$  mA. Specification is guaranteed at +75°C junction temperature.

- 4.  $I_{out} = 0$  mA, read 50% / write 50%,  $V_{do} = V_{do}$  max, frequency = min. cycle

- 5.  $I_{OUT} = 0$  mA, read 50% / write 50%,  $V_{DD} = V_{DD}$  max, frequency = 3 MHz

- 6. Output drives a 12 pF load and switches every cycle. This parameter should be used by the SRAM designer to determine electrical and package requirements for the SRAM device.

- 7. RQ = 250  $\Omega$ ,  $I_{OI}$  = 6.8 mA

- 8. RQ = 250  $\Omega$ ,  $I_{OH}$  = -6.8 mA

- 9. Measured at  $V_{OL} = 1/2 V_{DDQ}$

- 10. Measured at  $V_{OH} = 1/2 V_{DDQ}$

- 11. The total external capacitance of ZQ pin must be less than 7.5 pF.

## **AC Characteristics** (Ta = 0 to +85°C, $V_{DD} = 2.5 \text{ V} \pm 5\%$ )

Single Differential Clock Register-Latch Mode

|                                        |                                   | HM64YL | B36514BP |      |         |  |

|----------------------------------------|-----------------------------------|--------|----------|------|---------|--|

|                                        |                                   | -6H    |          |      | Notes   |  |

| Parameter                              | Symbol                            | Min    | Max      | Unit |         |  |

| CK clock cycle time                    | t <sub>khkh</sub>                 | 6.5    | _        | ns   |         |  |

| CK clock high width                    | t <sub>kHKL</sub>                 | 1.2    | _        | ns   |         |  |

| CK clock low width                     | t <sub>KLKH</sub>                 | 1.2    | _        | ns   |         |  |

| Address setup time                     | t <sub>avkh</sub>                 | 0.4    | _        | ns   | 2       |  |

| Data setup time                        | t <sub>DVKH</sub>                 | 0.4    | _        | ns   | 2       |  |

| Address hold time                      | t <sub>KHAX</sub>                 | 1.0    | _        | ns   |         |  |

| Data hold time                         | t <sub>KHDX</sub>                 | 1.0    | _        | ns   |         |  |

| Clock high to output valid             | t <sub>KHQV</sub>                 | 1.7    | 5.5      | ns   | 1       |  |

| Clock low to output valid              | t <sub>KLQV</sub>                 | 0.5    | 2.3      | ns   |         |  |

| Clock low to output hold               | t <sub>KLQX</sub>                 | 0.5    | _        | ns   |         |  |

| Clock low to output low-Z (SS control) | t <sub>KLQX2</sub>                | 0.5    | _        | ns   | 1, 4, 6 |  |

| Clock high to output high-Z            | t <sub>KHQZ</sub>                 | 0.5    | 2.3      | ns   | 1, 3, 6 |  |

| Output enable low to output low-Z      | t <sub>GLQX</sub>                 | 0.1    | _        | ns   | 1, 4, 6 |  |

| Output enable low to output valid      | $t_{\scriptscriptstyle \sf GLQV}$ | _      | 2.3      | ns   | 1, 4    |  |

| Output enable high to output high-Z    | t <sub>GHQZ</sub>                 | _      | 2.3      | ns   | 1, 3    |  |

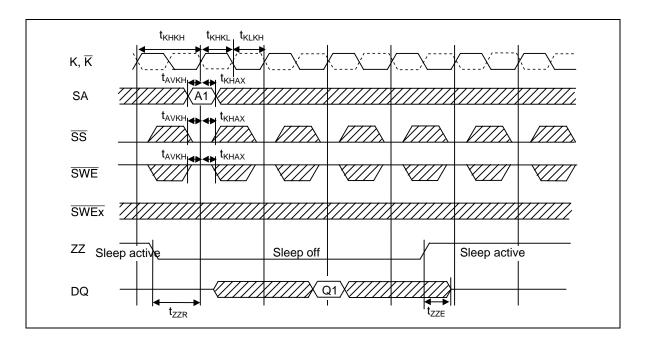

| Sleep mode recovery time               | t <sub>zzr</sub>                  | 20.0   | _        | ns   | 5       |  |

| Sleep mode enable time                 | t <sub>-77</sub>                  | _      | 15.0     | ns   | 1, 3, 5 |  |

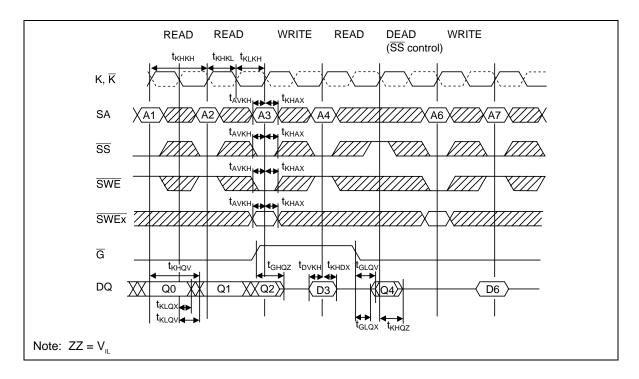

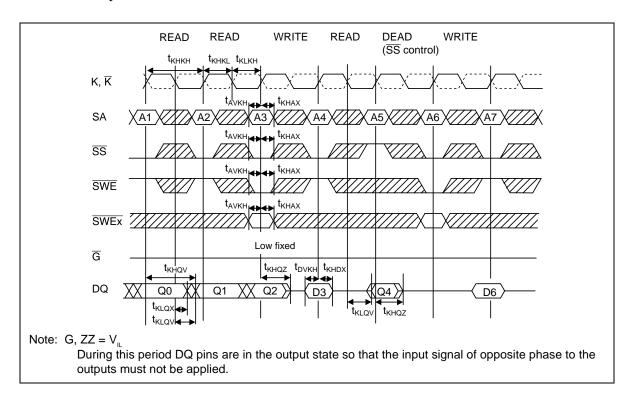

Notes: 1. See figure in "AC Test Conditions".

- 2. Parameters may be guaranteed by design, i.e., without tester guardband.

- 3. Transitions are measured ±50 mV of output high impedance from output low impedance.

- 4. Transitions are measured  $\pm 50$  mV from steady state voltage.

- 5. When ZZ is switching, clock input K must be at the same logic level for the reliable operation.

- 6. Minimum value is verified by design and tested without guardband.

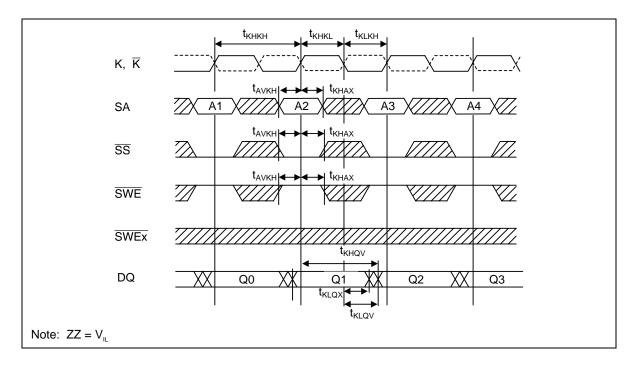

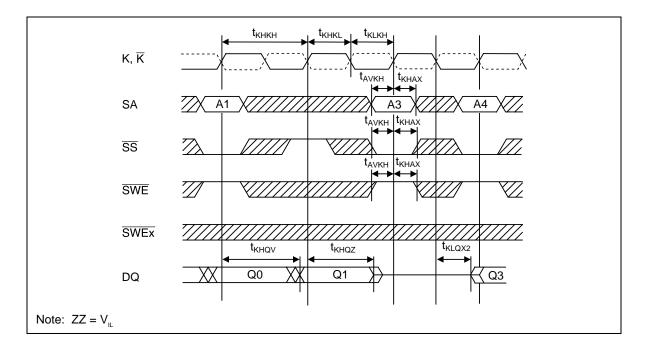

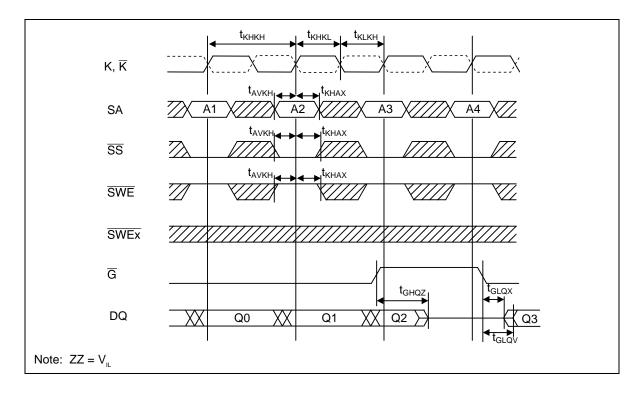

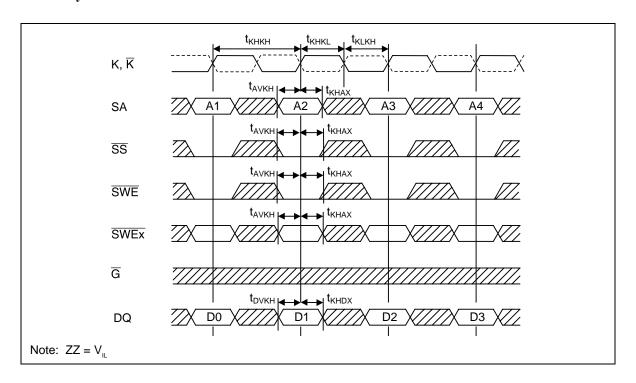

#### **Timing Waveforms**

## Read Cycle-1

## Read Cycle-2 (SS Controlled)

#### **Read Cycle-3** ( $\overline{G}$ Controlled)

## Write Cycle

#### Read-Write Cycle-1

#### Read-Write Cycle-2

#### **ZZ** Control

**Input Capacitance**  $(V_{DD} = 2.5 \text{ V}, V_{DDQ} = 1.5 \text{ V}, Ta = +25^{\circ}\text{C}, f = 1 \text{ MHz})$

| Parameter               | Symbol           | Min | Max | Unit | Pin name                                                    | Notes   |

|-------------------------|------------------|-----|-----|------|-------------------------------------------------------------|---------|

| Input capacitance       | C <sub>IN</sub>  | _   | 4   | pF   | SAn, $\overline{SS}$ , $\overline{SWE}$ , $\overline{SWEx}$ | 1, 3    |

| Clock input capacitance | C <sub>CLK</sub> | _   | 5   | pF   | K, $\overline{K}$                                           | 1, 2, 3 |

| I/O capacitance         | C <sub>io</sub>  | _   | 5   | pF   | DQxn                                                        | 1, 3    |

Notes: 1. This parameter is sampled and not 100% tested.

- 2. Exclude  $\overline{G}$

- 3. Connect pins to GND, except  $\rm V_{\rm \tiny DD},\,V_{\rm \tiny DDQ},$  and the measured pin.

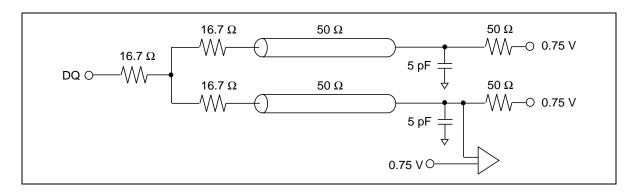

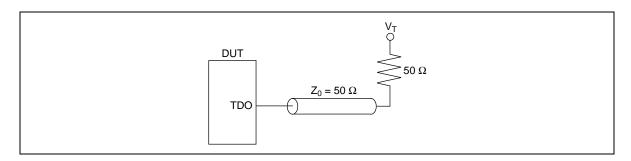

#### **AC Test Conditions**

| Parameter                                | Symbol              | Conditions               | Unit Note |  |

|------------------------------------------|---------------------|--------------------------|-----------|--|

| Input and output timing reference levels | $V_{REF}$           | 0.75                     | V         |  |

| Input signal amplitude                   | $V_{IL}$ , $V_{IH}$ | 0.25 to 1.25             | V         |  |

| Input rise / fall time                   | tr, tf              | 0.5 (10% to 90%)         | ns        |  |

| Clock input timing reference level       |                     | Differential cross point |           |  |

| V <sub>DIF</sub> to clock                |                     | 0.75                     | V         |  |

| V <sub>cм</sub> to clock                 |                     | 1.10                     | V         |  |

| Output loading conditions                |                     | See figure below         |           |  |

Note: Parameters are tested with RQ = 250  $\Omega$  and V<sub>DDQ</sub> = 1.5 V.

#### **Output Loading Conditions**

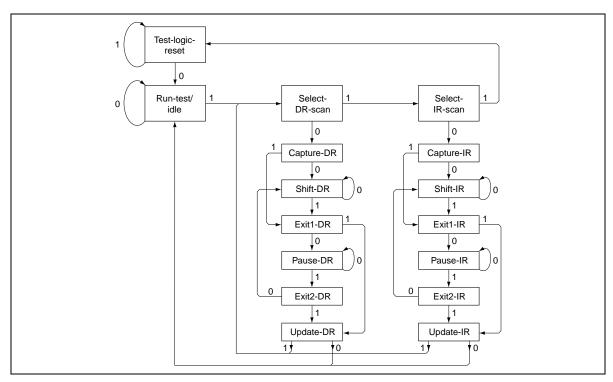

#### **Boundary Scan Test Access Port Operations**

#### Overview

In order to perform the interconnect testing of the modules that include this SRAM, the serial boundary scan test access port (TAP) is designed to operate in a manner consistent with IEEE Standard 1149.1 - 1990. But does not implement all of the functions required for 1149.1 compliance the HM64YLB series contains a TAP controller. Instruction register, boundary scans register, bypass register and ID register.

#### **Test Access Port Pins**

| Symbol I/O | Name             |  |

|------------|------------------|--|

| TCK        | Test clock       |  |

| TMS        | Test mode select |  |

| TDI        | Test data in     |  |

| TDO        | Test data out    |  |

Note: This device does not have a TRST (TAP reset) pin. TRST is optional in IEEE 1149.1. To disable the TAP, TCK must be connected to  $V_{\rm ss}$ . TDO should be left unconnected. To test boundary scan, the ZZ pin needs to be kept below  $V_{\rm REF} - 0.4~{\rm V}$ .

## **TAP DC Operating Characteristics** (Ta = 0 to +85°C)

| Parameter                            | Symbol          | Min    | Max    | Notes |

|--------------------------------------|-----------------|--------|--------|-------|

| Boundary scan input high voltage     | V <sub>IH</sub> | 1.4 V  | 3.6 V  |       |

| Boundary scan input low voltage      | V <sub>IL</sub> | -0.3 V | 0.8 V  |       |

| Boundary scan input leakage current  | I <sub>u</sub>  | –10 μA | +10 μΑ | 1     |

| Boundary scan output low voltage     | V <sub>oL</sub> | _      | 0.2 V  | 2     |

| Boundary scan output high voltage    | V <sub>OH</sub> | 2.1 V  | _      | 3     |

| Boundary scan output leakage current | I <sub>LO</sub> | –5 μΑ  | +5 μΑ  | 4     |

Notes: 1.  $0 \le V_{IN} \le 3.6 \text{ V}$  for all logic input pins

- 2.  $I_{OL} = 2 \text{ mA at } V_{DD} = 2.5 \text{ V}.$

- 3.  $I_{OH} = -2 \text{ mA}$  at  $V_{DD} = 2.5 \text{ V}$ .

- 4.  $0 \le V_{OUT} \le V_{DD}$ , TDO in high-Z

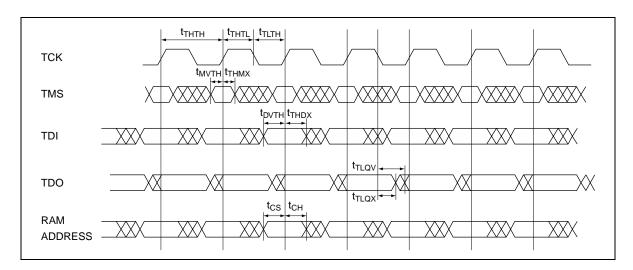

**TAP AC Operating Characteristics** (Ta = 0 to +85°C)

| Parameter                   | Symbol                                | Min | Max | Unit | Note |

|-----------------------------|---------------------------------------|-----|-----|------|------|

| Test clock cycle time       | t <sub>тнтн</sub>                     | 67  | _   | ns   |      |

| Test clock high pulse width | t <sub>THTL</sub>                     | 30  | _   | ns   |      |

| Test clock low pulse width  | $\mathbf{t}_{\scriptscriptstyleTLTH}$ | 30  | _   | ns   |      |

| Test mode select setup      | t <sub>MVTH</sub>                     | 10  | _   | ns   |      |

| Test mode select hold       | $\mathbf{t}_{THMX}$                   | 10  | _   | ns   |      |

| Capture setup               | t <sub>cs</sub>                       | 10  | _   | ns   | 1    |

| Capture hold                | t <sub>ch</sub>                       | 10  | _   | ns   | 1    |

| TDI valid to TCK high       | t <sub>DVTH</sub>                     | 10  | _   | ns   |      |

| TCK high to TDI don't care  | t <sub>THDX</sub>                     | 10  | _   | ns   |      |

| TCK low to TDO unknown      | t <sub>TLQX</sub>                     | 0   | _   | ns   |      |

| TCK low to TDO valid        | t <sub>TLQV</sub>                     | _   | 20  | ns   |      |

Note: 1.  $t_{cs} + t_{CH}$  defines the minimum pause in RAM I/O pad transitions to assure pad data capture.

## **TAP AC Test Conditions** $(V_{DD} = 2.5 \text{ V})$

Temperature  $0^{\circ}C \le Ta \le +85^{\circ}C$

Input timing measurement reference level 1.1 VInput pulse levels 0 to 2.5 V

Input rise/fall time 1.5 ns typical (10% to 90%)

Output timing measurement reference level 1.25 VTest load termination supply voltage ( $V_T$ ) 1.25 V

Output load See figure below

### **Boundary Scan AC Test Load**

## **TAP Controller Timing Diagram**

## **Test Access Port Registers**

| Register name          | Length  | Symbol    | Note |

|------------------------|---------|-----------|------|

| Instruction register   | 3 bits  | IR [2:0]  |      |

| Bypass register        | 1 bit   | BP        |      |

| ID register            | 32 bits | ID [31:0] |      |

| Boundary scan register | 70 bits | BS [70:1] |      |

#### **TAP Controller Instruction Set**

| IR2 | IR1 | IR0 | Instruction | Operation                                           |

|-----|-----|-----|-------------|-----------------------------------------------------|

| 0   | 0   | 0   | SAMPLE-Z    | Tristate all data drivers and capture the pad value |

| 0   | 0   | 1   | IDCODE      |                                                     |

| 0   | 1   | 0   | SAMPLE-Z    | Tristate all data drivers and capture the pad value |

| 0   | 1   | 1   | BYPASS      |                                                     |

| 1   | 0   | 0   | SAMPLE      |                                                     |

| 1   | 0   | 1   | BYPASS      |                                                     |

| 1   | 1   | 0   | PRIVATE     | Do not use. They are reserved for vendor use only   |

| 1   | 1   | 1   | BYPASS      |                                                     |

Note: This device does not perform EXTEST, INTEST or the preload portion of the PRELOAD command in IEEE 1149.1.

## Boundary Scan Order (HM64YLB36514)

| Bit# | Bump ID | Signal name | Bit # | Bump ID | Signal name |

|------|---------|-------------|-------|---------|-------------|

| 1    | 5R      | M2          | 36    | 3B      | SA12        |

| 2    | 4P      | SA0         | 37    | 2B      | SA15        |

| 3    | 4T      | SA3         | 38    | 3A      | SA13        |

| 4    | 6R      | SA1         | 39    | 3C      | SA11        |

| 5    | 5T      | SA2         | 40    | 2C      | SA16        |

| 6    | 7T      | ZZ          | 41    | 2A      | SA14        |

| 7    | 6P      | DQa8        | 42    | 2D      | DQc8        |

| 8    | 7P      | DQa7        | 43    | 1D      | DQc7        |

| 9    | 6N      | DQa6        | 44    | 2E      | DQc6        |

| 10   | 7N      | DQa5        | 45    | 1E      | DQc5        |

| 11   | 6M      | DQa4        | 46    | 2F      | DQc4        |

| 12   | 6L      | DQa2        | 47    | 2G      | DQc2        |

| 13   | 7L      | DQa3        | 48    | 1G      | DQc3        |

| 14   | 6K      | DQa0        | 49    | 2H      | DQc0        |

| 15   | 7K      | DQa1        | 50    | 1H      | DQc1        |

| 16   | 5L      | SWEa        | 51    | 3G      | SWEc        |

| 17   | 4L      | K           | 52    | 4D      | ZQ          |

| 18   | 4K      | K           | 53    | 4E      | SS          |

| 19   | 4F      | G           | 54    | 4G      | NC          |

| 20   | 5G      | SWEb        | 55    | 4H      | NC          |

| 21   | 7H      | DQb1        | 56    | 4M      | SWE         |

| 22   | 6H      | DQb0        | 57    | 3L      | SWEd        |

| 23   | 7G      | DQb3        | 58    | 1K      | DQd1        |

| 24   | 6G      | DQb2        | 59    | 2K      | DQd0        |

| 25   | 6F      | DQb4        | 60    | 1L      | DQd3        |

| 26   | 7E      | DQb5        | 61    | 2L      | DQd2        |

| 27   | 6E      | DQb6        | 62    | 2M      | DQd4        |

| 28   | 7D      | DQb7        | 63    | 1N      | DQd5        |

| 29   | 6D      | DQb8        | 64    | 2N      | DQd6        |

| 30   | 6A      | SA7         | 65    | 1P      | DQd7        |

| 31   | 6C      | SA8         | 66    | 2P      | DQd8        |

| 32   | 5C      | SA4         | 67    | 3T      | SA18        |

| 33   | 5A      | SA6         | 68    | 2R      | SA10        |

| 34   | 6B      | SA9         | 69    | 4N      | SA17        |

| 35   | 5B      | SA5         | 70    | 3R      | M1          |

Notes: 1. Bit#1 is the first scan bit to exit the chip.

- 2. The NC pads listed in this table are indeed no connects, but are represented in the boundary scan register by a "Place Holder". Place holder registers are internally connected to  $V_{ss}$ .

- 3. In boundary scan mode, differential input K and  $\overline{K}$  are referenced to each other and must be at the opposite logic levels for the reliable operation.

- 4. ZZ must remain V<sub>11</sub> during boundary scan.

- 5. In boundary scan mode, ZQ must be driven to  $V_{\tiny DDQ}$  or  $V_{\tiny SS}$  supply rail to ensure consistent results.

- 6. M1 and M2 must be driven to  $V_{\tiny DD}$ ,  $V_{\tiny DDQ}$  or  $V_{\tiny SS}$  supply rail to ensure consistent results.

#### **ID Register**

| Part         | Revision<br>number<br>(31:28) | Device density<br>and configuration<br>(27:18) | Vendor<br>definition<br>(17:12) | Vendor JEDEC<br>code (11:1) | Start<br>bit (0) |

|--------------|-------------------------------|------------------------------------------------|---------------------------------|-----------------------------|------------------|

| HM64YLB36514 | 0000                          | 0011100100                                     | 000000                          | 0000000111                  | 1                |

#### **TAP Controller State Diagram**

Note: The value adjacent to each state transition in this figure represents the signal present at TMS at the time of a rising edge at TCK.

No matter what the original state of the controller, it will enter Test-logic-reset when TMS is held high for at least five rising edges of TCK.

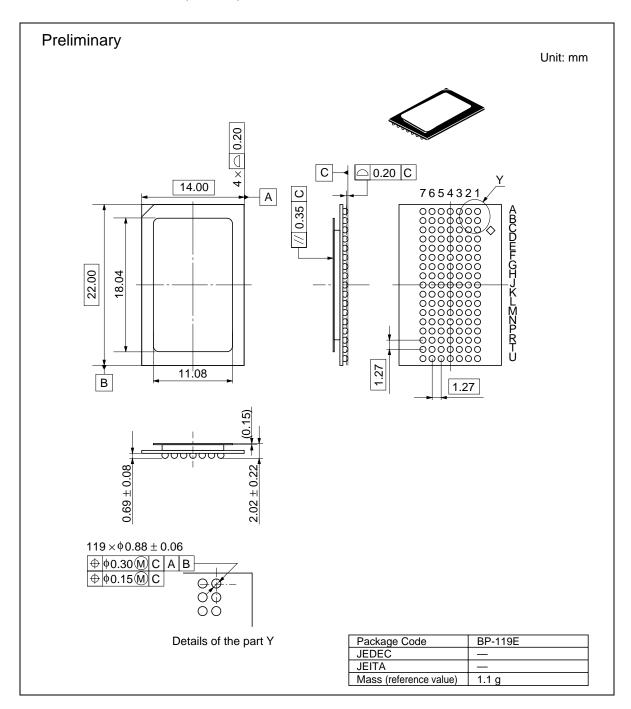

#### **Package Dimensions**

#### HM64YLB36514BP Series (BP-119E)

#### Renesas Technology Corp. Sales Strategic Planning Div. Nippon Bldg., 2-6-2, Ohte-machi, Chiyoda-ku, Tokyo 100-0004, Japan

Keep safety first in your circuit designs!

1. Renesas Technology Corporation puts the maximum effort into making semiconductor products better and more reliable, but there is always the possibility that trouble may occur with them. Trouble with semiconductors may lead to personal injury, fire or property damage.

Remember to give due consideration to safety when making your circuit designs, with appropriate measures such as (i) placement of substitutive, auxiliary circuits, (ii) use of nonflammable material or (iii) prevention against any malfunction or mishap.

- Notes regarding these materials are intended as a reference to assist our customers in the selection of the Renesas Technology Corporation product best suited to the customer's application; they do not convey any license under any intellectual property rights, or any other rights, belonging to Renesas Technology Corporation or a third party.

2. Renesas Technology Corporation assumes no responsibility for any damage, or infringement of any third-party's rights, originating in the use of any product data, diagrams, charts, programs, algorithms, or circuit application examples contained in these materials.

3. All information contained in these materials, including product data, diagrams, charts, programs and algorithms represents information on products at the time of publication of these materials, and are subject to change by Renesas Technology Corporation without notice due to product improvements or other reasons. It is therefore recommended that customers contact Renesas Technology Corporation or an authorized Renesas Technology Corporation product distributor for the latest product information before purchasing a product listed herein.

The information described here may contain technical inaccuracies or typographical errors.

Renesas Technology Corporation assumes no responsibility for any damage, liability, or other loss rising from these inaccuracies or errors.

Please also pay attention to information published by Renesas Technology Corporation by various means, including the Renesas Technology Corporation Semiconductor home page (http://www.renesas.com).

4. When using any or all of the information contained in these materials, including product data, diagrams, charts, programs, and algorithms, please be sure to evaluate all information as a total system before making a final decision on the applicability of the information and products. Renesas Technology Corporation assumes no responsibility for any damage, liability or other loss resulting from the information contained herein.

5. Renesas Technolo

- Any diversion or reexport contrary to the export control laws and regulations of Japan and/or the country of destination is prohibited. 8. Please contact Renesas Technology Corporation for further details on these materials or the products contained therein

http://www.renesas.com

Copyright © 2003. Renesas Technology Corporation, All rights reserved. Printed in Japan. Colophon 0.0