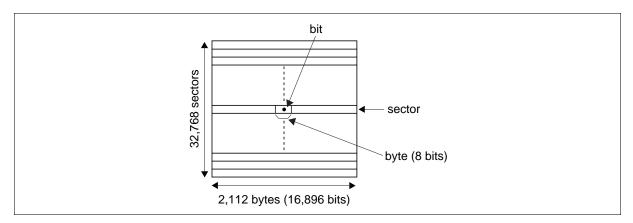

512M AND type Flash Memory More than 32,113-sector (542,581,248-bit)

# **HITACHI**

ADE-203-1221 (Z) Preliminary Rev. 0.0 Sep. 20, 2000

### **Description**

The Hitachi HN29V51211 Series is a CMOS Flash Memory with AND type multi-level memory cells. It has fully automatic programming and erase capabilities with a single 3.0 V power supply. The functions are controlled by simple external commands. To fit the I/O card applications, the unit of programming and erase is as small as (2048 + 64) bytes. Initial available sectors of HN29V51211 are more than 32,113 (98% of all sector address) and less than 32,768 sectors.

### **Features**

- On-board single power supply ( $V_{CC}$ ):  $V_{CC} = 2.7 \text{ V}$  to 3.6 V

- Organization

- AND Flash Memory: (2048 + 64) bytes  $\times$  (More than 32,113 sectors)

- Data register: (2048 + 64) bytes

- Multi-level memory cell

- 2 bit/per memory cell

- Automatic programming

- Sector program time: 1.0 ms (typ)

- System bus free

- Address, data latch function

- Internal automatic program verify function

- Status data polling function

- Automatic erase

- Single sector erase time: 1.0 ms (typ)

- System bus free

- Internal automatic erase verify function

- Status data polling function

Preliminary: The specification of this device are subject to change without notice. Please contact your nearest Hitachi's Sales Dept. regarding specification.

- Erase mode

- Single sector erase ((2048 + 64) byte unit)

- Fast serial read access time:

- First access time: 50 µs (max)

- Serial access time: 50 ns (max)

- Low power dissipation:

- $--I_{CC1} = 2 \text{ mA (typ) (Read)}$

- $I_{CC2} = 20 \text{ mA (max) (Read)}$

- $I_{SB2} = 50 \mu A \text{ (max) (Standby)}$

- $--I_{CC3}/I_{CC4} = 40 \text{ mA (max) (Erase/Program)}$

- $I_{SB3} = 20 \mu A \text{ (max) (Deep standby)}$

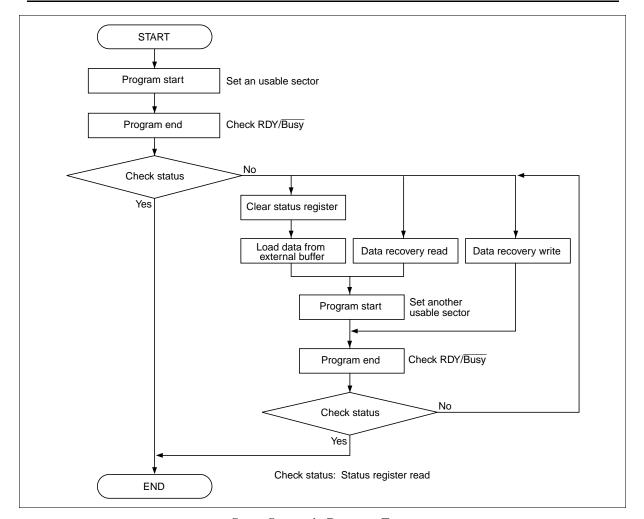

- The following architecture is required for data reliability.

- Error correction: more than 3-bit error correction per each sector read

- Spare sectors: 1.8% (579 sectors) within usable sectors

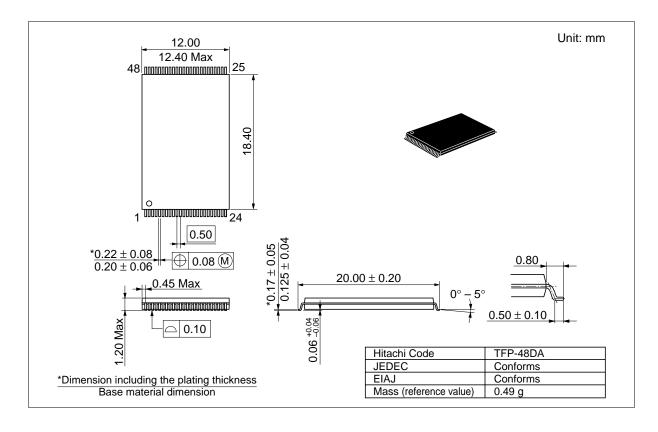

## **Ordering Information**

| Type No.       | Available sector         | Package                                                                       |

|----------------|--------------------------|-------------------------------------------------------------------------------|

| HN29V51211T-50 | More than 32,113 sectors | 12.0 × 18.40 mm <sup>2</sup> 0.5 mm pitch<br>48-pin plastic TSOP I (TFP-48DA) |

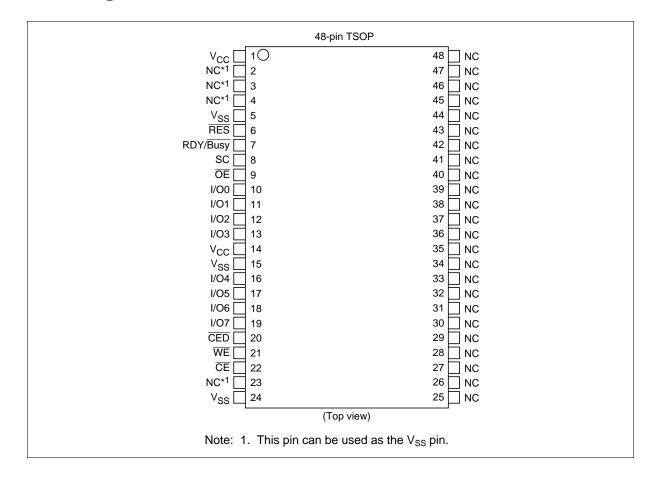

## Pin Arrangement

## **Pin Description**

| Pin name           | Function            |

|--------------------|---------------------|

| I/O0 to I/O7       | Input/output        |

| CE                 | Chip enable         |

| ŌĒ                 | Output enable       |

| WE                 | Write enable        |

| CDE                | Command data enable |

| V <sub>cc</sub> *1 | Power supply        |

| V <sub>SS</sub> *1 | Ground              |

| RDY/Busy           | Ready/Busy          |

| RES                | Reset               |

| SC                 | Serial clock        |

| NC                 | No connection       |

Note: 1. All  $V_{cc}$  and  $V_{ss}$  pins should be connected to a common power supply and a ground, respectively.

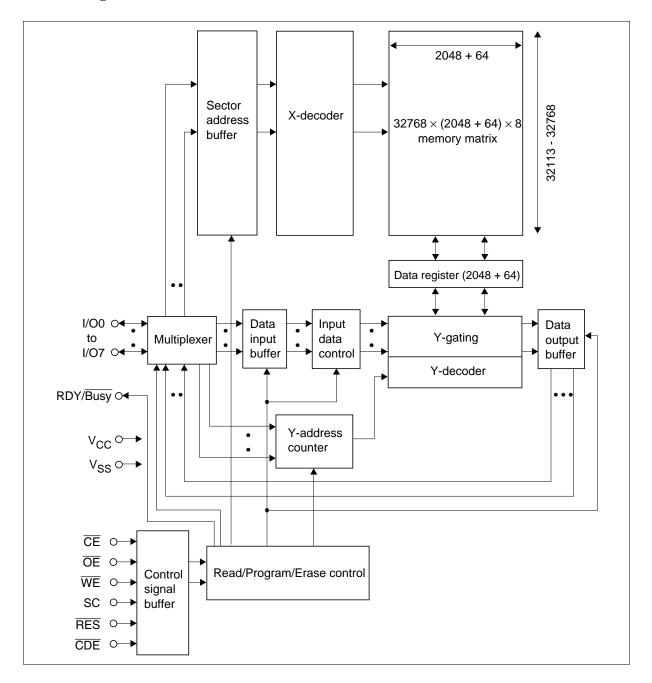

## **Block Diagram**

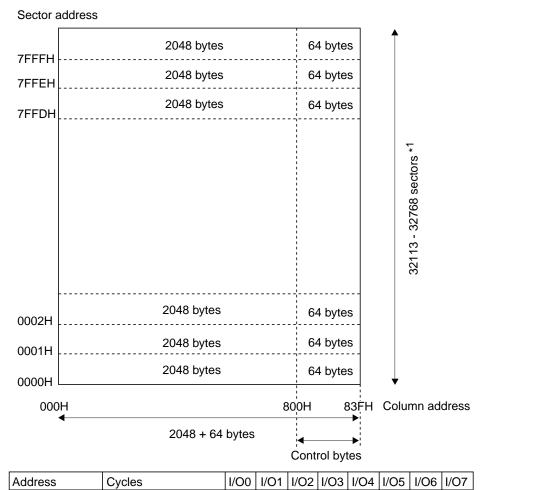

### **Memory Map and Address**

| Address        | Cycles               | 1/00 | I/O1 | 1/02 | I/O3 | 1/04 | I/O5 | 1/06 | 1/07 |

|----------------|----------------------|------|------|------|------|------|------|------|------|

| Sector address | SA (1): First cycle  | A0   | A1   | A2   | A3   | A4   | A5   | A6   | A7   |

|                | SA (2): Second cycle | A8   | A9   | A10  | A11  | A12  | A13  | A14  | ×*2  |

| Column address | CA (1): First cycle  | A0   | A1   | A2   | A3   | A4   | A5   | A6   | A7   |

|                | CA (2): Second cycle | A8   | A9   | A10  | A11  | ×    | ×    | ×    | ×    |

Notes: 1. Some failed sectors may exist in the device. The failed sectors can be recognized by reading the sector valid data written in a part of the column address 800 to 83F (The specific address is TBD.). The sector valid data must be read and kept outside of the sector before the sector erase. When the sector is programmed, the sector valid data should be written back to the sector.

An × means "Don't care". The pin level can be set to either V<sub>IL</sub> or V<sub>IH</sub>, referred to DC characteristics.

### **Pin Function**

$\overline{\text{CE}}$ :  $\overline{\text{CE}}$  is used to select the device. The status returns to the standby at the rising edge of  $\overline{\text{CE}}$  in the reading operation. However, the status does not return to the standby at the rising edge of  $\overline{\text{CE}}$  in the busy state in programming and erase operation.

$\overline{OE}$ : Memory data and status register data can be read, when  $\overline{OE}$  is  $V_{II}$ .

$\overline{WE}$ : Commands and address are latched at the rising edge of  $\overline{WE}$ .

SC: Programming and reading data is latched at the rising edge of SC.

$\overline{\text{RES}}$ :  $\overline{\text{RES}}$  pin must be kept at the  $V_{ILR}$  ( $V_{SS} \pm 0.2$  V) level when  $V_{CC}$  is turned on and off. In this way, data in the memory is protected against unintentional erase and programming.  $\overline{\text{RES}}$  must be kept at the  $V_{IHR}$  ( $V_{CC} \pm 0.2$  V) level during any operations such as programming, erase and read.

$\overline{\text{CDE}}$ : Commands and data are latched when  $\overline{\text{CDE}}$  is  $V_{IL}$  and address is latched when  $\overline{\text{CDE}}$  is  $V_{IH}$ .

**RDY/Busy:** The RDY/Busy indicates the program/erase status of the flash memory. The RDY/Busy signal is initially at a high impedance state. It turns to a  $V_{OL}$  level after the (40H) command in programming operation or the (B0H) command in erase operation. After the erase or programming operation finishes, the RDY/Busy signal turns back to the high impedance state.

**I/O0 to I/O7:** The I/O pins are used to input data, address and command, and are used to output memory data and status register data.

### **Mode Selection**

| Mode                   | CE              | OE              | WE              | SC              | RES              | CDE             | RDY/Busy*3      | I/O0 to I/O7            |

|------------------------|-----------------|-----------------|-----------------|-----------------|------------------|-----------------|-----------------|-------------------------|

| Deep standby           | ×*4             | ×               | ×               | ×               | $V_{ILR}$        | ×               | $V_{OH}$        | High-Z                  |

| Standby                | $V_{\text{IH}}$ | ×               | ×               | ×               | $V_{IHR}$        | ×               | $V_{OH}$        | High-Z                  |

| Output disable         | $V_{\text{IL}}$ | $V_{\text{IH}}$ | $V_{\text{IH}}$ | ×               | $V_{IHR}$        | ×               | V <sub>OH</sub> | High-Z                  |

| Status register read*1 | $V_{\text{IL}}$ | $V_{IL}$        | $V_{\text{IH}}$ | ×               | $V_{IHR}$        | ×               | $V_{OH}$        | Status register outputs |

| Command write*2        | V <sub>IL</sub> | V <sub>IH</sub> | V <sub>IL</sub> | V <sub>IL</sub> | $V_{\text{IHR}}$ | V <sub>IL</sub> | V <sub>OH</sub> | Din                     |

Notes: 1. Default mode after the power on is the status register read mode (refer to status transition). From I/O0 to I/O7 pins output the status, when  $\overline{CE} = V_{IL}$  and  $\overline{OE} = V_{IL}$  (conventional read operation condition).

- 2. Refer to the command definition. Data can be read, programmed and erased after commands are written in this mode.

- 3. The RDY/ $\overline{\text{Busy}}$  bus should be pulled up to  $V_{\text{CC}}$  to maintain the  $V_{\text{OH}}$  level while the RDY/ $\overline{\text{Busy}}$  pin outputs a high impedance.

- 4. An  $\times$  means "Don't care". The pin level can be set to either  $V_{IL}$  or  $V_{IH}$  referred to DC characteristics.

## **Command Definition**\*<sup>1, 2</sup>

|                 |                                                                                                                                                                                                                                                                         |                  |               | First bus c      | ycle    | Second bu      |          |                     |

|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|---------------|------------------|---------|----------------|----------|---------------------|

| Command         | Serial read (1) (Without (With CA)  Serial read (2)  Read identifier codes  Data recovery read  erase Single sector  program Program (1) (Without CA*7)  (With CA)  Program (2)*10  Program (3) (Control by Program (4) (Without CA*7)  (With CA)  et r status register |                  | Bus<br>cycles | Operation mode*3 | Data in | Operation mode | Data in  | Data out            |

| Read            | Serial read (1)                                                                                                                                                                                                                                                         | (Without CA)     | 3             | Write            | 00H     | Write          | SA (1)*4 |                     |

|                 |                                                                                                                                                                                                                                                                         | (With CA)        | 3 + 2h*6      | Write            | 00H     | Write          | SA (1)*4 |                     |

|                 | Serial read (2)                                                                                                                                                                                                                                                         |                  | 3             | Write            | F0H     | Write          | SA (1)*4 |                     |

|                 | Read identifier                                                                                                                                                                                                                                                         | codes            | 1             | Write            | 90H     | Read           |          | ID* <sup>8, 9</sup> |

|                 | Data recovery                                                                                                                                                                                                                                                           | read             | 1             | Write            | 01H     | Read           |          | Recovery data       |

| Auto erase      | Single sector                                                                                                                                                                                                                                                           |                  | 4             | Write            | 20H     | Write          | SA (1)*4 |                     |

| Auto program    | Program (1)                                                                                                                                                                                                                                                             | `                | 4             | Write            | 10H     | Write          | SA (1)*4 |                     |

|                 |                                                                                                                                                                                                                                                                         | (With CA*7)      | 4 + 2h*6      | Write            | 10H     | Write          | SA (1)*4 |                     |

|                 | Program (2)*10                                                                                                                                                                                                                                                          |                  | 4             | Write            | 1FH     | Write          | SA (1)*4 |                     |

|                 | Program (3) (0                                                                                                                                                                                                                                                          | Control bytes)*7 | 4             | Write            | 0FH     | Write          | SA (1)*4 |                     |

|                 | Program (4)                                                                                                                                                                                                                                                             | (WithoutCA*7)    | 4             | Write            | 11H     | Write          | SA (1)*4 |                     |

|                 |                                                                                                                                                                                                                                                                         | (With CA*7)      | 4 + 2h*6      | Write            | 11H     | Write          | SA (1)*4 |                     |

| Reset           |                                                                                                                                                                                                                                                                         |                  | 1             | Write            | FFH     |                |          |                     |

| Clear status re | egister                                                                                                                                                                                                                                                                 |                  | 1             | Write            | 50H     |                |          |                     |

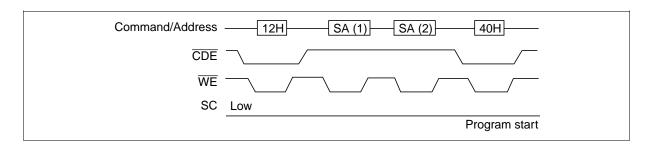

| Data recovery   | write                                                                                                                                                                                                                                                                   |                  | 4             | Write            | 12H     | Write          | SA (1)*4 | ·                   |

|                 |                 |                                |               | Third bus c    | ycle     | Fourth bus     | cycle              |

|-----------------|-----------------|--------------------------------|---------------|----------------|----------|----------------|--------------------|

| Command         |                 |                                | Bus<br>cycles | Operation mode | Data in  | Operation mode | Data in            |

| Read            | Serial read (1) | (Without CA)                   | 3             | Write          | SA (2)*4 |                |                    |

|                 |                 | (With CA)                      | 3 + 2h*6      | Write          | SA (2)*4 | Write          | CA (1)*5           |

|                 | Serial read (2) |                                | 3             | Write          | SA (2)*4 |                |                    |

|                 | Read identifier | codes                          | 1             |                |          |                |                    |

|                 | Data recovery   | read                           | 1             |                |          |                |                    |

| Auto erase      | Single sector   |                                | 4             | Write          | SA (2)*4 | Write          | B0H* <sup>11</sup> |

| Auto program    | Program (1)     | (Without<br>CA* <sup>7</sup> ) | 4             | Write          | SA (2)*4 | Write          | 40H*11, 12         |

|                 |                 | (With CA*7)                    | 4 + 2h*6      | Write          | SA (2)*4 | Write          | CA (1)             |

|                 | Program (2)*10  |                                | 4             | Write          | SA (2)*4 | Write          | 40H*11, 12         |

|                 | Program (3) (0  | Control bytes)*7               | 4             | Write          | SA (2)*4 | Write          | 40H*11, 12         |

|                 | Program (4)     | (WithoutCA*7)                  | 4             | Write          | SA (2)*4 | Write          | 40H*11, 12         |

|                 |                 | (With CA*7)                    | 4 + 2h*6      | Write          | SA (2)*4 | Write          | CA (1)             |

| Reset           |                 |                                | 1             |                |          |                |                    |

| Clear status re | egister         |                                | 1             |                |          |                |                    |

| Data recovery   | write           |                                | 4             | Write          | SA (2)*4 | Write          | 40H*11, 12         |

|                 |                 |                             |               | Fifth bus cy   | /cle     | Sixth bus c    | ycle       |

|-----------------|-----------------|-----------------------------|---------------|----------------|----------|----------------|------------|

| Command         |                 |                             | Bus<br>cycles | Operation mode | Data in  | Operation mode | Data in    |

| Read            | Serial read (1) | (Without CA)                | 3             |                |          |                |            |

|                 |                 | (With CA)                   | 3 + 2h*6      | Write          | CA (2)*5 |                |            |

|                 | Serial read (2) |                             | 3             |                |          |                |            |

|                 | Read identifier | codes                       | 1             |                |          |                |            |

|                 | Data recovery   | read                        | 1             |                |          |                |            |

| Auto erase      | Single sector   |                             | 4             |                |          |                |            |

| Auto program    | Program (1)     | (Without CA* <sup>7</sup> ) | 4             |                |          |                |            |

|                 |                 | (With CA*7)                 | 4 + 2h*6      | Write          | CA (2)*5 | Write          | 40H*11, 12 |

|                 | Program (2)*10  |                             | 4             |                |          |                |            |

|                 | Program (3) (0  | Control bytes)*7            | 4             |                |          |                |            |

|                 | Program (4)     | (WithoutCA*7)               | 4             |                |          |                |            |

|                 |                 | (With CA*7)                 | 4 + 2h*6      | Write          | CA (2)   | Write          | 40H*11, 12 |

| Reset           |                 |                             | 1             |                |          |                |            |

| Clear status re | egister         |                             | 1             |                |          |                |            |

| Data recovery   | write           |                             | 4             |                |          |                |            |

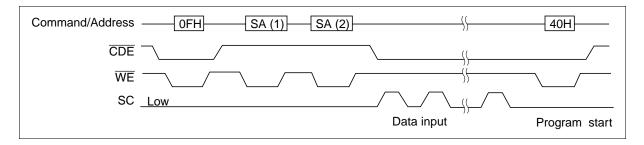

Notes: 1. Commands and sector address are latched at rising edge of WE pulses. Program data is latched at rising edge of SC pulses.

- 2. The chip is in the read status register mode when  $\overline{RES}$  is set to  $V_{IHR}$  first time after the power up.

- 3. Refer to the command read and write mode in mode selection.

- 4. SA (1) = Sector address (A0 to A7), SA (2) = Sector address (A8 to A14).

- 5. CA (1) = Column address (A0 to A7), CA (2) = Column address (A8 to A11). (0 A11 to A0 83FH)

- 6. The variable h is the input number of times of set of CA (1) and CA (2) (1 h 2048 + 64). Set of CA (1) and CA (2) can be input not only one time but free times.

- 7. By using program (1) and (3), data can additionally be programmed maximum 15 times for each sector before erase.

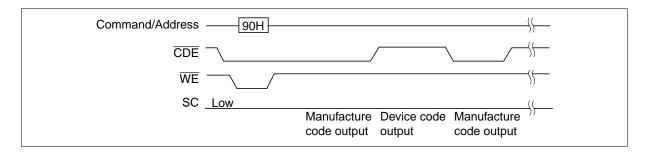

- 8. ID = Identifier code; Manufacturer code (07H), Device code (9DH).

- 9. The manufacturer identifier code is output when  $\overline{\text{CDE}}$  is low and the device identifier code is output when  $\overline{\text{CDE}}$  is high.

- 10. Before program (2) operations, data in the programmed sector must be erased.

- 11. No commands can be written during auto program and erase (when the RDY/ $\overline{\text{Busy}}$  pin outputs a  $V_{\text{ol}}$ ).

- 12. The fourth or sixth cycle of the auto program comes after the program data input is complete.

### **Mode Description**

#### Read

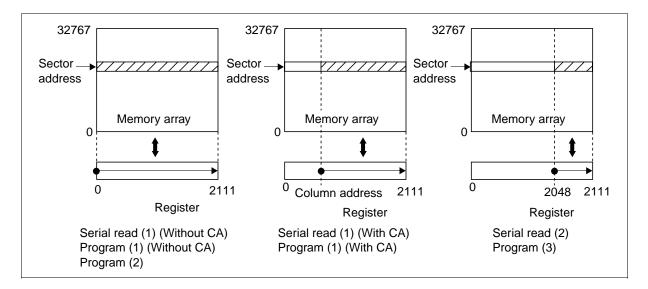

**Serial Read (1):** Memory data D0 to D2111 in the sector of address SA is sequentially read. Output data is not valid after the number of the SC pulse exceeds 2112. When CA is input, memory data D (m) to D (m + j) in the sector of address SA is sequentially read. Then output data is not valid after the number of the SC pulse exceeds (2112 to m). The mode turns back to the standby mode at any time when  $\overline{CE}$  is  $V_{IH}$ .

**Serial Read (2):** Memory data D2048 to D2111 in the sector of address SA is sequentially read. Output data is not valid after the number of the SC pulse exceeds 64. The mode turns back to the standby mode at any time when  $\overline{\text{CE}}$  is  $V_{\text{IH}}$ .

#### **Automatic Erase**

**Single Sector Erase:** Memory data D0 to D2111 in the sector of address SA is erased automatically by internal control circuits. After the sector erase starts, the erasure completion can be checked through the RDY/Busy signal and status data polling. All the bits in the sector are "1" after the erase. The sector valid data stored in a part of memory data D2048 to D2111 must be read and kept outside of the sector before the sector erase.

### **Automatic Program**

**Program** (1): Program data PD0 to PD2111 is programmed into the sector of address SA automatically by internal control circuits. When CA is input, program data PD (m) to PD (m + j) is programmed from CA into the sector of address SA automatically by internal control circuits. By using program (1), data can additionally be programed for each sector before the following erase. When the column is programmed, the data of the column must be [FF]. After the programming starts, the program completion can be checked through the RDY/Busy signal and status data polling. Programmed bits in the sector turn from "1" to "0" when they are programmed. The sector valid data should be included in the program data PD2048 to PD2111.

**Program (2):** Program data PD0 to PD2111 is programmed into the sector of address SA automatically by internal control circuits. After the programming starts, the program completion can be checked through the RDY/Busy signal and status data polling. Programmed bits in the sector turn from "1" to "0" when they are programmed. The sector must be erased before programming. The sector valid data should be included in the program data PD2048 to PD2111.

**Program (3):** Program data PD2048 to PD2111 is programmed into the sector of address SA automatically by internal control circuits. By using program (3), data can additionally be programed for each sector befor the following erase. When the column is programmed, the data of the column must be [FF]. After the programming starts, the program completion can be checked through the RDY/Busy signal and status data polling. Programmed bits in the sector turn from "1" to "0" when they are programmed.

**Program (4):** Program data PD0 to PD2111 is programmed into the sector of address SA automatically by internal control circuits. When CA is input, program data PD (m) to PD (m + j) is programmed from CA into the sector of address SA automatically by internal control circuits. By using program (4), data can be rewritten for each sector before the following erase. So the column data before programming operation are either "1" or "0". In this mode, E/W number of times must be counted whenever program (4) execute. After the programming starts, the program completion can be checked through the RDY/Busy signal and status data polling. The sector valid data should be included in the program data PD2048 to PD2111.

### Status Register Read

The status returns to the status register read mode from standby mode, when  $\overline{CE}$  and  $\overline{OE}$  is  $V_{IL}$ . In the status register read mode, I/O pins output the same operation status as in the status data polling defined in the function description.

#### **Identifier Read**

The manufacturer and device identifier code can be read in the identifier read mode. The manufacturer and device identifier code is selected with  $\overline{\text{CDE}} \, V_{IL}$  and  $V_{IH}$ , respectively.

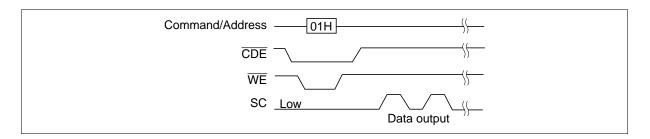

### **Data Recovery Read**

When the programming was an error, the program data can be read by using data recovery read. When an additional programming was an error, the data compounded of the program data and the origin data in the sector address SA can be read. Output data are not valid after the number of SA pulse exceeds 2112. The mode turns back to the standby mode at any time when  $\overline{CE}$  is  $V_{IH}$ . The read data are invalid when addresses are latched at a rising edge of  $\overline{WE}$  pulse after the data recovery read command is written.

### **Data Recovery Write**

When the programming into a sector of address SA was an error, the program data can be rewritten automatically by internal control circuit into the other selected sector of address SA'. Since the data recovery write mode is internally Program (4) mode, rewritten sector of address SA' needs no sector erase before rewrite. After the data recovery write mode starts, the program completion can be checked through the RDY/Busy signal and the status data polling.

### Command/Address/Data Input Sequence

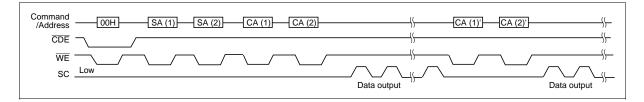

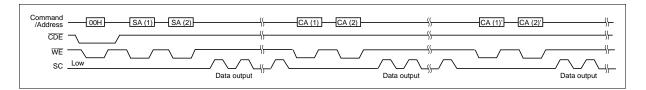

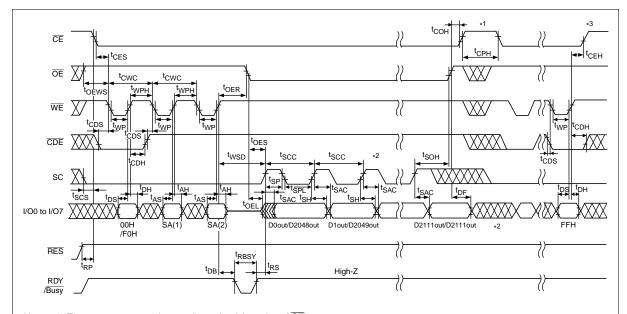

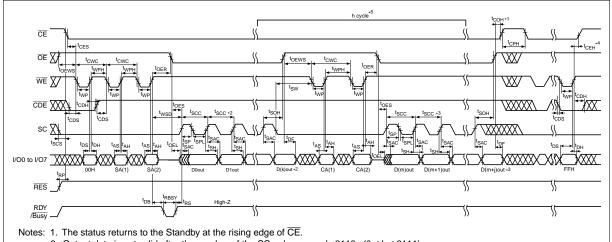

### Serial Read (1) (With CA before SC)

### Serial Read (1) (With CA after SC)

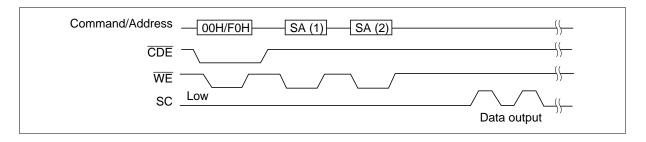

### Serial Read (1) (Without CA), (2)

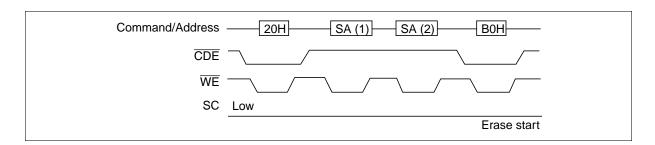

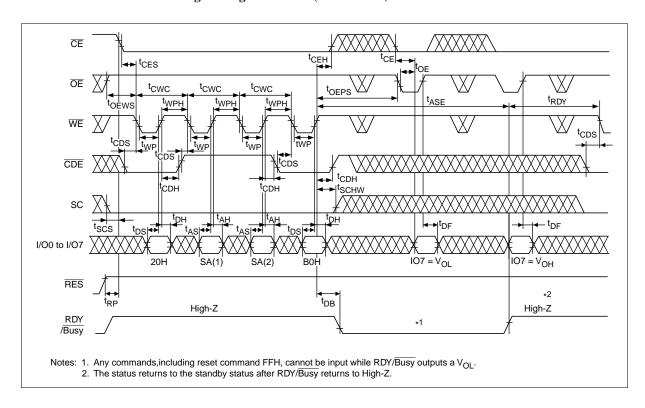

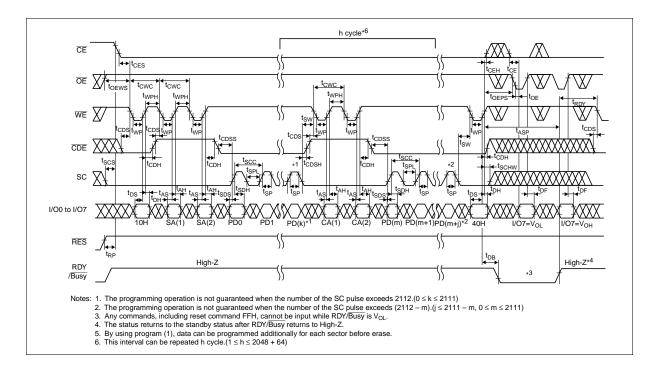

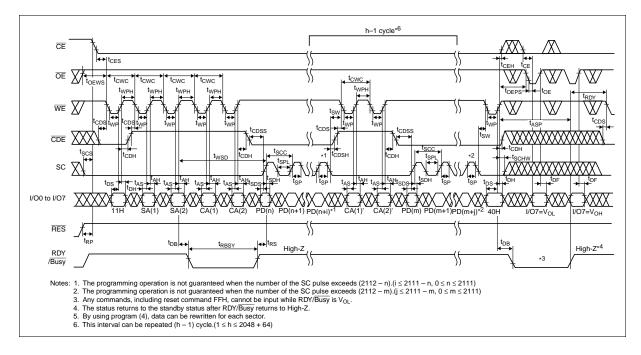

### **Single Sector Erase**

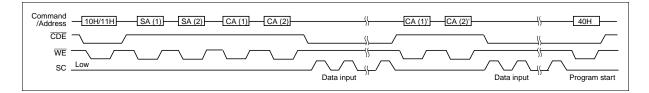

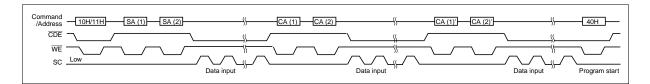

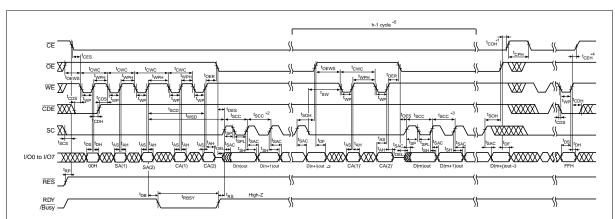

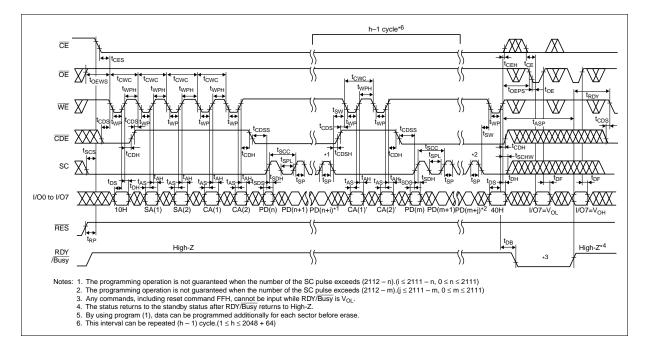

### Program (1), (4) (With CA before SC)

### Program (1), (4) (With CA after SC)

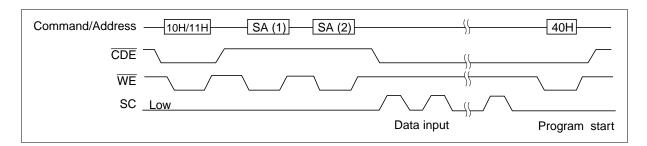

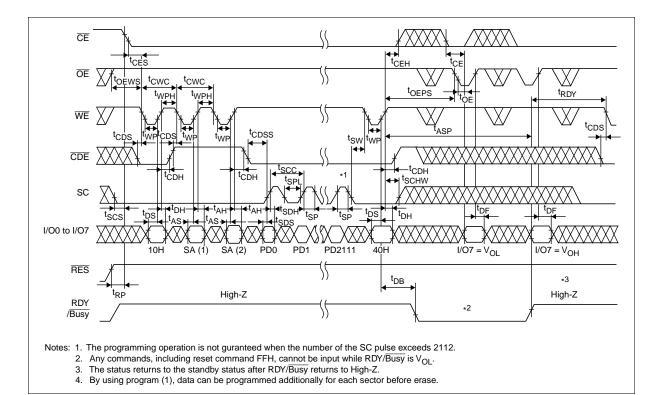

### Program (1), (4) (Without CA)

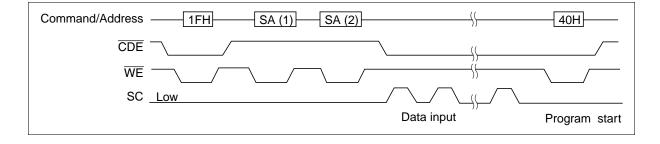

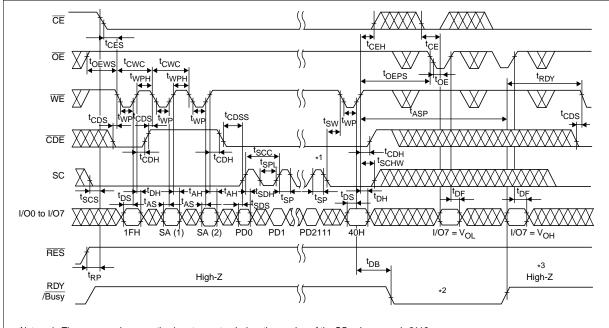

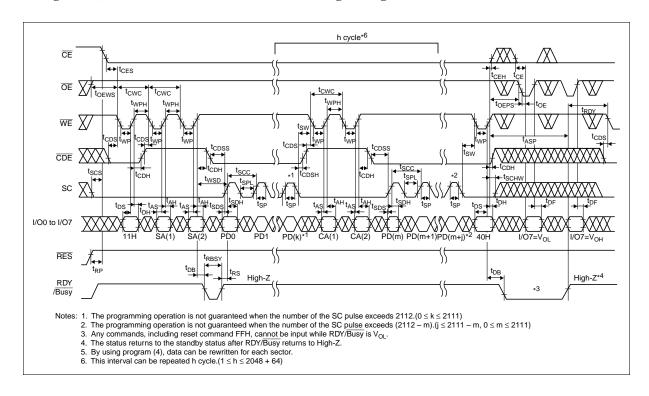

### Program (2)

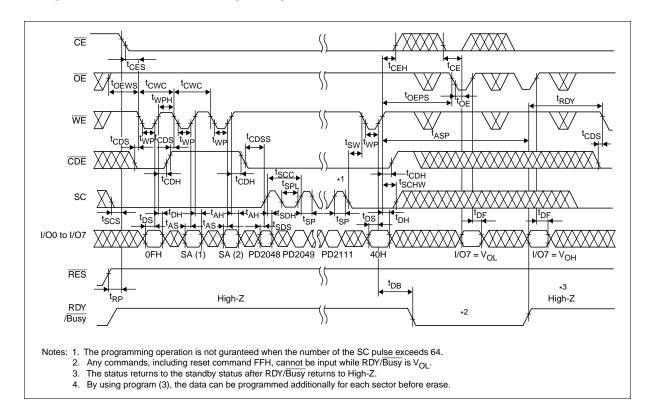

### Program (3)

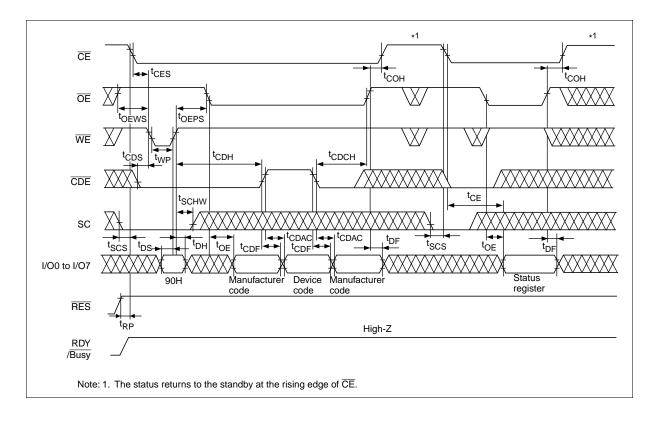

#### **ID Read Mode**

### **Data Recovery Read Mode**

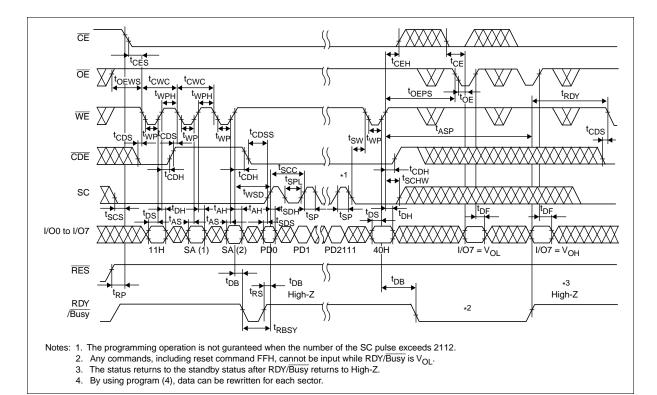

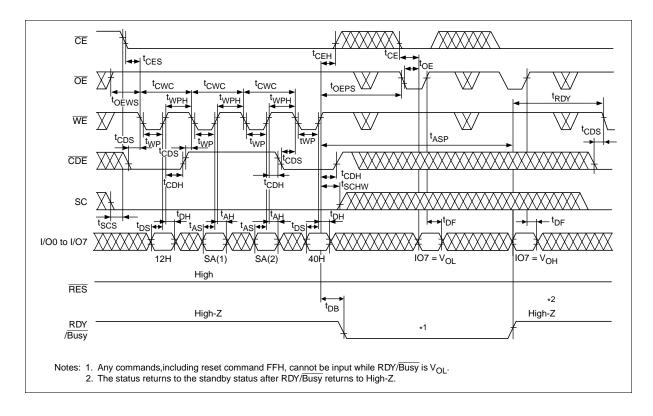

### **Data Recovery Write Mode**

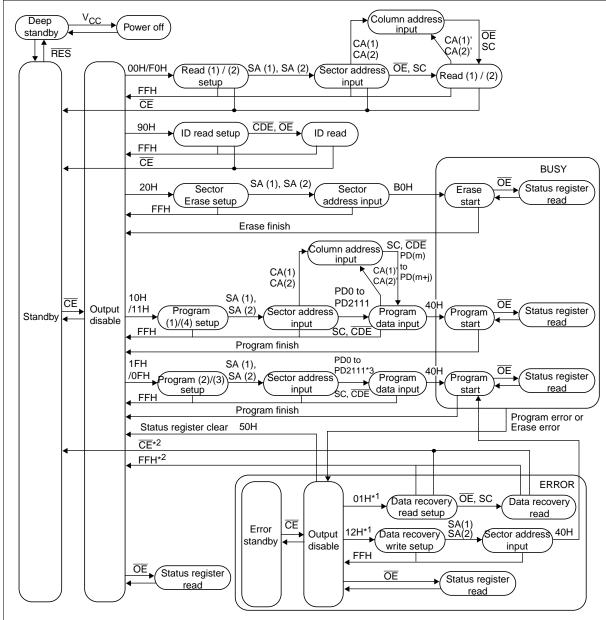

### **Status Transition**

Notes: 1. (01H)/(12H) Data recovery read/write can be used only for Program (1), (2), (3), (4) errors.

- 2. When reset is done by  $\overline{\text{CE}}$  or FFH, error status flag is cleared.

- 3. When Program (3) mode, input data is PD2048 to PD2111.

## **Absolute Maximum Ratings**

| Parameter                      | Symbol          | Value        | Unit | Notes |

|--------------------------------|-----------------|--------------|------|-------|

| V <sub>cc</sub> voltage        | V <sub>cc</sub> | -0.6 to +4.6 | V    | 1     |

| V <sub>ss</sub> voltage        | V <sub>ss</sub> | 0            | V    |       |

| All input and output voltages  | Vin, Vout       | -0.6 to +4.6 | V    | 1, 2  |

| Operating temperature range    | Topr            | 0 to +70     | °C   |       |

| Storage temperature range      | Tstg            | -65 to +125  | °C   | 3     |

| Storage temperature under bias | Tbias           | -10 to +80   | °C   |       |

Notes: 1. Relative to V<sub>ss</sub>.

- 2. Vin, Vout = -2.0 V for pulse width 20 ns.

- 3. Device storage temperature range before programming.

## **Capacitance** (Ta = 25°C, f = 1 MHz)

| Parameter          | Symbol | Min | Тур | Max | Unit | Test conditions |

|--------------------|--------|-----|-----|-----|------|-----------------|

| Input capacitance  | Cin    | _   | _   | 6   | pF   | Vin = 0 V       |

| Output capacitance | Cout   | _   | _   | 12  | pF   | Vout = 0 V      |

## **DC Characteristics** ( $V_{CC} = 2.7 \text{ V}$ to 3.6 V, Ta = 0 to $+70^{\circ}\text{C}$ )

| Parameter                                   | Symbol           | Min                   | Тур | Max                   | Unit | Test conditions                                                                         |

|---------------------------------------------|------------------|-----------------------|-----|-----------------------|------|-----------------------------------------------------------------------------------------|

| Input leakage current                       | I <sub>LI</sub>  | _                     | _   | 2                     | μΑ   | $Vin = V_{SS}$ to $V_{CC}$                                                              |

| Output leakage current                      | I <sub>LO</sub>  | _                     |     | 2                     | μΑ   | Vout = V <sub>SS</sub> to V <sub>CC</sub>                                               |

| Standby V <sub>cc</sub> current             | I <sub>SB1</sub> | _                     | 0.3 | 1                     | mA   | CE = V <sub>IH</sub>                                                                    |

|                                             | I <sub>SB2</sub> | _                     | 30  | 50                    | μΑ   | $\overline{CE} = V_{CC} \pm 0.2 \text{ V},$ $\overline{RES} = V_{CC} \pm 0.2 \text{ V}$ |

| Deep standby V <sub>cc</sub> current        | I <sub>SB3</sub> | _                     | 1   | 20                    | μΑ   | RES = V <sub>SS</sub> ± 0.2 V                                                           |

| Operating V <sub>cc</sub> current           | I <sub>CC1</sub> | _                     | 2   | 20                    | mA   | lout = 0 mA, f = 0.2 MHz                                                                |

|                                             | I <sub>CC2</sub> | _                     | 10  | 20                    | mA   | lout = 0 mA, f = 20 MHz                                                                 |

| Operating V <sub>cc</sub> current (Program) | I <sub>CC3</sub> | _                     | 20  | 40                    | mA   | In programming                                                                          |

| Operating V <sub>cc</sub> current (Erase)   | I <sub>CC4</sub> | _                     | 20  | 40                    | mA   | In erase                                                                                |

| Input voltage                               | $V_{\rm IL}$     | -0.3*1,2              | _   | 0.8                   | V    |                                                                                         |

|                                             | $V_{\text{IH}}$  | 2.0                   | _   | $V_{CC} + 0.3^{*3}$   | V    |                                                                                         |

| Input voltage (RES pin)                     | $V_{ILR}$        | -0.2                  | _   | 0.2                   | V    |                                                                                         |

|                                             | V <sub>IHR</sub> | V <sub>CC</sub> - 0.2 |     | V <sub>CC</sub> + 0.2 | V    |                                                                                         |

| Output voltage                              | $V_{OL}$         | _                     | _   | 0.4                   | V    | $I_{OL} = 2 \text{ mA}$                                                                 |

|                                             | $V_{OH}$         | 2.4                   | _   | _                     | V    | $I_{OH} = -2 \text{ mA}$                                                                |

Notes: 1.  $V_{IL} \min = -1.0 \text{ V}$  for pulse width 50 ns in the read operation.  $V_{IL} \min = -2.0 \text{ V}$  for pulse width 20 ns in the read operation.

- 2.  $V_{IL}$  min = -0.6 V for pulse width 20 ns in the erase/data programming operation.

- 3.  $V_{IH}$  max =  $V_{CC}$  + 1.5 V for pulse width 20 ns. If  $V_{IH}$  is over the specified maximum value, the operations are not guaranteed.

## **AC Characteristics** ( $V_{CC} = 2.7 \text{ V}$ to 3.6 V, Ta = 0 to $+70^{\circ}\text{C}$ )

### **Test Conditions**

• Input pulse levels: 0.4 V/2.4 V

• Input pulse levels for  $\overline{RES}$ : 0.2 V/V<sub>CC</sub> – 0.2 V

• Input rise and fall time: 5 ns

• Output load: 1 TTL gate + 100 pF (Including scope and jig.)

Reference levels for measuring timing: 0.8 V, 1.8 V

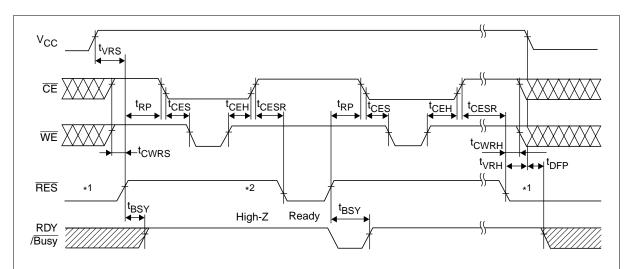

### Power on and off, Serial Read Mode

| Write cycle time         t <sub>COC</sub> 120         —         ns           Serial clock cycle time         t <sub>CCS</sub> 50         —         —         ns           CE setup time         t <sub>CSB</sub> 0         —         —         ns           CE hold time         t <sub>CSB</sub> 0         —         —         ns           Write pulse high time         t <sub>WPH</sub> 60         —         —         ns           Write pulse high time         t <sub>WPH</sub> 40         —         —         ns           Address setup time         t <sub>AS</sub> 50         —         —         ns           Address setup time         t <sub>AS</sub> 50         —         —         ns           Data setup time         t <sub>BS</sub> 50         —         —         ns           Data setup time         t <sub>BS</sub> 50         —         —         ns           SC to output delay         t <sub>BAC</sub> —         —         ns         GE = OE = V <sub>E</sub> , WE = V <sub>H</sub> DE setup time before read         t <sub>OER</sub> 100         —         ns         CE = OE = V <sub>E</sub> , WE = V <sub>H</sub> OE setup time before         t <sub>OER</sub> 0         —         —                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Parameter                          | Symbol            | Min | Тур | Max | Unit | Test conditions                                                  | Notes |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|-------------------|-----|-----|-----|------|------------------------------------------------------------------|-------|

| CE setup time         t <sub>CEH</sub> 0         —         ns           CE hold time         t <sub>CEH</sub> 0         —         ns           Write pulse time         t <sub>WP</sub> 60         —         ns           Write pulse high time         t <sub>WP</sub> 60         —         ns           Address setup time         t <sub>WB</sub> 50         —         ns           Address hold time         t <sub>AH</sub> 10         —         ns           Data setup time         t <sub>DS</sub> 50         —         ns           Data hold time         t <sub>OB</sub> 50         —         ns           SC to output delay         t <sub>SAC</sub> —         50         ns         CE = OE = V <sub>IL</sub> , WE = V <sub>IH</sub> SC to output delay         t <sub>SAC</sub> —         50         ns         CE = OE = V <sub>IL</sub> , WE = V <sub>IH</sub> OE setup time for SC         t <sub>CES</sub> 0         —         ns         CE = OE = V <sub>IL</sub> , WE = V <sub>IH</sub> OE setup time before read         t <sub>CER</sub> 100         —         ns         CE = OE = V <sub>IL</sub> , WE = V <sub>IH</sub> OE setup time before read         t <sub>CER</sub> 100         —         ns         CE = OE = V <sub>IL</sub> , WE = V <sub>IH</sub> OE setup tim                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Write cycle time                   | t <sub>cwc</sub>  | 120 | _   | _   | ns   |                                                                  |       |

| CE hold time         t <sub>CEH</sub> 0         —         ns           Write pulse time         t <sub>wp</sub> 60         —         ns         CE = V <sub>IL</sub> , OE = V <sub>IH</sub> Write pulse high time         t <sub>wp</sub> 60         —         ns         CE = V <sub>IL</sub> , OE = V <sub>IH</sub> Write pulse high time         t <sub>wp</sub> 60         —         ns           Address setup time         t <sub>wp</sub> 50         —         ns           Address hold time         t <sub>wp</sub> 10         —         ns           Data setup time         t <sub>os</sub> 50         —         ns           Data setup time         t <sub>os</sub> 50         —         ns           Data setup time         t <sub>os</sub> 50         —         ns           SC to output delay         t <sub>so</sub> —         —         ns           SC to output delay         t <sub>so</sub> —         —         ns           DE setup time before read         t <sub>oes</sub> 10         —         ns           DE setup time before read to output float         t <sub>oes</sub> 15         —         ns         CE = OE = V <sub>IL</sub> , WE = V <sub>IH</sub> DE high to output float         t <sub>oes</sub> —         —                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Serial clock cycle time            | t <sub>scc</sub>  | 50  | _   | _   | ns   |                                                                  |       |

| Write pulse time                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | CE setup time                      | t <sub>CES</sub>  | 0   | _   | _   | ns   |                                                                  |       |

| Write pulse high time         t <sub>WPH</sub> 40         —         ns           Address setup time         t <sub>AS</sub> 50         —         ns           Address hold time         t <sub>AH</sub> 10         —         ns           Data setup time         t <sub>DS</sub> 50         —         ns           Data hold time         t <sub>DH</sub> 10         —         ns           SC to output delay         t <sub>SAC</sub> —         —         50         ns           SC to output delay         t <sub>SAC</sub> —         —         ns           OE setup time for SC         t <sub>OES</sub> 0         —         —         ns           OE setup time before read         t <sub>OER</sub> 100         —         —         ns           OE setup time before read         t <sub>OER</sub> 100         —         —         ns           OE setup time before read         t <sub>OER</sub> 100         —         —         ns           OE setup time before read         t <sub>OER</sub> 0         —         —         ns           OE setup time before read         t <sub>OER</sub> 100         —         ns         CE = OE = V <sub>IL</sub> , WE = V <sub>IH</sub> SC to output hold         t <sub>SH</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | CE hold time                       | t <sub>CEH</sub>  | 0   | _   | _   | ns   |                                                                  |       |

| Address setup time         t <sub>AS</sub> 50         —         ns           Address hold time         t <sub>AH</sub> 10         —         —         ns           Data setup time         t <sub>DS</sub> 50         —         —         ns           Data hold time         t <sub>DH</sub> 10         —         —         ns           SC to output delay         t <sub>SAC</sub> —         —         50         ns         CE = OE = V <sub>L</sub> , WE = V <sub>H</sub> OE setup time for SC         t <sub>OES</sub> 0         —         —         ns           OE setup time before read         t <sub>OER</sub> 100         —         —         ns           OE setup time before read         t <sub>OER</sub> 100         —         —         ns           OE setup time before read         t <sub>OER</sub> 0         —         —         ns           OE setup time before read         t <sub>OER</sub> 100         —         —         ns           OE setup time before read         t <sub>OER</sub> 0         —         —         ns           SC to output hold         t <sub>SH</sub> 15         —         —         ns         CE = OE = V <sub>L</sub> , WE = V <sub>H</sub> DE high to output float         t <sub>DE</sub> <                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Write pulse time                   | t <sub>WP</sub>   | 60  | _   | _   | ns   | $\overline{CE} = V_{IL}, \overline{OE} = V_{IH}$                 |       |

| Address hold time         t <sub>M</sub> 10         —         ns           Data setup time         t <sub>DS</sub> 50         —         ns           Data hold time         t <sub>DH</sub> 10         —         ns           SC to output delay         t <sub>SAC</sub> —         —         50         ns         CE = OE = V <sub>IL</sub> , WE = V <sub>IH</sub> OE setup time for SC         t <sub>OES</sub> 0         —         —         ns           OE setup time before read         t <sub>OER</sub> 100         —         —         ns           OE setup time before command write         t <sub>OEWS</sub> 0         —         —         ns           SC to output hold         t <sub>SH</sub> 15         —         —         ns         CE = OE = V <sub>IL</sub> , WE = V <sub>IH</sub> 1           WE to SC delay time         t <sub>WSD</sub> 50         —         —         µs         2           RES to CE setup time         t <sub>RP</sub> 0.3         —         ms         S         2           RES to DE hold time         t <sub>SC</sub> 50         —         —         ns         S         SC pulse low time         t <sub>SC</sub> 20         —         ns         S         SC setup time for CE         t <sub>SC</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Write pulse high time              | t <sub>WPH</sub>  | 40  | _   | _   | ns   |                                                                  |       |

| $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Address setup time                 | t <sub>AS</sub>   | 50  | _   | _   | ns   |                                                                  |       |

| $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Address hold time                  | t <sub>AH</sub>   | 10  | _   | _   | ns   |                                                                  |       |

| $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Data setup time                    | t <sub>DS</sub>   | 50  | _   | _   | ns   |                                                                  |       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Data hold time                     | t <sub>DH</sub>   | 10  | _   | _   | ns   |                                                                  |       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | SC to output delay                 | t <sub>sac</sub>  | _   | _   | 50  | ns   | $\overline{CE} = \overline{OE} = V_{IL}, \overline{WE} = V_{IH}$ |       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | OE setup time for SC               | t <sub>OES</sub>  | 0   | _   | _   | ns   |                                                                  |       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | OE low to output low-Z             | t <sub>OEL</sub>  | 0   | _   | 40  | ns   |                                                                  |       |

| $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | OE setup time before read          | t <sub>OER</sub>  | 100 | _   | _   | ns   |                                                                  |       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | •                                  | t <sub>OEWS</sub> | 0   | _   | _   | ns   |                                                                  |       |

| $\begin{array}{ c c c c c c } \hline \text{WE to SC delay time} & t_{\text{WSD}} & 50 & & & \mu s \\ \hline \hline \text{RES to $\overline{\text{CE}}$ setup time} & t_{\text{RP}} & 0.3 & & & \text{ms} \\ \hline \text{SC to $\overline{\text{OE}}$ hold time} & t_{\text{SOH}} & 50 & & & \text{ns} \\ \hline \text{SC pulse width} & t_{\text{SP}} & 20 & & & \text{ns} \\ \hline \text{SC pulse low time} & t_{\text{SPL}} & 20 & & & \text{ns} \\ \hline \text{SC setup time for $\overline{\text{CE}}$} & t_{\text{SCS}} & 0 & & & \text{ns} \\ \hline \hline \text{CDE} \text{ setup time for $\overline{\text{WE}}$} & t_{\text{CDS}} & 0 & & & \text{ns} \\ \hline \hline \text{CDE} \text{ hold time for $\overline{\text{WE}}$} & t_{\text{CDH}} & 20 & & & \text{ns} \\ \hline \hline \text{CDE} \text{ setup time for $\overline{\text{RES}}$} & t_{\text{VRS}} & 1 & & & \mu s & \overline{\text{CE}} = \text{V}_{\text{IH}} \\ \hline \hline \text{RES} \text{ to $V_{\text{CC}}$ hold time} & t_{\text{VRH}} & 1 & & & \mu s & \overline{\text{CE}} = \text{V}_{\text{IH}} \\ \hline \hline \text{CE} \text{ setup time for $\overline{\text{RES}}$} & t_{\text{CESR}} & 1 & & & \mu s \\ \hline \text{RDY/Busy undefined for $V_{\text{CC}}$} & t_{\text{DFP}} & 0 & & & \text{ns} \\ \hline \hline \text{CE} \text{ pulse high time} & t_{\text{CPH}} & 200 & & & \text{ns} \\ \hline \hline \text{CE} \text{ pulse high time} & t_{\text{CPH}} & 200 & & & \text{ns} \\ \hline \hline \text{CE} \text{ pulse high time} & t_{\text{CPH}} & 200 & & & \text{ns} \\ \hline \hline \text{CE}, \overline{\text{WE}} \text{ setup time for $\overline{\text{RES}}$} & t_{\text{CWRS}} & 0 & & & \text{ns} \\ \hline \hline \text{CE}, \overline{\text{WE}} \text{ setup time for $\overline{\text{RES}}$} & t_{\text{CWRS}} & 0 & & & \text{ns} \\ \hline \hline \end{array}$ | SC to output hold                  | t <sub>SH</sub>   | 15  | _   | _   | ns   | $\overline{CE} = \overline{OE} = V_{IL}, \overline{WE} = V_{IH}$ |       |

| $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | OE high to output float            | t <sub>DF</sub>   | _   | _   | 40  | ns   | $\overline{CE} = V_{IL}, \overline{WE} = V_{IH}$                 | 1     |

| $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | WE to SC delay time                | t <sub>wsD</sub>  | 50  | _   | _   | μs   |                                                                  | 2     |

| $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | RES to CE setup time               | t <sub>RP</sub>   | 0.3 | _   | _   | ms   |                                                                  |       |

| $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | SC to OE hold time                 | t <sub>soh</sub>  | 50  | _   | _   | ns   |                                                                  |       |