## **Dual High Voltage Isolated MOSFET Driver**

#### **Ordering Information**

| Input to Output<br>Isolation Voltage | Package Option         |  |  |  |  |

|--------------------------------------|------------------------|--|--|--|--|

|                                      | 8-Pin Narrow Body SOIC |  |  |  |  |

| ±400V                                | HT0440LG               |  |  |  |  |

#### **Features**

- No external voltage supply required

- Dual isolated output drivers

- Option of internal or external clock

#### **Applications**

- Telecommunications

- Modems

- Solid state relays

- High side switches

- High end audio switches

- Avionics

- □ ATE

## **Absolute Maximum Ratings**<sup>1</sup>

| Input to Output Isolation Voltage, $V_{\rm ISO}$     | ±400V           |

|------------------------------------------------------|-----------------|

| Logic Input Voltage, V <sub>A</sub> , V <sub>B</sub> | -0.5 to +7.0V   |

| Operating Temperature                                | -40°C to +85°C  |

| Storage Temperature                                  | −55°C to +150°C |

| Soldering Temperature <sup>2</sup>                   | 300°C           |

|                                                      |                 |

#### Note:

- 1. All voltages are referenced to ground.

- 2. Distance of 1.6mm from case for 10 seconds.

For detailed circuit and application information, please refer to application note #AN-D26.

#### **General Description**

The Supertex HT0440 is a dual high voltage isolated driver utilizing Supertex's proprietary HVCMOS® technology. It is designed to drive discrete MOSFETs configured as bi-directional or unidirectional switches. It can drive N-channel MOSFETs as high side switches up to 400V. The HT0440 generates two independent DC isolated voltages to the outputs, V<sub>OUTA</sub> and V<sub>OUTB</sub> when logic inputs A and B are at logic high. The internal clock of the HT0440 can be disabled by applying an external clock signal to the CLK pin. This allows the power dissipation and AC characteristics to be tailored to meet specific needs. The CLK pin should be connected to ground when not in use. The HT0440 does not require any external power supplies. The internal supply voltage is supplied by either of the two logic inputs A or B when they are at logic high.

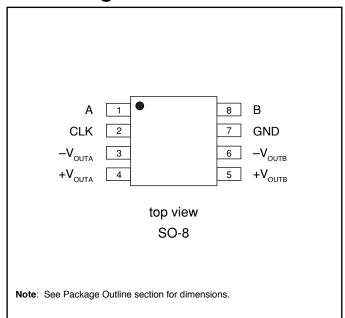

#### **Pin Configuration**

12/13/01

## **Electrical Characteristics**

(Over recommended operating conditions,  $T_A = 25^{\circ}C$  unless otherwise specified)

## **DC Characteristics**

| Symbol                                   | Parameter                          | Min  | Тур | Max | Unit | Conditions                                             |

|------------------------------------------|------------------------------------|------|-----|-----|------|--------------------------------------------------------|

| I <sub>IHA</sub> + I <sub>IHB</sub>      | Total logic high input current     |      |     | 300 | μΑ   | V <sub>A</sub> = 3.5V, V <sub>B</sub> = 3.5V, CLK = 0V |

|                                          |                                    |      |     | 500 | μΑ   | $V_A = 3.5V, V_B = 3.5V,$<br>CLK = 500KHz              |

|                                          |                                    |      |     | 2.0 | mA   | $V_A = 3.5V, V_B = 3.5V,$<br>CLK = 2.0MHz              |

|                                          |                                    |      |     | 1.0 | mA   | V <sub>A</sub> = 5.5V, V <sub>B</sub> = 5.5V, CLK = 0V |

|                                          |                                    |      |     | 2.0 | mA   | $V_A = 5.5V, V_B = 5.5V,$<br>CLK = 500KHz              |

| V <sub>OUTA</sub> ,<br>V <sub>OUTB</sub> | Output Voltage                     | 6.0  |     |     | V    | $V_A = 3.15V, V_B = 3.15V,$<br>CLK = 0V, no load       |

|                                          |                                    | 5.0  |     |     | V    | $V_A = 3.15V, V_B = 3.15V,$<br>CLK = 500KHz, no load   |

|                                          |                                    | 6.0  |     |     | V    | $V_A = 3.15V, V_B = 3.15V,$<br>CLK = 2.0MHz, no load   |

|                                          |                                    | 10.0 |     |     | V    | $V_A = 4.5V$ , $V_B = 4.5V$ , $CLK = 0V$ , no load     |

|                                          |                                    | 8.0  |     |     | V    | $V_A = 4.5V$ , $V_B = 4.5V$ , $CLK = 500KHz$ , no load |

| I <sub>ILA</sub>                         | Logic low input A current          |      |     | 10  | μΑ   | $V_A = 0.5V$ , $V_B = high$                            |

| I <sub>ILB</sub>                         | Logic low input B current          |      |     | 10  | μΑ   | $V_A = high, V_B = 0.5V$                               |

| I <sub>ILQ</sub>                         | Quiescent current                  |      |     | 10  | μΑ   | $V_A = 0.5V, V_B = 0.5V$                               |

| V <sub>ISO</sub>                         | Input to output isolation voltage  | ±400 |     |     | V    |                                                        |

| V <sub>CISO</sub>                        | Output to output isolation voltage | ±700 |     |     | V    |                                                        |

## **AC Characteristics**

| Symbol              | Parameter           | Min | Тур | Max | Unit | Conditions                          |

|---------------------|---------------------|-----|-----|-----|------|-------------------------------------|

| t <sub>d(ON)</sub>  | Turn on delay time  |     |     | 50  | μS   | See timing diagram and test circuit |

| t <sub>r</sub>      | Rise time           |     |     | 650 | μS   | CLK = 0V, C <sub>L</sub> = 600pF    |

| t <sub>d(OFF)</sub> | Turn off delay time |     |     | 150 | μS   |                                     |

| t <sub>f</sub>      | Fall time           |     |     | 3.0 | ms   |                                     |

## **Recommended Conditions**

| Symbol             | Parameter                | Min  | Тур | Max | Unit | Conditions |

|--------------------|--------------------------|------|-----|-----|------|------------|

| CLK                | External clock frequency | 0.5  |     | 2.0 | MHz  |            |

| V <sub>IHCLK</sub> | Clock input high voltage | 3.15 |     | 5.5 | V    |            |

| V <sub>ILCLK</sub> | Clock input low voltage  | 0    |     | 0.5 | V    |            |

| V <sub>IH</sub>    | Logic input high voltage | 3.15 |     | 5.5 | V    |            |

| V <sub>IL</sub>    | Logic input low voltage  | 0    |     | 0.5 | V    |            |

| T <sub>A</sub>     | Operating temperature    | -40  |     | +85 | °C   |            |

## **Truth Table**

| Α | В | CLK | V <sub>OUT</sub> A V <sub>OUT</sub> B |     | Internal Clock |

|---|---|-----|---------------------------------------|-----|----------------|

| 0 | 0 | 0   | Off                                   | Off | Off            |

| 0 |   | 0   | Off                                   | On  | On             |

|   | 0 | 0   | On                                    | Off | On             |

| 1 | 1 | 0   | On                                    | On  | On             |

| 0 | 0 | Clk | Off                                   | Off | Off            |

| 0 |   | Clk | Off                                   | On  | Off            |

|   | 0 | Clk | On                                    | Off | Off            |

| 1 | 1 | Clk | On                                    | On  | Off            |

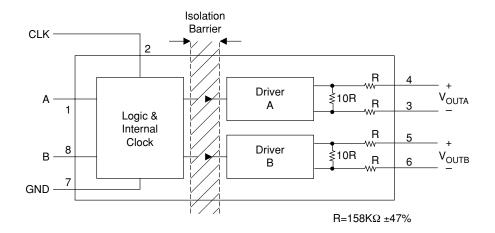

# **Block Diagram**

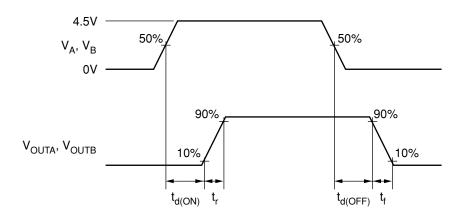

## **Timing Diagram**

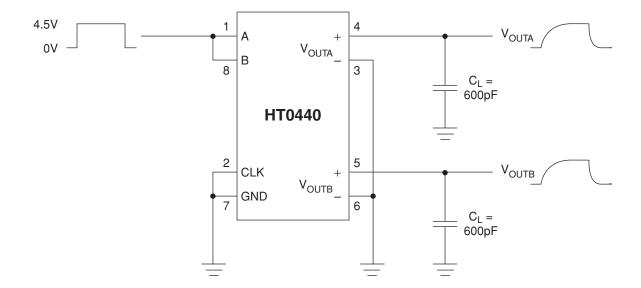

## **Test Circuit**