# HT16511 1/8 to 1/16 Duty VFD Controller

#### **Features**

- · Logic voltage: 5V

- High-voltage output: V<sub>DD</sub>-35V max.

- Multiple display (12-segment & 16-digit to 20-segment & 8-digit)

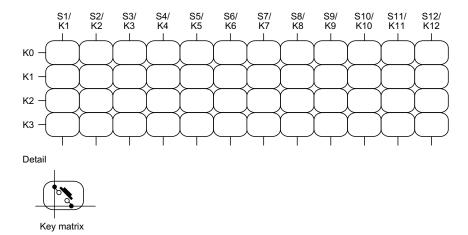

- 12×4 matrix key scanning

- 8 steps dimmer circuit

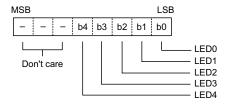

- 5 LED output ports (20mA max.)

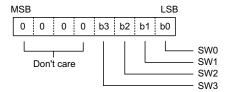

- 4-bit general purpose input port

- No external resistors necessary for driver output (provides PMOS open-drain and pull-low resistor output)

- Serial interface with MCU (CLK,  $\overline{\text{CS}}$ , DI, DO)

- 52-pin QFP package

## **Applications**

- · Consumer products panel function control

- · Industrial measuring instrument panel function control

- · Other similar application panel function control

#### **General Description**

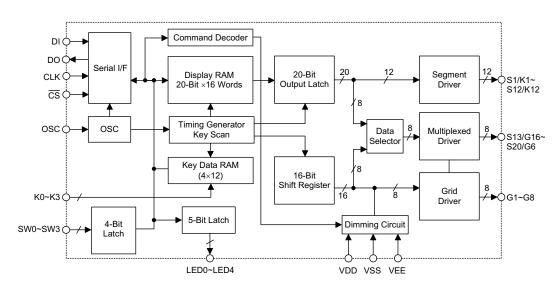

HT16511 is a VFD (Vacuum Fluorescent Display) controller/driver that is driven on a 1/8 to 1/16 duty factor. It consists of 12 segment output lines, 8 grid output lines, 8 segment/grid output drive lines, 5 LED output ports, a control circuit, a display memory, and a key scan circuit.

Serial data inputs to the HT16511 through a three-line serial interface. This VFD controller/driver is ideal as a peripheral device for an MCU.

# **Block Diagram**

Rev. 1.10 1 September 18, 2003

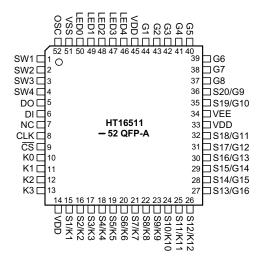

# **Pin Assignment**

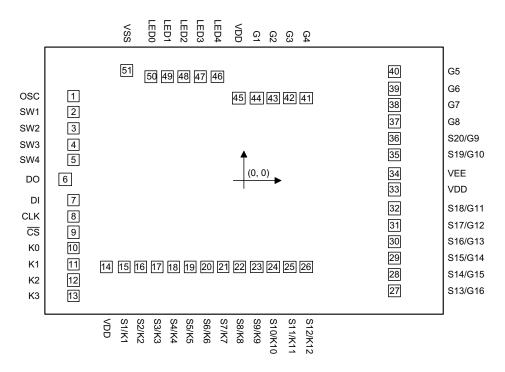

# **Pad Assignment**

Chip Size:  $103.5 \times 70.5 \text{ (mil)}^2$

Rev. 1.10 2 September 18, 2003

<sup>\*</sup> The IC substrate should be connected to VSS in the PCB layout artwork.

Pad Coordinates Unit: μm

| Pad No. | Х         | Y        | Pad No. | Х        | Υ        |

|---------|-----------|----------|---------|----------|----------|

| 1       | -1110.000 | 555.300  | 27      | 977.250  | -720.000 |

| 2       | -1110.000 | 450.300  | 28      | 977.250  | -612.000 |

| 3       | -1110.000 | 345.300  | 29      | 977.250  | -504.000 |

| 4       | -1110.000 | 240.300  | 30      | 977.250  | -396.000 |

| 5       | -1110.000 | 135.300  | 31      | 977.250  | -288.000 |

| 6       | -1165.900 | 9.800    | 32      | 977.250  | -180.000 |

| 7       | -1110.000 | -125.500 | 33      | 977.250  | -55.150  |

| 8       | -1110.000 | -230.500 | 34      | 977.250  | 49.850   |

| 9       | -1110.000 | -335.500 | 35      | 977.250  | 173.350  |

| 10      | -1110.000 | -440.500 | 36      | 977.250  | 281.350  |

| 11      | -1110.000 | -545.500 | 37      | 977.250  | 389.350  |

| 12      | -1110.000 | -650.500 | 38      | 977.250  | 497.350  |

| 13      | -1110.000 | -755.500 | 39      | 977.250  | 605.350  |

| 14      | -897.200  | -560.300 | 40      | 977.250  | 713.350  |

| 15      | -782.500  | -560.300 | 41      | 405.500  | 545.400  |

| 16      | -674.500  | -560.300 | 42      | 297.500  | 545.400  |

| 17      | -566.500  | -560.300 | 43      | 189.500  | 545.400  |

| 18      | -458.500  | -560.300 | 44      | 81.500   | 545.400  |

| 19      | -350.500  | -560.300 | 45      | -34.700  | 545.400  |

| 20      | -242.500  | -560.300 | 46      | -173.950 | 684.850  |

| 21      | -134.500  | -560.300 | 47      | -285.150 | 684.850  |

| 22      | -26.500   | -560.300 | 48      | -390.150 | 684.850  |

| 23      | 81.500    | -560.300 | 49      | -501.350 | 684.850  |

| 24      | 189.500   | -560.300 | 50      | -606.350 | 684.850  |

| 25      | 297.500   | -560.300 | 51      | -765.200 | 726.350  |

| 26      | 405.500   | -560.300 |         |          |          |

# **Pin Description**

| Pin No.         | Pin No. Pin Name I/O |   | Description                                                                                                                                                                                                                                                                                                                                                 |

|-----------------|----------------------|---|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1~4             | SW1~SW4              | ı | 4-bit general purpose input port                                                                                                                                                                                                                                                                                                                            |

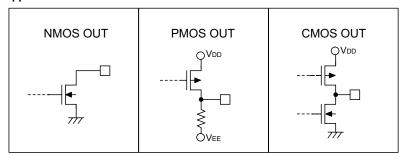

| 5               | DO                   | 0 | Output serial data at the falling edge of the shift clock, starting from low order bit. This is an NMOS open-drain output pin.                                                                                                                                                                                                                              |

| 6               | DI                   | ı | Input serial data at the rising edge of the shift clock, starting from the low order bit.                                                                                                                                                                                                                                                                   |

| 7               | NC                   | _ | No connection                                                                                                                                                                                                                                                                                                                                               |

| 8               | CLK                  | ı | Reads serial data at the rising edge, and outputs data at the falling edge.                                                                                                                                                                                                                                                                                 |

| 9               | <del>CS</del>        | ı | Initializes serial interface at the rising or falling edge of the HT16511. Then it waits to receive a command. Data input after $\overline{\text{CS}}$ has fallen is processed as a command. While command data is processed, current processing is stopped, and the serial interface is initialized. While $\overline{\text{CS}}$ is high, CLK is ignored. |

| 10~13           | K0~K3                | ı | Keying data input to these pins is latched at the end of the display cycle.                                                                                                                                                                                                                                                                                 |

| 14, 33, 45      | VDD                  | _ | Posistive power supply                                                                                                                                                                                                                                                                                                                                      |

| 15~26           | S1/K1~S12/K12        | 0 | Segment or key source output pins (dual function). This is PMOS open-drain and pull-low resistor output.                                                                                                                                                                                                                                                    |

| 27~32,<br>35~36 | S13/G16~S20/G9       | 0 | Segment or Grid driver output pins. These pins are selectable for segment or grid driving. This is PMOS open-drain and pull-low resistor output.                                                                                                                                                                                                            |

| 34              | VEE                  | _ | VFD power supply                                                                                                                                                                                                                                                                                                                                            |

| 37~44           | G8~G1                | 0 | Grid driver output pins (Grid only). This is PMOS open-drain and pull-low resistor output.                                                                                                                                                                                                                                                                  |

| 46~50           | LED4~LED0            | 0 | LED driver output ports. This is a CMOS output pin.                                                                                                                                                                                                                                                                                                         |

| 51              | VSS                  |   | Negative power supply, ground                                                                                                                                                                                                                                                                                                                               |

| 52              | osc                  | I | Connected to an external resistor or an RC oscillator circuit.                                                                                                                                                                                                                                                                                              |

# **Approximate Internal Connections**

# **Absolute Maximum Ratings**

| Supply VoltageV | $V_{\rm SS}$ =0.3V to $V_{\rm SS}$ +6.0V | Operating Temperature | 25°C to 75°C  |

|-----------------|------------------------------------------|-----------------------|---------------|

| Input VoltageV  | $V_{SS}$ =0.3V to $V_{DD}$ +0.3V         | Storage Temperature   | 50°C to 125°C |

Note: These are stress ratings only. Stresses exceeding the range specified under "Absolute Maximum Ratings" may cause substantial damage to the device. Functional operation of this device at other conditions beyond those listed in the specification is not implied and prolonged exposure to extreme conditions may affect device reliability.

# **D.C. Characteristics** Ta=25°C

|                   |                             |                            | Test Conditions                                      |                    | _    |                     |      |

|-------------------|-----------------------------|----------------------------|------------------------------------------------------|--------------------|------|---------------------|------|

| Symbol            | Parameter                   | V <sub>DD</sub> Conditions |                                                      | Min.               | Тур. | Max.                | Unit |

| V <sub>DD</sub>   | Logic Supply Voltage        | _                          | _                                                    | 4.5                | 5    | 5.5                 | V    |

| V <sub>EE</sub>   | VFD Supply Voltage          | _                          | _                                                    | 0                  | _    | V <sub>DD</sub> -35 | V    |

| fosc              | Oscillation Frequency       | 5V                         | R <sub>OSC</sub> =51kΩ                               | 350                | 500  | 650                 | kHz  |

| R <sub>PL</sub>   | Output Pull-low Resistor    | 5V                         | Driver output                                        | 50                 | 100  | 150                 | kΩ   |

| I <sub>DD</sub>   | Operating Current           | 5V                         | No load, VFD display off                             | _                  | _    | 5                   | mA   |

| l <sub>OL</sub>   | Driver Leakage Current      | 5V                         | V <sub>O</sub> =V <sub>DD</sub> -30V, VFD driver off | _                  | _    | -10                 | μА   |

| I <sub>OL1</sub>  | LED Sink Current            | 5V                         | V <sub>OL</sub> =1V, LED0~LED4                       | 20                 | _    | _                   | mA   |

| I <sub>OH1</sub>  | LED Source Current          | 5V                         | V <sub>OH</sub> =0.9V <sub>DD</sub> , LED0~LED4      | -1                 | _    | _                   | mA   |

| I <sub>OH21</sub> | Segment/Key Source Current  | 5V                         | V <sub>OH</sub> =V <sub>DD</sub> -2V, S1/K1~S12/K12  | -3                 | _    | _                   | mA   |

| I <sub>OH22</sub> | Segment/Grid Source Current | 5V                         | V <sub>OH</sub> =V <sub>DD</sub> -2V                 | -15                | _    | _                   | mA   |

| I <sub>OL3</sub>  | DO Sink Current             | 5V                         | V <sub>OL</sub> =0.4V                                | 4                  | _    | _                   | mA   |

| V <sub>IH</sub>   | "H" Input Voltage           | _                          | _                                                    | 0.7V <sub>DD</sub> | _    | V <sub>DD</sub>     | V    |

| V <sub>IL</sub>   | "L" Input Voltage           | _                          | _                                                    | 0                  | _    | 0.3V <sub>DD</sub>  | V    |

| V <sub>OH1</sub>  | High-level Output Voltage   | 5V                         | LED0~LED4, I <sub>OH1</sub> =-1mA                    | 0.9V <sub>DD</sub> | _    | V <sub>DD</sub>     | V    |

| V <sub>OL1</sub>  | Low-level Output Voltage    | 5V                         | LED0~LED4, I <sub>OL1</sub> =20mA                    | 0                  | _    | 1                   | V    |

| V <sub>OL2</sub>  | Low-level Output Voltage    | 5V                         | DO, I <sub>OL2</sub> =4mA                            | 0                  | _    | 0.4                 | V    |

Rev. 1.10 4 September 18, 2003

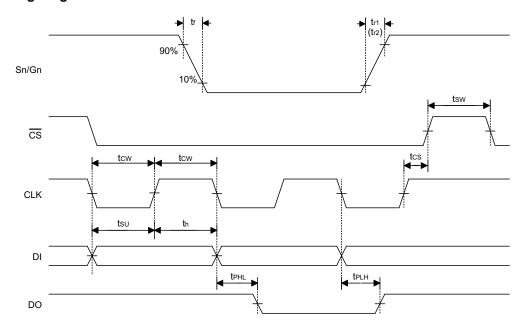

A.C. Characteristics Ta=25°C

| Symbol           | Parameter               | Test Conditions |                                     |      | Time | Max. | Unit  |

|------------------|-------------------------|-----------------|-------------------------------------|------|------|------|-------|

| Symbol           | Parameter               | $V_{DD}$        | Conditions                          | Min. | Тур. | wax. | UIIIL |

| t <sub>PHL</sub> | Drongation Daloy Time   | 5V              | CLK→DO                              |      | _    | 300  | ns    |

| t <sub>PLH</sub> | Propagation Delay Time  | 5V              | $C_L=15pF, R_L=10k\Omega$           | _    | _    | 100  | ns    |

| t <sub>r1</sub>  | Rise Time               |                 | C <sub>L</sub> =300pF, S0~S12       | _    | _    | 2    | μS    |

| t <sub>r2</sub>  |                         |                 | C <sub>L</sub> =300pF, G1~G16       | _    | _    | 0.5  | μS    |

| t <sub>f</sub>   | Fall Time               | 5V              | C <sub>L</sub> =300pF, Sn, Gn       |      | _    | 120  | μS    |

| t <sub>max</sub> | Maximum Clock Frequency | 5V              | Duty=50%                            | 1    | _    | _    | MHz   |

| Ci               | Input Capacitance       | 5V              | _                                   | _    | _    | 15   | pF    |

| t <sub>CW</sub>  | Clock Pulse Width       | 5V              | _                                   | 400  | _    | _    | ns    |

| t <sub>SW</sub>  | Strobe Pulse Width      | 5V              | _                                   | 1    | _    | _    | us    |

| t <sub>SU</sub>  | Data Setup Time         | 5V              | _                                   | 100  | _    | _    | ns    |

| t <sub>h</sub>   | Data Hold Time          | 5V              | _                                   | 100  | _    | _    | ns    |

| t <sub>CS</sub>  | Clock-Strobe Time       | 5V              | CLK rising edge to CS rising edge   | 1    | _    | _    | μS    |

| t <sub>W</sub>   | Wait Time               | 5V              | CLK rising edge to CLK falling edge | 1    | _    | _    | μS    |

# **Functional Description**

#### **Display RAM and Display Mode**

The static display RAM is organized into  $40\times8$  bits and stores the data transmitted from an external device to the HT16511 through a serial interface. The contents of the RAM are directly mapped to the contents of the VFD driver. Data in the RAM can be accessed through the data setting, address setting and display control commands. It is assigned addresses in 8-bit unit as follows:

SEG1 SEG4 SEG8 SEG12 SEG16 SEG20

| 00HL             | 00Ηυ         | 01HL             | <b>01Η</b> υ     | 02HL             | DIG1  |

|------------------|--------------|------------------|------------------|------------------|-------|

| 03HL             | <b>03H</b> υ | 04H∟             | <b>04Η</b> υ     | 05H∟             | DIG2  |

| 06HL             | <b>06Η</b> υ | 07HL             | 07Hυ             | 08HL             | DIG3  |

| 09HL             | <b>09H</b> ∪ | 0AHL             | 0AH∪             | 0BHL             | DIG4  |

| 0CH <sub>L</sub> | 0CH∪         | 0DHL             | 0DH∪             | 0EHL             | DIG5  |

| 0FH <sub>L</sub> | 0FH∪         | 10H∟             | 10Hυ             | 11H∟             | DIG6  |

| 12HL             | <b>12H</b> υ | 13HL             | 13H∪             | 14HL             | DIG7  |

| 15HL             | <b>15H</b> ∪ | 16HL             | 16H∪             | 17H∟             | DIG8  |

| 18HL             | 18H∪         | 19H∟             | <b>19H</b> ∪     | 1AHL             | DIG9  |

| 1BH <sub>L</sub> | 1BH∪         | 1CH <sub>L</sub> | 1CH <sub>∪</sub> | 1DH∟             | DIG10 |

| 1EH <sub>L</sub> | 1EHυ         | 1FH∟             | 1FH∪             | 20HL             | DIG11 |

| 21HL             | <b>21Η</b> υ | 22HL             | 22H∪             | 23HL             | DIG12 |

| 24HL             | 24H∪         | 25H∟             | <b>25H</b> ∪     | 26H∟             | DIG13 |

| 27HL             | 27H∪         | 28H∟             | <b>28H</b> ∪     | 29HL             | DIG14 |

| 2AH <sub>L</sub> | 2AH∪         | 2BHL             | 2BH∪             | 2CH <sub>L</sub> | DIG15 |

| 2DHL             | 2DH∪         | 2EH <sub>L</sub> | 2EHυ             | 2FHL             | DIG16 |

b0 b3b4 b7

XXHL XXHU

Lower Higher

4 bits 4 bits

Note: Only the lower 4 bits of the addresses assigned to SEG17 through SEG20 are valid, the higher 4 bits are ignored.

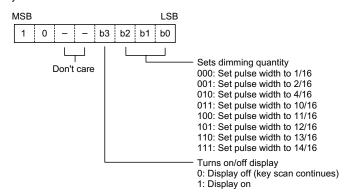

#### **Dimming Control**

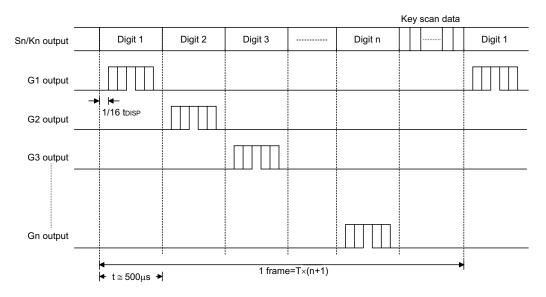

HT16511 provides 8-step dimmer function on display by controlling the 3-bit binary command code. The full pulse width of grid signal is divides into 16 uniform sections by PWM (pulse width modulation) technology.

The 16 uniform sections available form 8 steps dimmer via 3-bit binary code. The 8-step dimmer includes 1/16, 2/16, 4/16, 10/16, 11/16, 12/16, 13/16 and 14/16. The 1/16 pulse width indicates minimum lightness. The 14/16 pulse width represents maximum lightness (Refer to the display control command).

#### Key Matrix and Key-Input Data Storage RAM

The key matrix scans the series key states at each level of the key strobe signal (S1/K1~S12/K12) output of the HT16511. The key strobe signal outputs are time-multiplexed signals from S1/K1~S12/K12. The states of inputs K0~K3 are sampled by strobe signal S1/K1~S12/K12 and latched into the register.

The key matrix is made up of a 12×4 matrix, as shown below.

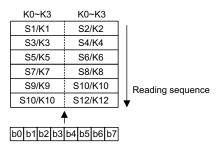

The data of each key is stored as illustrated below, and is read with the read command, starting from the least significant bit.

#### **LED Port**

The LED port belongs to the CMOS output configuration.

Data is written to the LED port with the write command, starting from the least port's least significant bit. In our application (see application circuits), the user adopts an internal NMOS device to a driver LED component by connecting VDD. When a bit of this port is 0, the corresponding LED lights; when the bit is 1, the LED turns off. The data of bits 6 through 8 are ignored.

#### **SW Data**

The HT16511 provides an extra 4-bit general input port. The SW data is provided with available binary code. The SW data is read with the read command, starting from the least significant bit. Bits 5 through 8 of the SW data are 0.

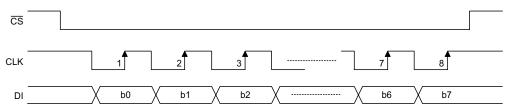

#### Commands

Commands set the display mode and status of the VFD driver

The first  $\frac{1}{CS}$  byte input to the HT16511 through the DI pin after the  $\frac{1}{CS}$  pin has fallen, is regarded as a command. If  $\frac{1}{CS}$  is set high while commands/data are transmitted, serial communication is initialized, and the commands/data being transmitted are not valid (however, the commands/data previously transmitted remains valid).

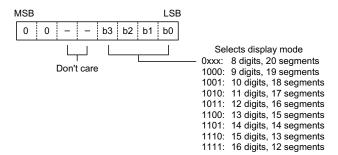

• Display mode setting commands

These commands initialize the HT16511 and select the number of segments and the number of grids (1/8~1/16 duty, 12 segments to 20 segments). When these commands are executed, the display is forcibly turned off, and key scanning is also stopped. To resume display, the display command "ON" must be executed. If the same mode is selected, nothing happens.

Note: Power-on status: 16-digit, 12 segment mode is selected.

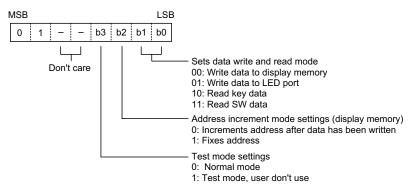

#### · Data setting commands

These commands set the data write and data read modes.

Note: power-on status: normal mode operation and address increment mode are set.

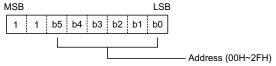

#### · Address setting commands

These commands set the address of the display memory.

If address 30H or higher is set, data is ignored until a valid address is set. Note: power-on status: the address is set to 00H.

#### · Display control commands

Note: power-on status: 1-16 pulse width is set and the display is turned off. Key scanning will be stopped during power

Rev. 1.10 7 September 18, 2003

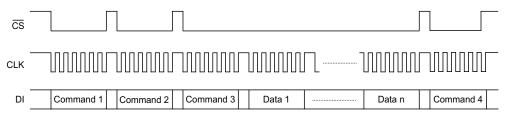

# **Timing Diagrams**

# **Key Scanning and Display Timing**

Note: One cycle of key scan consists of two frames, and data of 12×4 matrixes is stored in RAM.

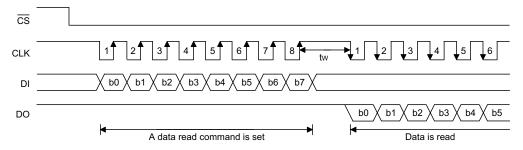

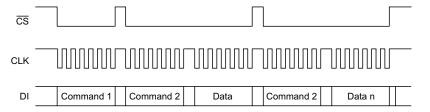

#### **Serial Communication Format**

• Reception (command/data write)

• Transmission (data read)

DO must be sure to connect an external pull-high resistor to this pin (1k $\Omega$  to 10k $\Omega$ ).

Note: When data is read, a wait time " $t_W$ " of  $1\mu s$  is necessary.

• Updating display memory by incrementing address

Note: Command 1: sets display mode

Command 2: sets data Command 3: sets address

Data 1 to n: transfers display data (48 bytes max.)

Command 4: controls display

· Updating specific addresses

9

Note: Command 1: sets data Command 2: sets address Data: display data

Rev. 1.10

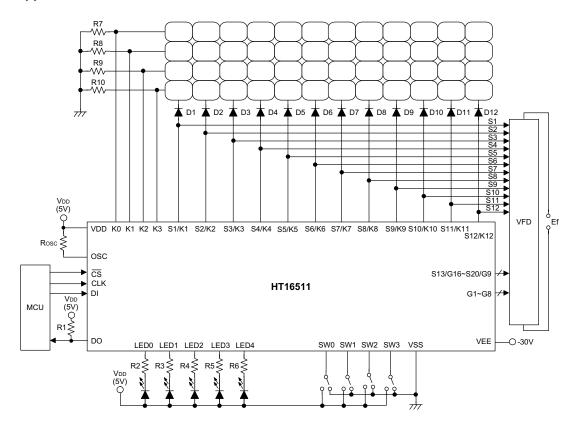

# **Application Circuits**

Note:  $R_{OSC}$ =51k $\Omega$  for oscillator resistor

R1=1~10k $\Omega$  for external pull-high resistor

R2~R6=750Ω~1.2kΩ

R7~R10=10k $\Omega$  for external pull-low resistor

D1~D12=1N4001

Ef=Filament voltage for VFD

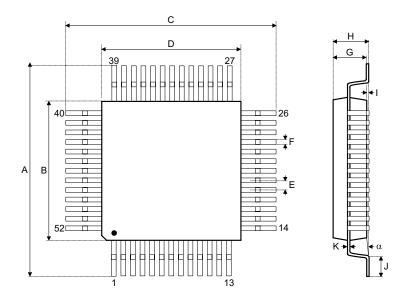

# **Package Information**

# 52-pin QFP (14×14) Outline Dimensions

| Symbol | Dimensions in mm |      |       |  |  |  |  |

|--------|------------------|------|-------|--|--|--|--|

|        | Min.             | Nom. | Max.  |  |  |  |  |

| Α      | 18.80            | _    | 19.20 |  |  |  |  |

| В      | 13.90            | _    | 14.10 |  |  |  |  |

| С      | 18.80            | _    | 19.20 |  |  |  |  |

| D      | 13.90            | _    | 14.10 |  |  |  |  |

| E      | _                | 0.65 | _     |  |  |  |  |

| F      | _                | 0.40 | _     |  |  |  |  |

| G      | 2.50             | _    | 3.10  |  |  |  |  |

| Н      | _                | _    | 3.40  |  |  |  |  |

| I      | _                | 0.10 | _     |  |  |  |  |

| J      | 0.73             | _    | 1.03  |  |  |  |  |

| K      | 0.10             | _    | 0.20  |  |  |  |  |

| α      | 0°               | _    | 7°    |  |  |  |  |

#### Holtek Semiconductor Inc. (Headquarters)

No.3, Creation Rd. II, Science Park, Hsinchu, Taiwan

Tel: 886-3-563-1999 Fax: 886-3-563-1189 http://www.holtek.com.tw

#### Holtek Semiconductor Inc. (Sales Office)

4F-2, No. 3-2, YuanQu St., Nankang Software Park, Taipei 115, Taiwan Tel: 886-2-2655-7070

Tel: 886-2-2655-7070 Fax: 886-2-2655-7373

Fax: 886-2-2655-7383 (International sales hotline)

# Holtek Semiconductor (Shanghai) Inc.

7th Floor, Building 2, No.889, Yi Shan Rd., Shanghai, China

Tel: 021-6485-5560 Fax: 021-6485-0313 http://www.holtek.com.cn

#### Holtek Semiconductor (Hong Kong) Ltd.

Block A, 3/F, Tin On Industrial Building, 7777-779 Cheung Sha Wan Rd., Kowloon, Hong Kong Tel: 852-2-745-8288

Tel: 852-2-745-8288 Fax: 852-2-742-8657

#### Holmate Semiconductor, Inc.

46712 Fremont Blvd., Fremont, CA 94538

Tel: 510-252-9880 Fax: 510-252-9885 http://www.holmate.com

#### Copyright © 2003 by HOLTEK SEMICONDUCTOR INC.

The information appearing in this Data Sheet is believed to be accurate at the time of publication. However, Holtek assumes no responsibility arising from the use of the specifications described. The applications mentioned herein are used solely for the purpose of illustration and Holtek makes no warranty or representation that such applications will be suitable without further modification, nor recommends the use of its products for application that may present a risk to human life due to malfunction or otherwise. Holtek's products are not authorized for use as critical components in life support devices or systems. Holtek reserves the right to alter its products without prior notification. For the most up-to-date information, please visit our web site at http://www.holtek.com.tw.

Rev. 1.10 12 September 18, 2003