# 16-BIT TRI-PORT BUS EXCHANGER

IDT73720/A

#### **FEATURES:**

- High-speed 16-bit bus exchange for interbus communication in the following environments:

- Multi-way interleaving memory

- Multiplexed address and data busses

- Direct interface to R3051 family RISChipSet™

- R3051<sup>™</sup> family of integrated RISController<sup>™</sup> CPUs

- R3721 DRAM controller

- · Data path for read and write operations

- Low noise 12mA TTL level outputs

- · Bidirectional 3-bus architecture: X, Y, Z

- One CPU bus: X

- Two (interleaved or banked) memory busses:Y & Z

- Each bus can be independently latched

- · Byte control on all three busses

- Source terminated outputs for low noise and undershoot control

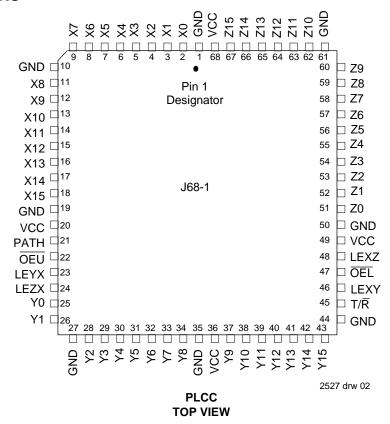

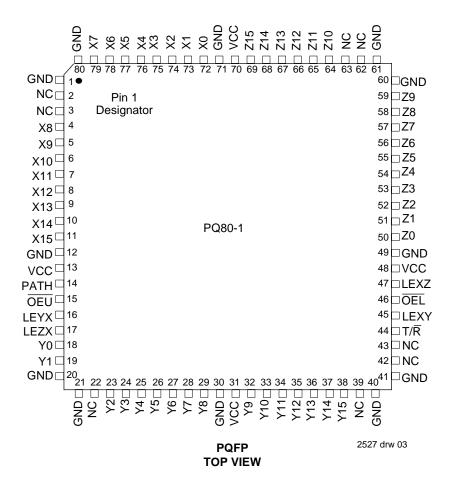

- 68-pin PLCC and 80-pin PQFP package

- · High-performance CMOS technology.

#### **DESCRIPTION:**

The IDT73720/A Bus Exchanger is a high speed 16-bit bus exchange device intended for inter-bus communication in interleaved memory systems and high performance multiplexed address and data busses.

The Bus Exchanger is responsible for interfacing between the CPU A/D bus (CPU address/data bus) and multiple memory data busses.

The 73720/A uses a three bus architecture (X, Y, Z), with control signals suitable for simple transfer between the CPU bus (X) and either memory bus (Y or Z). The Bus Exchanger features independent read and write latches for each memory bus, thus supporting a variety of memory strategies. All three ports support byte enable to independently enable upper and lower bytes.

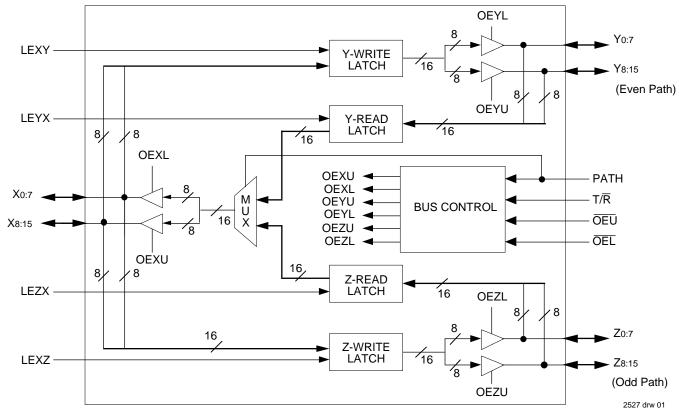

#### **FUNCTIONAL BLOCK DIAGRAM**

NOTE:

Figure 1. 73720 Block Diagram

1. Logic equations for bus control:

$OEXU = T/R^*$ .  $\overline{OEU^*}$ ;  $OEXL = T/R^*$ .  $\overline{OEL^*}$ ; OEYU = T/R. PATH.  $\overline{OEU^*}$ OEYL = T/R. PATH.  $\overline{OEL^*}$ ; OEZU = T/R. PATH\*.  $\overline{OEU^*}$ ; OEZL = T/R. PATH\*.  $\overline{OEL^*}$

RISChipSet, RISController, R305x, R3051, R3052 are trademarks and the IDT logo is a registered trademark of Integrated Device Technology, Inc.

#### **PIN CONFIGURATIONS**

#### **PIN DESCRIPTION**

| Signal  | I/O | Description                                                                                                                                                                                      |  |  |  |  |  |

|---------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| X(0:15) | I/O | Bidirectional Data Port X. Usually connected to the CPU's A/D (Address/Data) bus.                                                                                                                |  |  |  |  |  |

| Y(0:15) | I/O | Bidirectional Data port Y. Connected to the even path or even bank of memory.                                                                                                                    |  |  |  |  |  |

| Z(0:15) | I/O | Bidirectional Data port Z. Connected to the odd path or odd bank of memory.                                                                                                                      |  |  |  |  |  |

| LEXY    | I   | Latch Enable input for Y-Write Latch. The Y-Write Latch is open when LEXY is HIGH. Data from the X-port (CPU) is latched on the HIGH-to-LOW transition of LEXY                                   |  |  |  |  |  |

| LEXZ    | I   | Latch Enable input for Z-Write Latch. The Z-Write Latch is open when LEXZ is HIGH. Data from the X-port (CPU) is latched on the HIGH-to-LOW transition of LEXZ.                                  |  |  |  |  |  |

| LEYX    | I   | Latch Enable input for the Y-Read Latch. The Y-Read Latch is open when LEYX is HIGH. Data from the even path Y is latched on the HIGH-to-LOW transition of LEYX.                                 |  |  |  |  |  |

| LEZX    | I   | Latch Enable input for the Z-Read Latch. The Z-Read Latch is open when LEZX is HIGH. Data from the odd path Z is latched on the HIGH-to-LOW transition of LEZX                                   |  |  |  |  |  |

| PATH    | I   | Even/Odd Path Selection. When high, PATH enables data transfer between the X-Port and the Y-port (even path). When LOW, PATH enables data transfer between the X-Port and the Z-Port (odd path). |  |  |  |  |  |

| T/R     | I   | Transmit/Receive Data. When high, Port X is an input Port and either Port Y or Z is an output Port. When LOW, Port X is an output Port while Ports Y & Z are input Ports                         |  |  |  |  |  |

| ŌĒŪ     | I   | Output Enable for Upper byte. When LOW, the Upper byte of data is transferred to the port specified by PATH in the direction specified by $T/\overline{R}$ .                                     |  |  |  |  |  |

| OEL     | I   | Output Enable for Lower byte. When LOW, the Lower byte of data is transferred to the port specified by PATH in the direction specified by $T/\overline{R}$ .                                     |  |  |  |  |  |

2527 tbl 02

# ABSOLUTE MAXIMUM RATINGS(1)

| Symbol | Rating                               | Com'l.       | Mil.         | Unit |

|--------|--------------------------------------|--------------|--------------|------|

| VTERM  | Terminal Voltage with Respect to GND | -0.5 to +7.0 | -0.5 to +7.0 | ٧    |

| ТА     | Operating<br>Temperature             | 0 to +70     | -55 to +125  | Ô    |

| TBIAS  | Temperature<br>Under Bias            | -55 to +125  | –65 to +135  | °C   |

| Тѕтс   | Storage<br>Temperature               | -55 to +125  | -65 to +125  | °C   |

| Рт     | Power<br>Dissipation                 | 1.0          | 1.0          | W    |

| lout   | DC Output<br>Current                 | 50           | 50           | mA   |

#### NOTE:

2527 tbl (

Stresses greater than those listed under ABSOLUTE MAXIMUM RATINGS may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

# **CAPACITANCE** (TA = +25°C, F = 1.0MHz)

| Symb | ool                     | Parameter <sup>(1)</sup> | Conditions | Max. | Unit |

|------|-------------------------|--------------------------|------------|------|------|

| CIN  |                         | Input Capacitance        | VIN = 0V   | 8    | рF   |

| Cou  | Cout Output Capacitance |                          | Vout = 0V  | 12   | pF   |

#### NOTE:

2527 tbl 04

#### **TRUTH TABLE**

| Path | T/R | ŌĒŪ | ŌĒĹ | Functionality                                     |

|------|-----|-----|-----|---------------------------------------------------|

| L    | L   | L   | L   | Z→X (16-bits)–Read Z <sup>(1)</sup>               |

| L    | Н   | L   | L   | $X\rightarrow Z$ (16 bits)–Write $Z^{(1)}$        |

| Н    | L   | L   | L   | Y→X (16-bits)–Read Y <sup>(2)</sup>               |

| Н    | Н   | L   | L   | $X\rightarrow Y$ (16 bits)–Write $Y^{(2)}$        |

| Х    | Х   | Н   | Н   | All output buffers are disabled                   |

| Х    | Х   | Н   | L   | Transfer of lower 8 bits (0:7) as per PATH & T/R  |

| Х    | Х   | L   | Н   | Transfer of upper 8 bits (8:15) as per PATH & T/R |

#### NOTES:

2527 tbl 01

- 1. For Z→X and X→Z transfers, Y-port output buffers are tristated.

- 2. For Y  $\rightarrow$  X and X  $\rightarrow$  Y transfers, Z-port output buffers are tristated.

This parameter is guaranteed by device characterization, but is not production tested.

#### **ARCHITECTURE OVERVIEW**

The Bus Exchanger is used to service both read and write operations between the CPU and the dual memory busses. It includes independent data path elements for reads from and writes to each of the memory banks (Y and Z). Data flow control is managed by a simple set of control signals, analogous to a simple transceiver. In short, the Bus Exchanger allows bidirectional communication between ports X and Y and ports X and Z as illustrated in figure 1.

The data path elements for each port include:

**Read Latch**: Each of the memory ports Y and Z contains a transparent latch to capture the contents of the memory bus. Each latch features an independent latch enable.

**Write Latch**: Each memory port Y and Z contains an independent latch to capture data from the CPU bus during writes. Each memory port write latch features an independent latch enable, allowing write data to be directed to a specific memory port without disrupting the other memory port.

#### **Data Flow Control Signals**

**T/R** (Transmit/Receive). This signal controls the direction of data transfer. A transmit is used for CPU writes, and a receive is used for read operations.

OEU, OEL are the output enable control signals to select upper or lower bytes of all three ports.

**Path**: The path control signal is used to select between the even memory path Y and the odd memory path Z during read or write operations. Path selects the memory port to be connected to the CPU bus (X-port), and is independent of the latch enable signals. Thus, it is possible to transfer data from one memory port to the CPU bus (X) while capturing data from the other memory port.

#### **MEMORY READ OPERATIONS**

#### **Latch Mode**

In this mode the read operation consists of two stages. During the first stage, the data present at the memory port is captured by the read latch for that memory port. During a subsequent stage, data is brought from a selected memory port to the CPU A/D port X by using output enable control.

The read operation is selected by driving T/R LOW. The read is managed using the Path input to select the memory port (Y or Z); the LEYX/LEZX enable the data capture into the corresponding Read Latch.

In this way, memory interleaving can be performed. While data from one bank is output onto the CPU bus, data on the other bank is captured in the other memory port. In the next cycle, the Path input is changed, enabling the next data

element onto the CPU bus, while the first bank is presented with a new data element.

#### **Transparent Mode**

The Bus Exchanger may be used as a data transceiver by leaving all latches open or transparent.

#### **Memory Write Operations**

Memory write operations also consist of two distinct stages. During one stage, the write data is captured into the selected memory port write latch. During a later stage, the memory is presented on the memory port bus

The write operation is selected by driving  $T/\overline{R}$  HIGH. Writes are thus performed using the Path input to select the memory port (Y or Z). The LEXY/LEXZ capture data in the corresponding Write Latch.

Note that it is possible to utilize the bus exchanger's write resources as an additional write buffer, if desired; the CPU A/D bus can be freed up once the data has been captured by the Bus Exchanger.

#### **APPLICATIONS**

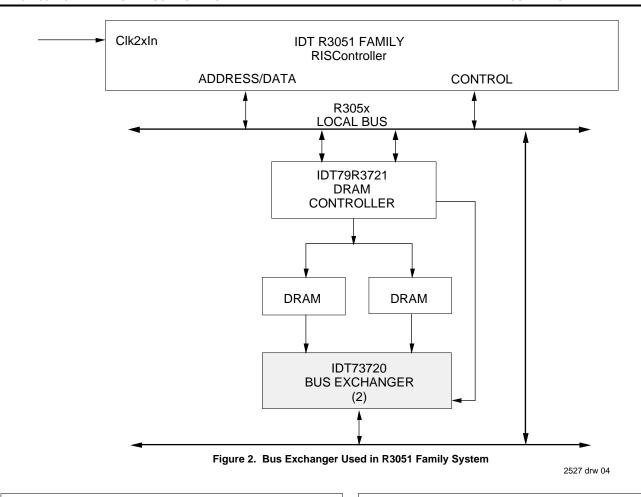

#### Use as Part of the R3051 Family ChipSet

Figure 2 shows the use of the Bus Exchanger in a typical R3051 based system.

In write transactions, the R3051 drives data on the CPU bus. The latch enables are held open through the entire write; thus, the bus exchanger is used like a transceiver. The appropriate LEXY/LEXZ signal is derived from ALE (Logic LOW- indicating that the processor is driving data) and the low order address bit. The rising edge of  $\overline{\text{Wr}}$  from the CPU, ends the write operation.

During read transactions, the memory system is responsible for generating the input control signals to cause data to be captured at the memory ports. The memory controller is also responsible for acknowledging back to the CPU that the data is available, and causing the appropriate path to be selected.

The R3721 DRAM controller for the R3051 family uses the transparent latches of the read ports. The R3721 directly controls the inputs of the bus exchanger, during both reads and writes. Consult the R3721 data sheet for more information on these control signals.

#### Use in a general 32-bit System

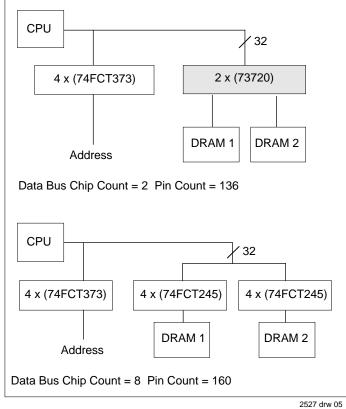

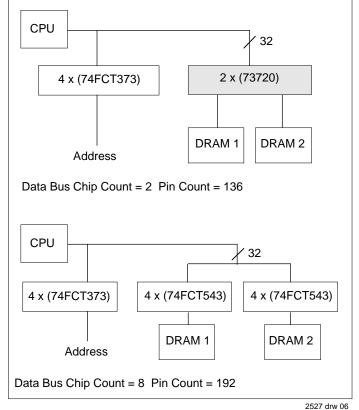

Figures 3 and 4 illustrate the use of the Bus Exchanger in a 32-bit microprocessor based system. Note the reduced pin count achieved with the Bus Exchanger.

11.5 4

Figure 3. CPU System with Transparent Data Path (2-way Interleaving)

Figure 4. CPU System with Latched Data Path (2-way Interleaving)

5

2527 tbl 05

# **DC ELECTRICAL CHARACTERISTICS** (Vcc = $5.0V \pm 5\%$ , TA = $0^{\circ}$ C to + $70^{\circ}$ C)

| Symbol             | Parameter Test Conditions <sup>(1)</sup>       |                                                                                                    | Min.                        | Typ. <sup>(2)</sup> | Max. | Unit         |            |

|--------------------|------------------------------------------------|----------------------------------------------------------------------------------------------------|-----------------------------|---------------------|------|--------------|------------|

| VIH                | Input HIGH Level                               |                                                                                                    |                             | 2.0                 | _    | _            | V          |

| VIL                | Input LOW Level                                |                                                                                                    |                             |                     | _    | 0.8          | V          |

| liH                | Input HIGH Current                             | Vcc = Max., ViH = 2.7V                                                                             | Inputs only                 | _                   | _    | 5.0          | μΑ         |

|                    |                                                |                                                                                                    | I/O pins                    |                     | _    | 5.0          |            |

| lıL                | Input LOW Current                              | Vcc = Max., VIL = 0.5V                                                                             | Inputs only                 | _                   | _    | -5.0         | μΑ         |

|                    |                                                |                                                                                                    | I/O pins                    | _                   | _    | -5.0         |            |

| Vıĸ                | Clamp Diode Voltage                            | VCC = Min., IN = -18mA                                                                             |                             |                     | -0.7 | -1.2         | V          |

| los <sup>(3)</sup> | Short Circuit Current                          | Vcc = Max., Vo = GND                                                                               |                             | -60                 | _    | -200         | mA         |

| Voн                | Output HIGH Voltage                            | VCC = Min., VIN = VIH or V                                                                         | $I_{IL}$ , $I_{OH} = -12mA$ | 2.4                 | 3.3  |              | V          |

| Vol                | Output LOW Voltage                             | VCC = Min., VIN = VIH or \                                                                         | /IL, IOL = 12mA             | _                   | 0.3  | 0.5          | V          |

| VH                 | Input Hysteresis<br>All inputs                 | Vcc = 5V                                                                                           |                             | _                   | 200  | _            | mV         |

| Icc                | Quiescent Power<br>Supply Current              | Vcc = Max.<br>Vin = GND or Vcc                                                                     |                             | _                   | 0.2  | 1.5          | mA         |

| Δlcc               | Quiescent Power<br>Supply Current              | Vcc = Max.<br>$Vin = 3.4 V^{(4)}$                                                                  | _                           | 0.5                 | 2.0  | mA/<br>Input |            |

| ICCD               | Dynamic Power<br>Supply Current <sup>(5)</sup> | Vcc = Max. VIN = Vcc or GND Outputs Disabled  OE = Vcc One Input Toggling 50 % Duty Cycle          |                             | _                   | 0.25 | 0.5          | mA/<br>MHz |

| Ic                 | Total Power Supply<br>Current <sup>(6)</sup>   | Vcc = Max. Vin = Vcc or GND Outputs Disabled 50 % Duty Cycle  OE = Vcc fi = 10MHz One Bit Toggling |                             | _                   | 2.7  | 6.5          | mA         |

NOTES:

1. For conditions shown as max. or min., use appropriate Vcc value.

2. Typical values are at Vcc = 5.0V, +25°C ambient.

- 3. Not more than one output should be shorted at a time. Duration of the short circuit test should not exceed one second.

- 4. Per TTL driven input  $(V_{IN} = 3.4V)$ ; all other inputs at Vcc or GND.

- 5. This parameter is not directly testable, but is derived for use in Total Power Supply Calculations.

- 6. IC = IQUIESCENT + INPUTS + IDYNAMIC

$IC = ICC + \Delta ICC DHNT + ICCD (fCP/2 + fiNi)$

Icc = Quiescent Current

$\Delta$ Icc = Power Supply Current for a TTL High Input (VIN = 3.4V)

DH = Duty Cycle for TTL Inputs High

NT = Number of TTL Inputs at DH

ICCD = Dynamic Current Caused by an Input Transition Pair (HLH or LHL)

fcp = Clock Frequency for Register Devices (Zero for Non-Register Devices)

fi = Input Frequency

Ni = Number of Inputs at fi

All currents are in milliamps and all frequencies are in megaherz.

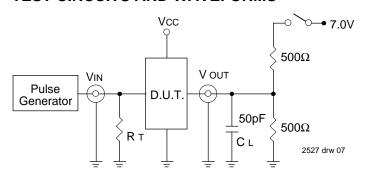

### **AC TEST CONDITIONS**

| Input Pulse Levels            | GND to 3.0V  |  |  |  |

|-------------------------------|--------------|--|--|--|

| Input Rise/Fall Times         | 5ns          |  |  |  |

| Input Timing Reference Levels | 1.5V         |  |  |  |

| Output Reference Levels       | 1.5V         |  |  |  |

| Output Load                   | See Figure 5 |  |  |  |

2527 tbl 06

# AC ELECTRICAL CHARACTERISTICS (Vcc = $5.0V \pm 5\%$ , TA = $0^{\circ}$ to + $70^{\circ}$ C)

|              |                                            |                              |                                | 737                 | 73720A |                     | 73720 |       |

|--------------|--------------------------------------------|------------------------------|--------------------------------|---------------------|--------|---------------------|-------|-------|

| Symbol       | Parameter                                  |                              | Test Conditions <sup>(1)</sup> | Min. <sup>(2)</sup> | Max.   | Min. <sup>(2)</sup> | Max.  | Units |

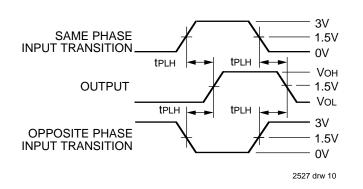

| tPLH<br>tPHL | X to Y & X to Z Latches enabled            |                              | CL = 50pF<br>RL = 500 Ohms     | 2.0                 | 6.0    | 2.0                 | 7.5   | ns    |

| tPLH<br>tPHL | Y to X & Z to X Latches enabled            |                              |                                | 2.0                 | 6.0    | 2.0                 | 7.5   | ns    |

| tPLH<br>tPHL | Latch Enable to Y & Z Port                 | LEXY to Y<br>LEXZ to Z       |                                | 2.0                 | 7.0    | 2.0                 | 8.5   | ns    |

| tPLH<br>tPHL | Latch Enable to X                          | LEYX to X<br>LEZX to X       |                                | 2.0                 | 7.0    | 2.0                 | 8.5   | ns    |

| tPLH<br>tPHL | Path to X Port Propagation Delay           |                              |                                | 2.0                 | 7.0    | 2.0                 | 8.5   | ns    |

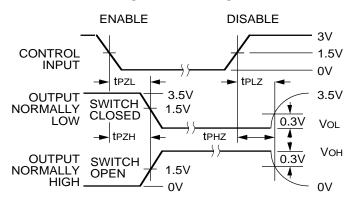

| tHZ<br>tLZ   | Y & Z Port Disable Time (T/R, PA           | TH, OEU, OEL) <sup>(3)</sup> |                                | 2.0                 | 8.5    | 2.0                 | 9.5   | ns    |

| tzh<br>tzl   | Y & Z Port Enable Time (T/R, PAT           | H, OEU, OEL)(3)              |                                | 2.0                 | 9.5    | 2.0                 | 10.5  | ns    |

| tHZ<br>tLZ   | X-Port DisableTime (T/R, OEU, O            | EL) <sup>(3)</sup>           |                                | 2.0                 | 8.5    | 2.0                 | 9.5   | ns    |

| tzh<br>tzl   | X-Port Enable Time (T/R, OEU, O            | EL) <sup>(3)</sup>           |                                | 2.0                 | 9.5    | 2.0                 | 10.5  | ns    |

| tsu          | Port to LE Set-up time                     |                              |                                | 2.0                 | _      | 2.0                 | _     | ns    |

| tH           | Port to LE Hold time                       |                              |                                | 1.5                 | _      | 1.5                 |       | ns    |

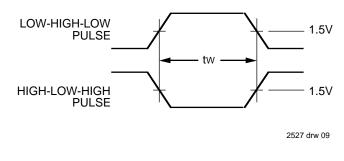

| tw           | LE Pulse Width, HIGH or LOW <sup>(2)</sup> |                              |                                | 3                   | _      | 4                   | _     | ns    |

#### NOTES:

- 1. All timings are referenced to 1.5 V.

- 2. Minimum Delay Times, Enable Times, Disable Times and Pulse Width are guaranteed by design, but not tested.

- 3. Bus turnaround times are guaranteed by design, but not tested. ( $T/\overline{R}$  enable/disable times).

# **TEST CIRCUITS AND WAVEFORMS**

Figure 5. Test Circuit for all outputs

#### **SWITCH POSITION**

| Test            | Switch |

|-----------------|--------|

| Disable LOW     | Closed |

| Enable LOW      |        |

| All Other Tests | Open   |

#### **DEFINITIONS:**

2527 tbl 08

2527 tbl 07

$\mathsf{CL} = \mathsf{Load}$  capacitance: includes jig and probe capacitance.

$\mathsf{RT}$  = Termination resistance: should be equal to  $\mathsf{ZOUT}$  of the Pulse Generator.

11.5 7

# SET-UP, HOLD AND RELEASE TIMES

# DATA INPUT TIMING INPUT ASYNCHRONOUS CONTROL PRESET CLEAR ETC. SYNCHRONOUS CONTROL SYNCHRONOUS CONTROL TIMING INPUT TIM

#### **PULSE WIDTH**

# **PROPAGATION DELAY**

#### **ENABLE AND DISABLE TIMES**

#### 2527 drw 11

#### NOTES:

2527 drw 08

- 1. Diagram shown for input Control Enable-LOW and input Control Disable-HIGH.

- 2. Pulse Generator for All Pulses: Rate  $\leq$  1.0 MHz; ZO  $\leq$  500; tF  $\leq$  2.5ns; tR  $\leq$  2.5ns.

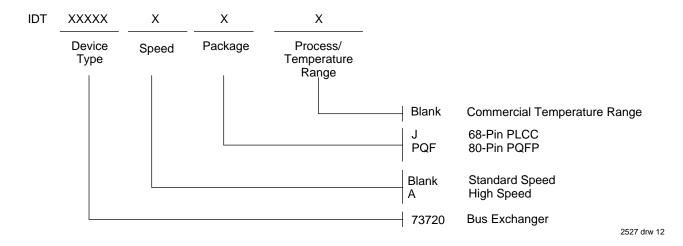

#### **ORDERING INFORMATION**