# **Quard Uart with 256-Byte FIFO**

IN16C1054

## 1. Functional Description

IN16C1054 is a quad UART(Universal Asynchronous Receiver/Transmitter) with 256-byte FIFO supporting maximum communication speed of 5.3Mbps. It offers flow control function by hardware or software and signal lines which can open or close the Tx/Rx input/output when communicating by RS-422 or RS-485. It can handle four interrupt signals (INT0, INT1, INT2 and INT3) with one global interrupt signal line (GINT) and offers a new 'Xoff re-transmit' function in addition to Xon any character.

UART can convert 8-bit parallel data to asynchronous serial data and vice versa. It can transmit 5 to 8-bit letters, program I/O interrupt trigger level and has 256-byte I/O data FIFO.

UART can generate any baud rate using clock and programmable divisor, transmit data with even, odd or no parity and 1, 1.5, 2 stop bit, and detect break, idle, framing error, FIFO overflow and parity error in input data.

UART has a software interface for modem controlling.

IN16C1054 offers TQFP80 and PLCC68 packages.

#### 2. Features

- 4 Channel UART

- 3.3V Operation

- 5V Tolerant Inputs

- Pin-to-pin Compatible with Industry Standard SB16C554 with Additional

- Enhancements

- Up to 5.3 Mbps Baud Rate (Up to 85 MHz Oscillator Input Clock)

- 256-byte Transmit FIFO

- 256-byte Receive FIFO with Error Flags

- Industrial Temperature Range (-20 ℃ to +85 ℃)

- Programmable and Selectable Transmit and Receive FIFO Trigger Levels for DMA

- · and Interrupt Generation

- Software (Xon/Xoff) / Hardware (RTS#/CTS#) Flow Control

- Programmable Xon/Xoff Characters

- Programmable Auto-RTS and Auto-CTS

- Global Interrupt Mask/Poll Control

- Optional Data Flow Resume by Xon Any Character Control

- Optional Data Flow Additional Halt by Xoff Retransmit Control

- RS-422 Point to Point/Multi-Drop Control

- RS-485 Echo/Non Echo Control

- DMA Signaling Capability for Both Received and Transmitted Data

- Software Selectable Baud Rate Generator

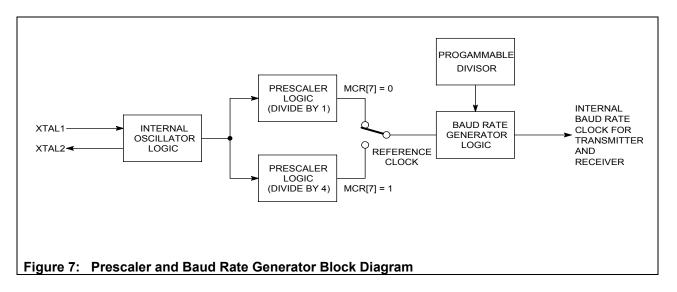

- Prescaler Provides Additional Divide-by-4 Function

- Fast Data Bus Access Time

- · Programmable Sleep Mode

- Programmable Serial Interface Characteristics

- 5, 6, 7, or 8-bit Characters

- Even, Odd, or No Parity Bit Generation and Detection

- 1, 1.5, or 2 Stop Bit Generation

- False Start Bit Detection

- · Line Break Generation and Detection

- Fully Prioritized Interrupt System Controls

- Modem Control Functions (RTS#, CTS#, DTR#, DSR#, DCD#, and RI#)

# 3. Ordering Information

**Table 1: Ordering Information**

| Part Number  | Package     | Operating Temperature Range | Device Status |

|--------------|-------------|-----------------------------|---------------|

| IN16C1054-TQ | 80-Pin TQFP | -20 ℃ to +85 ℃              | Active        |

| IN16C1054-PL | 68-Pin PLCC | -20 ℃ to +85 ℃              | Active        |

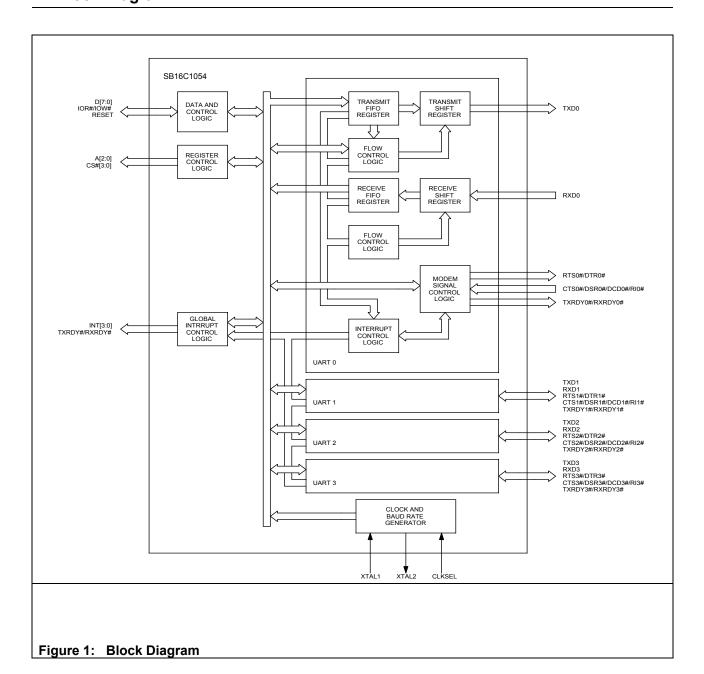

# 4. Block Diagram

## 5. Pin Configuration

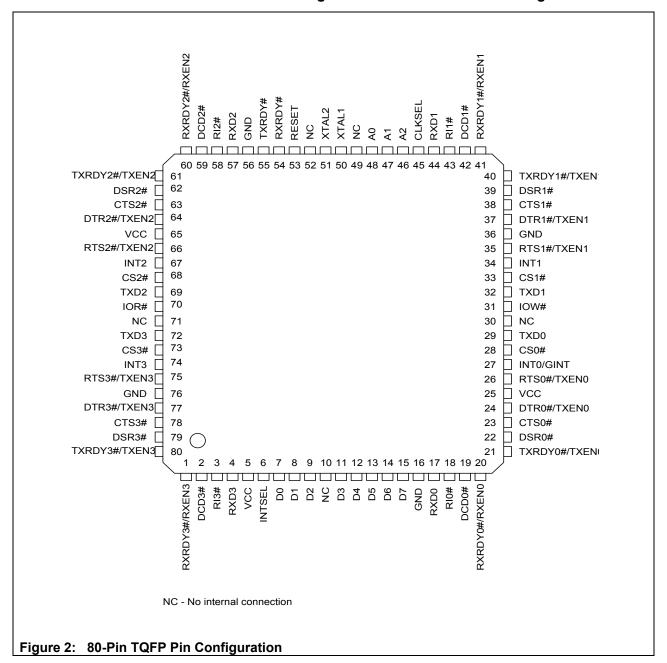

## 5.1 Pin Configuration for 80-Pin TQFP Package

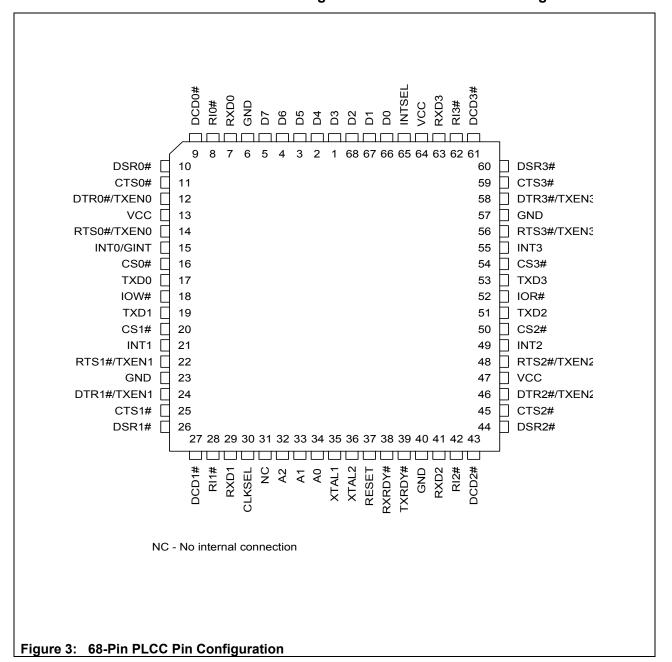

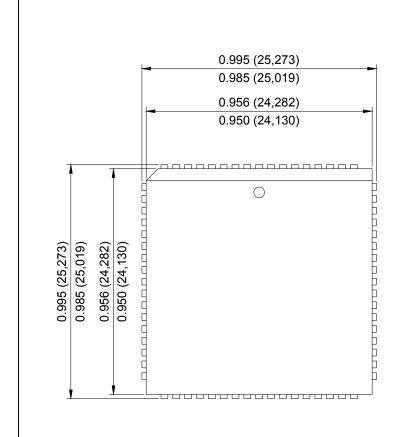

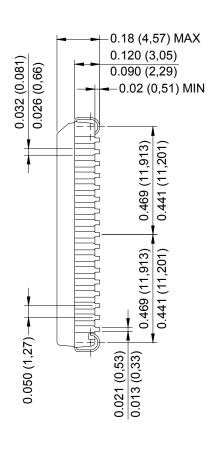

### 5.2 Pin Configuration for 68-Pin PLCC Package

# **5.3 Pin Description**

Table 2: Pin Description

| Name                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Data Bus Interface |        |         |     |                                                                 |  |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|--------|---------|-----|-----------------------------------------------------------------|--|--|--|

| No.   No. |                    |        | in Type |     | Description                                                     |  |  |  |

| A1         47         33         I         of the internal registers in UART channel 0-3 during a dark           A2         46         32         I         bus transaction.           D0         7         66         I/O         Data Bus Lines [7:0]. These pins are tri-state data bus for data transfer to or from the controlling CPU.           D1         8         67         I/O         data transfer to or from the controlling CPU.           D2         9         68         I/O         data transfer to or from the controlling CPU.           D3         11         1         I/O         data transfer to or from the controlling CPU.           D5         13         3         I/O         data transfer to or from the controlling CPU.           D6         14         4         I/O         data transfer to or from the controlling CPU.           D7         15         5         I/O         data transfer to or from the controlling CPU.           D8         10         I/O         data transfer to or from the controlling CPU.           D8         10         I/O         data transfer to or from the controlling CPU.           D8         10         I/O         data transfer to or from the controlling CPU.           D8         10         I/O         data transfer to or from the con                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                    | TQFP80 | PLCC68  |     |                                                                 |  |  |  |

| A2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | A0                 | 48     | 34      | 1   | Address Bus Lines [2:0]. These 3 address lines select one       |  |  |  |

| D0 7 66 I/O Data Bus Lines [7:0]. These pins are tri-state data bus for data transfer to or from the controlling CPU.  D2 9 68 I/O D3 11 1 I I/O D4 12 2 I/O D5 13 3 I/O D6 14 4 I/O D7 15 5 I/O  DR# 70 52 I Read Data (active low strobe). A valid low level on IOR# load the data of an internal register defined by address lin A [2:0] onto the UART data bus for access by an externa CPU.  IOW# 31 18 I Write Data (active low strobe). A valid low level on IOW# transfer the data from external CPU to an internal register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | A1                 | 47     | 33      | 1   | of the internal registers in UART channel 0-3 during a data     |  |  |  |

| D1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | A2                 | 46     | 32      | 1   | bus transaction.                                                |  |  |  |

| D2 9 68 I/O D3 11 1 1 I/O D4 12 2 I/O D5 13 3 I/O D6 14 4 I/O D7 15 5 I/O  IOR# 70 52 I Read Data (active low strobe). A valid low level on IOR# load the data of an internal register defined by address lin A [2:0] onto the UART data bus for access by an externa CPU.  IOW# 31 18 I Write Data (active low strobe). A valid low level on IOW# transfer the data from external CPU to an internal register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | D0                 | 7      | 66      | I/O | Data Bus Lines [7:0]. These pins are tri-state data bus for     |  |  |  |

| D3 D4 D4 D5 D5 D5 D5 D6 D6 D7 D7 D8 D8 D8 D9 D8 D9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | D1                 | 8      | 67      | I/O | data transfer to or from the controlling CPU.                   |  |  |  |

| D4 12 2 I/O D5 13 3 I/O D6 14 4 I/O D7 15 5 I/O  IOR# 70 52 I Read Data (active low strobe). A valid low level on IOR# load the data of an internal register defined by address lin A [2:0] onto the UART data bus for access by an externa CPU.  IOW# 31 18 I Write Data (active low strobe). A valid low level on IOW# transfer the data from external CPU to an internal register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | D2                 | 9      | 68      | I/O |                                                                 |  |  |  |

| D5 D6 D7 D7 D7 D8 D8 D8 D9 D8 D9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | D3                 | 11     | 1       | I/O |                                                                 |  |  |  |

| D6 D7 D8 D8 D9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | D4                 | 12     | 2       | I/O |                                                                 |  |  |  |

| D7 15 5 I/O  IOR# 70 52 I Read Data (active low strobe). A valid low level on IOR# load the data of an internal register defined by address lin A [2:0] onto the UART data bus for access by an externa CPU.  IOW# 31 18 I Write Data (active low strobe). A valid low level on IOW# transfer the data from external CPU to an internal register.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | D5                 | 13     | 3       | I/O |                                                                 |  |  |  |

| IOR# 70 52 I Read Data (active low strobe). A valid low level on IOR# load the data of an internal register defined by address lin A [2:0] onto the UART data bus for access by an externa CPU.  IOW# 31 I8 I Write Data (active low strobe). A valid low level on IOW# transfer the data from external CPU to an internal register.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | D6                 | 14     | 4       | I/O |                                                                 |  |  |  |

| load the data of an internal register defined by address ling A [2:0] onto the UART data bus for access by an externa CPU.  IOW# 31 18 I Write Data (active low strobe). A valid low level on IOW# transfer the data from external CPU to an internal register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | D7                 | 15     | 5       | I/O |                                                                 |  |  |  |

| A [2:0] onto the UART data bus for access by an externa CPU.  IOW# 31 18 I Write Data (active low strobe). A valid low level on IOW# transfer the data from external CPU to an internal register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | IOR#               | 70     | 52      | I   | Read Data (active low strobe). A valid low level on IOR# will   |  |  |  |

| IOW# 31 18 I Write Data (active low strobe). A valid low level on IOW# transfer the data from external CPU to an internal register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                    |        |         |     | load the data of an internal register defined by address lines  |  |  |  |

| IOW# 31 18 I Write Data (active low strobe). A valid low level on IOW# transfer the data from external CPU to an internal register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                    |        |         |     | A [2:0] onto the UART data bus for access by an external        |  |  |  |

| transfer the data from external CPU to an internal registe                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                    |        |         |     | CPU.                                                            |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | IOW#               | 31     | 18      | 1   | Write Data (active low strobe). A valid low level on IOW# will  |  |  |  |

| that is defined by address lines A [2:0]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                    |        |         |     | transfer the data from external CPU to an internal register     |  |  |  |

| that is defined by address lines A [2.0].                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                    |        |         |     | that is defined by address lines A [2:0].                       |  |  |  |

| CS0# 28 16 I Chip Select 0, 1, 2, and 3 (active low). These pins enable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | CS0#               | 28     | 16      | 1   | Chip Select 0, 1, 2, and 3 (active low). These pins enable      |  |  |  |

| CS1# 33 20 I data transfers between the external CPU and the UART to                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | CS1#               | 33     | 20      | 1   | data transfers between the external CPU and the UART for        |  |  |  |

| CS2# 68 50 I the respective channel.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | CS2#               | 68     | 50      | 1   | the respective channel.                                         |  |  |  |

| CS3# 73 54 I                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | CS3#               | 73     | 54      | 1   |                                                                 |  |  |  |

| INTO/GINT 27 15 O Interrupt 0/Global Interrupt, Interrupt 1, 2, and 3. These p                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | INT0/GINT          | 27     | 15      | 0   | Interrupt 0/Global Interrupt, Interrupt 1, 2, and 3. These pins |  |  |  |

| INT1 34 21 O provide individual channel interrupts or global interrupt.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | INT1               | 34     | 21      | 0   | provide individual channel interrupts or global interrupt.      |  |  |  |

| INT2 67 49 O INT0-3 are enabled when MCR[3] is set to '1' and AFR[4]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | INT2               | 67     | 49      | 0   | INT0-3 are enabled when MCR[3] is set to '1' and AFR[4] is      |  |  |  |

| INT3 74 55 O cleared to '0' (default state). But INT0 operates as GINT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | INT3               | 74     | 55      | 0   | cleared to '0' (default state). But INT0 operates as GINT and   |  |  |  |

| INT1-INT3 are disabled when AFR[4] is set to '1'.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                    |        |         |     | INT1-INT3 are disabled when AFR[4] is set to '1'.               |  |  |  |

| INT0-3's asserted state is active high, but GINT's asserted                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                    |        |         |     | INT0-3's asserted state is active high, but GINT's asserted     |  |  |  |

| state is determined by AFR[5]. GINT's asserted state is                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                    |        |         |     | state is determined by AFR[5]. GINT's asserted state is         |  |  |  |

| active high when AFR[5] is set to '1', and active low when                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                    |        |         |     | active high when AFR[5] is set to '1', and active low when      |  |  |  |

| AFR[5] is cleared to '0'.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                    |        |         |     | AFR[5] is cleared to '0'.                                       |  |  |  |

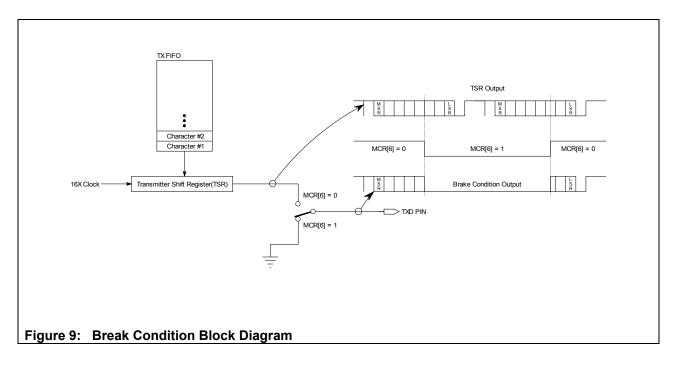

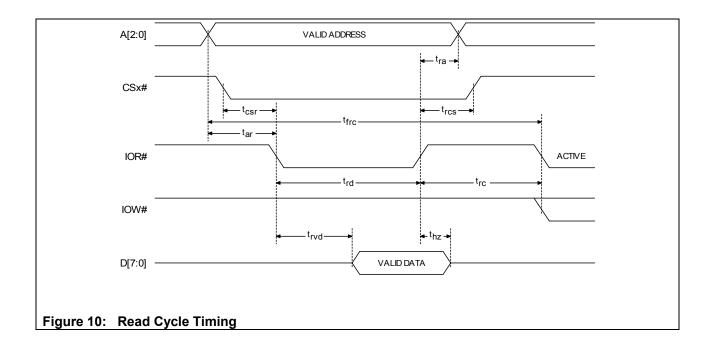

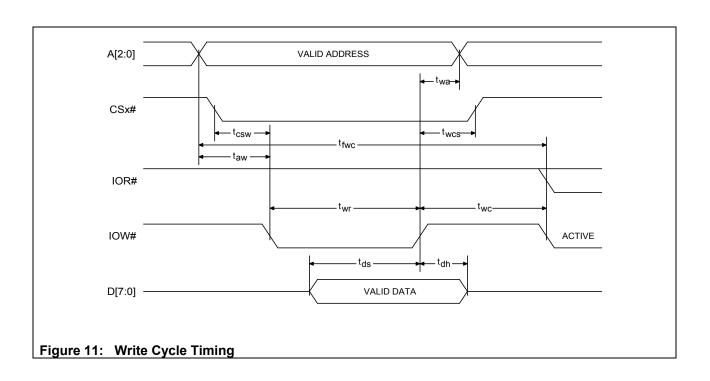

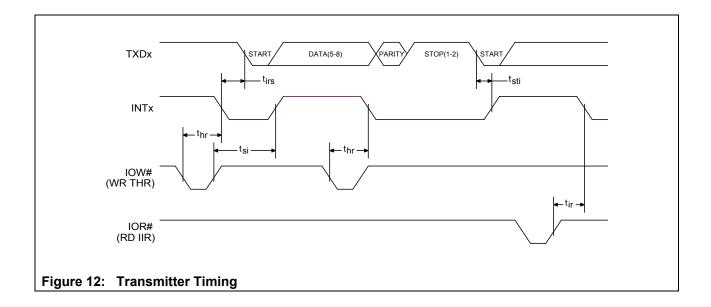

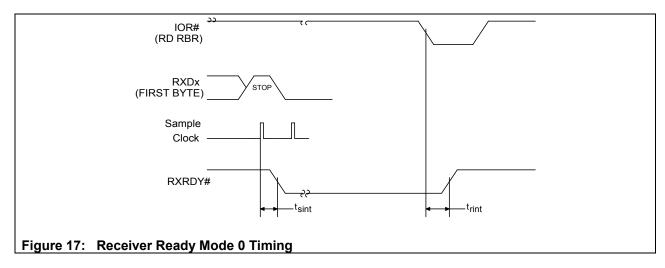

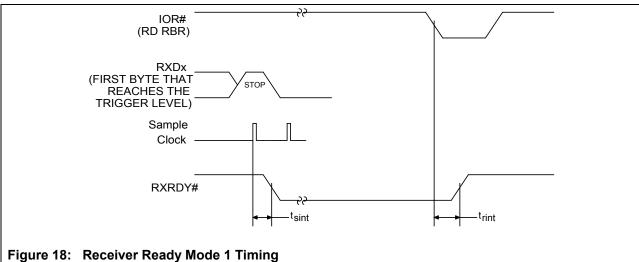

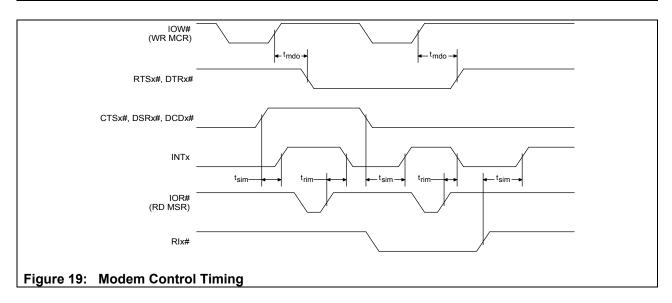

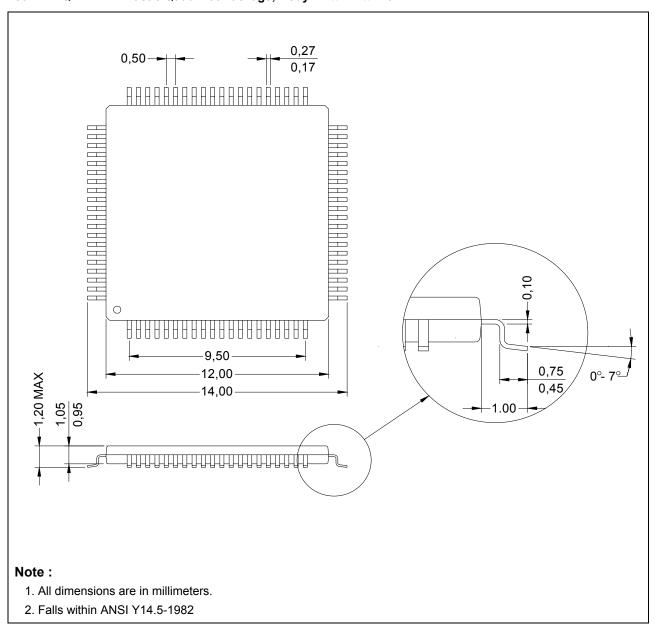

| INTSEL 6 65 I Interrupt Select. When INTSEL is left open or low state, t                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | INTSEL             | 6      | 65      | 1   | Interrupt Select. When INTSEL is left open or low state, the    |  |  |  |