# **Bluetooth<sup>®</sup> 4.2 Stereo Audio SoC**

### Features

- Qualified for Bluetooth v4.2 specifications

- Supports HFP 1.6, HSP 1.2, A2DP 1.3, SPP 1.2 and AVRCP 1.6

- Supports Bluetooth Low Energy (BLE) (FW dependent):

- Generic access service

- Device information service

- Proprietary services for data communication

- Apple Notification Center Service (ANCS)

- Supports high resolution up to 24-bit, 96 kHz audio data format

- I<sup>2</sup>S digital audio (IS2064 only), MIC, analog audio, AUX-In

- Supports microphone inputs: 2 (IS2062) and 1 (IS2064)

- UART, GPIOs, and LEDs

- Supports firmware field upgrade

- Battery charging

### **Baseband Features**

- 16 MHz main clock input

- Flash memory (8 Mbit)

- EEPROM (128 Kbit)

- Connects two hosts with HFP or A2DP profiles simultaneously, and SPP/BLE connection to one host

- Adaptive Frequency Hopping (AFH)

### **RF Features**

- Class 2 output power (+2 dBm typical)

- Receive sensitivity: -90 dBm (2 Mbps EDR)

- Supports Bluetooth (BDR/EDR/BLE) specifications (FW dependent)

- Combined Tx/Rx RF terminal simplifies external matching and reduces external antenna switches

- Tx/Rx RF switch for Class 2 or Class 3 applications

- Integrated synthesizer requires no external voltage-controlled oscillator (VCO), varactor diode, resonator, loop filter

- Crystal oscillator with built-in digital trimming compensates for temperature or process variations

### **DSP Audio Processing**

- · 32-bit DSP core

- Supports 64 kbps A-Law, μ-Law PCM format, Continuous Variable Slope Delta (CVSD) Modulation for Synchronous Connection-Oriented (SCO) channel operation

- Supports 8/16 kHz noise suppression

- Supports 8/16 kHz echo cancellation

- Packet loss concealment (PLC)

- Supports Serial Copy Management System (SCMS-T) content protection

### Audio Codec

- Sub-band Coding (SBC) and optional Advanced Audio Coding (AAC) decoding

- · 20-bit digital-to-analog (DAC) with 98 dB SNR

- 16-bit analog-to-digital (ADC) with 92 dB SNR

- Supports up to 24-bit, 96 kHz on I<sup>2</sup>S digital audio

### Peripherals

- High-speed Host Controller Interface (HCI)-UART (supports up to 921,600 bps)

- USB2.0 compatible interface for FW/EEPROM upgrade (IS2064)

- Built-in lithium-ion and lithium-polymer battery charger (up to 350 mA)

- Integrated 1.8V and 3V configurable switching regulator and low-dropout (LDO) regulator

- Built-in ADC for battery monitoring and voltage sensor and charger thermal protection

- Built-in undervoltage protection (UVP)

- LED drivers: 2 (IS2062) and 3 (IS2064)

### **Operating Condition**

- Operating voltage: 3.2V to 4.2V

- Temperature range: -20°C to +70°C

### Package

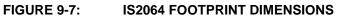

- IS2062: 7 mm x 7 mm, LGA-56 package

- IS2064: 8 mm x 8 mm, LGA-68 package

- 0.4 mm pitch

### Applications

- · Soundbars and subwoofers

- · Speaker phones

- · Headsets and headphones

### Description

The IS2062/64 is a Stereo Audio SoC qualified for Bluetooth 4.2 with Enhanced Data Rate (EDR). It integrates a 32-bit DSP co-processor and a codec which is dedicated for voice and audio applications. For voice applications, Continuously Variable Slope Delta (CVSD) encoding/decoding, 8K/16K noise reduction, and echo cancellation are implemented. For audio applications, Sub-band coding (SBC) and AAC Low-Complexity (AAC-LC) decoding functions are used.

The IS2062/64 SoC features a 20-bit audio DAC in addition to an I<sup>2</sup>S digital audio interface that supports up to 24-bit, 96 kHz data formats. System optimizations include an integrated battery voltage sensor, battery charger, switching regulator, and LDO.

### **Table of Contents**

| 1.0 Device Overview                       | 5    |

|-------------------------------------------|------|

| 2.0 Audio                                 |      |

| 3.0 Transceiver                           | . 19 |

| 1.0 Microcontroller                       | 21   |

| 5.0 Power management unit                 | . 23 |

| 5.0 Application Information               | . 25 |

| 7.0 Antenna Placement Rule                | . 35 |

| 3.0 Electrical Characteristics            | . 37 |

| 9.0 Package Information                   | . 45 |

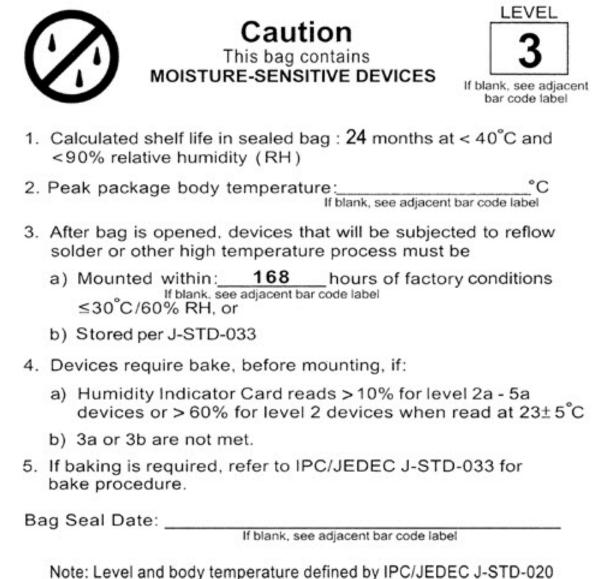

| 10.0 Reflow Profile and Storage Condition | . 53 |

| 11.0 Ordering Information                 |      |

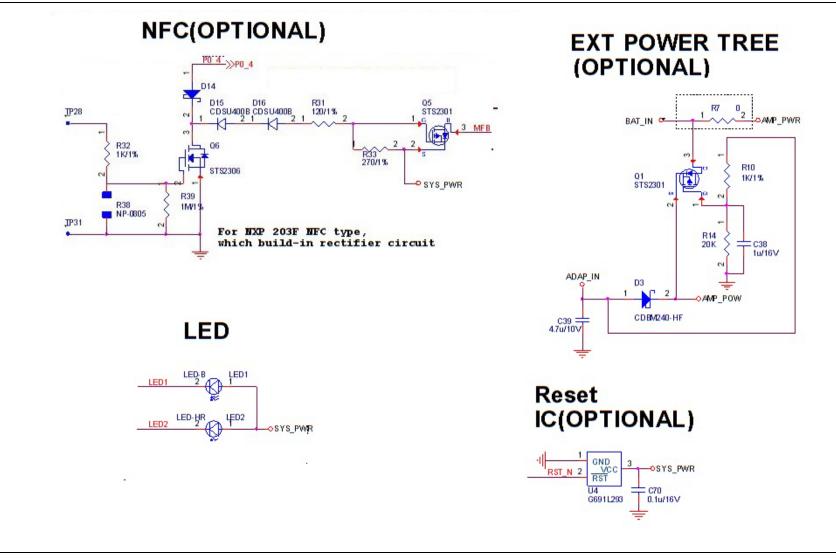

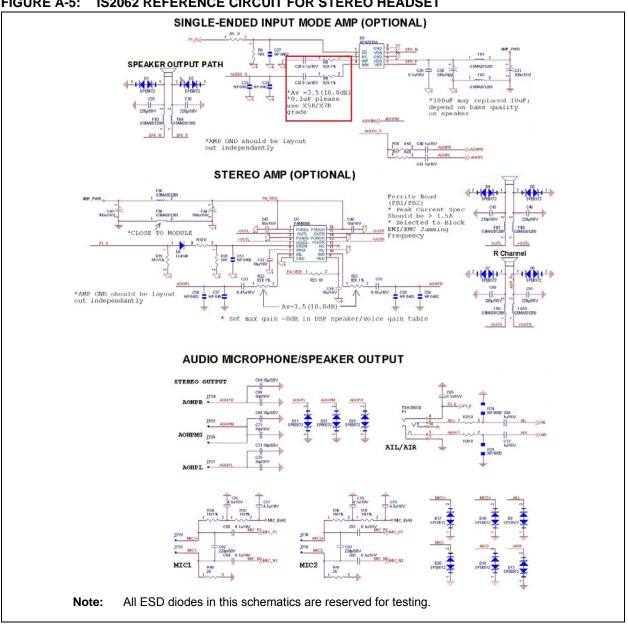

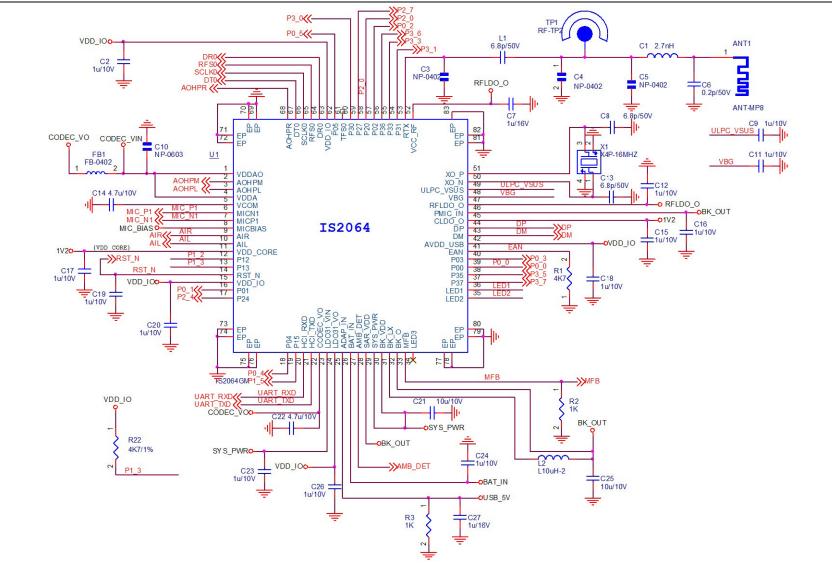

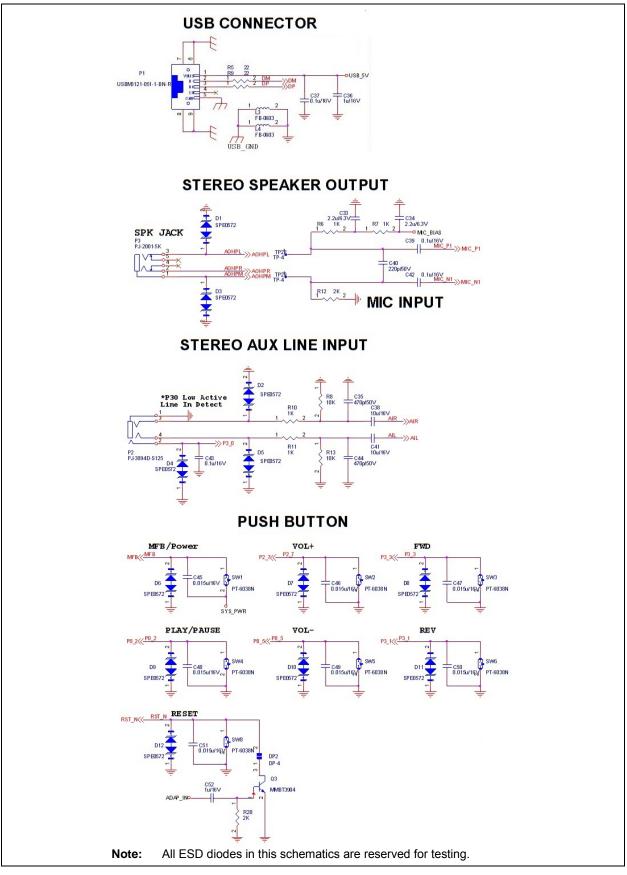

| Appendix A: Reference Circuit             | . 59 |

| Appendix B: Revision History              |      |

## TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at **docerrors@microchip.com** or fax the **Reader Response Form** in the back of this data sheet to (480) 792-4150. We welcome your feedback.

### Most Current Data Sheet

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

#### http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS3000000A is version A of document DS30000000).

#### Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

Microchip's Worldwide Web site; <a href="http://www.microchip.com">http://www.microchip.com</a>

· Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include literature number) you are using.

### **Customer Notification System**

Register on our web site at www.microchip.com to receive the most current information on all of our products.

NOTES:

## 1.0 DEVICE OVERVIEW

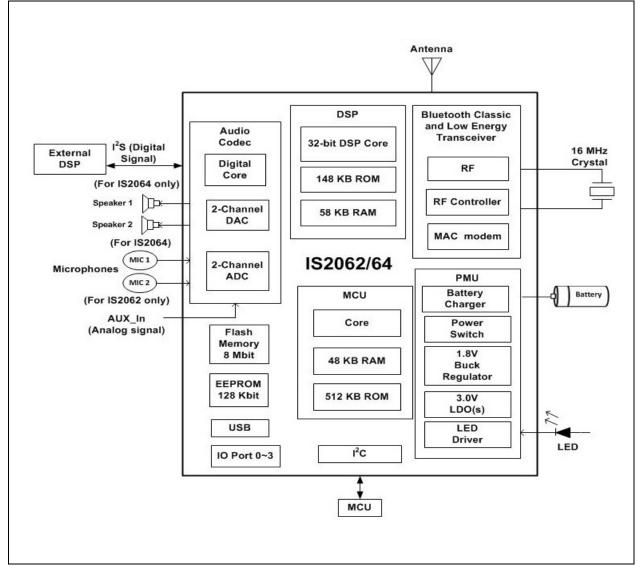

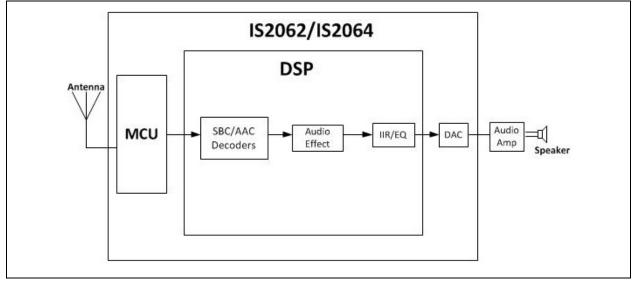

The IS2062/64 SoC integrates a Bluetooth 4.2 dualmode radio transceiver, a Power Management Unit (PMU), a Microcontroller (MCU), an audio codec, a crystal and a 32-bit DSP. The IS2062/64 SoC can be configured using a UI tool.

| Note: | The UI tool is a Windows <sup>®</sup> -based configu- |

|-------|-------------------------------------------------------|

|       | ration utility tool, which is available for           |

|       | download from the Microchip web site at:              |

|       | www.microchip.com/IS2062 and                          |

|       | www.microchip.com/IS2064.                             |

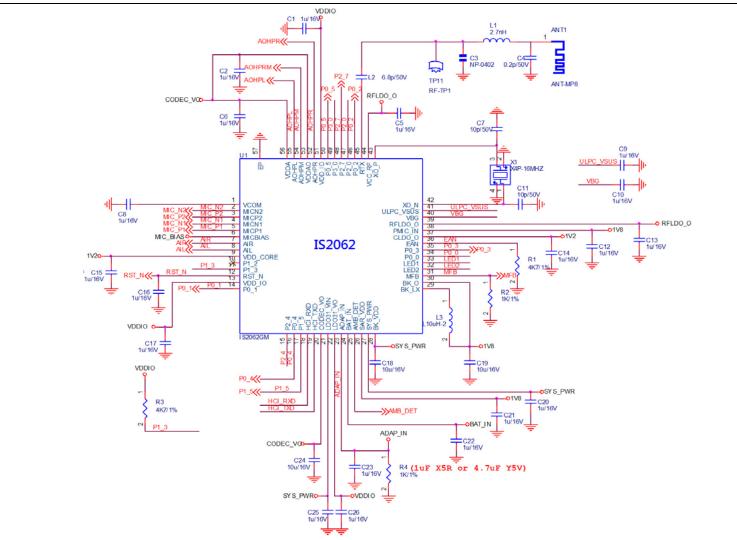

Figure 1-1 illustrates a typical block diagram of the IS2062/64 SoC.

### FIGURE 1-1: IS2062/64 STEREO AUDIO SOC BLOCK DIAGRAM

Table 1-2 provides the key features of the IS2062/64 SoC.

### TABLE 1-1: IS2062/64 KEY FEATURES

| Feature                             | IS2062          | IS2064    |

|-------------------------------------|-----------------|-----------|

| Application                         | Headset/Speaker | Speaker   |

| Stereo/mono                         | Stereo          | Stereo    |

| Pin count                           | 56              | 68        |

| Dimensions (mm <sup>2</sup> )       | 7 x 7           | 8 x 8     |

| Audio DAC output                    | 2 Channel       | 2 Channel |

| DAC (single-ended) SNR at 2.8V (dB) | -98             | -98       |

| DAC (capless) SNR at 2.8V (dB)      | -96             | -96       |

| ADC SNR at 2.8V (dB)                | -92             | -92       |

| I <sup>2</sup> S digital interface  | No              | Yes       |

| Analog AUX-In                       | Yes             | Yes       |

| Mono microphones                    | 2               | 1         |

| External audio amplifier interface  | Yes             | Yes       |

| UART                                | Yes             | Yes       |

| LED driver                          | 2               | 3         |

| Internal DC-DC step-down regulator  | Yes             | Yes       |

| DC 5V adaptor input                 | Yes             | Yes       |

| Battery charger (350 mA max)        | Yes             | Yes       |

| ADC for thermal charger protection  | Yes             | Yes       |

| Undervoltage protection             | Yes             | Yes       |

| GPIO                                | 10              | 15        |

| Button support                      | 6               | 6         |

| NFC (triggered by external NFC)     | Yes             | Yes       |

| EEPROM                              | 128 K           | 128 K     |

| Customized voice prompt             | Store in El     | EPROM     |

| Multi-tone                          | Yes             | Yes       |

| DSP sound effect                    | Yes             | Yes       |

| BLE                                 | Yes             | Yes       |

| Bluetooth profiles                  |                 |           |

| HFP                                 | 1.6             | 1.6       |

| AVRCP                               | 1.6             | 1.6       |

| A2DP                                | 1.3             | 1.3       |

| HSP                                 | 1.2             | 1.2       |

| SPP                                 | 1.2             | 1.2       |

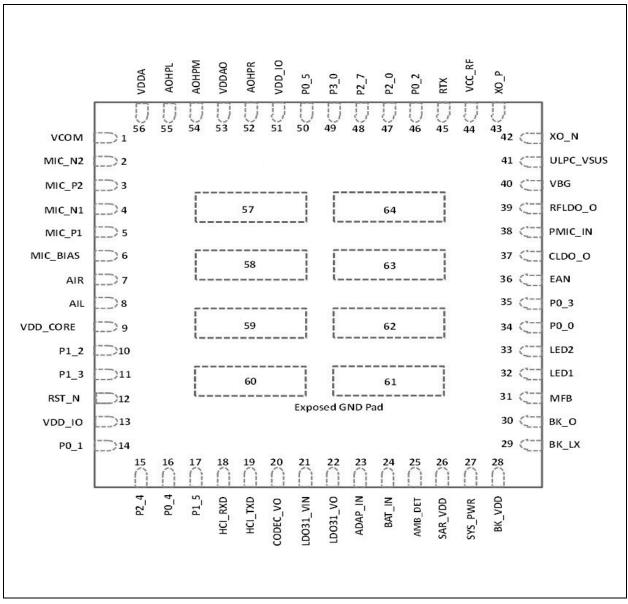

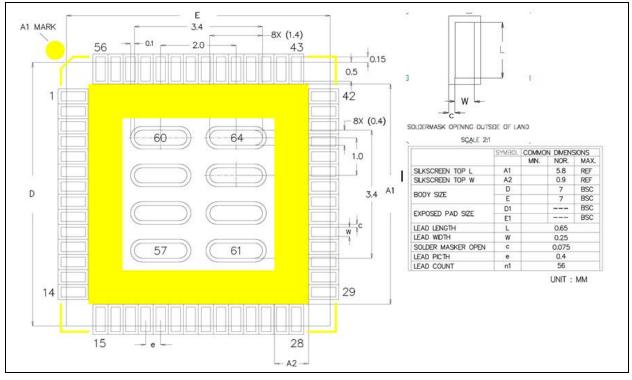

Figure 1-2 illustrates the IS2062 SoC pin diagram. Table 1-2 provides the pin descriptions of the IS2062 SoC and these pins can be configured using the UI tool.

FIGURE 1-2: IS2062 SOC PIN DIAGRAM

| Pin No | Pin Type | Name      | Description                                                                                                                                                                                                                                                                                                          |

|--------|----------|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1      | Р        | VCOM      | Internal biasing voltage for codec; connect to GND through a 1 µF (X5R/X7R) capacitor                                                                                                                                                                                                                                |

| 2      | I        | MIC_N2    | Mic 2 mono differential analog negative input                                                                                                                                                                                                                                                                        |

| 3      | Ι        | MIC_P2    | Mic 2 mono differential analog positive input                                                                                                                                                                                                                                                                        |

| 4      | I        | MIC_N1    | Mic 1 mono differential analog negative input                                                                                                                                                                                                                                                                        |

| 5      | Ι        | MIC_P1    | Mic 1 mono differential analog positive input                                                                                                                                                                                                                                                                        |

| 6      | Р        | MIC_BIAS  | Electric mic biasing voltage                                                                                                                                                                                                                                                                                         |

| 7      | I        | AIR       | R-channel, single-ended analog input                                                                                                                                                                                                                                                                                 |

| 8      | I        | AIL       | L-channel, single-ended analog input                                                                                                                                                                                                                                                                                 |

| 9      | Р        | VDD_CORE  | Core 1.2V power input; connect to the CLDO_O pin; connect to GND through a 1 $\mu$ F (X5R/X7R) capacitor                                                                                                                                                                                                             |

| 10     | 0        | P1_2      | I <sup>2</sup> C SCL (EEPROM)                                                                                                                                                                                                                                                                                        |

| 11     | I/O      | P1_3      | I <sup>2</sup> C SDA (EEPROM), requires external pull-up resistor                                                                                                                                                                                                                                                    |

| 12     | I        | RST_N     | System Reset (active-low)                                                                                                                                                                                                                                                                                            |

| 13     | Р        | VDD_IO    | I/O power supply input (3.0V~3.6V); connect to<br>LDO31_VO (pin # 22); connect to GND through a 1 μF<br>(X5R/X7R) capacitor                                                                                                                                                                                          |

| 14     | I/O      | P0_1      | <ul> <li>Configurable control or indication pin<br/>(Internally pulled up if configured as an input)</li> <li>FWD key when class 2 RF (default), active-low</li> <li>Class1 Tx control signal for external RF T/R<br/>switch, active-high</li> </ul>                                                                 |

| 15     | I        | P2_4      | <ul> <li>System configuration pin along with P2_0 and EAN pins can be used to set the SoC in any one of the following modes:</li> <li>Application mode (for normal operation)</li> <li>Test mode (to change EEPROM values)</li> <li>Write Flash mode (to load a new firmware into the SoC), see Table 6-1</li> </ul> |

| 16     | I/O      | P0_4      | Configurable control or indication pin<br>(Internally pulled up if configured as an input)<br>• NFC detection pin, active-low<br>• Out_Ind_1                                                                                                                                                                         |

| 17     | I/O      | P1_5      | Configurable control or indication pin<br>(Internally pulled up if configured as an input)<br>• NFC detection pin, active-low<br>• Out_Ind_1<br>• Slide Switch Detector                                                                                                                                              |

| 18     | Ι        | HCI_RXD   | HCI UART data input                                                                                                                                                                                                                                                                                                  |

| 19     | 0        | HCI_TXD   | HCI UART data output                                                                                                                                                                                                                                                                                                 |

| 20     | Р        | CODEC_VO  | LDO output for codec power                                                                                                                                                                                                                                                                                           |

| 21     | Р        | LDO31_VIN | LDO input, connect to SYS_PWR (pin # 27)                                                                                                                                                                                                                                                                             |

| 22     | Р        | LDO31_VO  | 3V LDO output for VDD_IO power, do not calibrate                                                                                                                                                                                                                                                                     |

| 23     | Р        | ADAP_IN   | 5V power adaptor input                                                                                                                                                                                                                                                                                               |

| 24     | P        | BAT_IN    | Battery input. voltage range: 3.2V to 4.2V                                                                                                                                                                                                                                                                           |

### TABLE 1-2: IS2062 SOC PIN DESCRIPTIONS

| TABLE 1-2: | E 1-2: IS2062 SOC PIN DESCRIPTIONS (CONTINUED) |           |                                                                                                                                                                                                                                                                                                                           |  |

|------------|------------------------------------------------|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Pin No     | Pin Type                                       | Name      | Description                                                                                                                                                                                                                                                                                                               |  |

| 25         | I                                              | AMB_DET   | Analog input for ambient temperature detection                                                                                                                                                                                                                                                                            |  |

| 26         | Р                                              | SAR_VDD   | SAR 1.8V input; connect to BK_O pin                                                                                                                                                                                                                                                                                       |  |

| 27         | Р                                              | SYS_PWR   | Power output from BAT_IN or ADAP_IN for IS2062 only                                                                                                                                                                                                                                                                       |  |

| 28         | Р                                              | BK_VDD    | 1.8V buck VDD power Input; connect to SYS_PWR pin                                                                                                                                                                                                                                                                         |  |

| 29         | Р                                              | BK_LX     | 1.8V buck PWM/PFM output                                                                                                                                                                                                                                                                                                  |  |

| 30         | Р                                              | BK_O      | 1.8V buck feedback input                                                                                                                                                                                                                                                                                                  |  |

| 31         | I                                              | MFB       | <ul><li>Multi-function button and power-on key</li><li>UART RX IND, active-high</li></ul>                                                                                                                                                                                                                                 |  |

| 32         | I                                              | LED1      | LED driver 1                                                                                                                                                                                                                                                                                                              |  |

| 33         | I                                              | LED2      | LED driver 2                                                                                                                                                                                                                                                                                                              |  |

| 34         | I/O                                            | P0_0      | Configurable control or indication pin<br>(Internally pulled up if configured as an input)<br>• Slide Switch Detector, active-low<br>• UART TX_IND, active-low                                                                                                                                                            |  |

| 35         | I/O                                            | P0_3      | <ul> <li>Configurable control or indication pin<br/>(Internally pulled up if configured as an input)</li> <li>REV key (default), active-low</li> <li>Buzzer signal output</li> <li>Out_Ind_2</li> <li>Class1 Rx Control signal of external RF T/R<br/>switch, active-high</li> </ul>                                      |  |

| 36         | I                                              | EAN       | <ul> <li>System configuration pin along with the P2_4 and P2_0 pins can be used to set the SoC in any one of the following modes:</li> <li>Application mode (for normal operation)</li> <li>Test mode (to change EEPROM values)</li> <li>Write Flash mode (to load a new firmware into the SoC), see Table 6-1</li> </ul> |  |

| 37         | Р                                              | CLDO_O    | 1.2V core LDO output                                                                                                                                                                                                                                                                                                      |  |

| 38         | Р                                              | PMIC_IN   | 1.8V power input for internal blocks; connect to BK_O<br>(pin # 30)                                                                                                                                                                                                                                                       |  |

| 39         | Р                                              | RFLDO_O   | 1.28V RF LDO output                                                                                                                                                                                                                                                                                                       |  |

| 40         | Р                                              | VBG       | Bandgap output reference for decoupling interference                                                                                                                                                                                                                                                                      |  |

| 41         | Р                                              | ULPC_VSUS | ULPC 1.2V output power                                                                                                                                                                                                                                                                                                    |  |

| 42         | I                                              | XO_N      | 16 MHz crystal input negative                                                                                                                                                                                                                                                                                             |  |

| 43         | I                                              | XO_P      | 16 MHz crystal input positive                                                                                                                                                                                                                                                                                             |  |

| 44         | Р                                              | VCC_RF    | RF power input (1.28V) for both synthesizer and Tx/Rx block                                                                                                                                                                                                                                                               |  |

| 45         | I/O                                            | RTX       | RF path (transmit/receive)                                                                                                                                                                                                                                                                                                |  |

| 46         | I                                              | P0_2      | Configurable control or indication pin<br>(Internally pulled up if configured as an input)<br>Play/Pause key (default), active-low                                                                                                                                                                                        |  |

| TABLE 1-2: | IS2062 SOC PIN DESCRIPTIONS (CONTINUED) |

|------------|-----------------------------------------|

|            |                                         |

| Pin No | Pin Type     | Name          | Description                                                                                                                                                                                                                                                                                       |

|--------|--------------|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 47     | 1            | P2_0          | <ul> <li>System configuration pin along with P2_4 and EAN pins can be used to set the SoC in any one of the following modes:</li> <li>Application mode (for normal operation),</li> <li>Test mode (to change EEPROM values)</li> <li>Write Flash mode (to load a new firmware into the</li> </ul> |

|        |              |               | SoC), see Table 6-1                                                                                                                                                                                                                                                                               |

| 48     |              | P2_7          | Configurable control or indication pin<br>(Internally pulled up if configured as an input)<br>Volume-up key (default)                                                                                                                                                                             |

| 49     | I            | P3_0          | Configurable control or indication pin<br>(Internally pulled up if configured as an input)<br>AUX-In detector                                                                                                                                                                                     |

| 50     | I            | P0_5          | Configurable control or indication pin<br>(Internally pulled up if configured as an input)<br>Volume-up key (default)                                                                                                                                                                             |

| 51     | Р            | VDD_IO        | I/O power supply input (3.0V~3.6V); Connect to LDO31_VO pin                                                                                                                                                                                                                                       |

| 52     | 0            | AOHPR         | R-channel analog headphone output,                                                                                                                                                                                                                                                                |

| 53     | Р            | VDDAO         | Power supply dedicated to codec output amplifiers; connect to CODEC_VO pin                                                                                                                                                                                                                        |

| 54     | 0            | AOHPM         | Headphone common mode output/sense input                                                                                                                                                                                                                                                          |

| 55     | 0            | AOHPL         | L-channel analog headphone output                                                                                                                                                                                                                                                                 |

| 56     | Р            | VDDA          | Power supply or reference voltage for external codec<br>connect to CODEC_VO pin                                                                                                                                                                                                                   |

| 57-64  | Р            | EP            | Exposed pads. Used as ground (GND) pins                                                                                                                                                                                                                                                           |

| egend: | I= Input pin | O= Output pin | I/O= Input/Output pin P= Power pin                                                                                                                                                                                                                                                                |

### TABLE 1-2: IS2062 SOC PIN DESCRIPTIONS (CONTINUED)

**Note:** The IS2062 SoC pins can be configured using the UI tool.

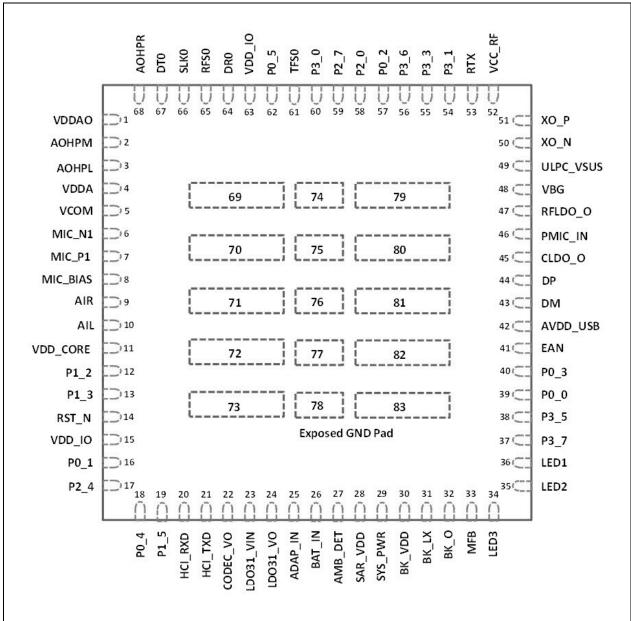

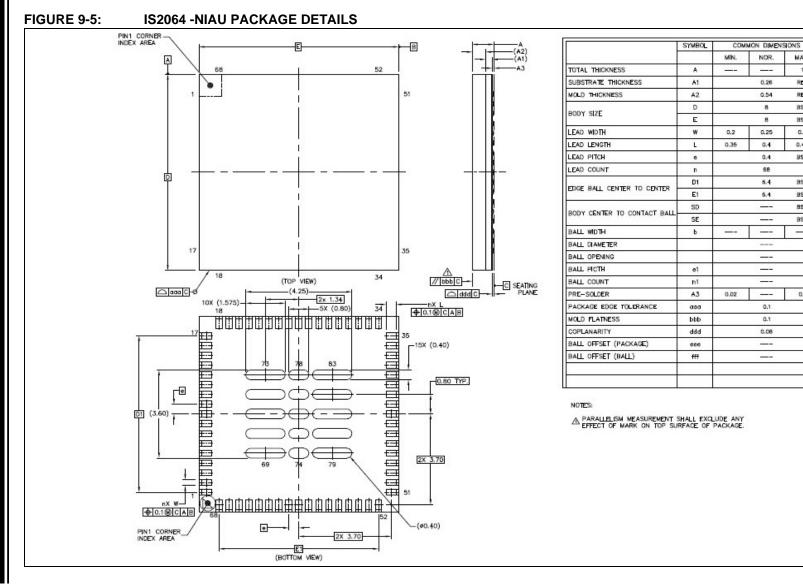

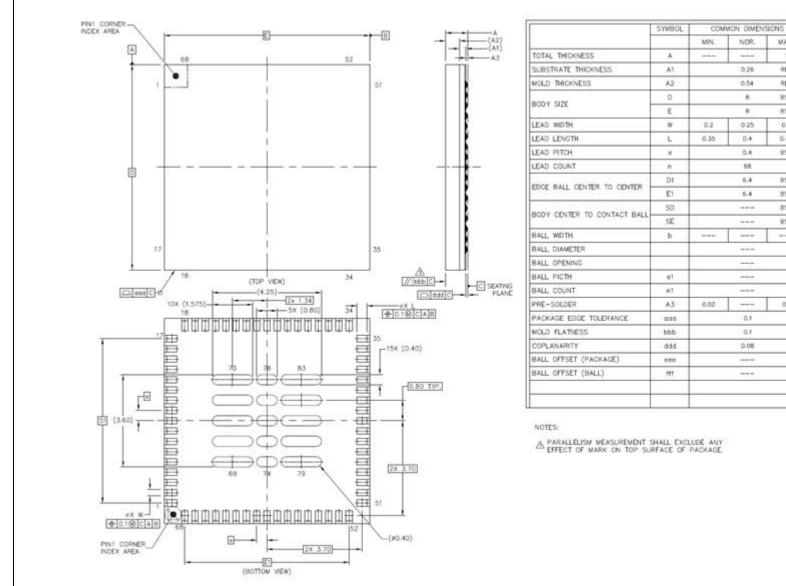

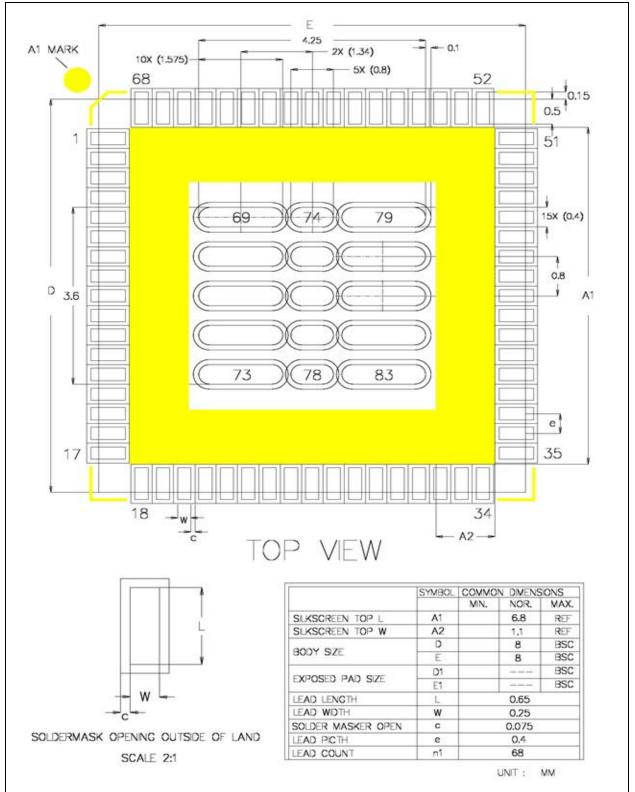

Figure 1-3 illustrates the pin diagram of the IS2064 SoC.

#### Table 1-3 provides the pin descriptions of the IS2064 SoC.

| Pin No | Pin Type | Name      | Description                                                                                                                                                                                                                                                                                 |

|--------|----------|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1      | Р        | VDDAO     | Power supply dedicated to codec output amplifiers;<br>connect to the CODEC_VO pin                                                                                                                                                                                                           |

| 2      | 0        | AOHPM     | Headphone common mode output or sense input                                                                                                                                                                                                                                                 |

| 3      | 0        | AOHPL     | Headphone output, left channel                                                                                                                                                                                                                                                              |

| 4      | Р        | VDDA      | Power supply or reference voltage for external codec; connect to the CODEC_VO pin                                                                                                                                                                                                           |

| 5      | Р        | VCOM      | Internal biasing voltage for codec                                                                                                                                                                                                                                                          |

| 6      | I        | MIC_N1    | Mic 1 mono differential analog negative input                                                                                                                                                                                                                                               |

| 7      | I        | MIC_P1    | Mic 1 mono differential analog positive input                                                                                                                                                                                                                                               |

| 8      | Р        | MIC_BIAS  | Electric microphone biasing voltage                                                                                                                                                                                                                                                         |

| 9      | I        | AIR       | R-channel single-ended analog input                                                                                                                                                                                                                                                         |

| 10     | I        | AIL       | L-channel single-ended analog input                                                                                                                                                                                                                                                         |

| 11     | Р        | VDD_CORE  | Core 1.2V power input; connect to the CLDO_O pin                                                                                                                                                                                                                                            |

| 12     | 0        | P1 2      | I <sup>2</sup> C SCL (EEPROM)                                                                                                                                                                                                                                                               |

| 13     | I/O      | P1 3      | I <sup>2</sup> C SDA (EEPROM), requires external pull-up resistor                                                                                                                                                                                                                           |

| 14     |          | RST N     | System Reset (active-low)                                                                                                                                                                                                                                                                   |

| 15     | Р        | VDD_IO    | I/O power supply input (3.0V~3.6V); connect to<br>LDO31_VO (pin # 24); connect to GND through a<br>1 μF (X5R/X7R) capacitor                                                                                                                                                                 |

| 16     | I/O      | P0_1      | <ul> <li>Configurable control or indication pin<br/>(Internally pulled up if configured as an input)</li> <li>FWD key when Class 2 RF (default), active-low</li> <li>Class1 Tx control signal for external RF Tx/Rx<br/>switch, active-high</li> </ul>                                      |

| 17     | I        | P2_4      | System configuration pin along with the P2_0 and EAN<br>pins, used to set the SoC in any one of the following<br>modes:<br>• Application mode (for normal operation)<br>• Test mode (to change EEPROM values)<br>• Write Flash mode (to load a new firmware into<br>the SoC), see Table 6-1 |

| 18     | I/O      | P0_4      | Configurable control or indication pin<br>(Internally pulled up if configured as an input)<br>• NFC detection pin, active-low<br>• Out_Ind_1                                                                                                                                                |

| 19     | I/O      | P1_5      | Configurable control or indication pin<br>(Internally pulled up if configured as an input)<br>• NFC detection pin<br>• Slide switch detector, active-high<br>• Out_Ind_1<br>• Multi-speaker Master/Slave mode control (FW<br>dependent)                                                     |

| 20     | I        | HCI_RXD   | HCI UART data input                                                                                                                                                                                                                                                                         |

| 21     | 0        | HCI_TXD   | HCI UART data output                                                                                                                                                                                                                                                                        |

| 22     | Р        | CODEC_VO  | LDO output for codec power                                                                                                                                                                                                                                                                  |

| 23     | Р        | LDO31 VIN | LDO input; connect to SYS PWR (pin # 29)                                                                                                                                                                                                                                                    |

TABLE 1-3:IS2064 SOC PIN DESCRIPTIONS

| ABLE 1-3: IS2064 SOC PIN DESCRIPTIONS (CONTINUED) |          |           |                                                                                                                                                                                                                                                                                                                               |

|---------------------------------------------------|----------|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin No                                            | Pin Type | Name      | Description                                                                                                                                                                                                                                                                                                                   |

| 24                                                | P        | LDO31_VO  | 3V LDO output, for VDD_IO power, do not calibrate                                                                                                                                                                                                                                                                             |

| 25                                                | Р        | ADAP_IN   | 5V power adaptor input                                                                                                                                                                                                                                                                                                        |

| 26                                                | Р        | BAT_IN    | Battery input. Voltage range: 3.2V to 4.2V                                                                                                                                                                                                                                                                                    |

| 27                                                | I        | AMB_DET   | Analog input for ambient temperature detection                                                                                                                                                                                                                                                                                |

| 28                                                | Р        | SAR_VDD   | SAR 1.8V input; connect to BK_O pin                                                                                                                                                                                                                                                                                           |

| 29                                                | Р        | SYS_PWR   | Power output which come from BAT_IN or ADAP_IN                                                                                                                                                                                                                                                                                |

| 30                                                | Р        | BK_VDD    | 1.8V buck VDD Power Input; connect to SYS_PWR pin                                                                                                                                                                                                                                                                             |

| 31                                                | Р        | BK_LX     | 1.8V buck PWM/PFM output                                                                                                                                                                                                                                                                                                      |

| 32                                                | Р        | BK_O      | 1.8V buck feedback input                                                                                                                                                                                                                                                                                                      |

| 33                                                | I        | MFB       | 1. Multi-function button and power-on key<br>2. UART RX_IND, active-high                                                                                                                                                                                                                                                      |

| 34                                                | I        | LED3      | LED driver 3                                                                                                                                                                                                                                                                                                                  |

| 35                                                | I        | LED2      | LED driver 2                                                                                                                                                                                                                                                                                                                  |

| 36                                                |          | LED1      | LED driver 1                                                                                                                                                                                                                                                                                                                  |

| 37                                                | I/O      | P3_7      | Configurable control or indication pin<br>(Internally pulled up if configured as an input)<br>UART TX_IND, active-low                                                                                                                                                                                                         |

| 38                                                | I/O      | P3_5      | Configurable control or indication pin<br>(Internally pulled up if configured as an input)                                                                                                                                                                                                                                    |

| 39                                                | I/O      | P0_0      | Configurable control or indication pin<br>(Internally pulled up if configured as an input)<br>Slide switch detector, active-high                                                                                                                                                                                              |

| 40                                                | 40 I/O   | P0_3      | Configurable control or indication pin<br>(Internally pulled up if configured as an input)<br>• REV key, active-low.                                                                                                                                                                                                          |

|                                                   |          |           | <ul> <li>Buzzer signal output</li> <li>Out_Ind_2</li> <li>Class 1 Rx Control signal of external RF T/R switch, active-high</li> </ul>                                                                                                                                                                                         |

| 41                                                | 1        | EAN       | <ul> <li>System configuration pin along with the P2_0 and P2_4 pins, used to set the IS2062/64 SoC in any one of the following modes:</li> <li>Application mode (for normal operation)</li> <li>Test mode (to change EEPROM values)</li> <li>Write Flash mode (to load a new firmware into the SoC), see Table 6-1</li> </ul> |

| 42                                                | Р        | AVDD_USB  | USB power input; connect to LDO31_VO pin                                                                                                                                                                                                                                                                                      |

| 43                                                | I/O      | DM        | Differential data-minus USB                                                                                                                                                                                                                                                                                                   |

| 44                                                | I/O      | DP        | Differential data-positive USB                                                                                                                                                                                                                                                                                                |

| 45                                                | Р        | CLDO_O    | 1.2V core LDO output                                                                                                                                                                                                                                                                                                          |

| 46                                                | Р        | PMIC_IN   | 1.8V power input for internal blocks; connect to BK_O<br>(pin # 32)                                                                                                                                                                                                                                                           |

| 47                                                | Р        | RFLDO_O   | 1.28V RF LDO output                                                                                                                                                                                                                                                                                                           |

| 48                                                | Р        | VBG       | Bandgap output reference for decoupling interference                                                                                                                                                                                                                                                                          |

| 49                                                | Р        | ULPC_VSUS | ULPC 1.2V output power, maximum loading 1 mA                                                                                                                                                                                                                                                                                  |

| 50                                                | I        | XO_N      | 16 MHz crystal input negative                                                                                                                                                                                                                                                                                                 |

| 51                                                | I        | XO_P      | 16 MHz crystal input positive                                                                                                                                                                                                                                                                                                 |

| TABLE 1-3: | IS2064 SOC PIN DESCRIPTIONS (CONTINUED) |

|------------|-----------------------------------------|

|            |                                         |

| Din Ma |          | -      | CONTINUED)                                                                                                                                                                                                                                                                                                                   |

|--------|----------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin No | Pin Type | Name   | Description                                                                                                                                                                                                                                                                                                                  |

| 52     | P        | VCC_RF | RF power input for both synthesizer and Tx/Rx block                                                                                                                                                                                                                                                                          |

| 53     | I/O      | RTX    | RF path (transmit/receive)                                                                                                                                                                                                                                                                                                   |

| 54     | I/O      | P3_1   | Configurable control or indication pin<br>(Internally pulled up if configured as an input)<br>REV key when Class 1 RF (default), active-low                                                                                                                                                                                  |

| 55     | I/O      | P3_3   | Configurable control or indication pin<br>(Internally pulled up if configured as an input)<br>FWD key when class 1 RF (default), active-low                                                                                                                                                                                  |

| 56     | I/O      | P3_6   | Configurable control or indication pin<br>(Internally pulled up if configured as an input)<br>Multi-SPK Master/Slave mode control (FW depender                                                                                                                                                                               |

| 57     | I/O      | P0_2   | Configurable control or indication pin<br>(Internally pulled up if configured as an input)<br>Play/Pause key as the default setting                                                                                                                                                                                          |

| 58     | I/O      | P2_0   | <ul> <li>System configuration pin along with the EAN and P2_pins can be used to set the SoC in any one of the following modes:</li> <li>Application mode (for normal operation),</li> <li>Test mode (to change EEPROM values), and</li> <li>Write Flash mode (to load a new firmware into the SoC), see Table 6-1</li> </ul> |

| 59     | I/O      | P2_7   | Configurable control or indication pin<br>(Internally pulled up if configured as an input)<br>Volume-up key (default)                                                                                                                                                                                                        |

| 60     | Ι/Ο      | P3_0   | Configurable control or indication pin<br>(Internally pulled up if configured as an input)<br>AUX-In detector                                                                                                                                                                                                                |

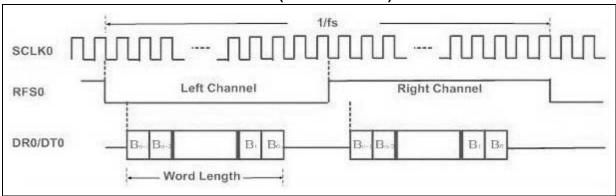

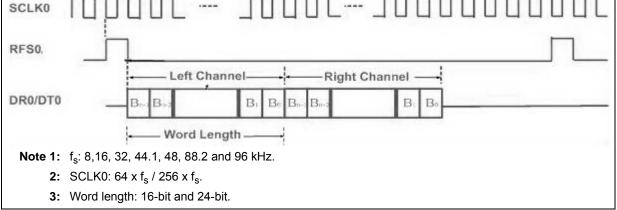

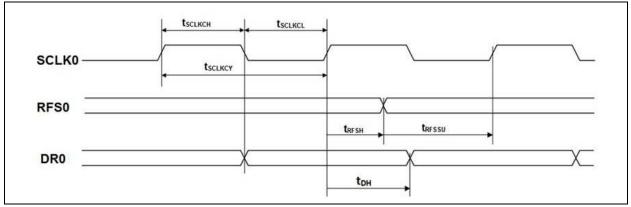

| 61     | I/O      | TFS0   | I <sup>2</sup> S interface: left/right clock                                                                                                                                                                                                                                                                                 |

| 62     | 1/0      | P0_5   | Configurable control or indication pin<br>(Internally pulled up if configured as an input)<br>Volume down key (default)                                                                                                                                                                                                      |

| 63     | Р        | VDD_IO | I/O power supply input (3.0V~3.6V); connect to LDO31_VO pin                                                                                                                                                                                                                                                                  |

| 64     | I/O      | DR0    | I <sup>2</sup> S interface: digital left/right data                                                                                                                                                                                                                                                                          |

| 65     | I/O      | RFS0   | I <sup>2</sup> S interface: left/right clock                                                                                                                                                                                                                                                                                 |

| 66     | I/O      | SCLK0  | I <sup>2</sup> S interface: bit clock                                                                                                                                                                                                                                                                                        |

| 67     | I/O      | DT0    | I <sup>2</sup> S interface: digital left/right data                                                                                                                                                                                                                                                                          |

| 68     | 0        | AOHPR  | Headphone output, right channel                                                                                                                                                                                                                                                                                              |

| 69-83  | Р        | EP     | Exposed pads, Used as ground (GND) pins                                                                                                                                                                                                                                                                                      |

### TABLE 1-3: IS2064 SOC PIN DESCRIPTIONS (CONTINUED)

**Note:** These pins can be configured using the UI tool.

## 2.0 AUDIO

The input and output audios have different stages and each stage can be programmed to vary the gain response characteristics. For microphone, both single-end inputs and differential inputs are supported. To maintain a high quality signal, a stable bias voltage source to the condenser microphone's FET is provided. The DC blocking capacitors can be used at both positive and negative sides of the input. Internally, this analog signal is converted to 16-bit, 8/16 kHz linear PCM data.

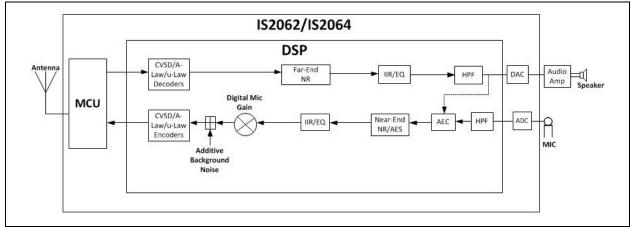

### 2.1 Digital Signal Processor

A Digital Signal Processor (DSP) is used to perform speech and audio processing. The advanced speech features, such as acoustic echo cancellation and noise reduction are in-built. To reduce nonlinear distortion and help echo cancellation, an outgoing signal level to the speaker will exceed the threshold (and therefore likely to create echo). This may result in suppression of the signal. Adaptive filtering is also applied to track the echo path impulse in response to provide echo free and full-duplex user experience. The embedded noise reduction algorithm helps to extract clean speech signals from the noisy inputs captured by microphones and improves mutual understanding in communication. Advanced audio features, such as multi-band dynamic range control, parametric multi-band equalizer, audio widening and virtual bass are in-built. The audio effect algorithms are to improve the user's audio listening experience in terms of better quality audio after audio signal processing.

Figure 2-1 and Figure 2-2 illustrate the processing flow of speaker phone applications for speech and audio signal processing.

The DSP parameters can be configured using the DSP tool. For additional information on the DSP tool, refer to the "IS206X DSP Application Note".

| Note: | The DSP tool and IS206X DSP Applica-      |

|-------|-------------------------------------------|

|       | tion Note are available for download from |

|       | the Microchip web site at:                |

|       | www.microchip.com/IS2062 and              |

|       | www.microchip.com/IS2064                  |

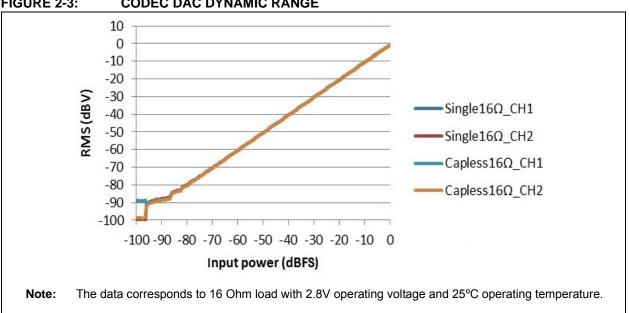

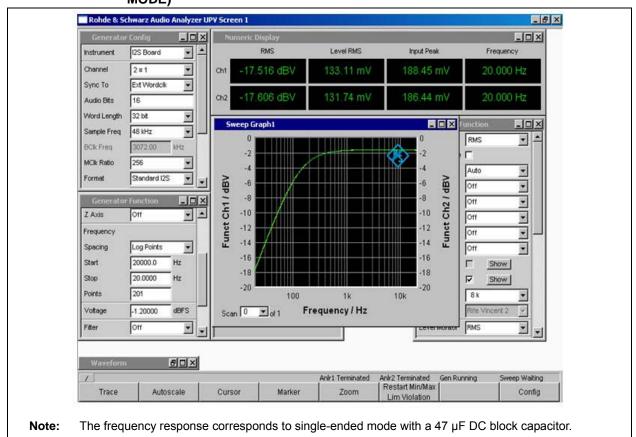

#### FIGURE 2-3: CODEC DAC DYNAMIC RANGE

#### 2.2 Codec

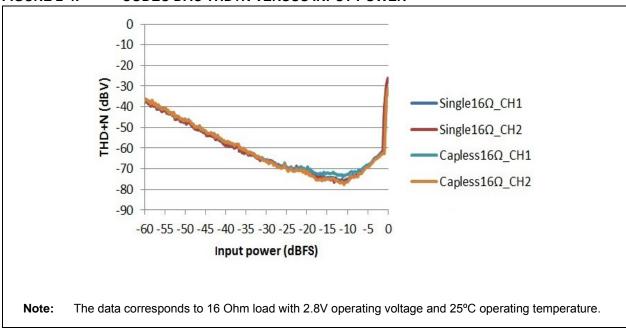

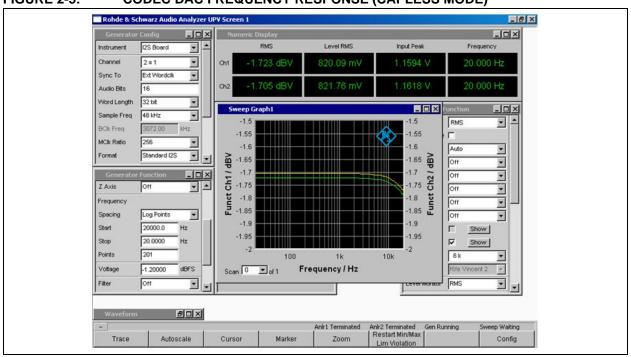

The built-in codec has a high signal-to-noise ratio (SNR) performance and it consist of an analog-to-digital converter (ADC), a digital-to-analog converter (DAC) and additional analog circuitry. Figure 2-3 through Figure 2-6 illustrate dynamic range and frequency response of the codec.

### FIGURE 2-5: CODEC DAC FREQUENCY RESPONSE (CAPLESS MODE)

## FIGURE 2-6: CODEC DAC FREQUENCY RESPONSE (SINGLE-ENDED MODE)

### 2.3 Auxiliary Port

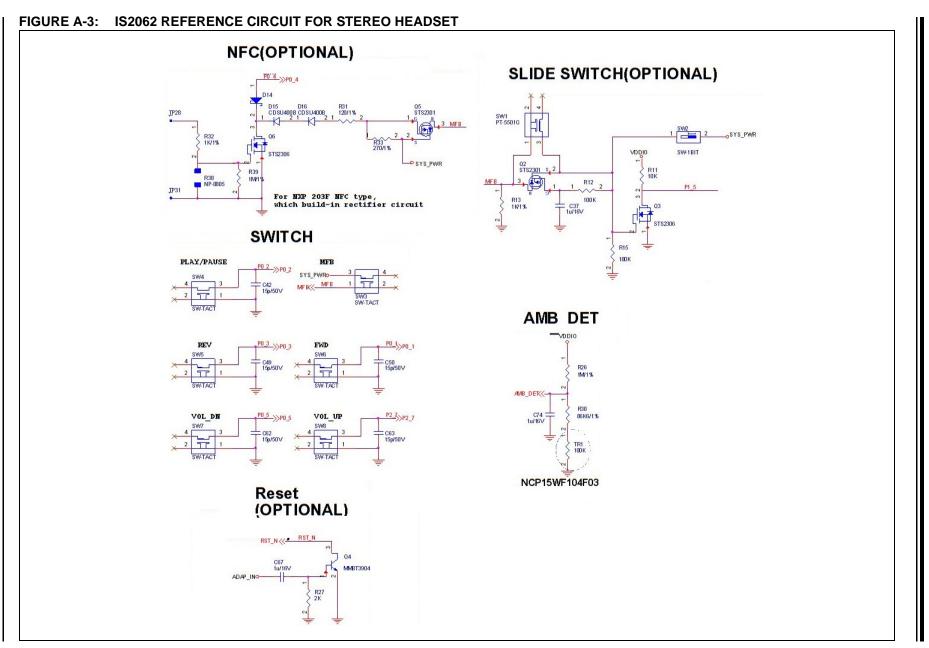

The IS2062/64 SoC supports one analog (line-in) signal from external audio source. The analog (line-in) signal can be processed by the DSP to generate different sound effects, multi-band dynamic range compression and audio widening, which can be setup by using the DSP tool.

### 2.4 Analog Speaker Output

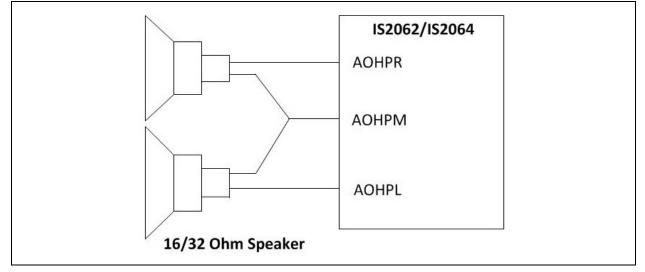

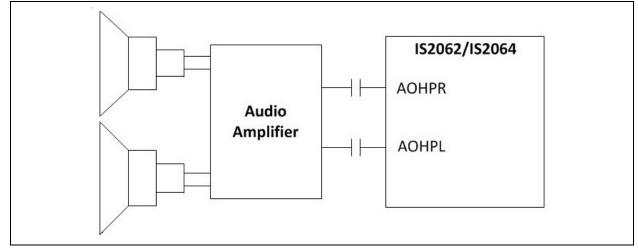

The IS2062/64 SoC supports the following speaker output modes:

- Capless mode Recommended for headphone applications in which capless output connection helps to save the BOM cost by avoiding a large DC blocking capacitor. Figure 2-7 illustrates the analog speaker output Capless mode.

- Single-ended mode Used for driving an external audio amplifier where a DC blocking capacitor is required. Figure 2-8 illustrates the analog speaker output Single-Ended mode.

#### FIGURE 2-7: ANALOG SPEAKER OUTPUT CAPLESS MODE

## 3.0 TRANSCEIVER

The IS2062/64 SoC is designed and optimized for Bluetooth 2.4 GHz systems. It contains a complete radio frequency transmitter/receiver section. An internal synthesizer generates a stable clock to synchronize with another device.

### 3.1 Transmitter

The internal power amplifier (PA) has a maximum output power of +4 dBm. This is applied for Class 2 or Class 3 radios without an external RF PA.

The transmitter directly performs IQ conversion to minimize the frequency drift.

### 3.2 Receiver

The low-noise amplifier (LNA) operates with TRcombined mode for single port application. It can save a pin on package without having an external Tx/Rxswitch.

The ADC is used to sample the input analog signal and convert it into digital signal for de-modulator analysis. A channel filter has been integrated into receiver channel before the ADC, which is used to reduce the external component count and increase the anti-interference capability. The image rejection filter is used to reject image frequency for low-IF architecture. This filter for low-IF architecture is intended to reduce external Band Pass Filter (BPF) component for super heterodyne architecture.

Received Signal Strength Indicator (RSSI) signal feedback to the processor is used to control the RF output power to make a good trade-off for effective distance and current consumption.

### 3.3 Synthesizer

A synthesizer generates a clock for radio transceiver operation. There is a VCO inside, with a tunable internal LC tank that can reduce variation for components. A crystal oscillator with an internal digital trimming circuit provides a stable clock for synthesizer.

### 3.4 Modem

For Bluetooth 1.2 specification and below, 1 Mbps was the standard data rate based on Gaussian Frequency Shift Keying (GFSK) modulation scheme. This basic rate modem meets Basic Data Rate (BDR) requirements of Bluetooth 2.0 with Enhanced Data Rate (EDR) specification.

For Bluetooth 2.0 and above specifications, EDR has been introduced to provide data rates of 1/2/3 Mbps. For baseband, both BDR and EDR utilize the same 1 MHz symbol rate and 1.6 kHz slot rate. For BDR, symbol 1 represents 1-bit. However, each symbol in the payload part of EDR packets represents 2-bit or 3-bit. This is achieved by using two different modulations,  $\pi/4$  DQPSK and 8 DPSK.

# 3.5 Adaptive Frequency Hopping (AFH)

The IS2062/64 SoC has an AFH function to avoid RF interference. It has an algorithm to check the nearby interference and to choose the clear channel for transceiver Bluetooth signal.

NOTES:

#### 4.0 MICROCONTROLLER

A microcontroller is built into an SoC to execute the Bluetooth protocols. It operates from 16 MHz to higher frequencies where the firmware can dynamically adjust the trade-off between the computing power and the power consumption. In ROM version, the MCU firmware is hard-wired to minimize power consumption and to save the external Flash cost.

#### 4.1 Memory

There are sufficient ROM and RAM to fulfill the requirement of processor, in which a synchronous single port RAM interface is used. The register bank, dedicated single port memory and Flash memory are connected to the processor bus. The processor coordinates all the link control procedures and data movement using a set of pointer registers.

#### 4.2 **External Reset**

The IS2062/64 SoC provides a watchdog timer (WDT) to Reset the SoC. It has an integrated Power-on Reset (POR) circuit that resets all circuits to a known Power-on state. This action can also be driven by an

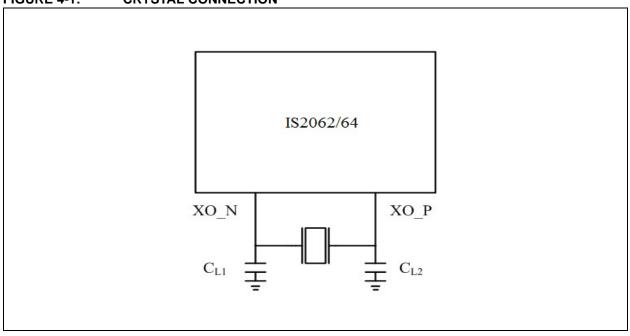

FIGURE 4-1: **CRYSTAL CONNECTION**

external Reset signal which is used to control the device externally by forcing it into a POR state. The RST N signal input is active-low and no connection is required in most of the applications.

#### 4.3 **Reference Clock**

The IS2062/64 SoC is composed of an integrated crystal oscillation function that uses a 16 MHz, ±10 ppm external crystal and two specified loading capacitors to provide a high quality system reference timer source. This feature is typically used to remove the initial tolerance frequency errors associated with the crystal and its equivalent loading capacitance in mass production. Frequency trim is achieved by adjusting the crystal loading capacitance through the on-chip trim capacitors (Ctrim).

The value of trimming capacitance is 200 fF

(200x10<sup>-15</sup> F) per LSb at 5-bit word and the overall adjustable clock frequency is ±50 kHz (based on crystal with load capacitance, C<sub>L</sub> spec = 9 pF). Figure 4-1 illustrates the crystal connection of the IS2062/64 SoC with two capacitors.

NOTES:

### 5.0 POWER MANAGEMENT UNIT

The IS2062/64 SoC has an integrated Power Management Unit (PMU). The main features of the PMU are a lithium-ion and lithium-polymer battery charger and voltage regulation. A power switch is used to switch over the power source between a battery and an adaptor. The PMU also provides current for driving LEDs.

### 5.1 Charging a Battery

The IS2062/64 SoC has a built-in battery charger which is optimized for lithium-ion and lithium-polymer batteries. The charger includes a current sensor for charging control, user programmable current regulator and high accuracy voltage regulator.

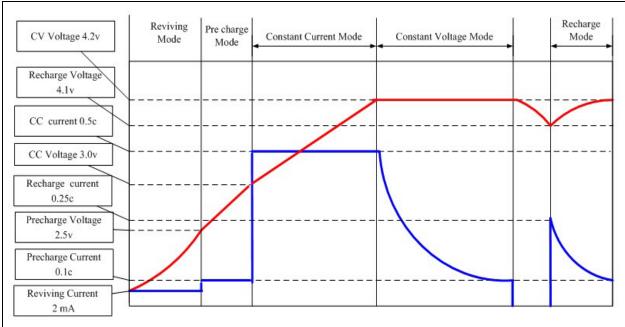

The charging current parameters are configured by using the UI tool. Whenever an adaptor is plugged-in, the charging circuit become activated. Reviving, pre-charging, constant current and constant voltage modes and re-charging functions are included. The maximum charging current is 350 mA. Figure 5-1 illustrates the charging curve of a battery.

### FIGURE 5-1: BATTERY CHARGING CURVE

### 5.2 Voltage Monitoring

A 10-bit, successive approximation ADC (SAR ADC) provides a dedicated channel for voltage level detection. The warning level can be programmed by using the UI tool. The ADC provides a granular resolution to enable the MCU to take control over the charging process.

### 5.3 LDO

A built-in Low-Dropout Regulator (LDO) is used to convert the battery or adaptor power for power supply. It also integrates hardware architecture to control the power on/off procedure. The built-in programmable LDOs provide power for codec and digital I/O pads. Also, it is used to buffer the high input voltage from battery or adapter. This LDO requires 1  $\mu$ F bypass capacitor.

### 5.4 Switching Regulator

The built-in programmable output voltage regulator can convert the battery voltage to RF and baseband core power supply. This converter has a high conversion efficiency and a fast transient response.

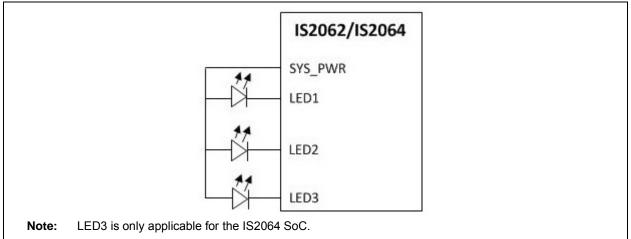

### 5.5 LED Driver

The IS2062 SoC has two LED drivers and the IS2064 SoC has three LED drivers. The LED drivers provide enough sink current (16-step control and 0.35 mA for each step) and the LED can be connected directly to the IS2062/64 SoC. The LED settings can be configured using the UI tool.

Figure 5-2 illustrates the LED driver details.

### 5.6 Under Voltage Protection

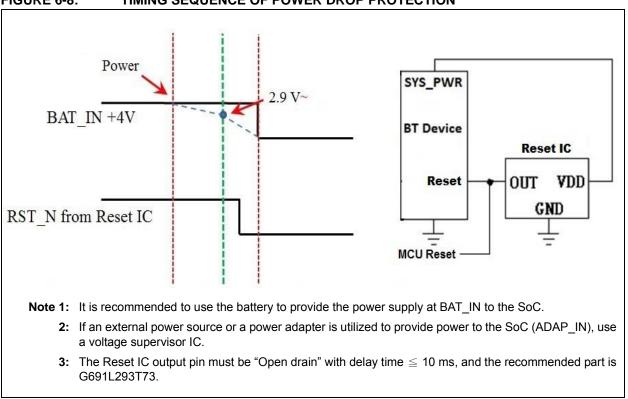

When the SYS\_PWR pin voltage drops below 2.9V, the system will shut-down automatically.

#### 5.7 Ambient Detection

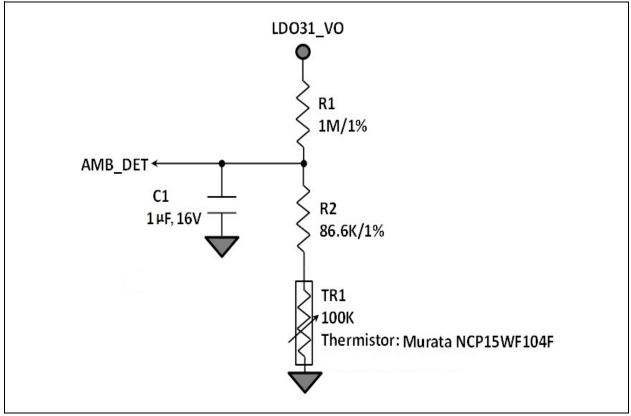

The IS2062/64 SoC has a built-in ADC for charger thermal protection.

Figure 5-3 illustrates the suggested circuit and thermistor, Murata NCP15WF104F. The charger thermal protection can avoid battery charge in restricted temperature range. The upper and lower limits for temperature values are configured by using the UI tool.

**Note:** Thermistor should be placed close to the battery in the user application for accurate temperature measurements and to enable thermal shutdown feature.

### FIGURE 5-3: AMBIENT DETECTION

## 6.0 APPLICATION INFORMATION

### 6.1 Power Supply

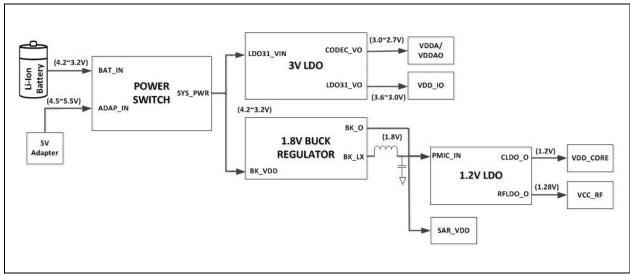

Figure 6-1 illustrates the connection from the BAT\_IN pin to any other voltage supply pins of the IS2062/64 SoC.

### FIGURE 6-1: POWER TREE DIAGRAM

The IS20/62/64 SoC is powered through the BAT\_IN input pin. If battery is not connected, an external power supply must be provided as an input to the ADAP\_IN pin.

Note: When external power supply is connected to the ADAP\_IN pin of the IS2062/64 SoC, the BAT\_IN pin can be left open if battery is not connected.

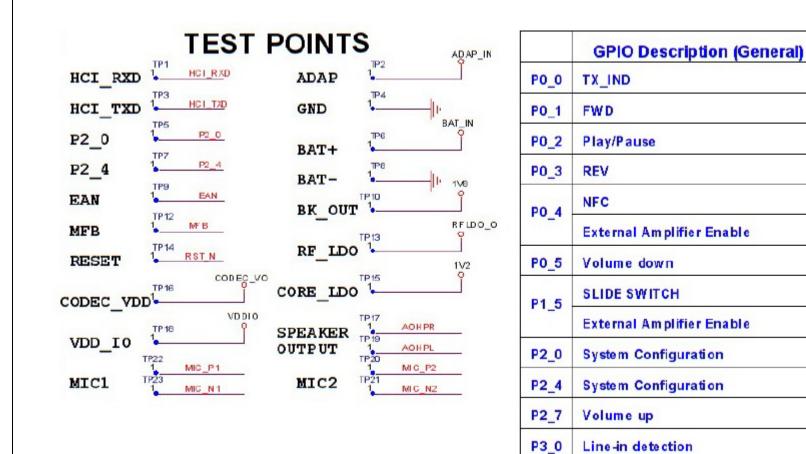

### 6.2 Host MCU Interface

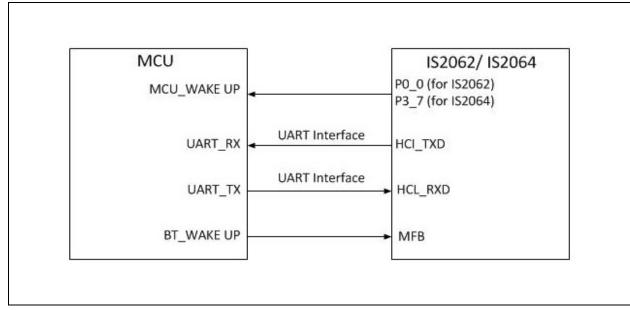

Figure 6-2 illustrates the UART interface between the IS2062/64 SoC and MCU.

#### FIGURE 6-2: HOST MCU INTERFACE OVER UART

The MCU can control the IS2062/64 SoC over the UART interface and wakeup the SoC using the MFB pins, P0\_0 (IS2062) and P3\_7 (IS2064).

Refer to the "UART\_CommandSet" document for a list of functions the IS2062/64 SoC supports and how to use the UI tool to set up the system using the UART command, which is available for download from the Microchip web site at: www.microchip.com/IS2062 and www.microchip.com/IS2064.

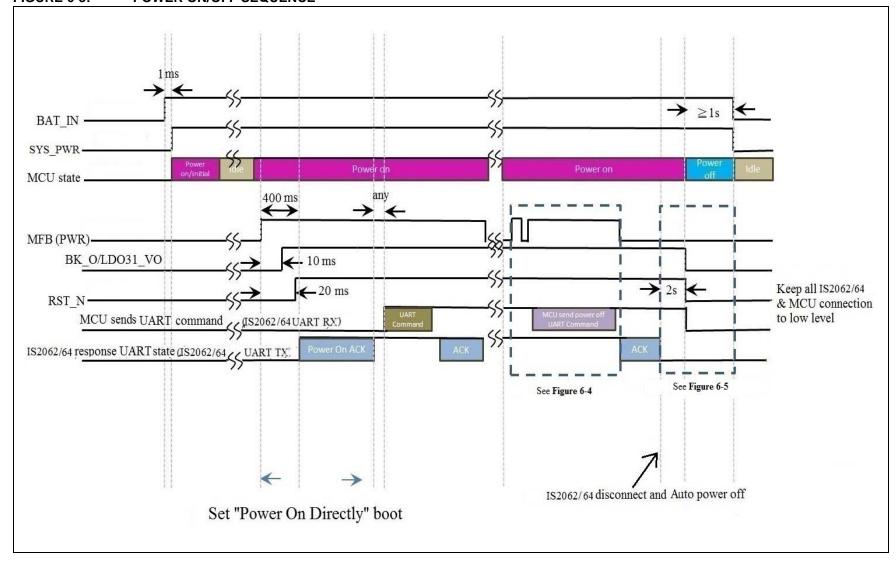

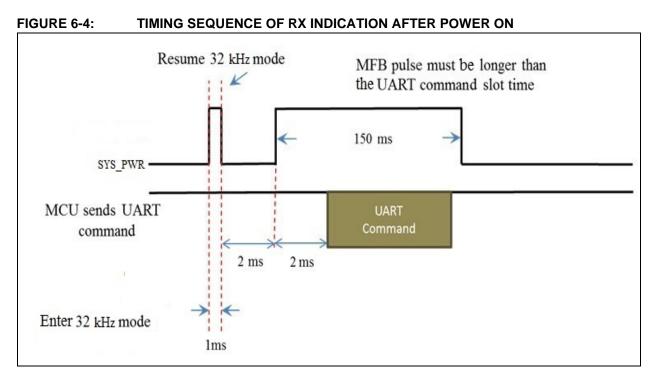

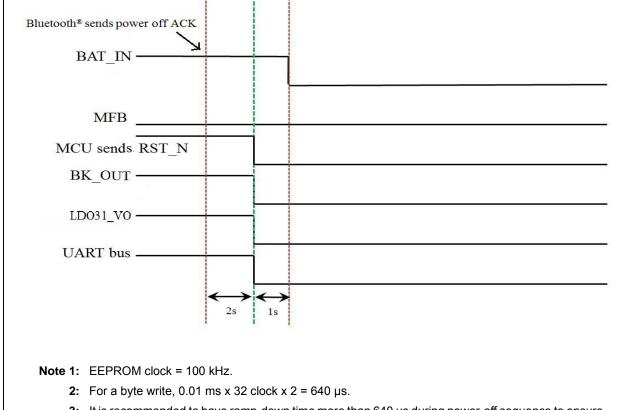

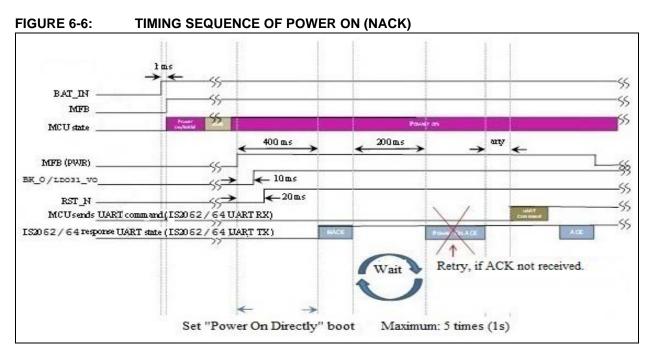

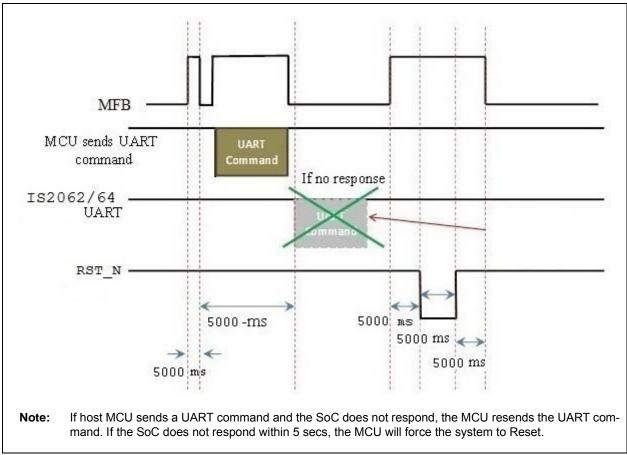

Figure 6-3 through Figure 6-8 illustrate the various UART control signal timing sequences.

**|S2062/64**

**3:** It is recommended to have ramp-down time more than 640 µs during power-off sequence to ensure safe operation of the device.

FIGURE 6-7: RESET TIMING SEQUENCE IN CASE OF NO RESPONSE FROM SOC TO HOST MCU

### FIGURE 6-8: TIMING SEQUENCE OF POWER DROP PROTECTION

## 6.3 Configuring and Programming

Configuration and firmware programming modes are entered according to the system configuration I/O pins.Table 6-1 provides the system configuration settings. The P2\_0, P2\_4 and EAN pins have internal pull ups.

TABLE 6-1:SYSTEM CONFIGURATION SETTINGS

| P2_0 | P2_4 | EAN                             | Operating Mode              |

|------|------|---------------------------------|-----------------------------|

| High | High | Flash code: Low; ROM code: High | APP mode (Normal operation) |

| Low  | High | Flash code: Low; ROM code: High | Test mode (Write EEPROM)    |

| Low  | Low  | High                            | Write Flash                 |

### 6.4 General Purpose I/O Pins

The IS2062 SoC provides 10 GPIOs and the IS2064 SoC provides 15 GPIOs, and these GPIOs can be configured using the UI tool. Table 6-2 through Table 6-5 provide the GPIO configuration details of the IS2062/64 SoC.

The MFB pin must be configured as the power on/off key and the remaining pins can be configured for any one of the default functions as provided in Table 6-2 and Table 6-3.

# TABLE 6-2:IS2062 I/O PIN<br/>CONFIGURATION

| I/O Pin Name | Default Functions |

|--------------|-------------------|

| MFB          | Power on/off      |

| P0_2         | Play/Pause        |

| P2_7         | Volume Up         |

| P0_5         | Volume Down       |

| P0_1         | FWD               |

| P0_3         | REV               |

#### TABLE 6-3: IS2064 I/O PIN CONFIGURATION

| I/O Pin Name | Default Functions |

|--------------|-------------------|

| MFB          | Power on/off      |

| P0_2         | Play/Pause        |

| P2_7         | Volume Up         |

| P0_5         | Volume Down       |

| P3_3         | FWD               |

| P3_1         | REV               |

Some pins can be configured to indicate or control the external devices. The most popular applications are NFC for easy pairing and Buzzer for indication and external audio amplifier for loud speaker.

# TABLE 6-4:IS2062 I/O PIN (FOR<br/>ADDITIONAL FUNCTIONS)

| I/O Configurable<br>Features | Functions           |

|------------------------------|---------------------|

| P1_5                         | Slide switch        |

| P0_4                         | NFC detect          |

| P0_4 / P1_5                  | External AMP enable |

# TABLE 6-5:IS2064 I/O PIN FOR ADDED<br/>FUNCTIONS

| I/O Configurable<br>Features | Functions           |

|------------------------------|---------------------|

| P1_5                         | Slide switch        |

| P0_4                         | NFC detect          |

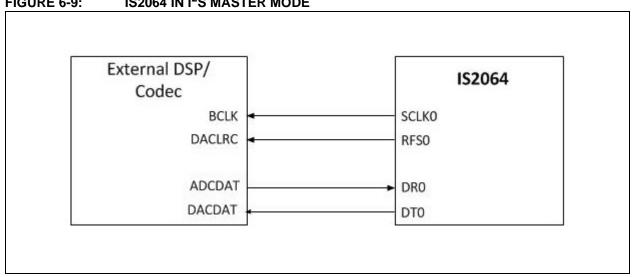

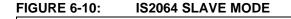

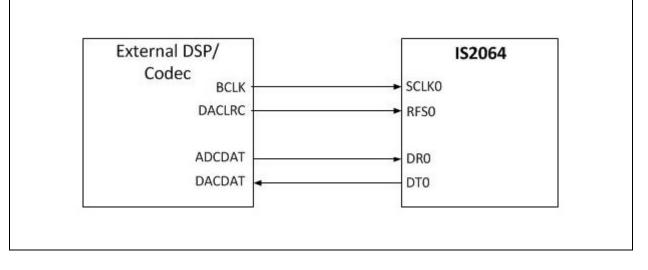

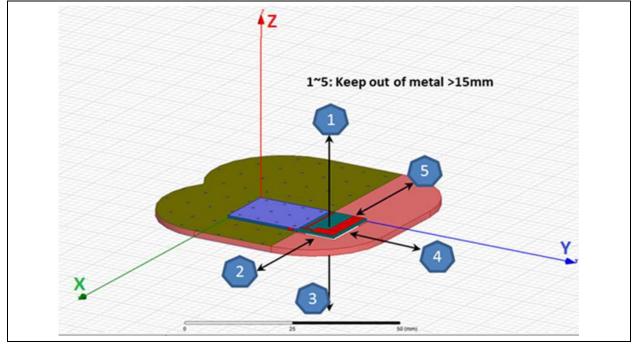

| P0_4 / P1_5                  | External AMP enable |