# OCTAL SERIAL SOLENOID DRIVER

- EIGHT LOW R<sub>DSon</sub> DMOS OUTPUTS  $(0.5\Omega \text{ AT I}_{O} = 1A @ 25^{\circ}\text{C V}_{CC} = 5\text{V}\pm 5\%)$

- 8 BIT SERIAL INPUT DATA (SPI)

- 8 BIT SERIAL DIAGNOSTIC OUTPUT FOR OVERLOADAND OPENCIRCUIT CONDITIONS

- OUTPUT SHORT CIRCUIT PROTECTION

- CHIP ENABLE SELECT FUNCTION (active low)

- INTERNAL 36V CLAMPING FOR EACH OUT-PUT

- CASCADABLE WITH ANOTHER OCTAL DRIVER

- LOW QUIESCENT CURRENT (10mA MAX.)

- PACKAGE PowerSO20

### **DESCRIPTION**

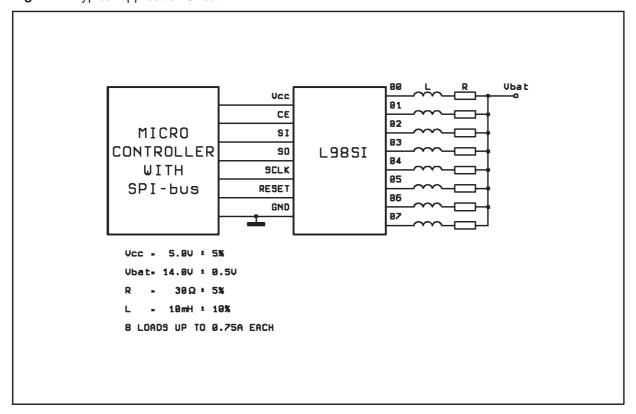

The L98SI is an octal low side solenoiddriver rea lized in Multipower-BCD technologyparticularly suited for driving lamps, relays and solenoids in indu-

### **MULTIPOWER BCD TECHNOLOGY**

strial environment. The L98SI DMOS outputs have very low power consumption.

Data is transmitted serially to the device using the Serial Peripheral Interface (SPI) protocol.

The L98SI features the outputs status monitoring function.

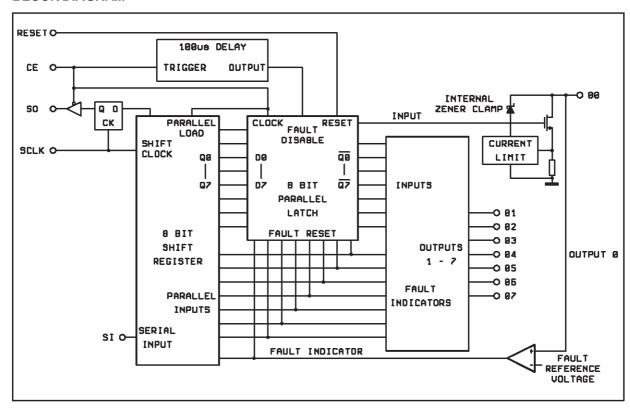

### **BLOCK DIAGRAM**

April 1998 1/9

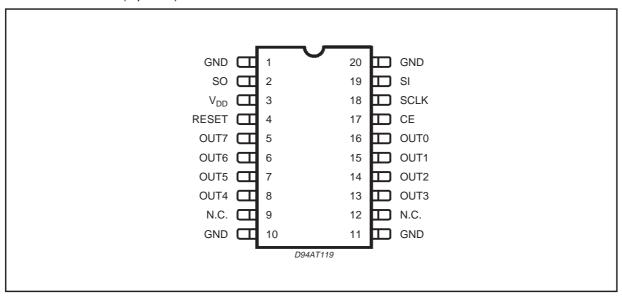

# **PIN CONNECTION** (top view)

# **ABSOLUTE MAXIMUM RATINGS**

| Symbol                            | Parameter                                                                                                | Val          | Unit |          |

|-----------------------------------|----------------------------------------------------------------------------------------------------------|--------------|------|----------|

| $V_{DD}$                          | DC Logic Supply                                                                                          | - 0.7        | 7    | V        |

| Vo                                | Output Voltage                                                                                           | internally   | V    |          |

| lı                                | Input Transient Current (CE, SI, SCLK, RESET, SO): Duration Time $t = 1s$ , $V_{I} < 0$ $V_{I} > V_{CC}$ | - 25         | + 25 | mA<br>mA |

| l <sub>Odc</sub>                  | Continuous Output Current (for each output)                                                              | Int. Limited |      | Α        |

| T <sub>j</sub> , T <sub>stg</sub> | Junction and Storage Temperature Range                                                                   | - 40         | 150  | °C       |

| E <sub>X</sub>                    | Max Clamping Energy (for each output)                                                                    |              | 200  | mJ       |

# THERMAL DATA

| Symbol                 | Parameter                           |      | Value | Unit |

|------------------------|-------------------------------------|------|-------|------|

| R <sub>th j-case</sub> | Thermal Resistance Junction-Case    | Max. | 1.5   | °C/W |

| R <sub>th j-amb</sub>  | Thermal Resistance Junction-Ambient | Max. | 60    | °C/W |

### PIN DESCRIPTION

Vcc

Logic supply voltage - nominally 5V

### **GROUND**

Device Ground. This ground applies for the logic circuits as well as the power output stages.

#### RESET

Asynchronous reset for the output stages, the parallel latch and the shift register inside the L98SI. This pin is active low and it must not be left floating. A power on clear function may be implemented connecting this pin to  $V_{CC}$  with an external resistor and to ground with an external capacitor.

### CE

Chip Enable. Data is transferred from the shift registers to the outputs on the rising edge of this signal. The falling edge of this signal sets the shift register with the output voltage sense bits coming from the output stages. The output driver for the SO pin is enabled when this pin is low.

### SO

Serial Output. This pin is the serial output from the shift register and it is tri-stated when CE is high. A high for a data bit on this pin indicates that the par-

ticular output is high. A low on this pin for a data bit indicates that the output is low.

Comparing the serial output bits with the previous serial input bits the external microcontroller implements the diagnostic data supplied by the L98SI.

### SI

Serial Input. This pin is the serial data input. A high on thispin will program a particular output to be OFF, while a low will turn it ON.

#### SCI K

Serial Clock. This pin clocks the shift register. New SO data will appear on every rising edge of this pin and new SI data will be latched on every SCLK's falling edge into the shift register.

### **OUTPUTS 00-07**

Power output pins. The input and output bits corresponding to 07 are sent and received first via the SPI bus and 00 is the last. The outputs are provided with current limiting and voltage sense functions for fault indication and protection. The nominal load current for these outputs is 500mA, but the current limiting is set to a minimum of 1.05A. The outputs also have on board clamps set at about 36V for recirculation of inductive load current.

# **ELECTRICAL CHARACTERISTICS** ( $V_{CC} = 5V \pm 5\%$ . $T_i = -40$ to $125^{\circ}C$ ; unless otherwise specified)

| Symbol             | Parameter                                            | Test Conditions                                                                 | Min. | Тур.                 | Max.        | Unit        |

|--------------------|------------------------------------------------------|---------------------------------------------------------------------------------|------|----------------------|-------------|-------------|

| Voc                | Output Clamping Volt.                                | I <sub>O</sub> = 0.5A, Output Programmed OFF                                    | 30   |                      | 40          | V           |

| I <sub>Oleak</sub> | Out. Leakage Current                                 | $V_O = 24V$ , Output Progr. OFF                                                 |      |                      | 1           | mA          |

| R <sub>DSon</sub>  | On Resistance                                        | Output Progr. ON $I_O = 0.5A$ $I_O = 0.8A$ $I_O = 1A$ With Fault Reset Disabled |      | 0.55<br>0.55<br>0.55 | 1<br>1<br>1 | Ω<br>Ω<br>Ω |

| l <sub>OL</sub>    | Out. Self Limiting<br>Current                        | Output Progr. ON                                                                | 1.05 |                      |             | А           |

| t <sub>PHL</sub>   | Turn-on Delay                                        | I <sub>O</sub> = 500mA<br>No Reactive Load                                      |      |                      | 10          | μS          |

| t <sub>P</sub>     | Turn-off Delay                                       | I <sub>O</sub> = 500mA<br>No Reactive Load                                      |      |                      | 10          | μS          |

| Voref              | Fault Refer. Voltage                                 | Output Progr. OFF Fault detected if V <sub>O</sub> > V <sub>OREF</sub>          | 1.6  |                      | 2           | ٧           |

| t <sub>UD</sub>    | Fault Reset Delay<br>(after CE L to H<br>transition) | See fig. 3                                                                      | 75   |                      | 250         | μs          |

| V <sub>OFF</sub>   | Output OFF Voltage                                   | Output Pin Floating.cOutput Progr. OFF,                                         |      |                      | 1.0         | V           |

# **ELECTRICAL CHARACTERISTICS** (Continued)

| Symbol                                     | Parameter                                        | Test Conditions                      | Min.               | Тур. | Max.                       | Unit |

|--------------------------------------------|--------------------------------------------------|--------------------------------------|--------------------|------|----------------------------|------|

| INPUT BUFFER (SI, CE, SCLK and RESET pins) |                                                  |                                      |                    |      |                            |      |

| V <sub>T</sub>                             | Threshold Voltage at Falling Edge SCLK only      | $V_{CC} = 5V \pm 10\%$               | 0.2V <sub>CC</sub> |      |                            | V    |

| V <sub>T+</sub>                            | Threshold Voltage at<br>Rising Edge<br>SCLK only | $V_{CC} = 5V \pm 10\%$               |                    |      | 0.7V <sub>CC</sub><br>4.15 | V    |

| V <sub>H</sub>                             | Hysteresis Voltage                               | $V_{T+} - V_{T-}$                    | 0.85               |      | 2.5                        | V    |

| II                                         | Input Current                                    | $V_{CC} = 5.50V, 0 < V_{I} < V_{CC}$ | - 10               |      | + 10                       | μΑ   |

| Cı                                         | Input Capacitance                                | $0 < V_I < V_{CC}$                   |                    |      | 20                         | nF   |

# OUTPUT BUFFER (SO pin)

| $V_{SOL}$         | Output LOW Voltage                                 | I <sub>O</sub> = 1.6mA                                        |                        | 0.4 | V  |

|-------------------|----------------------------------------------------|---------------------------------------------------------------|------------------------|-----|----|

| V <sub>SOH</sub>  | Output HIGH Voltage                                | $I_O = 0.8$ mA                                                | V <sub>CC</sub> – 1.3V |     | V  |

| I <sub>SOtl</sub> | Output Tristate Leakage<br>Current                 | $0 < V_O < V_{CC}$ , CE Pin Held High, $V_{CC} = 5.25V$       | - 20                   | 20  | μΑ |

| Cso               | Output Capacitance                                 | 0 < V <sub>O</sub> < V <sub>CC</sub><br>CE Pin Held High      |                        | 20  | pF |

| Icc               | Quiescent Supply<br>Current at V <sub>CC</sub> Pin | All Outputs Progr. ON. $I_O = 0.5A$ per Output Simultaneously |                        | 10  | mA |

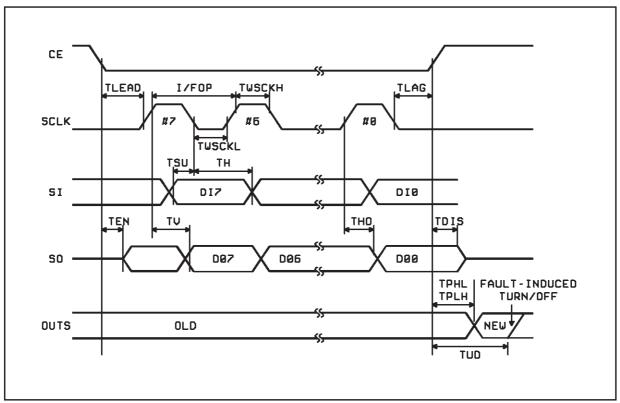

# SERIAL PERIPHERAL INTERFACE (see fig. 2, timing diagram)

| f <sub>op</sub>   | Operating Frequency                    |                                                              | D.C. | 2  | MHz |

|-------------------|----------------------------------------|--------------------------------------------------------------|------|----|-----|

| t <sub>lead</sub> | Enable Lead Time                       |                                                              | 250  |    | ns  |

| t <sub>lag</sub>  | Enable Lag Time                        |                                                              | 250  |    | ns  |

| twsckh            | Clock HIGH Time                        |                                                              | 200  |    | ns  |

| twsckl            | Clock LOW Time                         |                                                              | 200  |    | ns  |

| t <sub>su</sub>   | Data Setup Time                        |                                                              | 75   |    | ns  |

| t <sub>H</sub>    | Data Hold Time                         |                                                              | 75   |    | ns  |

| t <sub>EN</sub>   | Enable Time                            |                                                              | 250  |    | ns  |

| t <sub>DIS</sub>  | Disable Time                           |                                                              | 250  |    | ns  |

| t <sub>V</sub>    | Data Valid Time                        |                                                              | 100  |    | ns  |

| t <sub>rSO</sub>  | Rise Time (SO output)                  | $V_{CC}$ = 20 to 70% $C_L$ = 200pF                           |      | 50 | ns  |

| t <sub>fSO</sub>  | Fall Time (SO output)                  | $V_{CC} = 70 \text{ to } 20\% \text{ C}_{L} = 200 \text{pF}$ |      | 50 | ns  |

| t <sub>rSI</sub>  | Rise Time SPI<br>Inputs (SCK, SI, CE)  | $V_{CC}$ = 20 to 70% $C_L$ = 200pF                           | 200  |    | ns  |

| t <sub>fSI</sub>  | Fall Time SPI<br>Inputs (SCLK, SI, CE) | $V_{CC}$ = 70 to 20% $C_L$ = 200pF                           | 200  |    | ns  |

| t <sub>ho</sub>   | Output Data Hold Time                  |                                                              | 0    |    | μS  |

### **FUNCTIONAL DESCRIPTION**

The L98SI DMOS output is a low operating power device featu-ring, eight  $1\Omega$  R<sub>DSON</sub> DMOS drivers with transient protection circuits in output stages. Each channel is independently controlled by an output latch and a common RESET line which disables all eightoutputs. The driver has low saturation and short circuit protection and can drive inductive and resistive loads such as solenoids, lamps and relais. Data is transmitted to the device serially using the Serial Peripheral Interface (SPI) protocol. The circuit receives 8 bit serial databy means of the serial input (SI) which is stored in an internal register to control the output drivers. The serial output (SO) provides 8 bit of diagnostic data representing the voltage level at the driver output. This allows the microprocessor to diagnose the condition of the output drivers.

The output saturation voltage is monitored by a comparator for an out of saturation condition and is able to unlatch the particular driver through the fault reset line. This circuit is also cascadable with another octal driver in order to jam 8 bit multiple data. The device is selected when the chip enable (CE) line is low.

Additionally the (SO) is placed in a tri-state mode when the device is deselected. The negative edge of the (CE) transfers the voltage level of the drivers to the shift register and the positive edge of the (CE) latches the new data from the shift register to the drivers. When CE is Low, data bit contained into the shift register is transferred to SO output at every SCLK positive transition while data bit present at SI input is latched into the shift register on every SCLK negative transition.

### **Internal Blocks Description**

The internal architecture of the device is based on the three internal major blocks: the octal shift register for talking to the SPI bus, the octal latch for holding control bits written into the device and the octal load driver array.

# **Shift Register**

The shift register has both serial and parallel inputs and serial and parallel outputs. The serial input accepts data from the SPI bus and the serial output simultaneously sends data into the SPI bus. The parallel outputs are latched into the parallel latch inside the L98SI at the end of a data transfer. The parallel inputsjam diagnostic data into the shift register at the beginning of a data transfer cycle.

# **Parallel Latch**

The parallel latch holds the input data from the shift register. This data then actuates the output stages.

Individual registers in the latch may be cleared by fault conditions in order to protect the overloaded output stages. The entire latch may also be cleared by the RESET signal.

### **Output Stages**

The output stages provide an active low drive signal suitable for 0.75A continuous loads. Each output has a current limit circuit which limits the maximum output current to at least 1.05A to allow for high inrush currents. Additionally, the outputs have internal zeners set to 36 volts to clamp inductive transients at turn-off. Each output also has a voltage comparator observing the output node. If the voltage exceeds 1.8V on an ON output pin, a fault condition is assumed and the latch driving this particular stage is reset, turning the output OFF to protect it. The timing of this action is described below. These comparators also provide diagnostic feedback data to the shift register. Additionally, the comparators contain an internal pulldown current which will cause the cell to indicate a low output voltage if the output is programmed OFF and the output pin is open circuited.

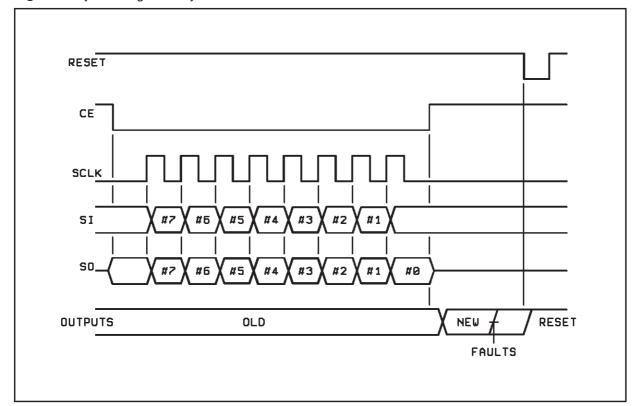

### TIMING DATA TRANSFER

Figure #2 shows the overall timing diagram from a byte transfer to and from the L98SI using the SPI bus.

# **CE High to Low Transition**

The action begins when the Chip Enable (CE) pin is pulled low. The tri-state Serial Output (SO) pin driver will be enabled entire time that CE is low. At the falling edge of the CE pin, the diagnostic data from the voltage comparators in the output stages will be latched into the shift register. If a particular output is high, a logic one will be jammed into that bit in the shift register. If the output is low, a logic zero will be loaded there. The most significant bit (07) should be presented at the Serial Input (SI) pin. A zero at this pin will program an output ON, while a one will program the output OFF.

# **SCLK Transitions**

The Serial Clock (SCLK) pin should then be pulled high. At this point the diagnostic bit from the most significant output (07) will appear at the SO pin. A high here indicates that the 07 pin is higher than 1.8V. The SCLK pin should then be toggled low then high. New SO data will appear following every rising edge of SCLK and new SI data will be latched into the L98SI shift register on the falling edges. An unlimited amount of data may be shifted through the device

shift register (into the SI pin and out the SO pin), allowing the other SPI devices to be cascaded in a daisy chain with the L98SI.

# **CE Low to High Transition**

Once the last data bit has been shifted into the L98SI, the CE pin should be pulled high.

At the rising edge of CE the shift register data is latched into the parallel latch and the output stages will be actuated by the new data. An internal 160µs delay timer will also be started at this rising edge (see  $t_{UD}$ ). During the 160µs period, the outputs will be protected only by the analog current limiting circuits since the resetting of the parallel latches by faults conditions will be inhibited during this period. This allows the part to overcome any high inrush currents that may flow immediately after turn on. Once the delay period has elapsed, the output voltages are sensed by the comparators and any output with voltages higher than 1.8V are latched OFF. It should be noted that the SCLK pin should be low at both tran-

sitions of the CE pin to avoid any false clocking of the shift register. The SCLK input is gated by the CE pin, so that the SCLK pin is ignored whenever the CE pin is high.

# **FAULT CONDITIONS CHECK**

Checking for fault conditions may be done in the following way. Clock in a new control byte. Wait 160 microseconds or so to allow the outputs to settle. Clock in the same control byte and observe the diagnostic data that comes out of the device. The diagnostic bits should be identical to the bits that were first clocked in. Any differences would point to a fault on that output. If the output was programmed ON by clocking in a zero, and a one came back as the diagnostic bit for that output, the output pin was still high and a short circuit or overload condition exists. If the output was programmed OFF by clocking in a one, and a zero came back as the diagnostic bit for that output, nothing had pulled the output pin high and it

Figure 2 : Timing Diagram.

Figure 3: Typical Application Circuit.

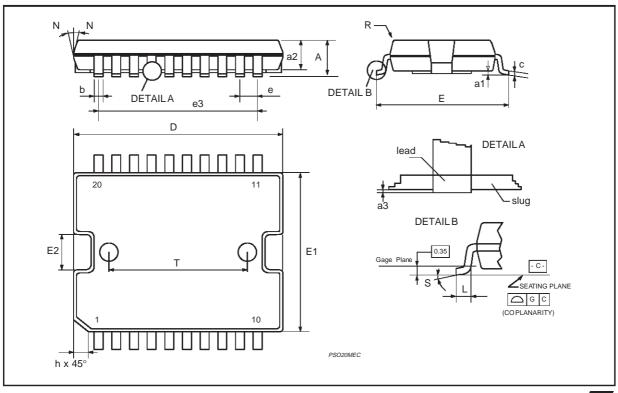

# POWERSO20 PACKAGE MECHANICAL DATA

| DIM.   |      | mm         |      |       | inch  |       |  |

|--------|------|------------|------|-------|-------|-------|--|

| DIWI.  | MIN. | TYP.       | MAX. | MIN.  | TYP.  | MAX.  |  |

| Α      |      |            | 3.6  |       |       | 0.142 |  |

| a1     | 0.1  |            | 0.3  | 0.004 |       | 0.012 |  |

| a2     |      |            | 3.3  |       |       | 0.130 |  |

| a3     | 0    |            | 0.1  | 0.000 |       | 0.004 |  |

| b      | 0.4  |            | 0.53 | 0.016 |       | 0.021 |  |

| С      | 0.23 |            | 0.32 | 0.009 |       | 0.013 |  |

| D (1)  | 15.8 |            | 16   | 0.622 |       | 0.630 |  |

| D1     | 9.4  |            | 9.8  | 0.370 |       | 0.386 |  |

| E      | 13.9 |            | 14.5 | 0.547 |       | 0.570 |  |

| е      |      | 1.27       |      |       | 0.050 |       |  |

| e3     |      | 11.43      |      |       | 0.450 |       |  |

| E1 (1) | 10.9 |            | 11.1 | 0.429 |       | 0.437 |  |

| E2     |      |            | 2.9  |       |       | 0.114 |  |

| E3     | 5.8  |            | 6.2  | 0.228 |       | 0.244 |  |

| G      | 0    |            | 0.1  | 0.000 |       | 0.004 |  |

| Н      | 15.5 |            | 15.9 | 0.610 |       | 0.626 |  |

| L      | 0.8  |            | 1.1  | 0.031 |       | 0.043 |  |

| N      |      | 10° (max.) |      |       |       |       |  |

| S      |      |            | 8° ( | (max) |       |       |  |

| Т      |      | 10         |      |       | 0.394 |       |  |

- (1) "D and F" do not include mold flash or protrusions.Mold flash or protrusions shall not exceed 0.15 mm (0.006").Critical dimensions: "E", "G" and "a3"

Information furnished is believed to be accurate and reliable. However, SGS-THOMSON Microelectronics assumes no responsibility for the consequences of use of such information nor for any infringement of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of SGS-THOMSON Microelectronics. Specification mentioned in this publication are subject to change without notice. This publication supersedes and replaces all information previously supplied. SGS-THOMSON Microelectronics products are not authorized for use as critical components in life support devices or systems without express written approval of SGS-THOMSON Microelectronics.

© 1998 SGS-THOMSON Microelectronics – Printed in Italy – All Rights Reserved PowerSO-20™ is a Trademark of SGS-THOMSON Microelectronics

### SGS-THOMSON Microelectronics GROUP OF COMPANIES

Australia - Brazil - Canada - China - France - Germany - Italy - Japan - Korea - Malaysia - Malta - Morocco - The Netherlands - Singapore - Spain - Sweden - Switzerland - Taiwan - Thailand - United Kingdom - U.S.A.