# **Three-Phase Brushless Motor Driver**

#### Overview

The LB1692 is a three-phase brushless motor driver IC. It is optimal for use with DC fan motors in equipment such as air conditioners or water heaters. The LB1692 is a high-breakdown voltage version of the LB1690.

#### **Functions and Features**

- Three-phase brushless motor driver

- 60 V breakdown voltage, 2.5 A output current

- Built-in current limiter

- Built-in low voltage protection circuit

- Built-in thermal protection circuit

- Built-in Hall amplifier with hysteresis

- FG output function

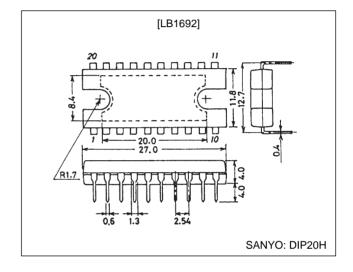

## **Package Dimensions**

unit: mm

#### 3037A-DIP20H

# **Specifications**

### Absolute Maximum Ratings at $Ta = 25^{\circ}C$

| Parameter                   | Symbol              | Conditions                          | Ratings     | Unit |

|-----------------------------|---------------------|-------------------------------------|-------------|------|

| NA-vi-                      | V <sub>CC</sub> max |                                     | 10          | V    |

| Maximum supply voltage      | V <sub>M</sub> max  |                                     | 60          | V    |

| Output current              | Io                  |                                     | 2.5         | А    |

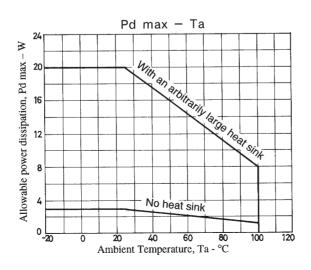

| All II P. C.                | Pd max1             | Independent IC                      | 3           | W    |

| Allowable power dissipation | Pd max2             | With an arbitrarily large heat sink | 20          | W    |

| Operating temperature       | Topr                |                                     | -20 to +100 | °C   |

| Storage temperature         | Tstg                |                                     | -55 to +150 | °C   |

### Allowable Operating Ranges at $Ta = 25^{\circ}C$

| Parameter            | Symbol          | Conditions | Ratings    | Unit |

|----------------------|-----------------|------------|------------|------|

| Cumply weltage range | V <sub>CC</sub> |            | 4.5 to 5.5 | V    |

| Supply voltage range | V <sub>M</sub>  |            | 5 to 56    | V    |

# Electrical Characteristics at Ta = 25°C, $V_{CC}$ = 5 V, $V_{M}$ = 45 V

| Parameter                                |            | Symbol              | Conditions                             | min  | typ  | max        | Unit |

|------------------------------------------|------------|---------------------|----------------------------------------|------|------|------------|------|

| Current drain                            |            | I <sub>CC1</sub>    | When stopped                           |      | 4    | 6          | mA   |

|                                          |            | I <sub>CC2</sub>    |                                        |      | 10   | 15         | mA   |

| Output saturation voltage                |            | V <sub>O</sub> sat1 | $I_O = 1 A, V_O (sink) + V_O (source)$ |      | 2.1  | 3.0        | V    |

|                                          |            | V <sub>O</sub> sat2 | $I_O = 2 A, V_O (sink) + V_O (source)$ |      | 3.0  | 4.2        | V    |

| Output leakage curi                      | rent       | I <sub>O</sub> leak |                                        |      |      | 100        | μA   |

| [Hall amplifier]                         |            |                     |                                        |      |      |            |      |

| Input bias current                       |            | I <sub>HB</sub>     |                                        |      | 1    | 4          | μA   |

| Common mode inpurange                    | ut voltage |                     |                                        | 1.5  |      | 3.2        | V    |

| Hysteresis                               |            | $\Delta V_{IN}$     |                                        | 23   | 30   | 37         | mV   |

| Input voltage                            |            | V <sub>SLH</sub>    | $L \rightarrow H$                      | 5    | 15   | 25         | mV   |

|                                          |            | V <sub>SHL</sub>    | $H \rightarrow L$                      | -25  | -15  | <b>-</b> 5 | mV   |

| [FG pin] (Speed pul                      | se output) |                     |                                        |      |      |            |      |

| Output low level voltage                 |            | V <sub>FGL</sub>    | I <sub>FG</sub> = 5 mA                 |      | 0.16 | 0.4        | V    |

| Pull-up resistance                       |            | R <sub>FG</sub>     |                                        | 7.5  | 10   | 12.5       | kΩ   |

| Forward, reverse, and stop operation     | Forward    | V <sub>FSR1</sub>   |                                        |      | 0    | 0.8        | V    |

|                                          | Stop       | V <sub>FSR2</sub>   |                                        | 2.1  | 2.5  | 2.9        | V    |

|                                          | Reverse    | V <sub>FSR3</sub>   |                                        | 4.2  | 5.0  |            | V    |

| Current control operation limiter        |            | V <sub>Rf</sub>     |                                        | 0.42 | 0.5  | 0.6        | V    |

| Thermal cutoff operating temperature     |            | T <sub>SD</sub>     | Design target value                    | 150  | 180  |            | °C   |

| Hysteresis                               |            | $\Delta T_{\sf SD}$ |                                        |      | 25   |            | °C   |

| Low voltage protection operating voltage |            | V <sub>LVSD</sub>   |                                        | 3.5  | 3.8  | 4.1        | V    |

| Hysteresis                               |            | $\Delta V_{LVSD}$   |                                        | 0.2  | 0.3  | 0.4        | V    |

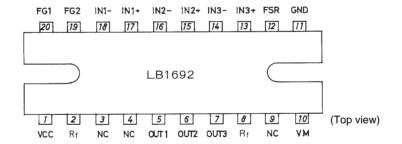

### **Pin Assignment**

### **Truth Table**

| Item | Source → Sink | Input |     |     | Forward/Reverse Control |  |

|------|---------------|-------|-----|-----|-------------------------|--|

|      | Source → Sink | IN1   | IN2 | IN3 | FSR                     |  |

| 1    | OUT3 → OUT2   | н     | н   | L   | L                       |  |

|      | OUT2 → OUT3   |       |     |     | Н                       |  |

| 2    | OUT3 → OUT1   | Н     | L   | L   | L                       |  |

| 2    | OUT1 → OUT3   |       |     |     | Н                       |  |

| 3    | OUT2 → OUT3   |       | L   | Н   | L                       |  |

|      | OUT3 → OUT2   |       |     |     | Н                       |  |

| 4    | OUT1 → OUT2   |       | Н   |     | L                       |  |

|      | OUT2 → OUT1   |       |     | _   | Н                       |  |

| 5    | OUT2 → OUT1   | Н     | L   | Н   | L                       |  |

|      | OUT1 → OUT2   | "     |     |     | Н                       |  |

| 6    | OUT1 → OUT3   |       | н   | Н   | L                       |  |

|      | OUT3 → OUT1   | ] L   |     |     | Н                       |  |

FSR

Forward: L (0 to 0.8 V) Reverse: H (4.2 to 5.0 V)

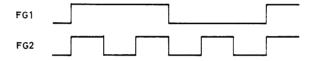

### **FG Output**

# **Block Diagram and Peripheral Circuits**

#### **Pin Functions**

| Pin                                    | Pin No.                    | Function                                                                                                                                                                                                                                                                                 |  |

|----------------------------------------|----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| IN1+, IN1-<br>IN2+, IN2-<br>IN3+, IN3- | 17, 18<br>15, 16<br>13, 14 | OUT1: A logic high level indicates that the Hall device input pins are in the state IN+ > IN  OUT2: A logic high level indicates that the Hall device input pins are in the state IN+ > IN  OUT3: A logic high level indicates that the Hall device input pins are in the state IN+ > IN |  |

| OUT1<br>OUT2<br>OUT3                   | 5<br>6<br>7                | Output pin 1 Output pin 2 Output pin 3                                                                                                                                                                                                                                                   |  |

| V <sub>CC</sub>                        | 1                          | Power supply for all sections other than the output block                                                                                                                                                                                                                                |  |

| V <sub>M</sub>                         | 10                         | Power supply that provides the output power                                                                                                                                                                                                                                              |  |

| Rf                                     | 2, 8                       | Output current detection pin. The output current is converted to a voltage for detection by a resistor connected between this pin and GND.                                                                                                                                               |  |

| GND                                    | 11                         | Ground for all sections other than the output block The Rf pin voltage will be the lowest output transistor potential.                                                                                                                                                                   |  |

| FSR                                    | 12                         | Forward/stop/reverse control pin The voltage on this pin controls the IC forward, stop, or reverse operation. Forward: 0 to 0.8 V Stop: 2.1 to 2.9 V Reverse: 4.2 to 5.0 V                                                                                                               |  |

| FG1<br>FG2                             | 20<br>19                   | Speed pulse output pin 1. A pull-up resistor is built in. Speed pulse output pin 2. A pull-up resistor is built in.                                                                                                                                                                      |  |

#### 1. Position Detection Circuit (Hall device input circuit)

The position detection circuit is a differential amplifier with hysteresis (typically 30 mV).

Voltages within the common mode input voltage range (1.5 V to  $V_{CC} - 1.8$  V) should be used as the operating DC level. We recommend using an input level that is more than three times the hysteresis, i.e., on the order of 120 to 160 mVp-p.

#### 2. Current Control Circuit

Current control is performed by switching the sink side transistor from the saturated to the unsaturated range. Therefore, it is possible for ASO to be a problem.

$$I = \frac{V_{Rf}}{Rf}$$

(A)

Therefore, if at all possible, applications should be designed so that the current limiter does not operate. Also, be especially careful to design applications so that the maximum output current (2.5 A) is not exceeded when the current limiter operates. Note that a current limiter must be added to the  $V_M$  power supply. (We recommend a current limiter with a short delay time and with a design current that is about 60 to 70% of the current control circuit's current value.)

#### 3. Protection Circuits

• Low voltage protection circuit

The sink side output drivers are turned off if the  $V_{CC}$  pin voltage falls below the stipulated range. This circuit is provided to prevent incorrect operation.

· Thermal cutoff protection circuit

If the junction temperature exceeds the stipulated temperature range, the sink side output drivers are turned off. This is identical to the operation of the circuit described in 3-1 above.

#### 4. V<sub>M</sub> power supply minimum voltage

The  $V_{M}$  power supply voltage should be greater than or equal to the  $V_{CC}$  voltage.

$$V_{\rm M} \ge V_{\rm CC}$$

#### 5. FG Output Circuit

The position detection inputs IN1, IN2, and IN3 are combined and the output is generated using waveform shaping. The frequencies of those outputs are proportional to the rotational speed signal, and, as seen from the position detectors, are equal to the input frequency itself (FG1) and three times the input frequency (FG2).

- No products described or contained herein are intended for use in surgical implants, life-support systems, aerospace equipment, nuclear power control systems, vehicles, disaster/crime-prevention equipment and the like, the failure of which may directly or indirectly cause injury, death or property loss.

- Anyone purchasing any products described or contained herein for an above-mentioned use shall:

- ① Accept full responsibility and indemnify and defend SANYO ELECTRIC CO., LTD., its affiliates, subsidiaries and distributors and all their officers and employees, jointly and severally, against any and all claims and litigation and all damages, cost and expenses associated with such use:

- ② Not impose any responsibility for any fault or negligence which may be cited in any such claim or litigation on SANYO ELECTRIC CO., LTD., its affiliates, subsidiaries and distributors or any of their officers and employees jointly or severally.

- Information (including circuit diagrams and circuit parameters) herein is for example only; it is not guaranteed for volume production. SANYO believes information herein is accurate and reliable, but no guarantees are made or implied regarding its use or any infringements of intellectual property rights or other rights of third parties.

This catalog provides information as of July, 1998. Specifications and information herein are subject to change without notice.