## **Three-Phase Brushless Motor Driver IC**

#### Overview

The LB1881M is a three-phase brushless motor driver IC designed for use as a camcorder capstan or drum motor driver, or as a digital audio tape player/recorder motor driver.

#### **Features**

- 120° voltage linear system

- Appropriate for portable applications, since the LB1881M reduces system power requirements by using motor voltage control for speed control.

- Built-in torque ripple compensation circuit

- Small external capacitances due to the adoption of a soft switching technique (chip capacitor).

- Built-in thermal shutdown circuit

- Built-in FG amplifier

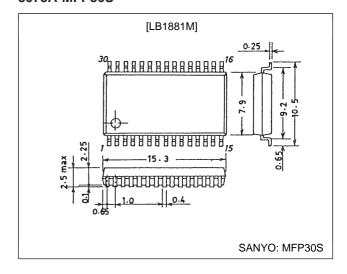

## **Package Dimensions**

unit: mm

#### 3073A-MFP30S

# **Specifications**

#### **Absolute Maximum Ratings at Ta = 25^{\circ}C**

| Parameter                   | Symbol                | Conditions     | Ratings            | Unit |

|-----------------------------|-----------------------|----------------|--------------------|------|

|                             | V <sub>CC</sub> 1 max |                | 7                  | V    |

| Supply voltage              | V <sub>CC</sub> 2 max |                | 12                 | V    |

|                             | V <sub>S</sub> max    |                | V <sub>CC</sub> 2  | V    |

| Output applied voltage      | V <sub>O</sub> max    |                | V <sub>S</sub> + 2 | V    |

| Input applied voltage       | V <sub>I</sub> max    | All input pins | V <sub>CC</sub> 1  | V    |

| Output current              | I <sub>O</sub> max    |                | 1.0                | А    |

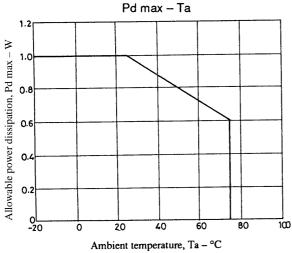

| Allowable power dissipation | Pd max                |                | 1.0                | W    |

| Operating temperature       | T <sub>opr</sub>      |                | -20 to +75         | °C   |

| Storage temperature         | T <sub>stg</sub>      |                | -55 to +150        | °C   |

#### Allowable Operating Ranges at $Ta = 25^{\circ}C$

| Parameter      | Symbol            | Conditions            | Ratings                 | Unit |

|----------------|-------------------|-----------------------|-------------------------|------|

|                | V <sub>CC</sub> 1 | $V_{CC}1 \le V_{CC}2$ | 4.0 to 6.0              | V    |

| Supply voltage | V <sub>CC</sub> 2 |                       | 4 to 10                 | V    |

|                | Vs                |                       | Up to V <sub>CC</sub> 2 | V    |

#### LB1881M

# Electrical Characteristics at $Ta=25^{\circ}C,\,V_{CC}1=5~V,\,V_{CC}2=7~V,\,V_{S}=3~V$

|                                                  |                        |                                                                          | Ratings |      |       |      |

|--------------------------------------------------|------------------------|--------------------------------------------------------------------------|---------|------|-------|------|

| Parameter                                        | Symbol                 | Conditions                                                               | min     | typ  | max   | Unit |

|                                                  | I <sub>CC</sub> 1      | V <sub>BR</sub> = 5 V                                                    |         | 3.0  | 5.0   | mA   |

| Supply current                                   | I <sub>CC</sub> 2      | V <sub>BR</sub> = 5 V                                                    |         | 6.5  | 10.0  | mA   |

|                                                  | Is                     | $V_{BR} = 5 \text{ V}, R_L = \infty$                                     |         |      | 5.0   | mA   |

| Output quiescent current                         | Iccoq                  | V <sub>STBY</sub> = 0 V                                                  |         |      | 100   | μA   |

| Output quiescent current                         | I <sub>SOQ</sub>       | V <sub>STBY</sub> = 0 V, R <sub>L</sub> = ∞                              |         |      | 150   | μA   |

| Output saturation voltage                        | V <sub>O(sat)</sub>    | I <sub>OUT</sub> = 0.6 A, sink + source                                  |         |      | 1.7   | V    |

| Output TRS withstand voltage                     | V <sub>O(sus)</sub>    | I <sub>OUT</sub> = 20 mA*1                                               | 12      |      |       | V    |

| Output quiescent voltage                         | V <sub>OQ</sub>        | V <sub>BR</sub> = 5 V                                                    | 1.45    | 1.55 | 1.65  | V    |

| Hall amplifier input offset voltage              | V <sub>HOFFSET</sub>   | *1                                                                       | -5      |      | +5    | mV   |

| Hall amplifier common mode input voltage range   | V <sub>нсом</sub>      |                                                                          | 1.4     |      | 2.8   | V    |

| Hall I/O voltage gain                            | GV <sub>HO</sub>       | Rangle = 8.2 kΩ                                                          | 34.0    | 37.0 | 40.0  | dB   |

| Brake pin high level voltage                     | V <sub>BRH</sub>       |                                                                          | 2.0     |      |       | V    |

| Brake pin low level voltage                      | V <sub>BRL</sub>       |                                                                          |         |      | 0.8   | V    |

| Brake pin input current                          | I <sub>BRIN</sub>      |                                                                          |         |      | 120   | μA   |

| Brake pin leakage current                        | I <sub>BRLEAK</sub>    |                                                                          |         |      | -30   | μA   |

| FRC pin high level voltage                       | V <sub>FRCH</sub>      |                                                                          | 2.8     |      |       | V    |

| FRC pin low level voltage                        | V <sub>FRCL</sub>      |                                                                          |         |      | 1.2   | V    |

| FRC pin input current                            | I <sub>FRCIN</sub>     |                                                                          |         |      | 100   | μA   |

| FRC pin leakage current                          | I <sub>FRCLEAK</sub>   |                                                                          |         |      | -30   | μA   |

| Upper side residual voltage                      | V <sub>XH</sub>        | I <sub>OUT</sub> = 100 mA, V <sub>CC</sub> 2 = 6 V, V <sub>S</sub> = 2 V | 0.285   |      | 0.455 | V    |

| Lower side residual voltage                      | V <sub>XL</sub>        | I <sub>OUT</sub> = 100 mA, V <sub>CC</sub> 2 = 6 V, V <sub>S</sub> = 2 V | 0.350   |      | 0.440 | V    |

| Residual voltage inflection point                | V <sub>S∆VX</sub>      | I <sub>OUT</sub> = 100 mA, V <sub>CC</sub> 2 = 6 V*1                     |         | 0.9  |       | V    |

| Overlap level                                    | OL                     | $V_{CC}2 = 6 \text{ V}, V_S = 3 \text{ V}, R_L = 100 \Omega (Y)$         | 60      | 70   | 80    | %    |

| Overlap vertical difference                      | ΔOL                    | $V_{CC}2 = 6 \text{ V}, V_S = 3 \text{ V}, R_L = 100 \Omega \text{ (Y)}$ | -10     | 0    | +10   | %    |

| Standby on voltage                               | V <sub>STBYL</sub>     | *2                                                                       | -0.2    |      | +0.8  | V    |

| Standby off voltage                              | V <sub>STBYH</sub>     |                                                                          | 2       |      | 5     | V    |

| Standby pin bias current                         | I <sub>STBYIN</sub>    |                                                                          |         |      | 100   | μA   |

| Thermal protection circuit operating temperature | T <sub>TSD</sub>       | *1                                                                       | 150     | 180  | 210   | °C   |

| Thermal protection circuit hysteresis            | $\Delta T_{TSD}$       | *1                                                                       |         | 15   |       | °C   |

| FG amplifier input offset voltage                | V <sub>FG OFFSET</sub> |                                                                          | -8      |      | +8    | mV   |

| Open loop voltage gain                           | GV <sub>FG</sub>       | f = 10 kHz                                                               |         | 43   |       | dB   |

| Source output saturation voltage                 | V <sub>FG OU</sub>     | $I_0 = -2 \text{ mA}$                                                    | 3.7     |      |       | V    |

| Sink output saturation voltage                   | V <sub>FG OD</sub>     | $I_O = 2 \text{ mA}$                                                     |         |      | 1.3   | V    |

| Common mode signal exclusion ratio               | G <sub>HR</sub>        | *1                                                                       |         | 80   |       | dB   |

| FG amplifier common mode input voltage range     | V <sub>FG CH</sub>     |                                                                          | 0       |      | 3.5   | V    |

| Phase margin                                     | φМ                     | *1                                                                       |         | 20   |       | deg  |

| Schmitt amplifier threshold voltage              | V <sub>FGS SH</sub>    | $V_{FGIN}^+$ = 2.5 V,<br>when $V_{FGOUT}^2$ goes from high to low        | 2.45    | 2.50 | 2.55  | V    |

| Schmitt amplifier hysteresis width               | V <sub>FGS HIS</sub>   | V <sub>FGIN</sub> <sup>+</sup> = 2.5 V                                   | 20      | 40   | 60    | mV   |

Note: 1. These are target settings, and are not measured. The overlap ratings are taken as test ratings without change.

2. When the standby pin is open the IC will be in the standby state.

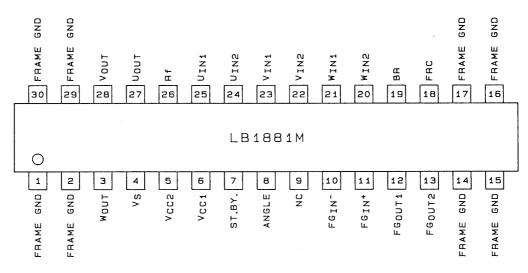

## **Pin Assignment**

A01379 Top view

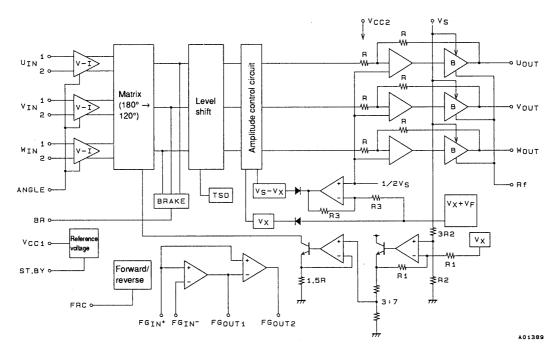

## **Block Diagram**

Pin Functions Unit (resistance:  $\Omega$ )

| Pin No.  | Symbol              | Pin voltage                                                         | Equivalent circuit                | Pin function                                                                                                                                                                                                 |

|----------|---------------------|---------------------------------------------------------------------|-----------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4        | V <sub>S</sub>      | ≤V <sub>CC</sub> 2                                                  |                                   | Power supply input that determines the output amplitude. It must be set to a voltage equal or lower than $V_{\text{CC}}2$ .                                                                                  |

| 5        | V <sub>CC</sub> 2   | 4 to 10 V                                                           |                                   | Power supply for power amplifier systems other than motor drive transistors. Power supply pin that provides voltage for blocks other than controblocks supplied by V <sub>CC</sub> 1.                        |

| 6        | V <sub>CC</sub> 1   | 4 to 6 V                                                            |                                   | Power supply that provides voltage for the Hall amplifier, the forward/reverse circuit, the FG amplifier, and the thermal shutdown circuit.                                                                  |

| 7        | ST. BY              | (H): 2.0 V max<br>(L): 0.8 V min<br>(When V <sub>CC</sub> 1 is 5 V) | 100k VCC1  100k  100k  A01380     | All circuits can be made inoperative either by connecting this pin to GND, or by leaving it open In that state the supply current will be approximately 0 µA. Hold at 2 V or higher during normal operation. |

| 8        | ANGLE               |                                                                     | VCC1 ≥200                         | Connect a resistor between this pin and GND. Changing the value of this resistor will change th Hall input-output gain (motor waveform slope).                                                               |

|          |                     |                                                                     | VCC1 \$200 \$ A01381              |                                                                                                                                                                                                              |

| 10<br>11 | FG <sub>IN</sub> +  | 0 V min<br>3.5 V max<br>(When V <sub>CC</sub> 1 is 5 V)             | VCC1 200 200 A01382               | FG signal input pin                                                                                                                                                                                          |

| 12       | FG <sub>OUT</sub> 1 |                                                                     | VCC1<br>38<br>38<br>200<br>A01383 | FG amplifier output pin                                                                                                                                                                                      |

Continued on next page

Continued from preceding page.

Unit (resistance:  $\Omega$ )

|                                       | om precedir                                                                                           |                                                   | Environment almosts                                                    | Unit (resistance: Ω)                                                                                                                                                                                                                                                       |

|---------------------------------------|-------------------------------------------------------------------------------------------------------|---------------------------------------------------|------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin No.                               | Symbol                                                                                                | Pin voltage                                       | Equivalent circuit                                                     | Pin function  FG Schmitt amplifier output pin                                                                                                                                                                                                                              |

| 13                                    | FG <sub>OUT</sub> 2                                                                                   |                                                   | VCC1 (13)                                                              | PG Schmitt ampliner output pin                                                                                                                                                                                                                                             |

| 18                                    | FRC                                                                                                   | (H): 2.8 V min                                    |                                                                        | Pin for setting the motor to forward or reverse                                                                                                                                                                                                                            |

|                                       |                                                                                                       | (L): 1.2 V max<br>(When V <sub>CC</sub> 1 is 5 V) | VCC1  100k  100k  A01385                                               | rotation  Low level: Forward rotation (under 1.2 V: when V <sub>CC</sub> 1 is 5 V)  High level: Reverse rotation (over 2.8 V: when V <sub>CC</sub> 1 is 5 V)                                                                                                               |

| 19                                    | BR                                                                                                    | (H): 2.0 V min                                    | VCC2                                                                   | Motor brake pin                                                                                                                                                                                                                                                            |

|                                       |                                                                                                       | (L): 0.8 V max                                    | AVCC1                                                                  | Low level: Motor drive (under 0.8 V)                                                                                                                                                                                                                                       |

|                                       |                                                                                                       |                                                   | \\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\                                 | High level: Motor brake                                                                                                                                                                                                                                                    |

|                                       |                                                                                                       |                                                   | 19 50k \$ \$ A01386                                                    | (over 2.0 V)                                                                                                                                                                                                                                                               |

| 20                                    | W <sub>IN</sub> 2                                                                                     | 1.4 V min                                         |                                                                        | W phase Hall element input pins.                                                                                                                                                                                                                                           |

| 21<br>22<br>23<br>24<br>25            | W <sub>IN</sub> 1<br>V <sub>IN</sub> 2<br>V <sub>IN</sub> 1<br>U <sub>IN</sub> 2<br>U <sub>IN</sub> 1 | 2.8 V max<br>(When V <sub>CC</sub> 1 is 5 V)      | 25) 200 24<br>23 W 200 22<br>21) 7 7 7 7 7 7 7 7 7 7 7 7 7 7 7 7 7 7 7 | Logic high is defined to be states where $W_{IN}1 > W_{IN}2$ .<br>V phase Hall element input pins.<br>Logic high is defined to be states where $V_{IN}1 > V_{IN}2$ .<br>U phase Hall element input pins.<br>Logic high is defined to be states where $U_{IN}1 > U_{IN}2$ . |

|                                       |                                                                                                       |                                                   | ,777 A01387                                                            |                                                                                                                                                                                                                                                                            |

| 26                                    | R <sub>f</sub>                                                                                        |                                                   |                                                                        | Output transistor GND                                                                                                                                                                                                                                                      |

| 27                                    | U <sub>OUT</sub>                                                                                      |                                                   | ∨s                                                                     | Output pin                                                                                                                                                                                                                                                                 |

| 28<br>3                               | Vout<br>Wout                                                                                          |                                                   | 27<br>W 28<br>3<br>M 3<br>Rf                                           |                                                                                                                                                                                                                                                                            |

| 1, 2,<br>14, 15,<br>16, 17,<br>29, 30 | FRAME<br>(GND)                                                                                        |                                                   |                                                                        | GND for all circuits other than output transistors.                                                                                                                                                                                                                        |

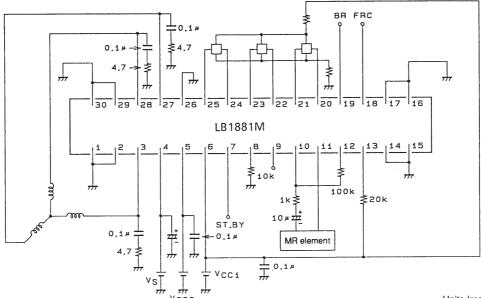

#### **Sample Application Circuit**

Units (resistance:  $\Omega$ , capacitance: F)

### **Logic Value Table**

|   | Source                                      | Input |   |   | Forward and reverse control |

|---|---------------------------------------------|-------|---|---|-----------------------------|

|   | Sink                                        | U     | V | W | F/RC                        |

| 1 | W phase $\rightarrow$ V phase               | Н     | Н | L | L                           |

|   | $V \text{ phase} \to W \text{ phase}$       |       |   |   | Н                           |

| 2 | W phase $\rightarrow$ U phase               | Н     | L | L | L                           |

|   | $U\;phase\toW\;phase$                       |       |   |   | Н                           |

| 3 | $V \text{ phase} \to W \text{ phase}$       |       | L | Н | L                           |

|   | W phase $\rightarrow$ V phase               | _     |   |   | Н                           |

| 4 | $\text{U phase} \rightarrow \text{V phase}$ |       | Н | - | L                           |

| 4 | $V \text{ phase} \to U \text{ phase}$       | _     |   | _ | Н                           |

| 5 | $V \text{ phase} \to U \text{ phase}$       | Н     | L | Н | L                           |

|   | U phase $\rightarrow$ V phase               |       |   |   | Н                           |

| 6 | U phase → W phase                           |       | Н | Н | L                           |

|   | W phase $\rightarrow$ U phase               | L     |   |   | Н                           |

#### Inputs:

High: For each phase, the input 1 potential is at least 0.2 V higher than the input 2 potential. Low: For each phase, the input 1 potential is at least 0.2 V lower than the input 2 potential.

Forward/reverse control: High: 2.8 V to V<sub>CC</sub>1

- High: 2.8 V to V<sub>CC</sub>1 Low: 0 to 1.2 V

- No products described or contained herein are intended for use in surgical implants, life-support systems, aerospace equipment, nuclear power control systems, vehicles, disaster/crime-prevention equipment and the like, the failure of which may directly or indirectly cause injury, death or property loss.

- Anyone purchasing any products described or contained herein for an above-mentioned use shall:

- ① Accept full responsibility and indemnify and defend SANYO ELECTRIC CO., LTD., its affiliates, subsidiaries and distributors and all their officers and employees, jointly and severally, against any and all claims and litigation and all damages, cost and expenses associated with such use:

- ② Not impose any responsibility for any fault or negligence which may be cited in any such claim or litigation on SANYO ELECTRIC CO., LTD., its affiliates, subsidiaries and distributors or any of their officers and employees jointly or severally.

- Information (including circuit diagrams and circuit parameters) herein is for example only; it is not guaranteed for volume production. SANYO believes information herein is accurate and reliable, but no guarantees are made or implied regarding its use or any infringements of intellectual property rights or other rights of third parties.

This catalog provides information as of November, 1997. Specifications and information herein are subject to change without notice.