Monolithic Digital IC

# LB1910

## **FDD Spindle Motor Driver**

### **Overview**

The LB1910 is a 3-phase disc drive motor driver that is optimal for use as a 3.5-inch FDD spindle motor driver.

## **Functions and Features**

- Three-phase full-wave linear driver

- Digital speed control circuit

- Start and stop circuits (active low)

- RPM switching H: 300 rpm

- L: 360 rpm

- Current limiter circuit

- Built-in index comparator

- Thermal shutdown circuit

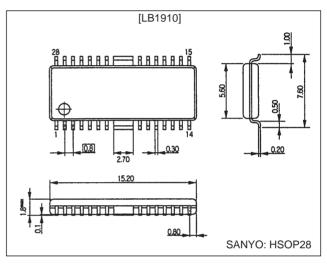

## **Package Dimensions**

unit: mm

3222-HSOP28

## **Specifications**

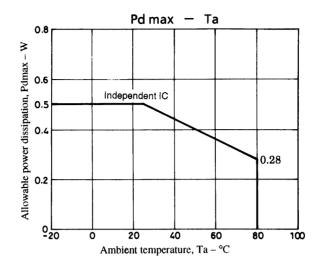

#### Absolute Maximum Ratings at $Ta = 25^{\circ}C$

| Parameter                           | Symbol              | Conditions     | Ratings     | Unit |

|-------------------------------------|---------------------|----------------|-------------|------|

| Maximum supply voltage              | V <sub>CC</sub> max |                | 7.0         | V    |

| Maximum output current              | I <sub>O</sub> max1 | $t \le 0.5 s$  | 1.0         | А    |

| Maximum steady-state output current | I <sub>O</sub> max2 |                | 0.7         | Α    |

| Allowable power dissipation         | Pd max              | Independent IC | 0.5         | W    |

| Operating temperature               | Topr                |                | -20 to +80  | °C   |

| Storage temperature                 | Tstg                |                | -40 to +150 | °C   |

#### Allowable Operating Ranges at $Ta = 25^{\circ}C$

| Parameter                  | Symbol          | Conditions | Ratings    | Unit |

|----------------------------|-----------------|------------|------------|------|

| Recommended supply voltage | V <sub>CC</sub> |            | 4.2 to 6.5 | V    |

SANYO Electric Co., Ltd. Semiconductor Bussiness Headquarters TOKYO OFFICE Tokyo Bldg., 1-10, 1 Chome, Ueno, Taito-ku, TOKYO, 110 JAPAN

## Electrical Characteristics at Ta = 25°C, $V_{CC}$ = 5 V

| Parameter                               | Symbol            | Conditions                            | min  | typ    | max                   | Unit  |

|-----------------------------------------|-------------------|---------------------------------------|------|--------|-----------------------|-------|

| Oursent desig                           | Icco              | S/S = 5 V (standby)                   |      |        | 10                    | μΑ    |

| Current drain                           | Icc               | S/S = 0 V (steady state)              |      | 12     | 18                    | mA    |

| SL bias current                         | I <sub>SL</sub>   | $V_{SL} = 0 V$                        |      |        | 10                    | μΑ    |

| SL input low-level voltage              | V <sub>SLL</sub>  |                                       | 0    |        | 1.0                   | V     |

| SL input high-level voltage             | V <sub>SLH</sub>  |                                       | 3.5  |        | V <sub>CC</sub>       | V     |

| S/S bias current                        | I <sub>S/S</sub>  |                                       |      | 180    | 270                   | μΑ    |

| S/S low-level voltage                   | V <sub>S/SL</sub> |                                       | 0    |        | 0.8                   | V     |

| S/S high-level voltage                  | V <sub>S/SH</sub> |                                       | 3.5  |        | V <sub>CC</sub>       | V     |

| Hall amplifier input bias current       | I <sub>HB</sub>   |                                       |      |        | 10                    | μΑ    |

| Common-mode input voltage range         | V <sub>h</sub>    |                                       | 1.5  |        | V <sub>CC</sub> – 1.0 | V     |

| Differential input voltage range        | Vdif              |                                       | 50   |        | 200                   | mVp-p |

| Hall bias output voltage                | V <sub>H</sub>    | I <sub>H</sub> = 5 mA                 |      | 0.8    |                       | V     |

| Leakage current                         | I <sub>HL</sub>   | S/S = 5 V                             |      |        | ±10                   | μΑ    |

| Output saturation voltage               | Vsat              | I <sub>O</sub> = 0.7 A, sink + source |      | 1.3    | 1.8                   | V     |

| Output leakage current                  | I <sub>OL</sub>   |                                       |      |        | 1.0                   | mA    |

| Current limiter                         | Vlim              |                                       | 0.27 | 0.3    | 0.33                  | V     |

| Control amplifier voltage gain          | G <sub>C</sub>    |                                       |      | -7     |                       | dB    |

| Voltage gain difference between phases  | $\Delta G_{C}$    |                                       |      |        | ±1                    | dB    |

| V/I conversion source current           | +                 |                                       | 9    | 14     | 19                    | μA    |

| V/I conversion sink current             | I-                |                                       | -9   | -14    | -19                   | μA    |

| V/I conversion current ratio            | +/ -              |                                       | 0.8  | 1.0    | 1.2                   |       |

| DSC buffer input current                | I <sub>DSC</sub>  |                                       |      |        | 1.0                   | μA    |

| FG Schmitt hysteresis                   | ∆Vsh              | *                                     |      | 50     |                       | mV    |

| Speed discriminator counts              | Ν                 |                                       |      | 1041.5 |                       |       |

| Discriminator operating frequency       | FD                | *                                     |      |        | 1.1                   | MHz   |

| Oscillator frequency range              | F <sub>OSC</sub>  | *                                     |      |        | 1.1                   | MHz   |

| Index output low-level voltage          | V <sub>IDL</sub>  | $I_0 = 2 \text{ mA}$                  |      |        | 0.4                   | V     |

| Index output leakage current            | IDL               |                                       |      |        | ±10                   | μΑ    |

| FG amplifier voltage gain               | G <sub>FG</sub>   | *                                     |      | 48     |                       | dB    |

| FG amplifier input offset               | V <sub>FG O</sub> |                                       |      |        | ±10                   | mV    |

| FG amplifier internal reference voltage | V <sub>FG B</sub> |                                       | 2.2  | 2.5    | 2.8                   | V     |

| Thermal shutdown temperature            | TSD               | *                                     | 150  | 180    |                       | °C    |

| Hysteresis                              | ΔTSD              | *                                     |      | 40     |                       | °C    |

Note: \* Items marked with an asterisk are design target values and are not measured.

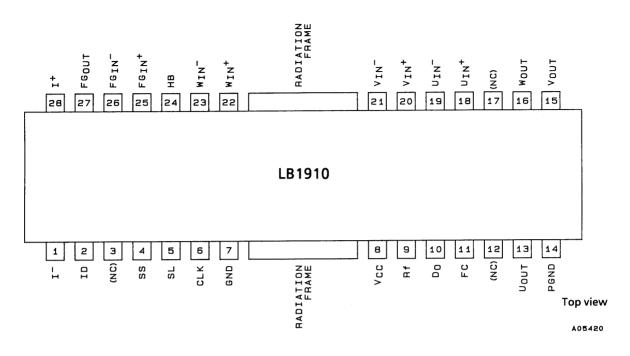

#### **Pin Assignment**

#### **Truth Table**

|   | Source $\rightarrow$ sink     | Hall input |   |   |  |

|---|-------------------------------|------------|---|---|--|

|   |                               | U          | V | W |  |

| 1 | V phase $\rightarrow$ W phase | Н          | Н | L |  |

| 2 | V phase $\rightarrow$ U phase | L          | Н | L |  |

| 3 | W phase $\rightarrow$ U phase | L          | Н | Н |  |

| 4 | W phase $\rightarrow$ V phase | L          | L | Н |  |

| 5 | U phase $\rightarrow$ V phase | Н          | L | Н |  |

| 6 | U phase $\rightarrow$ W phase | Н          | L | L |  |

Note: Hall input high levels are defined as:  $U_{IN}^+ > U_{IN}^ V_{IN}^+ > V_{IN}^ W_{IN}^+ > W_{IN}^-$

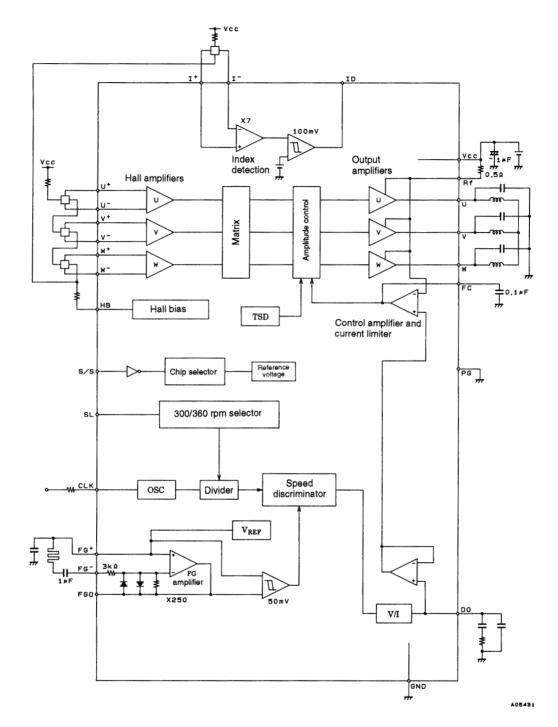

#### **Block Diagram**

#### **Pin Functions**

| Pin No.                          | Symbol                                                                                                                     | Pin voltage                                 | Equivalent circuit diagram                                                                                                                                                                                                                                               | Function                                                                                                                                                              |

|----------------------------------|----------------------------------------------------------------------------------------------------------------------------|---------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 18<br>19<br>20<br>21<br>22<br>23 | U <sub>IN</sub> +<br>U <sub>IN</sub> -<br>V <sub>IN</sub> +<br>V <sub>IN</sub> -<br>W <sub>IN</sub> +<br>W <sub>IN</sub> - | 1.5 V min<br>V <sub>CC</sub> – 1.0 V<br>max | VCC<br>18<br>1k 2<br>20<br>VCC<br>19<br>1k 2<br>VCC<br>19<br>1k 2<br>VCC<br>19<br>1k 2<br>VCC<br>19<br>1k 2<br>VCC<br>19<br>1k 2<br>VCC<br>18<br>1k 2<br>VCC<br>18<br>1k 2<br>VCC<br>18<br>1k 2<br>VCC<br>18<br>10<br>10<br>10<br>10<br>10<br>10<br>10<br>10<br>10<br>10 | U phase Hall element input<br>V phase Hall element input<br>W phase Hall element input                                                                                |

| 24                               | НВ                                                                                                                         | 0.8 V typ<br>(I <sub>H</sub> = 5 mA)        | 24<br>                                                                                                                                                                                                                                                                   | Minus side connection for providing the Hall bias<br>current<br>This pin becomes open in the stopped state, thus<br>cutting the Hall bias current.                    |

| 25<br>26<br>27                   | FG <sub>IN</sub> +<br>FG <sub>IN</sub> −<br>FG <sub>OUT</sub>                                                              | 2.5 V                                       | 25<br>25<br>25<br>25<br>25<br>25<br>25<br>25<br>25<br>25                                                                                                                                                                                                                 | <ul> <li>FG amplifier plus input<br/>A 2.5-V reference voltage is generated<br/>internally.</li> <li>FG amplifier minus input</li> <li>FG amplifier output</li> </ul> |

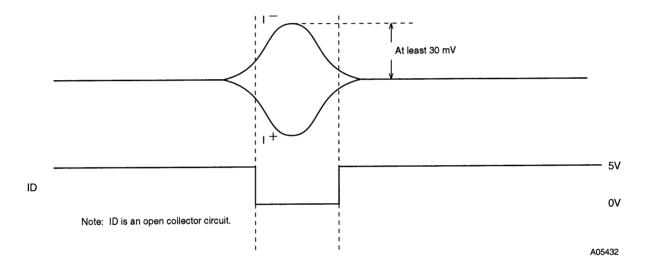

| 28<br>1                          | +<br> -                                                                                                                    |                                             | VCC<br>28<br>VCC<br>VCC<br>2000<br>VCC<br>2000<br>VCC<br>2000<br>VCC<br>A05424                                                                                                                                                                                           | Index input                                                                                                                                                           |

| 2                                | ID                                                                                                                         | L: 0.4 V max<br>H: 4.5 V min                | 2<br>405425                                                                                                                                                                                                                                                              | Index output                                                                                                                                                          |

Continued on next page.

Continued from preceding page.

| Pin No. | Symbol          | Pin voltage                                       | Equivalent circuit diagram | Function                                                                                                                                                                                                          |

|---------|-----------------|---------------------------------------------------|----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4       | SS              | L: 0.8 V max<br>H: 3.5 V min                      |                            | Start/stop mode switching<br>This is an active-low input.                                                                                                                                                         |

| 5       | SL              | L: 1.0 V max<br>H: 3.5 V min                      | VCC<br>V<br>5<br>A05427    | Rotational speed switching                                                                                                                                                                                        |

| 6       | CLK             | L: 1.0 V max<br>H: V <sub>CC</sub> – 1.0 V<br>min |                            | Reference clock input<br>A 1-MHz input frequency corresponds to speeds<br>of 300 and 360 rpm.                                                                                                                     |

| 7       | GND             |                                                   |                            | <ul> <li>Ground</li> <li>This pin, pin 14, and the frame must all be grounded together.</li> </ul>                                                                                                                |

| 8       | V <sub>CC</sub> |                                                   |                            | Power supply<br>This voltage must be stabilized so that ripple and<br>noise do not enter the IC.                                                                                                                  |

| 9       | Rf              |                                                   |                            | Output current detection<br>The output current is detected as a voltage by<br>connecting the resistor Rf between this pin and<br>$V_{CC}$ . The current limiter operates by detecting<br>the voltage on this pin. |

| 10      | Do              |                                                   | 10 VCC                     | Speed discriminator                                                                                                                                                                                               |

| 11      | Fc              |                                                   |                            | Frequency characteristics compensation<br>Current control system loop oscillation is<br>prevented by connecting a capacitor between<br>this pin and ground.                                                       |

Continued on next page.

Continued from preceding page.

| Pin No.        | Symbol                                       | Pin voltage | Equivalent circuit diagram | Function                                           |

|----------------|----------------------------------------------|-------------|----------------------------|----------------------------------------------------|

| 13<br>15<br>16 | U <sub>OUT</sub><br>V <sub>OUT</sub><br>WOUT |             |                            | U phase output<br>V phase output<br>W phase output |

| 14             | PGND                                         |             |                            | Output transistor ground connection                |

#### **Index Pulse Timing Chart**

No products described or contained herein are intended for use in surgical implants, life-support systems, aerospace equipment, nuclear power control systems, vehicles, disaster/crime-prevention equipment and the like, the failure of which may directly or indirectly cause injury, death or property loss.

- Anyone purchasing any products described or contained herein for an above-mentioned use shall:

- ① Accept full responsibility and indemnify and defend SANYO ELECTRIC CO., LTD., its affiliates, subsidiaries and distributors and all their officers and employees, jointly and severally, against any and all claims and litigation and all damages, cost and expenses associated with such use:

- ② Not impose any responsibility for any fault or negligence which may be cited in any such claim or litigation on SANYO ELECTRIC CO., LTD., its affiliates, subsidiaries and distributors or any of their officers and employees jointly or severally.

- Information (including circuit diagrams and circuit parameters) herein is for example only; it is not guaranteed for volume production. SANYO believes information herein is accurate and reliable, but no guarantees are made or implied regarding its use or any infringements of intellectual property rights or other rights of third parties.

This catalog provides information as of December, 1997. Specifications and information herein are subject to change without notice.