LB1923M

# Power Brushless Motor Pre-Driver IC for OA Equipment

## **Overview**

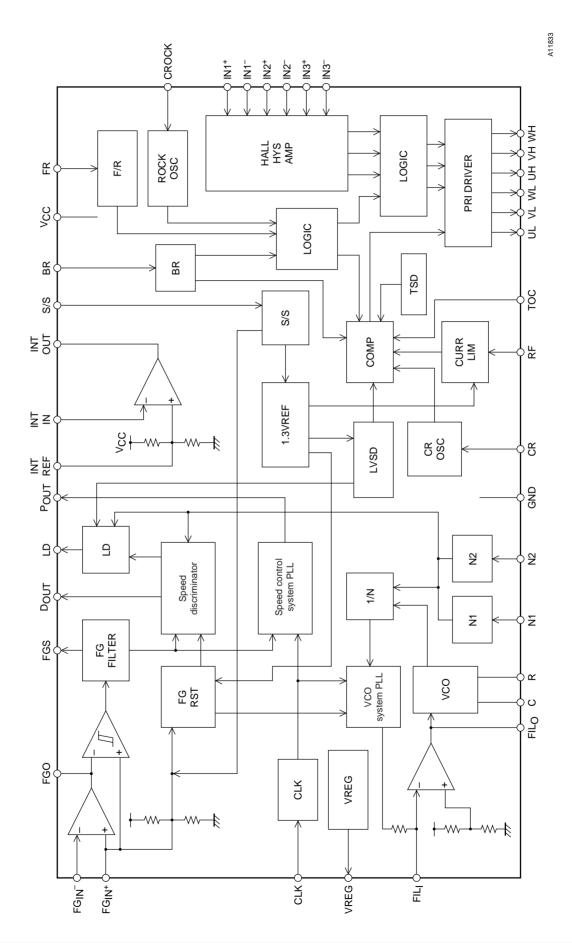

The LB1923M is a pre-driver IC that supports direct PWM drive and is appropriate for the power brushless motors used in office automation equipment. A motor drive circuit with the desired output capability (voltage and current characteristics) can be constructed by attaching a driver array at the IC output. The LB1923M includes on chip a speed control circuit that allows the motor speed to be varied using an external clock.

## **Features**

- Direct PWM drive output

- Speed discriminator + PLL speed control circuit

- FG and integrating amplifiers

- Forward/reverse switching circuit

- Braking circuit (short braking)

- Speed lock detection output

- Full complement of on-chip protection circuits,

including lock protection, current limiter, and thermal shutdown protection circuits.

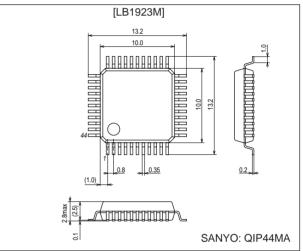

## **Package Dimensions**

unit: mm

#### 3148A-QFP44MA

# Specifications

## Absolute Maximum Ratings at $Ta = 25^{\circ}C$

| Parameter                   | Symbol               | Conditions             | Ratings     | Unit |

|-----------------------------|----------------------|------------------------|-------------|------|

| Maximum supply voltage      | V <sub>CC</sub> max  |                        | 9           | V    |

| Maximum input current       | I <sub>REG</sub> max | V <sub>REG</sub> pin   | 10          | mA   |

| Output current              | I <sub>O</sub> max   | UL, VL, and WL outputs | 30          | mA   |

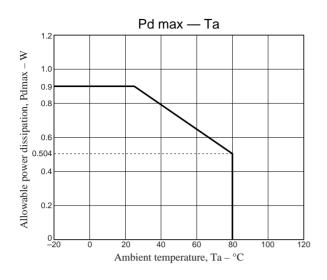

| Allowable power dissipation | Pd max               |                        | 0.9         | W    |

| Operating temperature       | Topr                 |                        | -20 to +80  | °C   |

| Storage temperature         | Tstg                 |                        | -55 to +150 | °C   |

#### Allowable Operating Ranges at $Ta = 25^{\circ}C$

| Parameter                         | Symbol           | Conditions                 | Ratings    | Unit |

|-----------------------------------|------------------|----------------------------|------------|------|

| Supply voltage                    | V <sub>CC</sub>  |                            | 4.4 to 7.0 | V    |

| Input current range               | I <sub>REG</sub> | V <sub>REG</sub> pin (7 V) | 1 to 5     | mA   |

| FG Schmitt output applied voltage | V <sub>FGS</sub> |                            | 0 to 8     | V    |

| FG Schmitt output current         | I <sub>FGS</sub> |                            | 0 to 5     | mA   |

| Lock detection output current     | I <sub>LD</sub>  |                            | 0 to 20    | mA   |

- Any and all SANYO products described or contained herein do not have specifications that can handle applications that require extremely high levels of reliability, such as life-support systems, aircraft's control systems, or other applications whose failure can be reasonably expected to result in serious physical and/or material damage. Consult with your SANYO representative nearest you before using any SANYO products described or contained herein in such applications.

- SANYO assumes no responsibility for equipment failures that result from using products at values that exceed, even momentarily, rated values (such as maximum ratings, operating condition ranges, or other parameters) listed in products specifications of any and all SANYO products described or contained herein.

SANYO Electric Co., Ltd. Semiconductor Company TOKYO OFFICE Tokyo Bldg., 1-10, 1 Chome, Ueno, Taito-ku, TOKYO, 110-8534 JAPAN

# Electrical Characteristics at Ta = 25°C, $V_{CC}$ = 6.3 V

| Deremeter                            | Cumhal                | Conditions                                  |     | Ratings |                       | Unit  |  |

|--------------------------------------|-----------------------|---------------------------------------------|-----|---------|-----------------------|-------|--|

| Parameter                            | Symbol                | Conditions                                  | min | typ     | max                   | Unit  |  |

|                                      | I <sub>CC</sub> 1     |                                             |     | 42      | 60                    | mA    |  |

|                                      | I <sub>CC</sub> 2     | In stop mode                                |     | 10      | 20                    | mA    |  |

| Current drain                        | I <sub>CC</sub> 3     | $V_{CC} = 5 V$                              |     | 38      | 55                    | mA    |  |

|                                      | I <sub>CC</sub> 4     | V <sub>CC</sub> = 5 V, In stop mode         |     | 8       | 18                    | mA    |  |

| Output saturation voltage            | V <sub>O</sub> (sat)  | UL, VL, WL output, I <sub>O</sub> = 20 mA   |     | 0.2     | 0.7                   | V     |  |

| Output current                       | Io                    | UH, VH, WH output, V <sub>OUT</sub> = 1.4 V | -20 | -16     | -12                   | mA    |  |

| Output leakage current               | I <sub>O</sub> leak   | UL, VL, WL output                           |     |         | 100                   | μA    |  |

| Output off voltage                   | V <sub>O</sub> off    | UH, VH, WH output                           |     |         | 0.5                   | V     |  |

| [Hall Amplifier]                     |                       |                                             |     |         |                       |       |  |

| Input bias current                   | I <sub>HB(HA)</sub>   |                                             | -4  | -1      |                       | μA    |  |

| Common-mode input voltage range      | VICM                  |                                             | 1.5 |         | V <sub>CC</sub> – 1.5 | V     |  |

| Hall input sensitivity               | ΔV <sub>IN(HA)</sub>  |                                             | 60  |         |                       | mVp-p |  |

| Hysteresis                           | ΔV <sub>IN(HA)</sub>  |                                             | 17  | 32      | 60                    | mV    |  |

| Input voltage low $\rightarrow$ high | V <sub>SLH</sub>      |                                             | 8   | 16      | 30                    | mV    |  |

| Input voltage high $\rightarrow$ low | V <sub>SHL</sub>      |                                             | -30 | -16     | -8                    | mV    |  |

| [CR Oscillator]                      |                       |                                             |     |         |                       |       |  |

|                                      | V <sub>OH(CR)</sub> 1 |                                             | 3.1 | 3.4     | 3.7                   | V     |  |

| Output high-level voltage            | V <sub>OH(CR)</sub> 2 | $V_{CC} = 5 V$                              | 2.4 | 2.7     | 3.0                   | V     |  |

|                                      | V <sub>OL(CR)</sub> 1 |                                             | 1.5 | 1.8     | 2.1                   | V     |  |

| Output low-level voltage             | V <sub>OL(CR)</sub> 2 | $V_{CC} = 5 V$                              | 1.1 | 1.4     | 1.7                   | V     |  |

| Oscillator frequency                 | f (CR)                | R = 75 kΩ, C = 1500 pF                      |     | 19      |                       | kHz   |  |

|                                      | V <sub>(CR)</sub> 1   |                                             | 1.4 | 1.6     | 1.8                   | Vp-p  |  |

| Amplitude                            | V <sub>(CR)</sub> 2   | $V_{CC} = 5 V$                              | 1.1 | 1.3     | 1.5                   | Vp-p  |  |

| [CROCK Oscillator]                   |                       |                                             | I   |         |                       |       |  |

|                                      | V <sub>OH(RK)</sub> 1 |                                             | 3.2 | 3.5     | 3.8                   | V     |  |

| Output high-level voltage            | V <sub>OH(RK)</sub> 2 | $V_{CC} = 5 V$                              | 2.5 | 2.8     | 3.1                   | V     |  |

|                                      | V <sub>OL(RK)</sub> 1 |                                             | 0.8 | 1.1     | 1.4                   | V     |  |

| Output low-level voltage             | V <sub>OL(RK)</sub> 2 | $V_{CC} = 5 V$                              | 0.6 | 0.9     | 1.2                   | V     |  |

| External capacitor charge current    | I <sub>CHG</sub> 1    |                                             | -17 | -13     | -9                    | μA    |  |

| External capacitor discharge current | I <sub>CHG</sub> 2    |                                             | 9   | 13      | 17                    | μA    |  |

| Oscillator frequency                 | f (RK)                | C = 0.068 µF                                |     | 35      |                       | Hz    |  |

|                                      | V <sub>(RK)</sub> 1   |                                             | 2.2 | 2.4     | 2.6                   | Vp-p  |  |

| Amplitude                            | V <sub>(RK)</sub> 2   | $V_{CC} = 5 V$                              | 1.7 | 1.9     | 2.1                   | Vp-p  |  |

| Parameter                                           | Symbol                                       | Conditions                       |                       | Ratings               | mov   | Uni     |

|-----------------------------------------------------|----------------------------------------------|----------------------------------|-----------------------|-----------------------|-------|---------|

|                                                     |                                              |                                  | min                   | typ                   | max   |         |

| [VCO Oscillator]                                    | V 4                                          |                                  | 4.4                   | 4.2                   | 4.6   | v       |

| Pin C output high-level voltage                     | V <sub>OH(C)</sub> 1                         | V <sub>CC</sub> = 5 V            | 4.1                   | 4.3                   | 4.6   | V       |

|                                                     | V <sub>OH(C)</sub> 2                         | VCC = 3 V                        | 3.6                   | 3.4                   | 4.1   | V       |

| Pin C output low-level voltage                      | V <sub>OL(C)</sub> 1<br>V <sub>OL(C)</sub> 2 | V <sub>CC</sub> = 5 V            | 2.8                   | 3.9                   | 3.2   | V       |

| Oscillator frequency                                | f (C)                                        |                                  |                       |                       | 1.0   | мн      |

| Amplitude                                           | V <sub>(C)</sub>                             |                                  | 0.2                   | 0.4                   | 0.6   | Vp-     |

| [Current Limiter Operation]                         | (0)                                          |                                  | _                     |                       |       |         |

| Limiter                                             | V <sub>RF</sub>                              |                                  | 0.47                  | 0.52                  | 0.57  | V       |

| [Thermal Shutdown Operation]                        |                                              |                                  |                       | 11                    |       | 1       |

| Thermal shutdown operating temperature              | TSD                                          | Design target value*             | 150                   | 180                   |       | °C      |

| Hysteresis                                          | ΔTSD                                         | Design target value*             |                       | 30                    |       | °C      |

| [V <sub>REG</sub> Pin]                              | _                                            |                                  |                       |                       |       |         |

| V <sub>REG</sub> pin voltage                        | V <sub>REG</sub>                             |                                  | 6.7                   | 7.1                   | 7.4   | V       |

| [FG Amplifier]                                      | INLO                                         |                                  |                       |                       |       |         |

| Input offset voltage                                | V <sub>IO(FG)</sub>                          |                                  | -10                   |                       | +10   | m\      |

| Input bias current                                  | I <sub>B(FG)</sub>                           |                                  | -1                    |                       | +1    | μΑ      |

| Output high-level voltage                           | V <sub>OH(FG)</sub>                          |                                  | V <sub>CC</sub> – 1.5 | V <sub>CC</sub> – 1   |       | μ/<br>V |

| Output low-level voltage                            | VOH(FG)                                      |                                  |                       | 1                     | 1.5   | V       |

| FG input sensitivity                                | · UL(FG)                                     | Gain: 100×                       | 3                     | · ·                   | 1.0   | m\      |

| Schmitt amplitude for the next stage                |                                              |                                  | 100                   | 180                   | 250   | m\      |

| Operating frequency range                           |                                              |                                  |                       |                       | 16    | kH      |

| Open-loop gain                                      |                                              | f <sub>(FG)</sub> = 2 kHz        | 45                    | 51                    | 10    | dE      |

| [FGS Output]                                        |                                              | (FG) = 2 KHZ                     |                       | 01                    |       |         |

| Output saturation voltage                           | V <sub>O(FGS)</sub>                          | I <sub>O(FGS)</sub> = 2 mA       |                       | 0.1                   | 0.5   | V       |

| Output leakage current                              | I <sub>L(FGS)</sub>                          | $V_0 = V_{CC}$                   |                       | 0.1                   | 10    | μA      |

| [Speed Discriminator Output]                        | L(FGS)                                       |                                  |                       |                       | 10    | μ μ     |

| Output high-level voltage                           | Vourp                                        |                                  | V <sub>CC</sub> – 1.0 | V <sub>CC</sub> - 0.7 |       | V       |

|                                                     | V <sub>OH(D)</sub>                           |                                  | V <sub>CC</sub> = 1.0 | 0.4                   | 1.1   | V       |

| Output low-level voltage [Speed Control PLL Output] | V <sub>OL(D)</sub>                           |                                  |                       | 0.4                   | 1.1   | v       |

|                                                     | V 1                                          |                                  | 4.05                  | 4.25                  | 4.65  | V       |

| Output high-level voltage                           | V <sub>OH(P)</sub> 1                         |                                  | 4.05                  | 4.35                  | 4.65  | v<br>v  |

|                                                     | V <sub>OH(P)</sub> 2                         | V <sub>CC</sub> = 5 V            | 3.25                  | 3.55                  | 3.83  | V       |

| Output low-level voltage                            | V <sub>OL(P)</sub> 1                         |                                  | 1.85                  | 2.15                  | 2.45  | V       |

|                                                     | V <sub>OL(P)</sub> 2                         | V <sub>CC</sub> = 5 V            | 1.25                  | 1.55                  | 1.85  | V       |

| [VCO PLL Output]                                    | 1                                            |                                  | 5.0                   | 50                    |       |         |

| Output high-level voltage                           | V <sub>OH(VCO)</sub>                         |                                  | 5.3                   | 5.6                   | 4.4   |         |

| Output low-level voltage                            | V <sub>OL(VCO)</sub>                         |                                  |                       | 0.4                   | 11    | V       |

| [Lock Detection]                                    |                                              | 1 10 1                           |                       | 0.4                   | 0.5   |         |

| Output saturation voltage                           | V <sub>OL(LD)</sub>                          | $I_{LD} = 10 \text{ mA}$         |                       | 0.1                   | 0.5   | V       |

| Output leakage current                              | I <sub>L(LD)</sub>                           | V <sub>O</sub> = V <sub>CC</sub> | 0.05                  |                       | 10    | μA      |

| Lock range                                          |                                              |                                  | -6.25                 |                       | +6.25 | %       |

| [Integrator]                                        |                                              |                                  | 10                    |                       | 10    |         |

| Input offset voltage                                | V <sub>IO(INT)</sub>                         |                                  | -10                   |                       | +10   | m\      |

| Input bias current                                  | I <sub>B(INT)</sub>                          |                                  | -0.4                  |                       | +0.4  | μA      |

| Output high-level voltage                           | V <sub>OH(INT)</sub>                         |                                  | V <sub>CC</sub> – 1.2 | V <sub>CC</sub> - 0.8 | 4.0   |         |

| Output low-level voltage                            | V <sub>OL(INT)</sub>                         |                                  |                       | 0.8                   | 1.2   |         |

| Open-loop gain                                      |                                              |                                  | 60                    |                       |       | dE      |

| Gain-bandwidth product                              |                                              |                                  |                       | 1.6                   |       | MH      |

| Reference voltage                                   | V <sub>B(INT)</sub>                          |                                  | -5%                   | V <sub>CC</sub> /2    | 5%    | V       |

| [Filter Amplifier]                                  |                                              |                                  |                       | · · ·                 |       |         |

| Input bias current                                  | I <sub>B(FIL)</sub>                          |                                  | -0.4                  |                       | +0.4  | μA      |

| Output high-level voltage                           | V <sub>OH(FIL)</sub>                         |                                  | V <sub>CC</sub> – 1.2 | V <sub>CC</sub> – 0.8 |       | V       |

| Output low-level voltage                            | V <sub>OL(FIL)</sub>                         |                                  |                       | 0.8                   | 1.2   | V       |

| Reference voltage                                   | V <sub>B(FIL)</sub> 1                        |                                  | -5%                   | 2.0                   | +5%   | V       |

| Reference voltage                                   | V <sub>B(FIL)</sub> 2                        | V <sub>CC</sub> = 5 V            | 1.5                   | 1.6                   | 1.7   | V       |

| Parameter                 | Symbol                  | Conditions                                  |      | Ratings |                 | Uni |

|---------------------------|-------------------------|---------------------------------------------|------|---------|-----------------|-----|

| i didineter               | Cymbol                  |                                             | min  | typ     | max             |     |

| [S/S Pin]                 |                         |                                             |      |         |                 |     |

| Output high-level voltage | V <sub>OH(S/S)</sub>    |                                             | 4.0  |         | V <sub>CC</sub> | V   |

| Output low-level voltage  | V <sub>OL(S/S)</sub>    |                                             | 0    |         | 1.5             | V   |

|                           | $\Delta V_{IN(S/S)}$ 1  |                                             | 0.35 | 0.45    | 0.55            | V   |

| Hysteresis                | $\Delta V_{IN(S/S)}2$   | $V_{CC} = 5 V$                              | 0.24 | 0.34    | 0.44            | V   |

| Pull-up resistance        | R <sub>U(S/S)</sub>     |                                             | 45   | 63      | 85              | kΩ  |

| [F/R Pin]                 |                         |                                             |      |         |                 |     |

| Input high-level voltage  | V <sub>IH(F/R)</sub>    |                                             | 4.0  |         | V <sub>CC</sub> | V   |

| Input low-level voltage   | V <sub>IL(F/R)</sub>    |                                             | 0    |         | 1.5             | V   |

| Lhusterezia               | $\Delta V_{IN(F/R)}$ 1  |                                             | 0.35 | 0.45    | 0.55            | V   |

| Hysteresis                | $\Delta V_{IN(F/R)}2$   | $V_{CC} = 5 V$                              | 0.24 | 0.34    | 0.44            | V   |

| Pull-up resistance        | R <sub>U(F/R)</sub>     |                                             | 45   | 63      | 85              | kΩ  |

| [BR Pin]                  |                         |                                             |      |         |                 |     |

| Input high-level voltage  | V <sub>IH(BR)</sub>     |                                             | 4.0  |         | V <sub>CC</sub> | V   |

| Input low-level voltage   | V <sub>IL(BR)</sub>     |                                             | 0    |         | 1.5             | V   |

| Hysteresis                | $\Delta V_{IN(BR)}$ 1   |                                             | 0.35 | 0.45    | 0.55            | V   |

|                           | $\Delta V_{IN(BR)}2$    | $V_{CC} = 5 V$                              | 0.24 | 0.34    | 0.44            | V   |

| Pull-up resistance        | R <sub>U(BR)</sub>      |                                             | 45   | 63      | 85              | k۵  |

| [CLK Pin]                 |                         |                                             |      |         |                 |     |

| Input high-level voltage  | V <sub>IH(CLK)</sub>    | Design target value*                        | 4.0  |         | V <sub>CC</sub> | V   |

| Input low-level voltage   | V <sub>IL(CLK)</sub>    | Design target value*                        | 0    |         | 1.5             | V   |

|                           | ΔV <sub>IN(CLK)</sub> 1 | Design target value*                        | 0.35 | 0.45    | 0.55            | V   |

| Hysteresis                | ΔV <sub>IN(CLK)</sub> 2 | V <sub>CC</sub> = 5 V, Design target value* | 0.24 | 0.34    | 0.44            | V   |

| Pull-up resistance        | R <sub>U(CLK)</sub>     |                                             | 45   | 63      | 85              | kΩ  |

| Input frequency           | f (CLK)                 |                                             |      |         | 16              | kH  |

| [N1 Pin]                  |                         |                                             |      |         |                 |     |

| Input high-level voltage  | V <sub>IH(N1)</sub>     |                                             | 4.0  |         | V <sub>CC</sub> | V   |

| Input low-level voltage   | V <sub>IL(N1)</sub>     |                                             | 0    |         | 1.5             | V   |

|                           | ΔV <sub>IN(N1)</sub> 1  |                                             | 0.35 | 0.45    | 0.55            | V   |

| Hysteresis                | $\Delta V_{IN(N1)}2$    | $V_{CC} = 5 V$                              | 0.24 | 0.34    | 0.44            | V   |

| Pull-up resistance        | R <sub>U(N1)</sub>      |                                             | 45   | 63      | 85              | k۵  |

| [N2 Pin]                  | I                       |                                             | I    |         |                 |     |

| Input high-level voltage  | V <sub>IH(N2)</sub>     |                                             | 4.0  |         | V <sub>CC</sub> | V   |

| Input low-level voltage   | V <sub>IL(N2)</sub>     |                                             | 0    |         | 1.5             | V   |

|                           | ΔV <sub>IN(N2)</sub> 1  |                                             | 0.35 | 0.45    | 0.55            | V   |

| Hysteresis                |                         | $V_{CC} = 5 V$                              | 0.24 | 0.34    | 0.44            | V   |

| Pull-up resistance        | R <sub>U(N2)</sub>      |                                             | 45   | 63      | 85              | k۵  |

| [Low Voltage Protection]  | \ \                     | 1                                           | I    |         |                 |     |

| Operating voltage         | V <sub>SDL</sub>        |                                             |      | 3.75    |                 | V   |

| Release voltage           | V <sub>SDH</sub>        |                                             |      | 4.0     |                 | V   |

| Hysteresis                | ΔV <sub>SD</sub>        |                                             | 0.15 | 0.25    | 0.35            | V   |

Note: \* Design target value. These items are not tested.

## **Speed Discriminator Counts**

| N1           | N2           | Number of counts |

|--------------|--------------|------------------|

| High or open | High or open | 64               |

| High or open | L            | 256              |

| L            | High or open | 128              |

| L            | L            | 512              |

## Three-Phase Logic Truth Table (A high (H) input is the state where IN<sup>+</sup> > IN<sup>-</sup>.)

| 14   |     | F / R = L |     |     | F / R = H |     | Ou     | tput |

|------|-----|-----------|-----|-----|-----------|-----|--------|------|

| Item | IN1 | IN2       | IN3 | IN1 | IN2       | IN3 | Source | Sink |

| 1    | Н   | L         | Н   | L   | Н         | L   | VH     | UL   |

| 2    | Н   | L         | L   | L   | Н         | Н   | WH     | UL   |

| 3    | Н   | Н         | L   | L   | L         | Н   | WH     | VL   |

| 4    | L   | Н         | L   | Н   | L         | Н   | UH     | VL   |

| 5    | L   | Н         | Н   | Н   | L         | L   | UH     | WL   |

| 6    | L   | L         | Н   | Н   | Н         | L   | VH     | WL   |

#### S/S Pin

#### BRK Pin

| High or open | Stop  |

|--------------|-------|

| L            | Start |

| High or open | Brake    |

|--------------|----------|

| L            | Released |

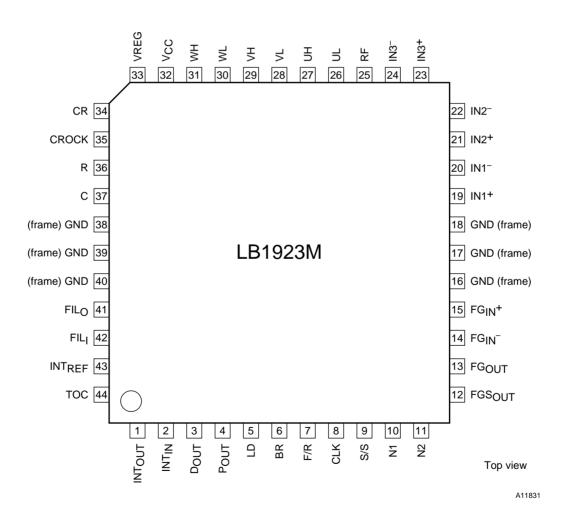

## **Pin Assignment**

## **Pin Functions**

| Pin                      | Pin No.                    | Function                                                                                                                                                                                                                  |

|--------------------------|----------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| IN1+, IN1-<br>IN2+, IN2- | 19, 20<br>21, 22<br>23, 24 | Hall inputs for the phases<br>The logic high level corresponds to the state $V_{IN}^+ > V_{IN}^-$ .                                                                                                                       |

| UH<br>VH                 | 23, 24<br>27<br>29         | Outputs. These are fixed-current source outputs.                                                                                                                                                                          |

| UL                       | 31<br>26                   |                                                                                                                                                                                                                           |

| VL                       | 28                         | The duty is controlled by the output pin PWM.                                                                                                                                                                             |

| WL                       | 30                         | These are open collector sink outputs.                                                                                                                                                                                    |

| V <sub>CC</sub>          | 32                         | A capacitor must be inserted between this pin and ground to prevent noise entering the circuit.                                                                                                                           |

| V <sub>REG</sub>         | 33                         | 7-V shunt regulator output                                                                                                                                                                                                |

| GND                      | 16 to 18<br>38 to 40       | Ground                                                                                                                                                                                                                    |

| CR                       | 34                         | Used to set the PWM circuit oscillator frequency.                                                                                                                                                                         |

| CROCK                    | 35                         | Motor lock protection circuit. Reference signal oscillator connection. Used by the circuit that prevents incorrect operation if the clock line is disconnected. A capacitor must be inserted between this pin and ground. |

| R                        | 36                         | VCO circuit. This pin sets the charge and discharge current. A resistor must be inserted between this pin and ground.                                                                                                     |

| с                        | 37                         | VCO oscillator connection. A capacitor must be inserted between this pin and ground. Select a value for that capacitor such that the C pin oscillator frequency does not exceed 1 MHz.                                    |

| FIL                      | 42                         | Inverting input to the VCO filter amplifier. This pin is connected to the VCO PLL through an (IC internal) 10-kW resistor.                                                                                                |

| FILO                     | 41                         | VCO filter amplifier output. This pin is connected to the VCO circuit internally.                                                                                                                                         |

| D <sub>OUT</sub>         | 3                          | Speed discriminator output. A low level is output when the motor is over speed.                                                                                                                                           |

| R <sub>OUT</sub>         | 4                          | PLL circuit output. Outputs the result of the phase comparison between 1/2fCLK and 1/2fFG.                                                                                                                                |

| LD                       | 5                          | Lock detection output. This is an open collector output.<br>This pin outputs a low level when the motor speed is within the locked range (±6.25%).                                                                        |

| INT <sub>REF</sub>       | 43                         | Integrating amplifier noninverting input (the 1/2 V <sub>CC</sub> potential)                                                                                                                                              |

| INT <sub>IN</sub>        | 2                          | Integrating amplifier inverting input                                                                                                                                                                                     |

| INT <sub>OUT</sub>       | 1                          | Integrating amplifier output                                                                                                                                                                                              |

| тос                      | 44                         | Torque command input. Normally, this pin is connected to the INTOUT pin. Lowering the TOC pin potential increases the torque by changing the PWM signal duty for the UL, VL, and WL outputs.                              |

| FGIN+                    | 15                         | FG amplifier noninverting input (the $1/2 V_{CC}$ potential). A capacitor must be inserted between this pin and ground.                                                                                                   |

| FGIN <sup>_</sup>        | 14                         | FG amplifier inverting input                                                                                                                                                                                              |

| FG <sub>OUT</sub>        | 13                         | FG amplifier output                                                                                                                                                                                                       |

| FGS <sub>OUT</sub>       | 12                         | FG amplifier (post-Schmitt) output. This is an open collector output.                                                                                                                                                     |

| RF                       | 25                         | Output current detection. A resistor must be inserted between this pin and ground. This resistor sets the maximum output current $I_{OUT}$ to be 0.5/Rf.                                                                  |

| S/S                      | 9                          | Start/stop control input. Apply a low level for start, and either a high level or an open (high-impedance) state for start.                                                                                               |

| F/R                      | 7                          | Forward/reverse control input. Apply a low level for forward, and either a high level or an open (high-impedance) state for reverse.                                                                                      |

| BR                       | 6                          | Braking control input (short braking operation). Apply a low level for start, and either a high level or an open (high-impedance) state to brake the motor.                                                               |

| CLK                      | 8                          | External clock signal input. 10 kHz max.                                                                                                                                                                                  |

| N1                       | 10                         | Speed discriminator count value selection inputs                                                                                                                                                                          |

| N2                       | 11                         |                                                                                                                                                                                                                           |

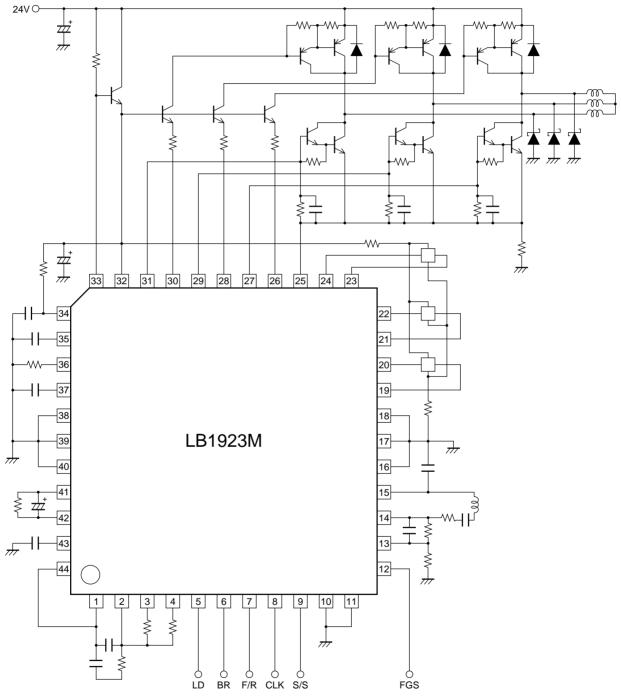

## Sample Application Circuit

## **IC Operation Description**

1. Speed Control Circuit

This IC implements speed control using the combination of a speed discriminator circuit and a PLL circuit. The speed discriminator and the PLL circuit output (using a charge pump technique) an error signal once every two FG periods. As compared to the earlier technique in which only a speed discriminator circuit was used, the combination of a speed discriminator and a PLL circuit allows variations in motor speed to be better suppressed when a motor that has large load variations is used. The FG servo frequency is controlled to be the same frequency as the clock signal input to the CLK pin. This means that the motor speed can be changed by changing the clock frequency.

## 2. VCO Circuit

The LB1821M includes an on-chip VCO circuit to generate the reference signal for the speed discriminator circuit. The reference signal frequency is determined by the following formula.

- $f_{VCO} = f_{CLK} \times number of counts$

- f<sub>VCO</sub>: Reference signal frequency

- f<sub>CLK</sub>: Frequency of the externally input clock signal

The range over which the reference signal can be varied is determined by the resistor and capacitor connected to the R pin (pin 36) and the C pin (pin 37) and by the VCO loop filter constants (the external constants connected to pins 41 and 42).

(Reference Values)

| Supply voltage   | R (kΩ) | C (pF) |

|------------------|--------|--------|

| $V_{CC} = 5 V$   | 4.7    | 390    |

| $V_{CC} = 6.3 V$ | 4.7    | 820    |

The value of R must not be less than 2.7 k $\Omega$ .

Applications can handle a wider range of speed variations than would be possible if a fixed number of counts was used by changing the number of discriminator counts (which is related to the divisor in the VCO circuit). The number of counts can be switched between 64, 128, 256, and 512 by setting the N1 (pin 10) and N2 (pin 11) pins.

3. Output Drive Circuit

To reduce power loss in the output, this IC adopts the direct PWM drive technique. The output transistors (which are external to the IC) are always saturated when on, and the motor drive output is adjusted by changing the duty with which the output is on. Since the (external) output switching is handled by the upper side output transistors, a Schottky diode or similar device must be connected between the output (OUT) and ground. This is because a through current will flows at the instant the upper side output transistors turn on if a diode with a short reverse recovery time is not used. A rectifying diode can be used between OUT and  $V_{CC}$ . Transistors that have no parasitic diodes must be used for the lower side output transistors. If these transistors have parasitic diode components, then through currents will occur due to the reverse recovery time of the parasitic diodes despite the inclusion of the external Schottky diodes.

4. Current Limiter Circuit

The current limiter circuit limits the (peak) current at the value  $I = V_{RF}/R_f$  ( $V_{RF} = 0.52$  V (typical),  $R_f$ : current detection resistor). The current limitation operation consists of reducing the output duty to suppress the current.

5. Speed Lock Range

The speed lock range is  $\pm 6.25\%$  of the fixed speed. When the motor speed is in the lock range, the LD pin (an open collector output) goes low. If the motor speed goes out of the lock range, the motor on duty is adjusted according to the speed error to control the motor speed to be within the lock range.

#### 6. Notes on the PWM Frequency

The PWM frequency is determined by the resistor and capacitor connected to the CR pin.

$f_{PWM} \approx 1/(0.48 \times C \times R)$

A PWM frequency of between 15 and 25 kHz is desirable. If the PWM frequency is too low, the motor may resonate at the PWM frequency during motor control, and if that frequency is in the audible range, that resonation may result in audible noise. If the PWM frequency is too high, the output transistor switching loss will increase. The external resistor must not have a value under 30 k $\Omega$ .

### 7. Hall Input Signals

Input signals with an amplitude greater than the hysteresis (60 mV, maximum) are required for the Hall inputs. An input amplitude of 100 mV or greater is desirable, taking noise and other considerations into account. The Hall input DC voltage must be set to fall within the common-mode input voltage range specifications.

8. Forward/Reverse (F/R) Switching

The F/R pin can be used to switch the motor direction. The direction can be switched with the F/R pin even if the motor is turning. The IC circuit is designed to compensate for the through currents that occur when the direction is switched. However, caution is required with respect to increases in the  $V_{CC}$  voltage (due to motor current returning to the power system instantaneously) during direction switching. If this is a problem, try increasing the capacitance of the capacitor connected between the power supply and ground.

9. Brake Switching

The LB1923M implements a short braking technique in which the upper side transistors (the external transistors) for all phases are turned on. (The lower side transistors for all phases are turned off.) This means that the output current during braking does not pass through the  $R_f$  (the current detection resistor) and therefore that the current limiter does not function. Thus caution is required. During braking, the upper side transistors operate at a 100% duty, regardless of the motor speed. The braking function can be operated and released in the start state. Thus motor start and stop control can be performed from the brake pin with the S/S pin at the low level, i.e., with the system in the start state. If the startup time is a problem, the motor can be started with a shorter startup time by using the brake pin for motor start/stop control than it can with the S/S pin. (This is because the stop state is a power saving state, and restarting from this state requires waiting the time required for the VCO circuit to stabilize.)

10. Constraint Protection Circuit

The LB1923M includes an on-chip constraint protection circuit to protect the IC and the motor in motor constraint mode. If the LD output remains high (indicating the locked state) for a fixed period in the start state, the upper side (external) transistors are turned off. This time is set by the capacitance of the capacitor attached to the CROCK pin. A time of a few seconds can be set with a capacitance of under  $0.1 \, \mu$ F.

$\langle$ Set time (s) $\rangle \approx 44 \times C (\mu F)$

To release the constraint protection state, the LB1923M must be set to either the stop state or the brake state, or power must be reapplied. The CROCK pin must be connected to ground if the constraint protection circuit is not used. However, note that the clock disconnection protection circuit described later cannot be used in this case.

11. Clock Disconnection Protection Circuit

If clock input stops with the LB1923M in the start state, this protection circuit operates and turns off the (external) upper side output transistors. If the clock is reapplied, the IC resumes operation.

12. Low-Voltage Protection Circuit

The LB1923M includes a low-voltage protection circuit to protect against incorrect operation when power is first applied or if the power-supply voltage ( $V_{CC}$ ) falls. The (external) upper side output transistors are turned off if  $V_{CC}$  falls under about 3.75 volts, and this function is cleared at about 4.0 volts.

13. Power Supply Stabilization

Since this IC is used in applications that draw large output currents, the power-supply line is subject to fluctuations. Therefore, capacitors with capacitances adequate to stabilize the power-supply voltage must be connected between the  $V_{CC}$  pin and ground. If diodes are inserted in the power-supply line to prevent IC destruction due to reverse power supply connection, since this makes the power-supply voltage even more subject to fluctuations, even larger capacitors will be required.

14. Ground Lines

The signal system ground and the output system ground must be separated and a single ground point must be taken at the connector. Since the output system ground carries large currents, this ground line must be made as short as possible.

Output system ground ... Ground for R<sub>f</sub> and the output diodes

Signal system ground ... Ground for the IC and the IC external components

#### 15. $V_{REG}$ Pin

If a motor drive system is formed from a single power supply, the  $V_{REG}$  pin (pin 33) can be used to create the powersupply voltage (about 6.3 V) for this IC. The  $V_{REG}$  pin is a shunt regulator and generates a voltage of about 7 volts by passing a current through an external resistor. A stable voltage can be generated by setting the current to value in the range 1 to 7 mA. The external transistors must have current capacities of at least 80 mA (to cover the I<sub>CC</sub> + Hall bias current + output current <source> requirements) and they must have voltage handling capacities in excess of the motor power-supply voltage. Since the heat generated by these transistor may be a problem, heat sinks may be required depending on the packages used. If the IC power-supply voltage (4.4 to 7.0 V) is provided from an external circuit, apply that voltage directly to the V<sub>CC</sub> pin(pin 32). In that case, the V<sub>REG</sub> pin must either be left open or connected to ground.

#### 16. FG Amplifier

Normally, the FG amplifier is used to construct a filter amplifier such as that shown in the application circuit to reject noise. Since a Schmitt comparator is connected after the FG amplifier, applications must set the amplification so that the amplifier output amplitude is at least 250 mV p-p. (However, a setting that results in an amplitude of 1 to 3 V p-p during steady-state rotation is desirable.) The capacitor connected between the FG<sub>IN</sub>+ pin (pin 15) and ground is required for bias voltage stabilization and to generate the initial reset pulse for the internal logic. The reset pulse is generated in the time it takes for the FG<sub>IN</sub>+ pin to go from 0 to about 1.3 V.

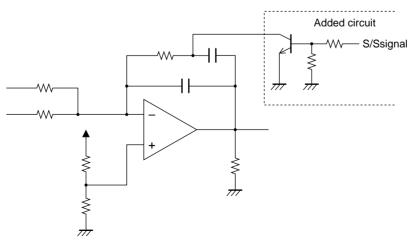

17. Integrating Amplifier

The integrating amplifier integrates the speed error pulses and the phase error pulses and converts them to a speed command voltage. At the same time it also sets the control loop gain and frequency characteristics using external components. The integrating amplifier output (pin 1) is normally connected to the TOC pin (pin 44) by an external line. Separating the integrating amplifier output and the PWM control circuit allows applications to switch the integrating amplifier constants using an external operational amplifier, analog switch, or other circuit. This is useful in applications that require integration constant switching due to a wide range of variability in the motor speeds that must be provided.

18. VCO Filter Amplifier

The VCO filter amplifier converts the VCO system PLL output to the VCO voltage. The amplifier input resistor (about 10 k $\Omega$ ) is built in. Therefore, the gain and the frequency characteristics are set by the feedback resistor and the feedback capacitor. Since the range of frequency variation supported becomes narrower as the gain is reduced, it is desirable to set the gain of this amplifier to be 1 or higher.

19. Startup Techniques

If the motor is started and stopped repeatedly over a short period, the charge accumulated on the integrating amplifier's external capacitor may become a problem. (This can result in abnormal speed overshooting at startup and other problems.) The circuit shown below can be effective at resolving this problem.

### Integrating amplifier related external circuit

## **Pin Functions**

| Pin No. | Pin                | Functions                                                                                                                    | Equivalent circuit                                                                                      |

|---------|--------------------|------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|

| 1       | INT <sub>OUT</sub> | Integrating amplifier output (speed control)                                                                                 |                                                                                                         |

| 2       | INT <sub>IN</sub>  | Integrating amplifier inverting input                                                                                        |                                                                                                         |

| 43      | INTREF             | Integrating amplifier noninverting input (a potential of 1/2 ${\rm V}_{\rm CC}$ )                                            | $\begin{array}{c} 43 \\ \hline \\ 43 \\ \hline \\ \\ \hline \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ $ |

| 3       | D <sub>OUT</sub>   | Speed discriminator output Acceleration $\rightarrow$ low                                                                    |                                                                                                         |

| 4       | P <sub>OUT</sub>   | Speed control system PLL output<br>Outputs the phase comparison result for<br>1/2 f <sub>CLK</sub> and 1/2 f <sub>FG</sub> . | VCC<br>(4)                                                                                              |

| 5       | LD                 | Speed lock detection output<br>Goes low when the motor speed is within the speed lock<br>range (±6.25%).                     | Vcc<br>5<br>m<br>m<br>m<br>m                                                                            |

| Pin No. | Pin | Functions                                                                                                                                                                                       | Equivalent circuit                                                                                      |

|---------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|

| 6       | BR  | Brake control (short braking operation)<br>Low: 0 to 1.5 V<br>High: 4.0 V to $V_{CC}$<br>Goes high when left open.<br>High or open for brake mode operation.<br>The hysteresis is about 0.45 V. | V <sub>CC</sub><br>63 kΩ<br>200 Ω<br>6<br>μ<br>μ<br>μ<br>μ<br>μ<br>μ<br>μ<br>μ<br>μ<br>μ<br>μ<br>μ<br>μ |

| 7       | F/R | Forward/reverse control<br>Low: 0 to 1.5 V<br>High: 4.0 V to $V_{CC}$<br>An open state functions as a high-level input.<br>Low for forward.<br>The hysteresis is about 0.45 V.                  | V <sub>CC</sub><br>63 kΩ<br>63 kΩ<br>7<br>7<br>7<br>7<br>7<br>7<br>7                                    |

| 8       | CLK | External clock signal input<br>Low: 0 to 1.5 V<br>High: 4.0 V to V <sub>CC</sub><br>An open state functions as a high-level input.<br>The hysteresis is about 0.45 V.<br>f = 10  kHz, maximum   | V <sub>CC</sub><br>63 kΩ<br>200 Ω<br>8<br>π<br>π<br>π<br>π<br>π                                         |

| 9       | S/S | Start/stop control<br>Low: 0 to 1.5 V<br>High: 4.0 V to V <sub>REG</sub><br>An open state functions as a high-level input.<br>Low for start.<br>The hysteresis is about 0.45 V.                 | V <sub>CC</sub><br>63 kΩ<br>9<br>4<br>7<br>7<br>9<br>7<br>7<br>7<br>9                                   |

| 10      | N1  | Speed discriminator count switching<br>Low: 0 to 1.5 V<br>High: 4.0 V to V <sub>CC</sub><br>An open state functions as a high-level input.<br>The hysteresis is about 0.45 V.                   | V <sub>CC</sub><br>63 kΩ <sup>§</sup><br>10<br>10<br>10                                                 |

| Pin No.              | Pin                                      | Functions                                                                                                                                                              | Equivalent circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|----------------------|------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 11                   | N2                                       | Speed discriminator count switching<br>Low: 0 to 1.5 V<br>High: 4.0 V to $V_{CC}$<br>An open state functions as a high-level input.<br>The hysteresis is about 0.45 V. | $\frac{\sqrt{CC}}{63 \text{ k}\Omega}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 12                   | FGS <sub>OUT</sub>                       | FG amplifier output (after the Schmitt circuit)<br>This is an open collector output.                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 13                   | FG <sub>OUT</sub>                        | FG amplifier output<br>This pin is connected to the FG Schmitt comparator circuit<br>internally in the IC.                                                             | VCC<br>()<br>()<br>()<br>()<br>()<br>()<br>()<br>()<br>()<br>()                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 14<br>15             | FG <sub>IN</sub> -<br>FG <sub>IN</sub> + | FG amplifier inputs<br>An initial reset is applied to the logic circuit block by<br>connecting a capacitor (of about 0.1 μF) between the FGIN+<br>pin and ground.      | $V_{CC}$ $20 \text{ k}\Omega {\otimes}$ $FG \text{ reset circuit}$ $(15)$ $20 \text{ k}\Omega {\otimes}$ $(15)$ $20 \text{ k}\Omega {\otimes}$ $(15)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(1$ |

| 16 to 18<br>38 to 40 | GND                                      | Ground connections<br>These pins are all connected internally to the frame.                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Pin No.                          | Pin                                          | Functions                                                                                                                                                                                                                                                                            | Equivalent circuit                                                                 |

|----------------------------------|----------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|

| 19<br>20<br>21<br>22<br>23<br>24 | IN1⁺<br>IN1⁻<br>IN2⁺<br>IN2⁻<br>IN3⁺<br>IN3⁻ | Hall inputs<br>High is defined as $IN^* > IN^-$ , and low as the opposite.<br>An amplitude of 100 mV p-p (differential) or more is<br>desirable in the Hall signals. Connect capacitors between<br>the IN* and IN <sup>-</sup> pins if noise on the Hall signals causes<br>problems. |                                                                                    |

| 25                               | RF                                           | Output current detection<br>Connect a resistor between this pin and ground.<br>The output limitation maximum current, $I_{OUT}$ , is set to be<br>0.52/R <sub>f</sub> by this resistor.                                                                                              |                                                                                    |

| 26<br>28<br>30                   | UL<br>VL<br>WL                               | This IC implements duty control using output signal PWM.<br>These are open collector sink outputs.                                                                                                                                                                                   |                                                                                    |

| 27<br>29<br>31                   | UH<br>VH<br>WH                               | Outputs (Fixed current source outputs)                                                                                                                                                                                                                                               | V <sub>CC</sub><br>(27)(29)(31)<br>2 KΩ \$<br>//////////////////////////////////// |

| 32                               | V <sub>CC</sub>                              | Power-supply voltage<br>Connect a capacitor between this pin and ground for power<br>supply stabilization.                                                                                                                                                                           |                                                                                    |

| Pin No. | Pin              | Functions                                                                                                                                                                                                       | Equivalent circuit                                                                                                      |

|---------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|

| 33      | V <sub>REG</sub> | 7-V shunt regulator output                                                                                                                                                                                      |                                                                                                                         |

| 34      | CR               | PWM oscillator frequency setting                                                                                                                                                                                | $\begin{array}{c} V_{CC} \\ \hline \\ $ |

| 35      | CROCK            | Sets the operating time for the lock protection circuit. A protection operating time of about 2.1 seconds can be set by connecting a capacitor (of about 0.047 $\mu$ F) between this pin and ground.            | $\begin{array}{c} V_{CC} \\ \hline \\ \hline \\ \\ \hline \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ $                         |

| 36      | R                | Setting for the charge current used for the VCO circuit C pin Connect a resistor between this pin and ground. The value of that resistor must not be lower than 2.7 k $\Omega$ .                                | $\begin{array}{c} \underbrace{V_{CC}} \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ $                              |

| 37      | С                | VCO oscillator connection. This pin sets the VCO<br>frequency.<br>Connect a capacitor between this pin and ground.<br>Set the value of the capacitor so that the oscillator<br>frequency does not exceed 1 MHz. |                                                                                                                         |

| Pin No. | Pin  | Functions                                                                                                                                                                                                                                                                        | Equivalent circuit                                          |

|---------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|

| 41      | FILO | VCO filter amplifier output<br>This pin is connected to the VCO circuit internally in the IC.                                                                                                                                                                                    | $V_{CC}$<br>$200 \Omega$ $V_{CO}$ input<br>41               |

| 42      | FIL  | VCO filter amplifier inverting input<br>This pin is connected through a 10-k $\Omega$ resistor internally in<br>the IC to the VCO system PLL output.                                                                                                                             | $\begin{array}{c} V_{CC} \\ 43 \text{ k}\Omega \end{array}$ |