# Single-Chip PLL Microcontrollers

# Overview

The LC72358N, LC72362N, and LC72366 are 1.33  $\mu$ s instruction execution time single-chip microcontrollers for electronic tuning applications. These products incorporate a high-speed locking circuit and a high-performance direct PLL circuit that can control the local oscillator C/N characteristics. These products have 256 or 512 bytes of RAM and 16K, 24K or 32K bytes of program ROM on chip, and incorporate a three-channel serial I/O interface, a six-channel A/D converter and other interfaces.

# **Features**

- ROM

- LC72358N: 8K steps (8191 × 16 bits)

- LC72362N: 12K steps (12287 × 16 bits)

- LC72366: 16K steps (16383 × 16 bits) The subroutine area in both products is 4K steps (4095 × 16 bits).

- RAM

- LC72358N, 72362N: 512 × 4 bits (banks 0 to 7)

LC72366: 1K × 4 bits (banks 0 to F)

- Stack: Eight levels

- Serial I/O: Three channels (8-bit 3-wire format) There are three internal serial clocks: 12.5 kHz, 37.5 kHz and 187.5 kHz.

- External interrupts: Two channels (the INT0 and INT1 pins) Switching between rising and falling edge detection is supported.

- Internal interrupts:

- Three channels

- Two internal timer interrupt channels

The timers provide eight interrupt periods: 100 μs, 1 ms, 2 ms, 5 ms, 10 ms, 50 ms, 125 ms and 250 ms.

One serial I/O interrupt channel

- Multiple interrupt levels:

Four levels

- Hardware priority order

- INTO pin > INT1 pin > SI/O pin > internal timer 0 > internal timer 1

- A/D converter: Six channels (6-bit successive approximation type)

- General-purpose ports

- Input ports: 10

- Output ports: 28

- I/O ports: 25 (These pins can be switched between input and output in bit units.)

- PLL block

- Built-in sub-charge pump for high-speed locking

- Support for dead zone control

- Built-in unlock detection circuit

- Twelve reference frequencies: 1, 3, 3.125, 5, 6.25, 9, 10, 12.5, 25, 30, 50 and 100 kHz

- Universal counter: 20 bits

Supports frequency and period measurement with counting periods of 1, 4, 8 and 32 ms.

- Timers: Timer interrupt periods

- $100~\mu s, 1~m s, 2~m s, 5~m s, 10~m s, 50~m s, 125~m s$  and 250 m s

- Beep: Six frequencies: 2.08 kHz, 2.25 kHz, 2.5 kHz, 3.0 kHz, 3.75 kHz, 4.17 kHz.

- Reset: Built-in voltage detection type reset circuit

- Cycle time: 1.33 µs (all instructions execute in one cycle)

- Halt mode: The microcontroller operating clock is stopped in halt mode. There are four types of event that clear halt mode: interrupt requests, timer FF overflows, key inputs, and hold pin inputs.

- Operating supply voltage: 4.5 to 5.5 V (3.5 to 5.5 V when only the controller block operates)

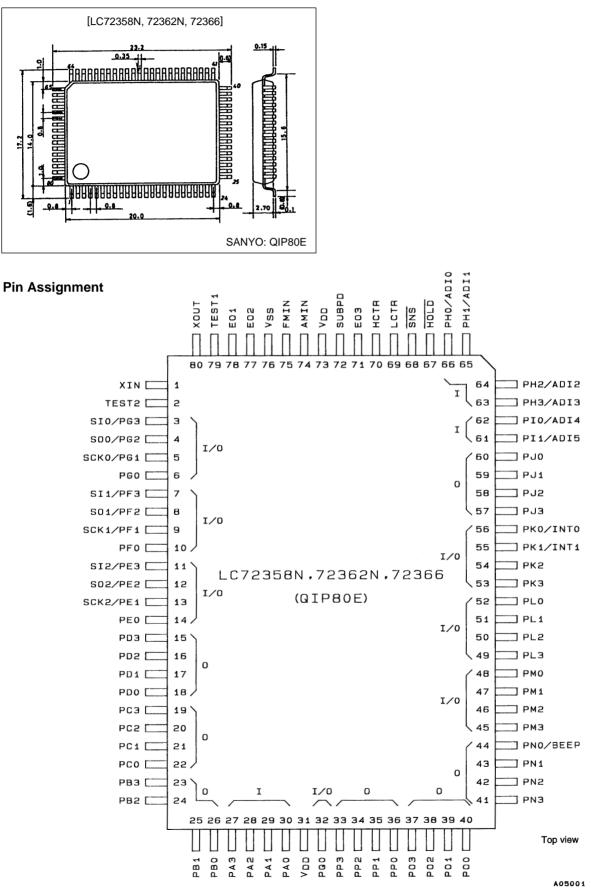

- Package: QFP80E (QIP80E)

- OTP version: LC72P366

- Development tools: Emulator ......RE32N Evaluation chip......LC72EV350

- Evaluation chip board ......EB-72EV350

This LSI can easily use CCB that is SANYO's original bus format.

- CCB is a trademark of SANYO ELECTRIC CO., LTD.

- CCB is SANYO's original bus format and all the bus addresses are controlled by SANYO.

SANYO Electric Co., Ltd. Semiconductor Bussiness Headquarters TOKYO OFFICE Tokyo Bldg., 1-10, 1 Chome, Ueno, Taito-ku, TOKYO, 110 JAPAN

## **Package Dimensions**

unit: mm

#### 3174-QFP80E

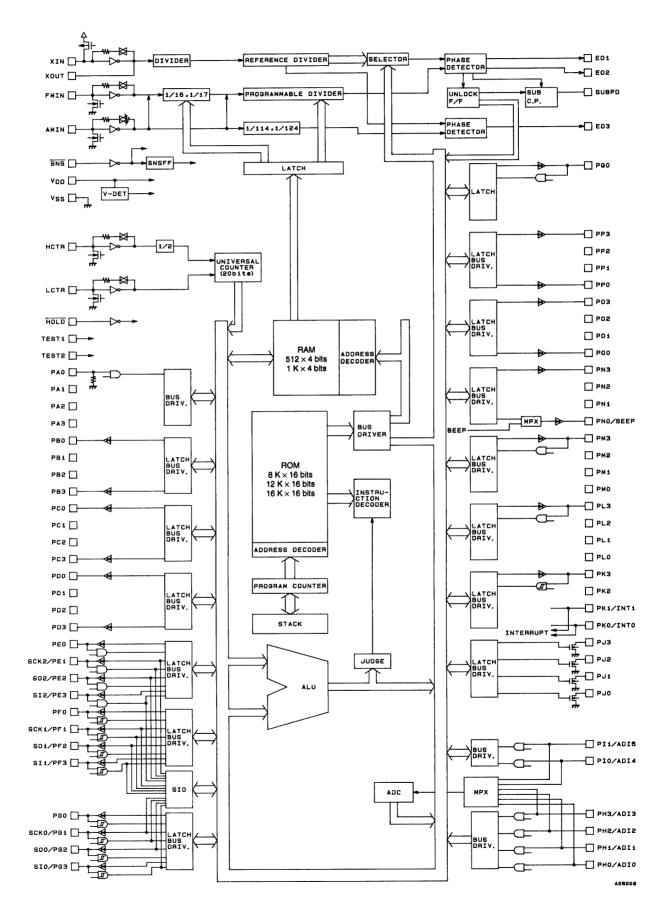

#### **Block Diagram**

# Specifications

# Absolute Maximum Ratings at Ta = $25^{\circ}$ C, V<sub>ss</sub> = 0 V

| Parameter                   | Symbol               | Conditions                                                        | Ratings                       | Unit |

|-----------------------------|----------------------|-------------------------------------------------------------------|-------------------------------|------|

| Maximum supply voltage      | V <sub>DD</sub> max  |                                                                   | -0.3 to +6.5                  | V    |

| Input voltage               | V <sub>IN</sub>      | All input pins                                                    | -0.3 to V <sub>DD</sub> + 0.3 | V    |

| Output valtage              | V <sub>OUT</sub> (1) | J port                                                            | -0.3 to +15                   | V    |

| Output voltage              | V <sub>out</sub> (2) | All output ports other than $V_{out}$ (1)                         | -0.3 to V <sub>DD</sub> + 0.3 | V    |

|                             | I <sub>оυт</sub> (1) | J port                                                            | 0 to 5                        | mA   |

| Output current              | I <sub>OUT</sub> (2) | D, E, F, G, K, L, M, N, O, P and Q ports,<br>EO1, EO2, EO3, SUBPD | 0 to 3                        | mA   |

|                             | I <sub>OUT</sub> (3) | B and C ports                                                     | 0 to 1                        | mA   |

| Allowable power dissipation | Pd max               | Ta = -40 to +85°C                                                 | 400                           | mW   |

| Operating temperature       | Topr                 |                                                                   | -40 to +85                    | °C   |

| Storage temperature         | Tstg                 |                                                                   | -45 to +125                   | °C   |

# Allowable Operating Ranges at Ta=-40 to $+85^{\circ}C,\,V_{_{DD}}=3.5$ to 5.5 V

| Parameter                | Symbol              | Conditions                                                            | min                 | typ | max                 | Unit |

|--------------------------|---------------------|-----------------------------------------------------------------------|---------------------|-----|---------------------|------|

|                          | V <sub>DD</sub> (1) | CPU and PLL operating                                                 | 4.5                 | 5.0 | 5.5                 | V    |

| Supply voltage           | V <sub>DD</sub> (2) | CPU operating                                                         | 3.5                 |     | 5.5                 | V    |

|                          | V <sub>DD</sub> (3) | Memory retention                                                      | 1.3                 |     | 5.5                 | V    |

|                          | V <sub>IH</sub> (1) | E, H, I, L, M and Q ports, HCTR and LCTR<br>(when selected for input) | $0.7 \ V_{_{DD}}$   |     | V <sub>DD</sub>     | V    |

| Input high level voltage | V <sub>IH</sub> (2) | F, G and K ports, LCTR (period measurement mode), HOLD                | $0.8 V_{\text{dd}}$ |     | V <sub>DD</sub>     | V    |

|                          | V <sub>IH</sub> (3) | SNS                                                                   | 2.5                 |     | V <sub>DD</sub>     | V    |

|                          | V <sub>IH</sub> (4) | A port                                                                | $0.6 \ V_{_{DD}}$   |     | V <sub>DD</sub>     | V    |

|                          | V <sub>IL</sub> (1) | E, H, I, L, M and Q ports, HCTR and LCTR<br>(when selected for input) | 0                   |     | 0.3 V <sub>DD</sub> | V    |

| Input low level voltage  | V <sub>IL</sub> (2) | A, F, G and K ports, LCTR (period measurement mode)                   | 0                   |     | 0.2 V <sub>DD</sub> | V    |

| 1                        | V <sub>IL</sub> (3) | SNS                                                                   | 0                   |     | 1.3                 | V    |

|                          | V <sub>IL</sub> (4) | HOLD                                                                  | 0                   |     | 0.4 V <sub>DD</sub> | V    |

|                          | f <sub>IN</sub> (1) | XIN                                                                   | 4.0                 | 4.5 | 5.0                 | MHz  |

|                          | f <sub>IN</sub> (2) | FMIN: V <sub>IN</sub> (2), V <sub>DD</sub> (1)                        | 10                  |     | 150                 | MHz  |

|                          | f <sub>IN</sub> (3) | FMIN: V <sub>IN</sub> (3), V <sub>DD</sub> (1)                        | 10                  |     | 130                 | MHz  |

| Input frequency          | f <sub>IN</sub> (4) | AMIN (H): V <sub>IN</sub> (3), V <sub>DD</sub> (1)                    | 2.0                 |     | 40                  | MHz  |

| input nequency           | f <sub>IN</sub> (5) | AMIN (L): V <sub>IN</sub> (3), V <sub>DD</sub> (1)                    | 0.5                 |     | 10                  | MHz  |

|                          | f <sub>IN</sub> (6) | HCTR: V <sub>IN</sub> (3), V <sub>DD</sub> (1)                        | 0.4                 |     | 12                  | MHz  |

|                          | f <sub>IN</sub> (7) | LCTR: V <sub>IN</sub> (3), V <sub>DD</sub> (1)                        | 100                 |     | 500                 | kHz  |

|                          | f <sub>IN</sub> (8) | LCTR (period measurement): $V_{IH}$ (2), $V_{IL}$ (2), $V_{DD}$ (1)   | 1                   |     | 20 × 103            | Hz   |

|                          | V <sub>IN</sub> (1) | XIN                                                                   | 0.5                 |     | 1.5                 | Vrms |

| Input amplitude          | V <sub>IN</sub> (2) | FMIN                                                                  | 0.10                |     | 1.5                 | Vrms |

|                          | V <sub>IN</sub> (3) | FMIN, AMIN, HCTR, LCTR                                                | 0.07                |     | 1.5                 | Vrms |

| Input voltage range      | V <sub>IN</sub> (4) | ADI0 to ADI5                                                          | 0                   |     | V <sub>DD</sub>     | V    |

| Parameter                    | Symbol               | Conditions                                                                                                                                                                                                      | min                   | typ                   | max                  | Unit |

|------------------------------|----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|-----------------------|----------------------|------|

|                              | I <sub>III</sub> (1) | XIN: $V_{I} = V_{DD} = 5.0 V$                                                                                                                                                                                   | 2.0                   | 5.0                   | 15                   | μA   |

|                              | I <sub>IH</sub> (2)  | FMIN, AMIN, HCTR, LCTR: $V_1 = V_{DD} = 5.0 \text{ V}$                                                                                                                                                          | 4.0                   | 10                    | 30                   | μA   |

| Input high level current     | I <sub>н</sub> (3)   | A, E, F, G, H, I, K, L, M and Q ports, <u>SNS</u> , <u>HOLD</u> ,<br>HCTR, LCTR, with no pull-down resistor on A port.<br>$V_i = V_{DD} = 5.0 V$ ,<br>with the E, F, G, K, L, M and Q ports selected for input. |                       |                       | 3.0                  | μA   |

|                              | I <sub>IH</sub> (4)  | A port: pull-down resistor present, $V_1 = V_{DD} = 5.0 V$                                                                                                                                                      |                       | 50                    |                      | μA   |

|                              | I <sub>⊫</sub> (1)   | XIN: $V_1 = V_{SS}$                                                                                                                                                                                             | 2.0                   | 5.0                   | 15                   | μA   |

|                              | I <sub>IL</sub> (2)  | FMIN, AMIN, HCTR, LCTR: V <sub>1</sub> = V <sub>SS</sub>                                                                                                                                                        | 4.0                   | 10                    | 30                   | μA   |

| Input low level current      | I <sub>⊫</sub> (3)   | A, E, F, G, H, I, K, L, M and Q ports, SNS, HOLD,<br>HCTR, LCTR, with no pull-down resistor on A port.<br>$V_i = V_{ss}$ ,<br>with the E, F, G, K, L, M and Q ports selected for input.                         |                       |                       | 3.0                  | μA   |

| Input floating voltage       | V <sub>IF</sub>      | A port: pull-down resistor present                                                                                                                                                                              |                       |                       | 0.05 V <sub>DD</sub> | V    |

| Pull-down resistance         | R <sub>PD</sub> (1)  | A port: pull-down resistor present, $V_{DD} = 5 V$                                                                                                                                                              | 75                    | 100                   | 200                  | kΩ   |

| Hysteresis                   | V <sub>H</sub>       | F, G and K ports, LCTR (period measurement mode)                                                                                                                                                                | 0.1 V <sub>DD</sub>   | 0.2 V <sub>DD</sub>   |                      | V    |

|                              | V <sub>он</sub> (1)  | B and C ports: $I_0 = -1 \text{ mA}$                                                                                                                                                                            | V <sub>DD</sub> - 2.0 | V <sub>DD</sub> - 1.0 |                      | V    |

| Output high lovel veltage    | V <sub>он</sub> (2)  | D, E, F, G, K, L, M, N, O, P and Q ports: $I_0 = -1 \text{ mA}$                                                                                                                                                 | V <sub>DD</sub> - 1.0 |                       |                      | V    |

| Output high level voltage    | V <sub>он</sub> (3)  | EO1, EO2, EO3, SUBPD: Ι <sub>0</sub> = -500 μA                                                                                                                                                                  | V <sub>DD</sub> - 1.0 |                       |                      | V    |

|                              | V <sub>он</sub> (4)  | XOUT: Ι <sub>o</sub> = -200 μA                                                                                                                                                                                  | V <sub>DD</sub> - 1.0 |                       |                      | V    |

|                              | V <sub>oL</sub> (1)  | B and C ports: $I_0 = 50 \ \mu A$                                                                                                                                                                               |                       | 1.0                   | 2.0                  | V    |

|                              | V <sub>oL</sub> (2)  | D, E, F, G, K, L, M, N, O, P and Q ports: I <sub>o</sub> = 1 mA                                                                                                                                                 |                       |                       | 1.0                  | V    |

| Output low level voltage     | V <sub>oL</sub> (3)  | EO1, EO2, EO3, SUBPD: Ι <sub>o</sub> = 500 μA                                                                                                                                                                   |                       |                       | 1.0                  | V    |

|                              | V <sub>oL</sub> (4)  | XOUT: Ι <sub>o</sub> = 200 μA                                                                                                                                                                                   |                       |                       | 1.5                  | V    |

|                              | V <sub>oL</sub> (5)  | J port: I <sub>o</sub> = 5 mA                                                                                                                                                                                   |                       |                       | 2.0                  | V    |

|                              | I <sub>OFF</sub> (1) | B, C, D, E, F, G, K, L, M, N, O, P and Q ports                                                                                                                                                                  | -3.0                  |                       | +3.0                 | μA   |

| Output off leakage current   | I <sub>OFF</sub> (2) | EO1, EO2, EO3, SUBPD                                                                                                                                                                                            | -100                  |                       | +100                 | nA   |

|                              | I <sub>OFF</sub> (3) | J port                                                                                                                                                                                                          | -5.0                  |                       | +5.0                 | μA   |

| A/D conversion error         |                      | ADI0 to ADI5: V <sub>DD</sub> (1)                                                                                                                                                                               | -1/2                  |                       | +1/2                 | LSB  |

| Reject pulse width           | P <sub>REJ</sub>     | SNS                                                                                                                                                                                                             |                       |                       | 50                   | μs   |

| Power-down detection voltage | V <sub>det</sub>     |                                                                                                                                                                                                                 | 2.7                   | 3.0                   | 3.3                  | V    |

| Pull-down resistance         | R <sub>PD</sub> (2)  | TEST1, TEST2                                                                                                                                                                                                    |                       | 10                    |                      | kΩ   |

|                              | I <sub>DD</sub> (1)  | V <sub>DD</sub> (1): f <sub>IN</sub> (2) = 130 MHz, Ta = 25°C                                                                                                                                                   |                       | 12                    | 24                   | mA   |

| Ourseat design               | I <sub>DD</sub> (2)  | V <sub>DD</sub> (2): Halt mode*, Ta = 25°C (Figure 1)                                                                                                                                                           |                       | 0.45                  | (0.9)                | mA   |

| Current drain                | I <sub>DD</sub> (3)  | $V_{DD} = 5.5 \text{ V}$ , oscillator stopped, Ta = 25°C (Figure 2)                                                                                                                                             |                       |                       | 5                    | μA   |

|                              | I <sub>DD</sub> (4)  | $V_{DD} = 2.5 \text{ V}$ , oscillator stopped, Ta = 25°C (Figure 2)                                                                                                                                             |                       |                       | 1                    | μA   |

Note: Execute 20 STEP instructions every 1 ms. With the PLL, counters and other functions all stopped.

() Value: LC72366

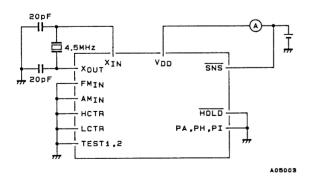

### **Test Circuit**

Note: All of the pins PB to PG and PJ to PQ must be left open. Here, the pins PE to PG, PK to PM, and PQ are selected for output.

Figure 1:  $I_{DD}(2)$  in Halt Mode

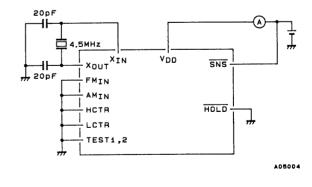

Note: All of the pins PA to PQ must be left open.

# Figure 2. $I_{DD}(3)$ and $I_{DD}(4)$ in Backup Mode

### **Pin Functions**

| Pin No.                                                       | Symbol                                                                                                                  | I/O    | I/O type                             | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|---------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|--------|--------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 30<br>29<br>28<br>27                                          | PA0<br>PA1<br>PA2<br>PA3                                                                                                | I      | Pull-down resistor<br>included Input | Key return signal input-only ports. The threshold voltage is set to a relatively low value.<br>When a key matrix is formed in combination with the PB and PC ports, up to three<br>simultaneous key presses can be detected.<br>The pull-down resistors are set by the IOS instruction with PWn = 2 for all four pins at the<br>same time and cannot be set on an individual pin basis.<br>Input is disabled in clock stop mode.                                                                                                                     |

| 26<br>25<br>24<br>23<br>22<br>21<br>20<br>19                  | PB0<br>PB1<br>PB2<br>PB3<br>PC0<br>PC1<br>PC2<br>PC3                                                                    | 0      | Unbalanced CMOS<br>push-pull         | Key source signal output-only ports. Since the output transistor circuit is an unbalanced CMOS structure, diodes to prevent shorting due to multiple key presses are not required. In clock stop mode, these pins go to the output high-impedance state. During the power-on reset, these pins go to the output high-impedance state and hold that state until an output instruction is executed.                                                                                                                                                    |

| 18<br>17<br>16<br>15                                          | PD0<br>PD1<br>PD2<br>PD3                                                                                                | 0      | CMOS push-pull                       | Output-only ports.<br>In clock stop mode, these pins go to the output high-impedance state.<br>During the power-on reset, these pins go to the output high-impedance state and hold that<br>state until an output instruction is executed.                                                                                                                                                                                                                                                                                                           |

| 14<br>13<br>12<br>11<br>10<br>9<br>8<br>7<br>6<br>5<br>4<br>3 | PE0<br>PE1/SCK2<br>PE2/SO2<br>PE3/SI2<br>PF0<br>PF1/SCK1<br>PF2/SO1<br>PF3/SI1<br>PG0<br>PG1/SCK0<br>PG2/SO0<br>PG3/SI0 | I/O    | CMOS push-pull                       | General-purpose I/O port/serial I/O pin shared-function ports.<br>The F and G port inputs are Schmitt inputs. The E ports is a normal input.<br>The IOS instruction switches these ports between general-purpose I/O ports and serial I/O<br>ports, and between input and output for general-purpose I/O ports.<br>• When used as general-purpose I/O ports these pins:<br>Can be set for input or output in bit units (bit I/O), and<br>are set for use as general-purpose I/O ports by the IOS instruction with PWn = 0.<br>b0 = SI/O 0 0          |

| 1<br>80                                                       | XIN<br>XOUT                                                                                                             | і<br>0 | _                                    | Connections for a 4.5 MHz crystal oscillator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 78<br>77                                                      | EO1<br>EO2                                                                                                              | 0      | CMOS tristate                        | Main charge pump outputs<br>These pins output a high level when the frequency generated by dividing the local<br>oscillator signal frequency by N is higher than the reference frequency, and a low level<br>when that frequency is lower.<br>These pins go to the high-impedance state when the frequencies match.<br>These pins go to the high-impedance state when the HOLD pin is set low in the hold<br>enable state.<br>In clock stop mode, during the power-on reset and in the PLL stop state, these pins go to<br>the high-impedance state. |

#### Continued from preceding page.

| Pin No.        | Symbol                                                | I/O | I/O type      | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |  |

|----------------|-------------------------------------------------------|-----|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| 76<br>73<br>31 | V <sub>ss</sub><br>V <sub>dd</sub><br>V <sub>dd</sub> | _   | _             | Power supply connections                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |  |

| 75             | FMIN                                                  | I   | Input         | FM VCO (local oscillator) input<br>This pin is selected by the PLL instruction CW1 (b1, b0 are ignored).<br>Capacitor coupling must be used for signal input.<br>Input is disabled when the HOLD pin is set low in the hold enable state.<br>Input is disabled in clock stop mode, during the power-on reset, and in the PLL stop state.                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |  |

| 74             | AMIN                                                  | I   | Input         | AM VCO (local oscillator) input         This pin is selected and the band set by the PLL instruction CW1 (b1, b0).         b1       b0       Band         1       0       2 to 40 MHz (SW)         1       1       0.5 to 10 MHz (MW, LW)         Capacitor coupling must be used for signal input.         Input is disabled when the HOLD pin is set low in the hold enable state.         Input is disabled in clock stop mode, during the power-on reset, and in the PLL stop state.                                                                                                                                                                                            |  |  |  |  |  |  |  |

| 72             | SUBPD                                                 | 0   | CMOS tristate | Sub-charge pump output         This pin, in combination with the main charge pump, allows the construction of a high-speed locking circuit.         The DZC instruction controls the sub-charge pump. <u>b3</u> <u>b2</u> <u>Operation         </u> <u>0         0         High impedance         <u>0         1         Only operates in the unlocked state (450 kHz)         <u>1         1         Normal operation         </u>         This pin goes to the high-impedance state when the HOLD pin is set low in the hold enable state.         This pin goes to the high-impedance state in clock stop mode, during the power-on reset, and in the PLL stop state.   </u></u> |  |  |  |  |  |  |  |

| 71             | EO3                                                   | 0   | CMOS tristate | Second PLL charge pump output<br>This pin outputs a low level when the frequency generated by dividing the local oscillator<br>signal frequency by N is higher than the reference frequency, and a high level when that<br>frequency is lower.<br>This pin goes to the high-impedance state when the frequencies match. (Note that this<br>pin's output logic is the opposite of that of the EO1 and EO2 pins.)<br>This pin goes to the high-impedance state when the HOLD pin is set low in the hold enable<br>state.<br>This pin goes to the high-impedance state in clock stop mode, during the power-on reset,<br>and in the PLL stop state.                                    |  |  |  |  |  |  |  |

#### Continued from preceding page.

| Pin No. | Symbol | I/O | I/O type | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|---------|--------|-----|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 70      | HCTR   | I   | Input    | <ul> <li>Universal counter/general-purpose input shared-function input port</li> <li>The IOS instruction b3 with PWn = 3 switches the pin function between universal counter input and general-purpose input.</li> <li>Frequency measurement</li> <li>The universal counter function is selected by an IOS instruction with PWn = 3 and b3 = 0.</li> <li>HCTR frequency measurement mode is set up by a UCS instruction with b3 = 0 and b2 = 0, and counting is started with a UCC instruction after the count time is selected.</li> <li>The CNTEND flag is set when the count completes.</li> <li>To operate this circuit as an AC amplifier in this mode, the input must be capacitor coupled.</li> <li>General-purpose input pin use</li> <li>The general-purpose input port function is selected by an IOS instruction with PWn = 3 and b3 = 1.</li> <li>An internal register (address: 0EH) input instruction INR (b0) is used to acquire data from this pin.</li> <li>Input is disabled in clock stop mode. (The input pin will be pulled down.)</li> <li>During the power-on reset, the universal counter function is selected.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 69      | LCTR   | I   | Input    | <ul> <li>Universal counter (frequency and period measurement)/general-purpose input shared-function input port</li> <li>The IOS instruction b2 with PWn = 3 switches the pin function between universal counter input and general-purpose input.</li> <li>Frequency measurement</li> <li>The universal counter function is selected by an IOS instruction with PWn = 3 and b2 = 0. LCTR frequency measurement mode is set up by a UCS instruction with b3 = 0 b2 = 1, and counting is started with a UCC instruction after the count time is selected.</li> <li>The CNTEND flag is set when the count completes.</li> <li>To operate this circuit as an AC amplifier in this mode, the input must be capacitor coupled.</li> <li>Period measurement</li> <li>With the universal counter function selected, set up period measurement mode with a UCS instruction with b3 = 1 and b2 = 0, and start the count with a UCC instruction after selecting the count time. The CNTEND flag will be set when the count completes. In this mode, the signal must be input with DC coupling to turn off the bias feedback resistor.</li> <li>General-purpose input pin use</li> <li>The general-purpose input port function is selected by an IOS instruction with PWn = 3, b2 = 1.</li> <li>An internal register (address: 0EH) input instruction INR (b1) is used to acquire data from this pin.</li> <li>Input is disabled in clock stop mode. (The input pin will be pulled down.)</li> <li>During the power-on reset, the universal counter function (in HCTR frequency measurement mode) is selected.</li> </ul> |

| 68      | SNS    | I   | Input    | <ul> <li>Voltage sense/general-purpose input pin shared-function port</li> <li>This circuit is designed for a relatively low input threshold voltage.</li> <li>Voltage sense pin usage</li> <li>This input pin is used to determine whether or not a power failure occurred after recovery from backup (clock stop) mode. An internal sense F/F is used for this determination. The sense F/F is tested with a TUL instruction (b2).</li> <li>General-purpose input port usage</li> <li>When used as a general-purpose input port, the state is sensed by using a TUL instruction (b3).</li> <li>Since, unlike other input ports, input is not disabled in clock stop mode and during the power-on reset, special care is required with respect to through currents.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

#### Continued from preceding page.

| Pin No.                          | Symbol                                                               | I/O | I/O type             | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|----------------------------------|----------------------------------------------------------------------|-----|----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 67                               | HOLD                                                                 | I   | Input                | PLL control and clock stop mode control<br>Setting this pin low in the hold enabled state disables input to the FMIN and AMIN pins and<br>sets the EO pin to the high-impedance state.<br>To enter clock stop mode, set the HOLDEN flag, set this pin low, and execute a CKSTP<br>instruction.<br>To clear clock stop mode, set this pin high.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 66<br>65<br>64<br>63<br>62<br>61 | PH0/ADI0<br>PH1/ADI1<br>PH2/ADI2<br>PH3/ADI3<br>PI0/ADI4<br>PI1/ADI5 | I   | Input                | <ul> <li>General-purpose input port/A/D converter shared-function pins<br/>The IOS instruction with PWn = 7 or 8 switches the pin function between general-purpose<br/>input ports and A/D converter inputs.</li> <li>General-purpose input port usage<br/>Specify general-purpose input port usage with the IOS instruction with PWn = 7 or 8 in bit<br/>units.</li> <li>A/D converter usage<br/>Specify A/D converter usage with the IOS instruction with PWn = 7 or 8 in bit units.</li> <li>A/D converter usage with the IOS instruction with PWn = 7 or 8 in bit units.<br/>Specify the pin to convert with the IOS instruction with PWn = 1.<br/>Start a conversion with the UCC instruction (b2).<br/>The ADCE flag will be set when the conversion competes.<br/>Note: Executing an input instruction for a port specified for ADI usage will always return<br/>low since input is disabled. These pins must be set up for general-purpose input<br/>port usage before an input instruction is executed.</li> <li>Input is disabled in clock stop mode.</li> <li>During the power-on reset, these pins go to the general-purpose input port function.</li> </ul>              |

| 60<br>59<br>58<br>57             | PJ0<br>PJ1<br>PJ2<br>PJ3                                             | 0   | N-channel open drain | General-purpose output ports<br>An external pull-up resistor is required since these pins are open-drain circuits.<br>In clock stop mode, these pins go to the transistor off state (high level output).<br>During the power-on reset, these pins are set up as general-purpose output ports and go<br>to the transistor off state (high level output).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 56<br>55<br>54<br>53             | PK0/INT0<br>PK1/INT1<br>PK2<br>PK3                                   | I/O | CMOS push-pull       | <ul> <li>General-purpose I/O/external interrupt shared-function ports</li> <li>There is no instruction that switches the function of these ports between general-purpose ports and external interrupt ports. These pins function as external interrupt pins at the point that the external interrupt enable flag is set.</li> <li>General-purpose I/O port usage</li> <li>These pins can be set for input or output in bit units (bit I/O).</li> <li>The IOS instruction is used to specify input or output in bit units.</li> <li>External interrupt pin usage</li> <li>This function can be used by setting the external interrupt enable flags (INTOEN and INT1EN) in status register 2. The corresponding pin must be set up for input.</li> <li>To enable interrupt operation, the interrupt enable flag (INTEN) in status register 1 also must be set.</li> <li>The IOS instruction with PWn = 3, b1 = INT1, and b0 = INT0 is used to select rising or falling edge detection.</li> <li>In clock stop mode, input is disabled and these pins go to the high impedance state.</li> <li>During the power-on reset, these pins function as general-purpose input ports.</li> </ul> |

| 52 to<br>45                      | PL0 to PL3<br>PM0 to PM3                                             | I/O | CMOS push-pull       | General-purpose I/O ports<br>The IOS instruction is used to specify input or output.<br>In clock stop mode input is disabled and these pins go to the high impedance state.<br>During the power-on reset, these pins function as general-purpose input ports.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

#### Continued from preceding page.

| Pin No.              | Symbol                        | I/O | I/O type       | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|----------------------|-------------------------------|-----|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 44<br>43<br>42<br>41 | PN0/BEEP<br>PN1<br>PN2<br>PN3 | 0   | CMOS push-pull | <ul> <li>General-purpose output port/BEEP tone shared-function output pins</li> <li>The BEEP instruction switches between the general-purpose output port and BEEP tone functions.</li> <li>General-purpose output port usage</li> <li>The BEEP instruction with b3 = 0 sets up the general-purpose output port function. Pins PN1 to PN3 are general-purpose output-only pins.</li> <li>BEEP output usage</li> <li>The BEEP instruction with b3 = 1 sets up BEEP output.</li> <li>The BEEP instruction bits b0, b1 and b2 sets the frequency.</li> <li>When set up as the BEEP port, executing an output instruction will set the internal latch data but has no influence on the output.</li> <li>These pins go to the output high-impedance state in clock stop mode.</li> <li>These pins go to the output high-impedance state during the power-on reset and hold that state until an output instruction is executed.</li> </ul> |

| 40 to<br>33          | PO0 to PO3<br>PP0 to PP3      | 0   | CMOS push-pull | Output-only ports<br>These pins go to the output high-impedance state in clock stop mode.<br>These pins go to the output high-impedance state during the power-on reset and hold that<br>state until an output instruction is executed.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 32                   | PQ0                           | I/O | CMOS push-pull | General-purpose I/O ports<br>The IOS instruction is used to specify input or output.<br>The OUTR and INR instructions are used for output and input.<br>The bit set, reset and test instruction cannot be used.<br>In clock stop mode input is disabled and these pins go to the high impedance state.<br>During the power-on reset, these pins function as general-purpose input ports.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 79                   | TEST1                         |     |                | LSI test pins                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 2                    | TEST2                         |     |                | These pins must be either left open or connected to ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

#### LC72358N, LC72362N and LC72366 Instruction Table

Abbreviations:

| ADDR: | Program | memory | address |

|-------|---------|--------|---------|

|-------|---------|--------|---------|

- b: Borrow

- C: Carry

- D<sub>H</sub>: Data memory address high (row address): 2 bits

- D<sub>L</sub>: Data memory address low (column address):4 bits

- I: Immediate data:4 bits

- M: Data memory address

- N: Bit position

- Pn: Port number:4 bits

- PWn: Port control word number: 4 bits

- r: General register (one of banks 00 to 0FH)

- Rn: Register number:4 bits

- (): Contents of register or memory

- ()N: Contents of bit N of register or memory

| Instruction<br>Group     |          | Ope | rand    |                                                          |                                             | Machine code |       |                |         |          |  |  |  |  |  |

|--------------------------|----------|-----|---------|----------------------------------------------------------|---------------------------------------------|--------------|-------|----------------|---------|----------|--|--|--|--|--|

| Instruct<br>Group        | Mnemonic | 1st | 1st 2nd | Function                                                 |                                             | D15 14 13 12 | 11 10 | 98             | 7 6 5 4 | 3 2 1 D0 |  |  |  |  |  |

|                          | AD       | r   | М       | Add M to r                                               | $r \leftarrow (r) + (M)$                    | 0 1 0 0      | 0 0   | D <sub>H</sub> | DL      | r        |  |  |  |  |  |

|                          | ADS      | r   | М       | Add M to r,<br>then skip if carry                        | $r \leftarrow (r) + (M)$<br>skip if carry   | 0 1 0 0      | 0 1   | D <sub>H</sub> | DL      | r        |  |  |  |  |  |

| suo                      | AC       | r   | М       | Add M to r with carry                                    | $r \gets (r) + (M) + C$                     | 0 1 0 0      | 1 0   | D <sub>H</sub> | DL      | r        |  |  |  |  |  |

| Addition instructions    | ACS      | r   | М       | Add M to r with carry,<br>then skip if carry             | $r \leftarrow (r) + (M) + C$ skip if carry  | 0 1 0 0      | 1 1   | D <sub>H</sub> | DL      | r        |  |  |  |  |  |

| on ir                    | AI       | М   | Ι       | Add I to M                                               | $M \gets (M) + I$                           | 0 1 0 1      | 0 0   | D <sub>H</sub> | DL      | I        |  |  |  |  |  |

| Additio                  | AIS      | М   | I       | Add I to M,<br>then skip if carry                        | $M \leftarrow (M) + I$<br>skip if carry     | 0 1 0 1      | 0 1   | D <sub>H</sub> | DL      | I        |  |  |  |  |  |

| 1                        | AIC      | М   | Ι       | Add I to M with carry                                    | $M \gets (M) + I + C$                       | 0 1 0 1      | 1 0   | D <sub>H</sub> | DL      | I        |  |  |  |  |  |

|                          | AICS     | М   | Ι       | Add I to M with carry,<br>then skip if carry             | $M \leftarrow (M) + I + C$<br>skip if carry | 0 1 0 1      | 1 1   | D <sub>H</sub> | DL      | I        |  |  |  |  |  |

|                          | SU       | r   | М       | Subtract M from r                                        | $r \gets (r) - (M)$                         | 0 1 1 0      | 0 0   | D <sub>H</sub> | DL      | r        |  |  |  |  |  |

|                          | SUS      | r   | М       | Subtract M from r,<br>then skip if borrow                | $r \leftarrow (r) - (M)$<br>skip if borrow  | 0 1 1 0      | 0 1   | D <sub>H</sub> | DL      | r        |  |  |  |  |  |

| su                       | SB       | r   | М       | Subtract M from r with<br>borrow                         | $r \leftarrow (r) - (M) - b$                | 0 1 1 0      | 1 0   | D <sub>H</sub> | DL      | r        |  |  |  |  |  |

| Subtraction instructions | SBS      | r   | М       | Subtract M from r with<br>borrow,<br>then skip if borrow | $r \leftarrow (r) - (M) - b$ skip if borrow | 0 1 1 0      | 1 1   | D <sub>H</sub> | DL      | r        |  |  |  |  |  |

| tion                     | SI       | М   | I       | Subtract I from M                                        | $M \gets (M) - I$                           | 0 1 1 1      | 0 0   | D <sub>H</sub> | D       | I        |  |  |  |  |  |

| ubtract                  | SIS      | М   | I       | Subtract I from M,<br>then skip if borrow                | $M \leftarrow (M) - I$<br>skip if borrow    | 0 1 1 1      | 0 1   | D <sub>H</sub> | DL      | I        |  |  |  |  |  |

| <i>с</i> о               | SIB      | М   | I       | Subtract I from M with<br>borrow                         | $M \gets (M) - I - b$                       | 0 1 1 1      | 1 0   | D <sub>H</sub> | DL      | I        |  |  |  |  |  |

|                          | SIBS     | М   | I       | Subtract I from M with<br>borrow,<br>then skip if borrow | $M \leftarrow (M) - I - b$ skip if borrow   | 0 1 1 1      | 1 1   | D <sub>H</sub> | DL      | I        |  |  |  |  |  |

|                          | SEQ      | r   | М       | Skip if r equal to M                                     | (r) – M<br>skip if zero                     | 0 0 0 1      | 0 0   | D <sub>H</sub> | DL      | r        |  |  |  |  |  |

| suo                      | SEQI     | М   | Ι       | Skip if M equal to I                                     | (M) – I<br>skip if zero                     | 0 0 0 1      | 0 1   | D <sub>H</sub> | DL      | I        |  |  |  |  |  |

| nstructi                 | SNEI     | М   | I       | Skip if M not equal to I                                 | (M) – I<br>skip if not zero                 | 0 0 0 0      | 0 1   | D <sub>H</sub> | DL      | I        |  |  |  |  |  |

| Comparison instructions  | SGE      | r   | М       | Skip if r is greater<br>than or equal to M               | (r) – M<br>skip if not borrow               | 0 0 0 0      | 1 1   | D <sub>H</sub> | DL      | r        |  |  |  |  |  |

| Сол                      | SGEI     | М   | I       | Skip if M is greater<br>than or equal to I               | (M) – I<br>skip if not borrow               | 0 0 0 1      | 1 1   | D <sub>H</sub> | DL      | I        |  |  |  |  |  |

|                          | SLEI     | М   | I       | Skip if M is less than I                                 | (M) – I<br>skip if zero                     | 0 0 0 0      | 1 1   | D <sub>H</sub> | DL      | I        |  |  |  |  |  |

Continued from preceding page.

| stion                                 |          | Оре | rand |                                                              |                                                        |                    |    |    |    |    | М              | achine         | code             |                  |

|---------------------------------------|----------|-----|------|--------------------------------------------------------------|--------------------------------------------------------|--------------------|----|----|----|----|----------------|----------------|------------------|------------------|

| Instruction<br>Group                  | Mnemonic | 1st | 2nd  | Function                                                     | Operation                                              | D15                | 14 | 13 | 12 | 11 | 10             | 98             | 7 6 5 4          | 3 2 1 D0         |

|                                       | AND      | r   | м    | AND M with r                                                 | $r \leftarrow (r) \text{ AND (M)}$                     | 0                  | 0  | 1  | 0  | 0  | 0              | D <sub>H</sub> | DL               | r                |

| ions                                  | ANDI     | М   | ı    | AND I with M                                                 | M ← (M) AND I                                          | 0                  | 0  | 1  | 0  | 0  | 1              | D <sub>H</sub> | DL               | I                |

| Logical operation instructions        | OR       | r   | м    | OR M with r                                                  | $r \leftarrow (r) \text{ OR } (M)$                     | 0                  | 0  | 1  | 0  | 1  | 0              | D <sub>H</sub> | DL               | r                |

| eration                               | ORI      | м   | I    | OR I with M                                                  | M ← (M) ORI                                            | 0                  | 0  | 1  | 0  | 1  | 1              | D <sub>H</sub> | DL               | I                |

| ical op                               | EXL      | r   | м    | Exclusive OR M with r                                        | $r \leftarrow (r) \text{ XOR } (M)$                    | 0                  | 0  | 1  | 1  | 0  | 0              | D <sub>H</sub> | DL               | r                |

| Log                                   | EXLI     | М   | I    | Exclusive OR I with M                                        | $M \gets (M) \; XOR \; I$                              | 0                  | 0  | 1  | 1  | 0  | 1              | D <sub>H</sub> | DL               | I                |

|                                       | SHR      |     | r    | Shift r right with<br>carry                                  | Carry (r)                                              | 0                  | 0  | 0  | 0  | 0  | 0              | 0 0            | 1 1 1 0          | r                |

|                                       | LD       | r   | м    | Load M to r                                                  | $r \leftarrow (M)$                                     | 1                  | 1  | 0  | 1  | 0  | 0              | D <sub>H</sub> | DL               | r                |

|                                       | ST       | М   | r    | Store r to M                                                 | $M \gets (r)$                                          | 1                  | 1  | 0  | 1  | 0  | 1              | D <sub>H</sub> | DL               | r                |

| structions                            | MVRD     | r   | М    | Move M to destination<br>M referring to r in<br>the same row | $[D_{H},rn] \leftarrow (M)$                            | 1                  | 1  | 0  | 1  | 1  | 0              | D <sub>H</sub> | DL               | r                |

| Transfer instructions                 | MVRS     | М   | r    | Move source M<br>referring to r to M in<br>the same row      | $M \gets [D_H, rn]$                                    | 1                  | 1  | 0  | 1  | 1  | 1              | D <sub>H</sub> | DL               | r                |

| μ                                     | MVSR     | M1  | M2   | Move M to M in the same row                                  | $[D_{H},D_{L}1] \gets [D_{H},D_{L}2]$                  | 1                  | 1  | 1  | 0  | 0  | 0              | D <sub>H</sub> | D <sub>L</sub> 1 | D <sub>L</sub> 2 |

|                                       | MVI      | М   | I    | Move I to M                                                  | $M \gets I$                                            | 1                  | 1  | 1  | 0  | 0  | 1              | D <sub>H</sub> | DL               | I                |

| Bit test<br>instructions              | тмт      | М   | N    | Test M bits, then skip<br>if all bits specified<br>are true  | if M (N) = all 1,<br>then skip                         | 1                  | 1  | 1  | 1  | 0  | 0              | D <sub>H</sub> | DL               | Ν                |

| Bit tes<br>instru                     | TMF      | М   | N    | Test M bits, then skip<br>if all bits specified<br>are false | if M (N) = all 0,<br>then skip                         | 1                  | 1  | 1  | 1  | 0  | 1              | D <sub>H</sub> | DL               | Ν                |

|                                       | JMP      | AD  | DR   | Jump to the address                                          | $PC \leftarrow ADDR$                                   | 1 0 ADDR (14 bits) |    |    |    |    | )              |                |                  |                  |

| uctions                               | CAL      | AD  | DR   | Call subroutine                                              | Stack $\leftarrow$ (PC) + 1                            | 1                  | 1  | 0  | 0  |    | ADDR (12 bits) |                |                  |                  |

| all instr                             | RT       |     |      | Return from subroutine                                       | $PC \leftarrow Stack$                                  | 0                  | 0  | 0  | 0  | 0  | 0              | 0 0            | 1 0 0 0          |                  |

| outine c                              | RTS      |     |      | Return from subroutine<br>and skip                           | $PC \leftarrow Stack + 1$                              | 0                  | 0  | 0  | 0  | 0  | 0              | 0 0            | 1010             |                  |

| ord subro                             | RTB      |     |      | Return from subroutine with bank data                        | $PC \leftarrow Stack$<br>BANK $\leftarrow Stack$       | 1                  | 1  | 1  | 1  | 1  | 1              | 1 1            | 1 1 0 0          |                  |

| Jump and subroutine call instructions | RTBS     |     |      | Return from subroutine with bank data and skip               | $PC \leftarrow Stack + 1$<br>BANK ← Stack              | 1                  | 1  | 1  | 1  | 1  | 1              | 1 1            | 1 1 0 1          |                  |

| -                                     | RTI      |     |      | Return from interrupt                                        | $PC \leftarrow Stack$<br>BANK ← Stack<br>Carry ← Stack | 0                  | 0  | 0  | 0  | 0  | 0              | 0 0            | 1001             |                  |

| tions                                 | SS       | I   | N    | Set status register                                          | (Status reg I) $N \leftarrow 1$                        | 1                  | 1  | 1  | 1  | 1  | 1              | 1 1            | 0001             | N                |

| ır instruc                            | RS       | I   | N    | Reset status register                                        | (Status reg I) $N \leftarrow 0$                        | 1                  | 1  | 1  | 1  | 1  | 1              | 1 1            | 0 0 1 I          | Ν                |

| Status register instructions          | TST      | I   | N    | Test status register true                                    | if (Status reg I) N =<br>all 1, then skip              | 1                  | 1  | 1  | 1  | 1  | 1              | 1 1            | 0 1 1            | N                |

| Statu:                                | TSF      | I   | N    | Test status register false                                   | if (Status reg I) N =<br>all 0, then skip              | 1                  | 1  | 1  | 1  | 1  | 1              | 1 1            | 1 0 I            | Ν                |

Continued from preceding page.

| Instruction<br>Group                       |          | Operand |     |                                                                 |                                                 | Machine code |    |    |    |    |    |                |         |          |  |

|--------------------------------------------|----------|---------|-----|-----------------------------------------------------------------|-------------------------------------------------|--------------|----|----|----|----|----|----------------|---------|----------|--|

|                                            | Mnemonic | 1st     | 2nd | Function                                                        | Operation                                       | D15          | 14 | 13 | 12 | 11 | 10 | 98             | 7 6 5 4 | 3 2 1 D0 |  |

| F/F test<br>instructions                   | TUL      | Ν       |     | Test unlock F/F<br>then skip if it has<br>not been set          | if unlock FF (N) =<br>0, then skip              | 0            | 0  | 0  | 0  | 0  | 0  | 0 0            | 1 1 0 1 | N        |  |

| Internal register<br>transfer instructions | PLL      | м       | r   | Load M to PLL registers                                         | $PLL \ reg \gets PLL \ data$                    | 1            | 1  | 1  | 1  | 1  | 0  | D <sub>H</sub> | DL      | r        |  |

|                                            | INR      | М       | Rn  | Input register/port<br>data to M                                | M ← (Rn reg)                                    | 0            | 0  | 1  | 1  | 1  | 0  | D <sub>H</sub> | DL      | Rn       |  |

|                                            | OUTR     | М       | Rn  | Output contents of M to register/port                           | Rn reg ← (M)                                    | 0            | 0  | 1  | 1  | 1  | 1  | D <sub>H</sub> | DL      | Rn       |  |

| Hardware control<br>instructions           | SIO      | 11      | 12  | Serial I/o control                                              | SIO reg ← I1, I2                                | 0            | 0  | 0  | 0  | 0  | 0  | 0 1            | 11      | 12       |  |

|                                            | UCS      | I       |     | Set I to UCCW1                                                  | UCCW1 ← I                                       | 0            | 0  | 0  | 0  | 0  | 0  | 0 0            | 0 0 0 1 | I        |  |

|                                            | UCC      | I       |     | Set I to UCCW2                                                  | UCCW2 ← I                                       | 0            | 0  | 0  | 0  | 0  | 0  | 0 0            | 0 0 1 0 | I        |  |

|                                            | BEEP     | I       |     | Beep control                                                    | Beep reg ← I                                    | 0            | 0  | 0  | 0  | 0  | 0  | 0 0            | 0 1 1 0 | I        |  |

|                                            | DZC      | I       |     | Data zone control                                               | DZC reg ← I                                     | 0            | 0  | 0  | 0  | 0  | 0  | 0 0            | 1011    | I        |  |

|                                            | TMS      | N       |     | Set timer register                                              | Timer reg ← I                                   | 0            | 0  | 0  | 0  | 0  | 0  | 0 0            | 1 1 0 0 | N        |  |

|                                            | IOS      | PWn     | N   | Set port control word                                           | IOS reg PWn ← N                                 | 1            | 1  | 1  | 1  | 1  | 1  | 1 0            | PWn     | N        |  |

| I/O instructions                           | IN       | М       | Pn  | Input port data to M                                            | $M \leftarrow (Pn)$                             | 1            | 1  | 1  | 0  | 1  | 0  | D <sub>H</sub> | D       | Pn       |  |

|                                            | OUT      | М       | Pn  | Output contents of M to port                                    | $Pn \gets M$                                    | 1            | 1  | 1  | 0  | 1  | 1  | D <sub>H</sub> | D       | Pn       |  |

|                                            | SPB      | Pn      | N   | Set port bits                                                   | (Pn) N ← 1                                      | 0            | 0  | 0  | 0  | 0  | 0  | 1 0            | Pn      | N        |  |

|                                            | RPB      | Pn      | N   | Reset port bits                                                 | (Pn) N ← 0                                      | 0            | 0  | 0  | 0  | 0  | 0  | 1 1            | Pn      | N        |  |

|                                            | ТРТ      | Pn      | N   | Test port bits,<br>then skip if all bits<br>specified are true  | if (Pn) N = all 1,<br>then skip                 | 1            | 1  | 1  | 1  | 1  | 1  | 0 0            | Pn      | N        |  |

|                                            | TPF      | Pn      | N   | Test port bits,<br>then skip if all bits<br>specified are false | if (Pn)) N = all 0,<br>then skip                | 1            | 1  | 1  | 1  | 1  | 1  | 0 1            | Pn      | Ν        |  |

| Bank switching instructions                | BANK     | I       |     | Select bank                                                     | BANK ← I                                        | 0            | 0  | 0  | 0  | 0  | 0  | 0 0            | 0111    | I        |  |

| Other<br>instruc-tions                     | HALT     | I       |     | Halt mode control                                               | HALT reg $\leftarrow$ I, then<br>CPU clock stop | 0            | 0  | 0  | 0  | 0  | 0  | 0 0            | 0 1 0 0 | I        |  |

|                                            | CKSTP    |         |     | Clock stop                                                      | Stop Xtal OSC if<br>HOLD = 0                    | 0            | 0  | 0  | 0  | 0  | 0  | 0 0            | 0 1 0 1 |          |  |