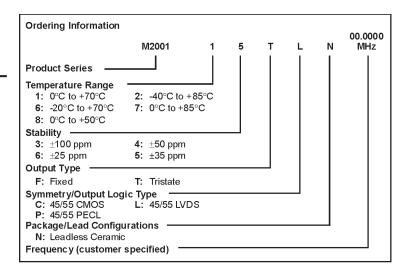

# M2001 Series

## 5x7 mm, 3.3 Volt, CMOS/LVPECL/LVDS, Clock Oscillator

- Low cost oscillator series with jitter performance optimized specifically for Fibre Channel applications. CMOS, LVPECL, and LVDS versions available.

- Ideal for Fibre Channel, Storage Area Networks (SAN), and HDD Control

M2001Sxxx - Contact factory for datasheet

|                |                           |                                                                                       | ·                                      |                            |               |       |                          |  |

|----------------|---------------------------|---------------------------------------------------------------------------------------|----------------------------------------|----------------------------|---------------|-------|--------------------------|--|

|                | PARAMETER                 | Symbol                                                                                | Min.                                   | Тур.                       | Max.          | Units | Condition/Notes          |  |

|                | Frequency Range           | F                                                                                     | 53.125                                 |                            | 125           | MHz   | CMOS                     |  |

|                |                           |                                                                                       | 53.125                                 |                            | 156.25        | MHz   | PECL/LVDS                |  |

|                | Operating Temperature     | TA                                                                                    | (See ordering information)             |                            |               |       |                          |  |

|                | Storage Temperature       | Ts                                                                                    | -55                                    |                            | +125          | °C    |                          |  |

|                | Frequency Stability       | ÄF/F                                                                                  | (See ordering information              |                            |               | n)    | See Note 1               |  |

|                | Aging                     |                                                                                       |                                        |                            |               |       |                          |  |

|                | 1 <sup>st</sup> Year      |                                                                                       |                                        | ±2                         |               | ppm   |                          |  |

|                | Thereafter (per year)     |                                                                                       |                                        | ±1                         |               | ppm   |                          |  |

|                | Input Voltage             | Vcc/Vdd                                                                               | 3.135                                  | 3.3                        | 3.465         | V     |                          |  |

|                | Input Current             | Vdd/ldd                                                                               |                                        |                            | 60            | mA    | CMOS/LVDS                |  |

|                |                           |                                                                                       |                                        |                            | 100           | mA    | PECL                     |  |

|                | Output Type               |                                                                                       |                                        |                            |               |       | CMOS/PECL/LVDS           |  |

|                | Load                      |                                                                                       | 15 pF                                  | <del></del>                |               |       | CMOS (See Note 2)        |  |

| Specifications |                           |                                                                                       | 50 Ohms to                             | Vcc-2 \                    | /DC           |       | PECL (See Note 3)        |  |

|                |                           |                                                                                       | 100 Ohms                               | 100 Ohms differential load |               |       | LVDS (See Note 4)        |  |

| ica            | Symmetry (Duty Cycle)     |                                                                                       | 45                                     | 50                         | 55            | %     | 50% Vdd (CMOS)           |  |

| l i            |                           |                                                                                       | 45                                     | 50                         | 55            | %     | Vcc-1.3 VDC (PECL)       |  |

| Ιğ             |                           |                                                                                       | 45                                     | 50                         | 55            | %     | 1.25 VDC (LVDS)          |  |

| 15             | Output Skew               |                                                                                       |                                        |                            | 200           | ps    | PECL                     |  |

| Electrical     | Differential Voltage      | Vo                                                                                    | 250                                    | 340                        | 450           | mV    | LVDS                     |  |

|                | Logic "1" Level           | Voh                                                                                   | 90% Vdd                                |                            |               | V     | CMOS                     |  |

|                |                           |                                                                                       | Vcc -1.02                              |                            |               | V     | PECL                     |  |

|                |                           |                                                                                       | 1.375                                  |                            |               | V     | LVDS                     |  |

|                | Logic "0" Level           | Vol                                                                                   |                                        |                            | 10% Vdd       | V     | CMOS                     |  |

|                |                           |                                                                                       |                                        |                            | Vcc-1.63      | V     | PECL                     |  |

|                |                           |                                                                                       |                                        |                            | 1.125         |       | LVDS                     |  |

|                | Output Current            |                                                                                       | -4                                     |                            | +4            | mA    | CMOS                     |  |

|                | Rise/Fall Time            | Tr/Tf                                                                                 |                                        |                            | 3             | ns    | CMOS @20/80%             |  |

|                |                           |                                                                                       |                                        | 0.35                       | 0.55          | ns    | LVPECL @ 20/80%          |  |

|                |                           |                                                                                       |                                        | .50                        | 1.0           | ns    | LVDS @ 20/80%            |  |

|                | Tristate Function         |                                                                                       |                                        |                            | ating: output |       |                          |  |

|                |                           |                                                                                       | 20% Vdd max: output disables to high-Z |                            |               |       |                          |  |

|                | Start up Time             |                                                                                       |                                        |                            | 10            | ms    |                          |  |

|                | Peak to Peak Jitter (+/-) | Tj                                                                                    |                                        |                            |               |       | @ BER 1E-12 (See Note 5) |  |

|                |                           |                                                                                       |                                        | 10                         | 15            | ps    | CMOS                     |  |

|                |                           |                                                                                       |                                        | 15                         | 20            | ps    | PECL/LVDS                |  |

| Environmental  | Mechanical Shock          | Per MIL-STD-202, Method 213, Condition C (100 g's, 6 mS duration, ½ sinewave)         |                                        |                            |               |       |                          |  |

|                | Vibration                 | Per MIL-STD-202, Method 201 & 204 (10 g's from 10-2000 Hz)                            |                                        |                            |               |       |                          |  |

|                | Hermeticity               | Per MIL-STD-202, Method 112, (1x10 <sup>-8</sup> atm. cc/s of Helium)                 |                                        |                            |               |       |                          |  |

|                | Thermal Cycle             | Per MIL-STD-883, Method 1010, Condition B (-55°C to +125°C, 15 min. dwell, 10 cycles) |                                        |                            |               |       |                          |  |

|                | Solderability             | Per EIAJ-STD-002                                                                      |                                        |                            |               |       |                          |  |

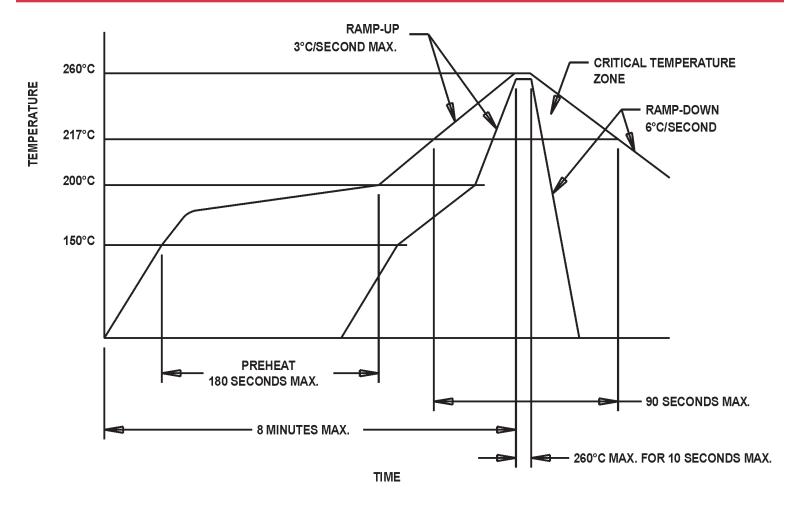

| ш              | Max Soldering Conditions  | See solder profile, Figure 1                                                          |                                        |                            |               |       |                          |  |

- 1. Inclusive of initial tolerance, deviation over temperature, shock, vibration, voltage and aging.

- See Load circuit diagram #2.

See Load circuit diagram #5.

- 4. See Load circuit diagram #9.

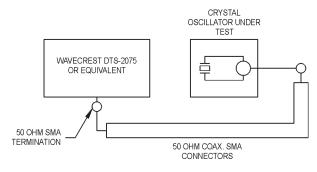

- See jitter test circuit in Figure 1.

MtronPTI reserves the right to make changes to the product(s) and service(s) described herein without notice. No liability is assumed as a result of their use or application.

# M2001 Series

# 5x7 mm, 3.3 Volt, CMOS/LVPECL/LVDS, Clock Oscillator

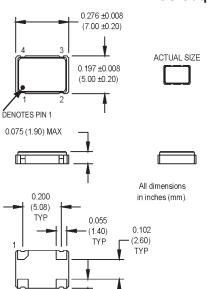

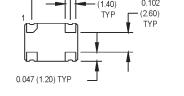

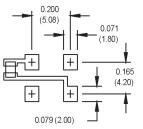

### **CMOS Output**

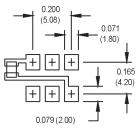

#### SUGGESTED SOLDER PAD LAYOUT

| Pin Connections |             |  |  |  |  |

|-----------------|-------------|--|--|--|--|

| PIN             | FUNCTION    |  |  |  |  |

| 1               | Tristate/NC |  |  |  |  |

| 2               | Gro und     |  |  |  |  |

| 3               | Output      |  |  |  |  |

| 4               | +Vdd        |  |  |  |  |

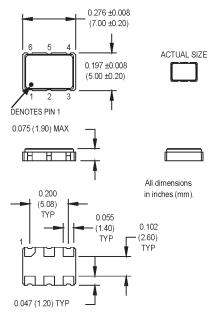

## LVPECL/LVDS Output

#### SUGGESTED SOLDER PAD LAYOUT

#### **Pin Connections**

| I III Oolillections |            |  |  |  |  |

|---------------------|------------|--|--|--|--|

| PIN                 | FUNCTION   |  |  |  |  |

| 1                   | Tristate   |  |  |  |  |

| 2                   | N/C        |  |  |  |  |

| 3                   | Ground     |  |  |  |  |

| 4                   | Output1/ Q |  |  |  |  |

| 5                   | Output2/ Q |  |  |  |  |

| 6                   | +Vdd       |  |  |  |  |

|                     |            |  |  |  |  |

Figure 1

MtronPTI reserves the right to make changes to the product(s) and service(s) described herein without notice. No liability is assumed as a result of their use or application.