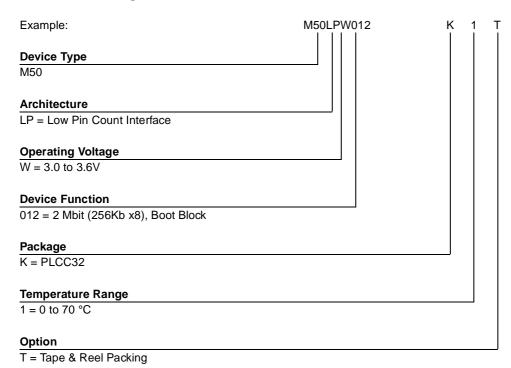

### M50LPW012

### 2 Mbit (256Kb x8, Boot Block) 3V Supply Low Pin Count Flash Memory

PRELIMINARY DATA

#### ■ SUPPLY VOLTAGE

- V<sub>CC</sub> = 3V to 3.6V for Program, Erase and Read Operations

- V<sub>PP</sub> = 12V for Fast Program and Fast Erase

- LOW PIN COUNT (LPC)

- Standard Interface for embedded operation with PC Chipsets that are without automapping memory features

- ADDRESS/ADDRESS MULTIPLEXED (A/A MUX)

- Interface for programming equipment compatibility

- LOW PIN COUNT (LPC) HARDWARE INTERFACE MODE

- 5 Signal Communication Interface supporting Read and Write Operations

- Hardware Write Protect Pins for Block Protection

- Register Based Read and Write Protection

- 5 Additional General Purpose Inputs for platform design flexibility

- Synchronized with 33MHz PCI clock

- BYTE PROGRAMMING TIME

- Single Byte Mode 10µs typical

- Quadruple Byte Mode 2.5µs typical

- 7 MEMORY BLOCKS

- 1 Boot Block

- 4 Main Blocks and 2 Parameter Blocks

- PROGRAM/ERASE CONTROLLER

- Embedded Byte Program and Block/Chip Erase algorithms

- Status Register Bits

- PROGRAM and ERASE SUSPEND

- FOR USE in PC BIOS APPLICATIONS

- ELECTRONIC SIGNATURE

- Manufacturer Code: 20h

- Device Code: 3Bh

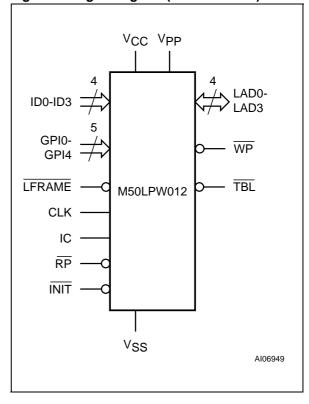

Figure 1. Logic Diagram (LPC Interface)

September 2002 1/35

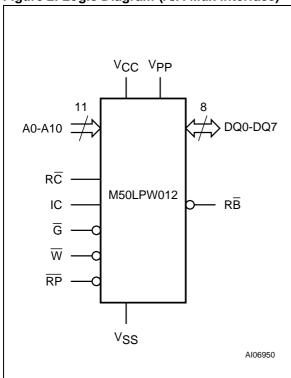

Figure 2. Logic Diagram (A/A Mux Interface)

#### **DESCRIPTION**

The M50LPW012 is a 2Mbit (256Kb x8) non-volatile memory that can be read, erased and reprogrammed. These operations can be performed using a single low voltage (3.0 to 3.6V) supply. For fast programming and fast erasing in production lines an optional 12V power supply can be used to reduce the programming and the erasing times.

The memory is divided into blocks that can be erased independently so it is possible to preserve valid data while old data is erased. Blocks can be protected individually to prevent accidental Program or Erase commands from modifying the memory. Program and Erase commands are written to the Command Interface of the memory. An on-chip Program/Erase Controller simplifies the process of programming or erasing the memory by taking care of all of the special operations that are required to update the memory contents. The end of a program or erase operation can be detected and any error conditions identified. The command set required to control the memory is consistent with JEDEC standards.

Two different bus interfaces are supported by the memory. The primary interface is the Low Pin Count (or LPC) Standard Interface. This has been designed to remove the need for the ISA bus in

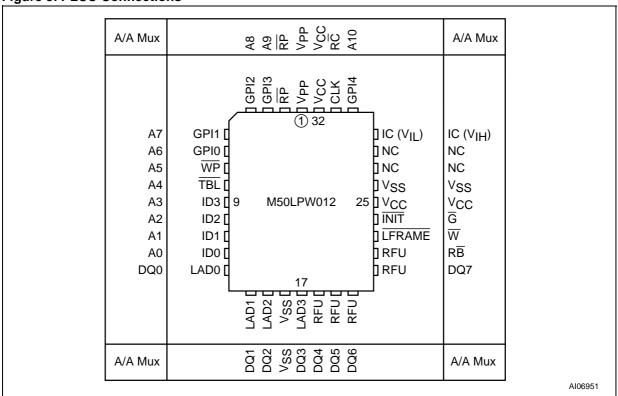

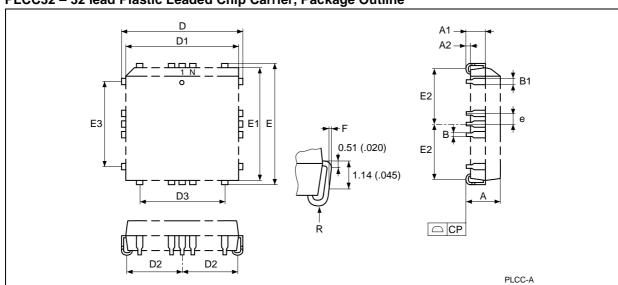

Figure 3. PLCC Connections

Note: Pins 27 and 28 are not internally connected.

current PC Chipsets; the M50LPW012 acts as the PC BIOS on the Low Pin Count bus for these PC Chipsets.

The secondary interface, the Address/Address Multiplexed (or A/A Mux) Interface, is designed to be compatible with current Flash Programmers for production line programming prior to fitting to a PC Motherboard.

The memory is offered in a PLCC32 package and is supplied with all the bits erased (set to 1).

#### **System Memory Mapping**

The LPC address sequence is 32 bits long. The M50LPW012 responds to addresses mapped to the top of the 4 GByte memory space, from FFFF FFFFh. Address bits A31-A24, A22 must be set to 1. A23 is set to 1 for array access, and to 0 for register access.

The M50LPW012 also responds to addresses mapped to the bottom of the 4 GByte memory space, from 0000 0000h. Address bits A31-A24, A22 must be set to 0. A23 is set to 0 for array access, and to 1 for register access.

For A21-A18, see Table 2. A17-A0 are for array addresses.

Table 1. Signal Names (LPC Interface) Memory

| LAD0-LAD3       | Input/Output Communications                                                                |

|-----------------|--------------------------------------------------------------------------------------------|

| LFRAME          | Input Communication Frame                                                                  |

| ID0-ID3         | Identification Inputs                                                                      |

| GPI0-GPI4       | General Purpose Inputs                                                                     |

| IC              | Interface Configuration                                                                    |

| RP              | Interface Reset                                                                            |

| ĪNIT            | CPU Reset                                                                                  |

| CLK             | Clock                                                                                      |

| TBL             | Top Block Lock                                                                             |

| WP              | Write Protect                                                                              |

| RFU             | Reserved for Future Use. Leave disconnected or set at V <sub>IL</sub> or V <sub>IH</sub> . |

| V <sub>CC</sub> | Supply Voltage                                                                             |

| V <sub>PP</sub> | Optional Supply Voltage for Fast<br>Erase Operations                                       |

| V <sub>SS</sub> | Ground                                                                                     |

| NC              | Not Connected Internally                                                                   |

**Table 2. Memory Identification Input Configuration**

| Mamani           |                             |                             |                             |                             |         | To      | р       |         |         | Bot     | tom     |         |

|------------------|-----------------------------|-----------------------------|-----------------------------|-----------------------------|---------|---------|---------|---------|---------|---------|---------|---------|

| Memory<br>Number | ID2                         | ID2                         | ID1                         | ID0                         | A<br>21 | A<br>20 | A<br>19 | A<br>18 | A<br>21 | A<br>20 | A<br>19 | A<br>18 |

| 1 (Boot)         | V <sub>IL</sub> or floating | 1       | 1       | 1       | 1       | 0       | 0       | 1       | 1       |

| 2                | V <sub>IL</sub> or floating | V <sub>IL</sub> or floating | V <sub>IL</sub> or floating | V <sub>IH</sub>             | 1       | 1       | 1       | 0       | 0       | 0       | 1       | 0       |

| 3                | V <sub>IL</sub> or floating | V <sub>IL</sub> or floating | V <sub>IH</sub>             | V <sub>IL</sub> or floating | 1       | 1       | 0       | 1       | 0       | 0       | 0       | 1       |

| 4                | V <sub>IL</sub> or floating | V <sub>IL</sub> or floating | V <sub>IH</sub>             | V <sub>IH</sub>             | 1       | 1       | 0       | 0       | 0       | 0       | 0       | 0       |

| 5                | V <sub>IL</sub> or floating | V <sub>IH</sub>             | V <sub>IL</sub> or floating | V <sub>IL</sub> or floating | 1       | 0       | 1       | 1       | 0       | 1       | 1       | 1       |

| 6                | V <sub>IL</sub> or floating | V <sub>IH</sub>             | V <sub>IL</sub> or floating | V <sub>IH</sub>             | 1       | 0       | 1       | 0       | 0       | 1       | 1       | 0       |

| 7                | V <sub>IL</sub> or floating | V <sub>IH</sub>             | V <sub>IH</sub>             | V <sub>IL</sub> or floating | 1       | 0       | 0       | 1       | 0       | 1       | 0       | 1       |

| 8                | V <sub>IL</sub> or floating | V <sub>IH</sub>             | V <sub>IH</sub>             | V <sub>IH</sub>             | 1       | 0       | 0       | 0       | 0       | 1       | 0       | 0       |

| 9                | V <sub>IH</sub>             | V <sub>IL</sub> or floating | V <sub>IL</sub> or floating | V <sub>IL</sub> or floating | 0       | 1       | 1       | 1       | 1       | 0       | 1       | 1       |

| 10               | V <sub>IH</sub>             | V <sub>IL</sub> or floating | V <sub>IL</sub> or floating | V <sub>IH</sub>             | 0       | 1       | 1       | 0       | 1       | 0       | 1       | 0       |

| 11               | V <sub>IH</sub>             | V <sub>IL</sub> or floating | V <sub>IH</sub>             | V <sub>IL</sub> or floating | 0       | 1       | 0       | 1       | 1       | 0       | 0       | 1       |

| 12               | V <sub>IH</sub>             | V <sub>IL</sub> or floating | V <sub>IH</sub>             | V <sub>IH</sub>             | 0       | 1       | 0       | 0       | 1       | 0       | 0       | 0       |

| 13               | V <sub>IH</sub>             | V <sub>IH</sub>             | V <sub>IL</sub> or floating | V <sub>IL</sub> or floating | 0       | 0       | 1       | 1       | 1       | 1       | 1       | 1       |

| 14               | V <sub>IH</sub>             | V <sub>IH</sub>             | V <sub>IL</sub> or floating | V <sub>IH</sub>             | 0       | 0       | 1       | 0       | 1       | 1       | 1       | 0       |

| 15               | V <sub>IH</sub>             | V <sub>IH</sub>             | V <sub>IH</sub>             | V <sub>IL</sub> or floating | 0       | 0       | 0       | 1       | 1       | 1       | 0       | 1       |

| 16               | V <sub>IH</sub>             | V <sub>IH</sub>             | V <sub>IH</sub>             | V <sub>IH</sub>             | 0       | 0       | 0       | 0       | 1       | 1       | 0       | 0       |

4

Table 3. System Memory Map

|        | A31:24, A22 | A     | 23       |

|--------|-------------|-------|----------|

|        | A31.24, A22 | Array | Register |

| Тор    | FFh, 1b     | 1     | 0        |

| Bottom | 00h, 0b     | 0     | 1        |

#### SIGNAL DESCRIPTIONS

There are two different bus interfaces available on this part. The active interface is selected before power-up or during Reset using the Interface Configuration Pin, IC.

The signals for each interface are discussed in the Low Pin Count (LPC) Signal Descriptions section and the Address/Address Multiplexed (A/A Mux) Signal Descriptions section below. The supply signals are discussed in the Supply Signal Descriptions section below.

#### Low Pin Count (LPC) Signal Descriptions

For the Low Pin Count (LPC) Interface see Figure 1, Logic Diagram, and Table 1, Signal Names.

Input/Output Communications (LAD0-LAD3). All Input and Output Communication with the memory take place on these pins. Addresses and Data for Bus Read and Bus Write operations are encoded on these pins.

Input Communication Frame ( $\overline{\text{LFRAME}}$ ). The Input Communication Frame ( $\overline{\text{LFRAME}}$ ) signals the start of a bus operation. When Input Communication Frame is Low,  $V_{IL}$ , on the rising edge of the Clock a new bus operation is initiated. If Input Communication Frame is Low,  $V_{IL}$ , during a bus operation then the operation is aborted. When Input Communication Frame is High,  $V_{IH}$ , the current bus operation is proceeding or the bus is idle.

Identification Inputs (ID0-ID3). The Identification Inputs (ID0-ID3) allow to address up to 16 memories on a bus. The value on addresses A18-A21 is compared to the hardware strapping on the ID0-ID3 pins to select which memory is being addressed, as shown in Table 2.

General Purpose Inputs (GPI0-GPI4). The General Purpose Inputs can be used as digital inputs for the CPU to read. The General Purpose Input Register holds the values on these pins. The pins must have stable data from before the start of the cycle that reads the General Purpose Input Register until after the cycle is complete. These pins must not be left to float, they should be driven Low,  $V_{\rm IL}$ , or High,  $V_{\rm IH}$ .

Interface Configuration (IC). The Interface Configuration input selects whether the Low Pin Count (LPC) or the Address/Address Multiplexed (A/A Mux) Interface is used. The chosen interface must be selected before power-up or during a Reset

and, thereafter, cannot be changed. The state of the Interface Configuration, IC, should not be changed during operation.

To select the Low Pin Count (LPC) Interface the Interface Configuration pin should be left to float or driven Low,  $V_{IL}$ ; to select the Address/Address Multiplexed (A/A Mux) Interface the pin should be driven High,  $V_{IH}$ . An internal pull-down resistor is included with a value of  $R_{IL}$ ; there will be a leakage current of  $I_{LI2}$  through each pin when pulled to  $V_{IH}$ ; see Table 21.

Interface Reset ( $\overline{RP}$ ). The Interface Reset ( $\overline{RP}$ ) input is used to reset the memory. When Interface Reset ( $\overline{RP}$ ) is set Low, V<sub>IL</sub>, the memory is in Reset mode: the outputs are put to high impedance and the current consumption is minimized. When  $\overline{RP}$  is set High, V<sub>IH</sub>, the memory is in normal operation. After exiting Reset mode, the memory enters Read mode.

**CPU Reset (INIT).** The CPU Reset,  $\overline{\text{INIT}}$ , pin is used to Reset the memory when the CPU is reset. It behaves identically to Interface Reset,  $\overline{\text{RP}}$ , and the internal Reset line is the logical OR (electrical AND) of  $\overline{\text{RP}}$  and  $\overline{\text{INIT}}$ .

**Clock (CLK).** The Clock, CLK, input is used to clock the signals in and out of the Input/Output Communication Pins, LAD0-LAD3. The Clock conforms to the PCI specification.

**Top Block Lock (TBL).** The Top Block Lock input is used to prevent the Top Block (Block 6) from being changed. When Top Block Lock, TBL, is set Low, V<sub>IL</sub>, Program and Block Erase operations in the Top Block have no effect, regardless of the state of the Lock Register. When Top Block Lock, TBL, is set High, V<sub>IH</sub>, the protection of the Block is determined by the Lock Register. The state of Top Block Lock, TBL, does not affect the protection of the Main Blocks (Blocks 0 to 5).

Top Block Lock, TBL, must be set prior to a Program or Block Erase operation is initiated and must not be changed until the operation completes or unpredictable results may occur. Care should be taken to avoid unpredictable behavior by changing TBL during Program or Erase Suspend.

Write Protect (WP). The Write Protect input is used to prevent the Main Blocks (Blocks 0 to 5) from being changed. When Write Protect, WP, is set Low, V<sub>IL</sub>, Program and Block Erase operations in the Main Blocks have no effect, regardless of the state of the Lock Register. When Write Protect, WP, is set High, V<sub>IH</sub>, the protection of the Block is determined by the Lock Register. The state of Write Protect, WP, does not affect the protection of the Top Block (Block 6).

Write Protect, WP, must be set prior to a Program or Block Erase operation is initiated and must not

be changed until the operation completes or unpredictable results may occur. Care should be taken to avoid unpredictable behavior by changing WP during Program or Erase Suspend.

Reserved for Future Use (RFU). These pins do not have assigned functions in this revision of the part. They may be left disconnected or driven Low,  $V_{IL}$ , or High,  $V_{IH}$ .

# Address/Address Multiplexed (A/A Mux) Signal Descriptions

For the Address/Address Multiplexed (A/A Mux) Interface see Figure 2, Logic Diagram, and Table 4, Signal Names.

**Address Inputs (A0-A10).** The Address Inputs are used to set the Row Address bits (A0-A10) and the Column Address bits (A11-A17). They are latched during any bus operation by the Row/Column Address Select input,  $R\overline{C}$ .

Data Inputs/Outputs (DQ0-DQ7). The Data Inputs/Outputs hold the data that is written to or read from the memory. They output the data stored at the selected address during a Bus Read operation. During Bus Write operations they represent the commands sent to the Command Interface of the internal state machine. The Data Inputs/Outputs, DQ0-DQ7, are latched during a Bus Write operation.

Output Enable ( $\overline{G}$ ). The Output Enable,  $\overline{G}$ , controls the Bus Read operation of the memory.

Write Enable ( $\overline{W}$ ). The Write Enable,  $\overline{W}$ , controls the Bus Write operation of the memory's Command Interface.

Row/Column Address Select ( $\overline{RC}$ ). The Row/Column Address Select input selects whether the Address Inputs should be latched into the Row Address bits (A0-A10) or the Column Address bits (A11-A17). The Row Address bits are latched on the falling edge of  $\overline{RC}$  whereas the Column Address bits are latched on the rising edge.

**Ready/Busy Output (RB).** The Ready/Busy pin gives the status of the memory's Program/Erase Controller. When Ready/Busy is Low,  $V_{OL}$ , the memory is busy with a Program or Erase operation and it will not accept any additional Program or Erase command except the Program/Erase Suspend command. When Ready/Busy is High,  $V_{OH}$ , the memory is ready for any Read, Program or Erase operation.

#### **Supply Signal Descriptions**

The Supply Signals are the same for both interfaces.

$V_{CC}$  Supply Voltage. The  $V_{CC}$  Supply Voltage supplies the power for all operations (Read, Program, Erase etc.).

The Command Interface is disabled when the  $V_{CC}$  Supply Voltage is less than the Lockout Voltage,

Table 4. Signal Names (A/A Mux Interface)

| IC              | Interface Configuration                                                  |

|-----------------|--------------------------------------------------------------------------|

| A0-A10          | Address Inputs                                                           |

| DQ0-DQ7         | Data Inputs/Outputs                                                      |

| G               | Output Enable                                                            |

| W               | Write Enable                                                             |

| RC              | Row/Column Address Select                                                |

| RB              | Ready/Busy Output                                                        |

| RP              | Interface Reset                                                          |

| Vcc             | Supply Voltage                                                           |

| V <sub>PP</sub> | Optional Supply Voltage for Fast<br>Program and Fast Erase<br>Operations |

| V <sub>SS</sub> | Ground                                                                   |

| NC              | Not Connected Internally                                                 |

$V_{LKO}$ . This prevents Bus Write operations from accidentally damaging the data during power up, power down and power surges. If the Program/ Erase Controller is programming or erasing during this time then the operation aborts and the memory contents being altered will be invalid. After  $V_{CC}$  becomes valid the Command Interface is reset to Read mode.

A 0.1 $\mu$ F capacitor should be connected between the V<sub>CC</sub> Supply Voltage pins and the V<sub>SS</sub> Ground pin to decouple the current surges from the power supply. Both V<sub>CC</sub> Supply Voltage pins must be connected to the power supply. The PCB track widths must be sufficient to carry the currents required during program and erase operations.

**VPP Optional Supply Voltage.** The VPP Optional Supply Voltage pin is used to select the Fast Program (see the Quadruple Byte Program Command description) and Fast Erase options of the memory. VPP can be left floating. When VPP = VPPH Fast Program (if a Quadruple Byte Program Command is performed) and Fast Erase operations are used.

$V_{\text{PP}}$  should not be set to  $V_{\text{PPH}}$  for more than 80 hours during the life of the memory.

$\textbf{V}_{\textbf{SS}}$  **Ground.**  $\textbf{V}_{\textbf{SS}}$  is the reference for all the voltage measurements.

| Table 5. Absolute Maximum Ratings (1) |

|---------------------------------------|

|---------------------------------------|

| Symbol              | Parameter                     | Value                         | Unit |

|---------------------|-------------------------------|-------------------------------|------|

| T <sub>A</sub>      | Ambient Operating Temperature | 0 to 70                       | °C   |

| T <sub>BIAS</sub>   | Temperature Under Bias        | -50 to 125                    | °C   |

| T <sub>STG</sub>    | Storage Temperature           | -65 to 150                    | °C   |

| V <sub>IO</sub> (2) | Input or Output Voltage       | -0.6 to V <sub>CC</sub> + 0.6 | V    |

| V <sub>CC</sub>     | Supply Voltage                | -0.6 to 4                     | V    |

| V <sub>PP</sub>     | Program Voltage               | -0.6 to 13                    | V    |

Note: 1. Except for the rating "Operating Temperature Range", stresses above those listed in the Table "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only and operation of the device at these or any other conditions above those indicated in the Operating sections of this specification is not implied. Exposure to Absolute Maximum Rating conditions for extended periods may affect device reliability. Refer also to the STMicroelectronics SURE Program and other relevant quality documents.

Minimum Voltage may undershoot to -2V and for less than 20ns during transitions. Maximum Voltage may overshoot to V<sub>CC</sub> +2V

and for less than 20ns during transitions.

#### **BUS OPERATIONS**

The two interfaces have similar bus operations but the signals and timings are completely different. The Low Pin Count (LPC) Interface is the usual interface and all of the functionality of the part is available through this interface. Only a subset of functions are available through the Address/ Address Multiplexed (A/A Mux) Interface.

Follow the section Low Pin Count (LPC) Bus Operations below and the section Address/ Address Multiplexed (A/A Mux) Interface Bus Operations below for a description of the bus operations on each interface.

#### Low Pin Count (LPC) Bus Operations

The Low Pin Count (LPC) Interface consists of four data signals (LAD0-LAD3), one control line (LFRAME) and a clock (CLK). In addition protection against accidental or malicious data corruption can be achieved using two further signals (TBL and WP). Finally two reset signals (RP and INIT) are available to put the memory into a known state.

The data signals, control signal and clock are designed to be compatible with PCI electrical specifications. The interface operates with clock speeds up to 33MHz.

The following operations can be performed using the appropriate bus cycles: Bus Read, Bus Write, Standby, Reset and Block Protection.

**Bus Read.** Bus Read operations read from the memory cells, specific registers in the Command Interface or Low Pin Count Registers. A valid Bus Read operation starts when Input Communication Frame, LFRAME, is Low, V<sub>IL</sub>, as Clock rises and the correct Start cycle is on LAD0-LAD3. On the

following clock cycles the Host will send the Cycle Type + Dir, Address and other control bits on LAD0-LAD3. The memory responds by outputting Sync data until the wait-states have elapsed followed by Data0-Data3 and Data4-Data7.

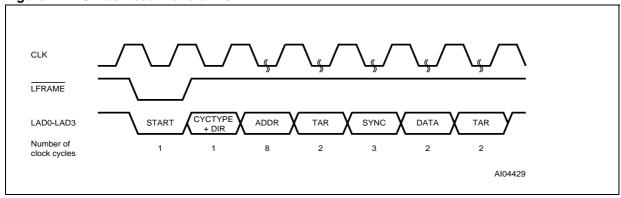

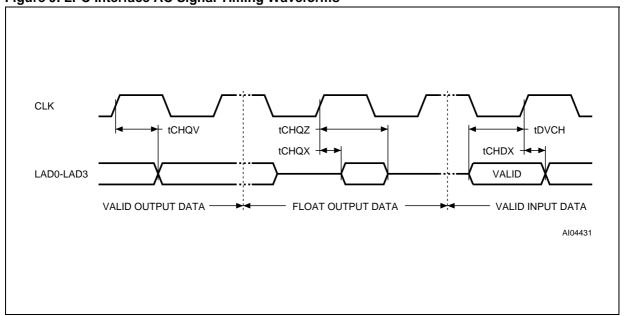

Refer to Table 7, LPC Bus Read Field Definitions, and Figure 4, LPC Bus Read Waveforms, for a description of the Field definitions for each clock cycle of the transfer. See Table 23, LPC Interface AC Signal Timing Characteristics and Figure 9, LPC Interface AC Signal Timing Waveforms, for details on the timings of the signals.

**Bus Write.** Bus Write operations write to the Command Interface or Low Pin Count Registers. A valid Bus Write operation starts when Input Communication Frame,  $\overline{LFRAME}$ , is Low,  $V_{IL}$ , as Clock rises and the correct Start cycle is on LAD0-LAD3. On the following Clock cycles the Host will send the Cycle Type + Dir, Address, other control bits, Data0-Data3 and Data4-Data7 on LAD0-LAD3. The memory outputs Sync data until the wait-states have elapsed.

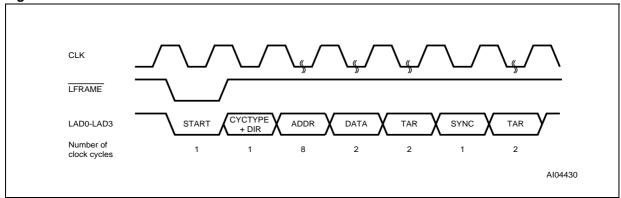

Refer to Table 8, LPC Bus Write Field Definitions, and Figure 5, LPC Bus Write Waveforms, for a description of the Field definitions for each clock cycle of the transfer. See Table 23, LPC Interface AC Signal Timing Characteristics and Figure 9, LPC Interface AC Signal Timing Waveforms, for details on the timings of the signals.

**Bus Abort.** The Bus Abort operation can be used to immediately abort the <u>current bus</u> operation. A Bus Abort occurs when  $\overline{\mathsf{LFRAME}}$  is driven Low,  $\mathsf{V_{IL}}$ , during the bus operation; the memory will tristate the Input/Output Communication pins, LAD0-LAD3.

**Table 6. Block Addresses**

| Size<br>(KBytes) | Address Range | Block<br>Number | Block Type         |

|------------------|---------------|-----------------|--------------------|

| 16               | 3C000h-3FFFFh | 6               | Boot Block         |

| 8                | 3A000h-3BFFFh | 5               | Parameter<br>Block |

| 8                | 38000h-39FFFh | 4               | Parameter<br>Block |

| 32               | 30000h-37FFFh | 3               | Main Block         |

| 64               | 20000h-2FFFFh | 2               | Main Block         |

| 64               | 10000h-1FFFFh | 1               | Main Block         |

| 64               | 00000h-0FFFFh | 0               | Main Block         |

Note: For A19:18 values, refer to Table 2.

Note that, during a Bus Write operation, the Command Interface starts executing the command as soon as the data is fully received; a Bus Abort during the final TAR cycles is not guaranteed to abort the command; the bus, however, will be released immediately.

**Standby.** When  $\overline{\text{LFRAME}}$  is High, V<sub>IH</sub>, the memory is put into Standby mode where LAD0-LAD3 are put into a high-impedance state and the Supply Current is reduced to the Standby level, I<sub>CC1</sub>.

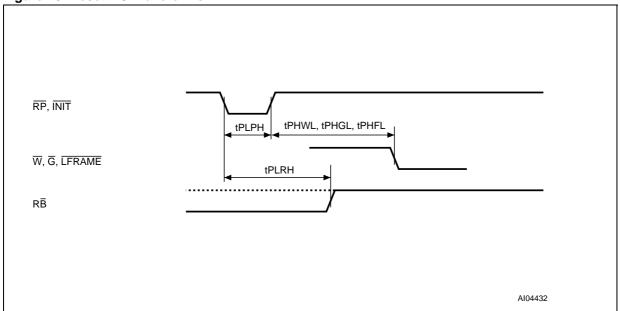

**Reset.** During Reset mode all internal circuits are switched off, the memory is deselected and the outputs are put in high-impedance. The memory is in Reset mode when Interface Reset,  $\overline{RP}$ , or CPU Reset,  $\overline{INIT}$ , is Low,  $V_{IL}$ .  $\overline{RP}$  or  $\overline{INIT}$  must be held Low,  $V_{IL}$ , for  $t_{PLPH}$ . The memory resets to Read mode upon return from Reset mode and the Lock Registers return to their default states regardless of their state before Reset, see Table 16. If  $\overline{RP}$  or  $\overline{INIT}$  goes Low,  $V_{IL}$ , during a Program or Erase operation, the operation is aborted and the memory cells affected no longer contain valid data; the memory can take up to  $t_{PLRH}$  to abort a Program or Erase operation.

**Block Protection.** Block Protection <u>can</u> be forced using the <u>signals Top Block Lock</u>, <u>TBL</u>, and Write Protect, <u>WP</u>, regardless of the state of the Lock Registers.

## Address/Address Multiplexed (A/A Mux) Bus Operations

The Address/Address Multiplexed (A/A Mux) Interface has a more traditional style interface. The signals consist of a multiplexed address signals (A0-A10), data signals, (DQ0-DQ7) and three control signals (RC, G, W). An additional signal, RP, can be used to reset the memory.

The Address/Address Multiplexed (A/A Mux) Interface is included for use by Flash Programming equipment for faster factory programming. Only a subset of the features available to the Low Pin Count (LPC) Interface are available; these include all the Commands but exclude the Security features and other registers.

The following operations can be performed using the appropriate bus cycles: Bus Read, Bus Write, Output Disable and Reset.

When the Address/Address Multiplexed (A/A Mux) Interface is selected all the blocks are unprotected. It is not possible to protect any blocks through this interface.

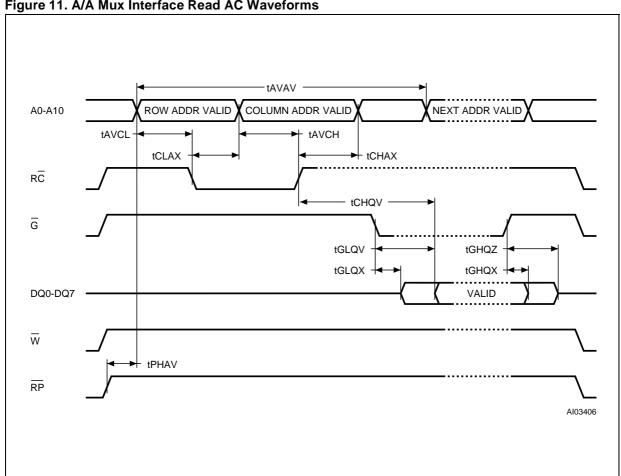

Bus Read. Bus Read operations are used to output the contents of the Memory Array, the Electronic Signature and the Status Register. A valid Bus Read operation begins by latching the Row Address and Column Address signals into the memory using the Address Inputs, A0-A10, and the Row/Column Address Select RC. Then Write Enable (W) and Interface Reset (RP) must be High, V<sub>IH</sub>, and Output Enable, G, Low, V<sub>IL</sub>, in order to perform a Bus Read operation. The Data Inputs/Outputs will output the value, see Figure 11, A/A Mux Interface Read AC Waveforms, and Table 25, A/A Mux Interface Read AC Characteristics, for details of when the output becomes valid

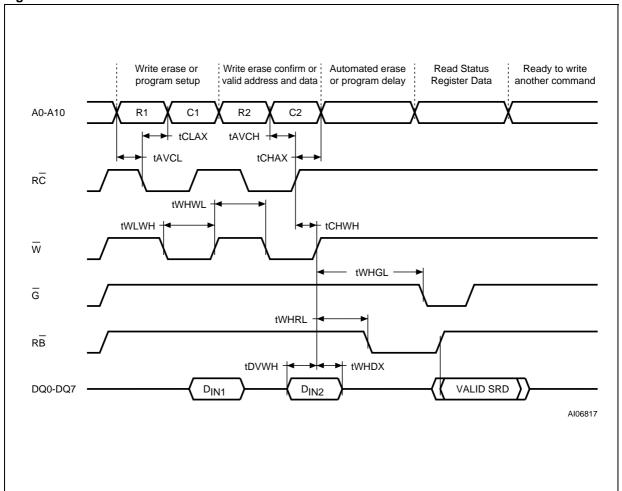

Bus Write. Bus Write operations write to the Command Interface. A valid Bus Write operation begins by latching the Row Address and Column Address signals into the memory using the Address Inputs, A0-A10, and the Row/Column Address Select R $\overline{C}$ . The data should be set up on the Data Inputs/Outputs; Output Enable,  $\overline{G}$ , and Interface Reset,  $\overline{RP}$ , must be High,  $V_{IH}$  and Write Enable,  $\overline{W}$ , must be Low,  $V_{IL}$ . The Data Inputs/Outputs are latched on the rising edge of Write Enable,  $\overline{W}$ . See Figure 12, A/A Mux Interface Write AC Waveforms, and Table 26, A/A Mux Interface Write AC Characteristics, for details of the timing requirements.

Output Disable. The data outputs are high-impedance when the Output Enable,  $\overline{G}$ , is at V<sub>IH</sub>.

**Reset.** During Reset mode all internal circuits are switched off, the memory is deselected and the outputs are put in high-impedance. The memory is in Reset mode when  $\overline{RP}$  is  $\underline{Low}$ ,  $V_{IL}$ .  $\overline{RP}$  must be held Low,  $V_{IL}$  for  $t_{PLPH}$ . If  $\overline{RP}$  is goes Low,  $V_{IL}$ , during a Program or Erase operation, the operation is aborted and the memory cells affected no longer contain valid data; the memory can take up to  $t_{PLRH}$  to abort a Program or Erase operation.

477

**Table 7. LPC Bus Read Field Definitions**

| Clock<br>Cycle<br>Number | Clock<br>Cycle<br>Count | Field                | LAD0-<br>LAD3    | Memory<br>I/O | Description                                                                                                                                                                |

|--------------------------|-------------------------|----------------------|------------------|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1                        | 1                       | START                | 0000b            | I             | On the rising edge of CLK with LFRAME Low, the contents of LAD0-LAD3 must be 0000b to indicate the start of a LPC cycle.                                                   |

| 2                        | 1                       | CYCTY<br>PE +<br>DIR | 0100b            | I             | Indicates the type of cycle. Bits 3:2 must be 01b. Bit 1 indicates the direction of transfer: 0b for read. Bit 0 is '0'.                                                   |

| 3-10                     | 8                       | ADDR                 | XXXX             | ı             | A 32-bit address phase is transferred starting with the most significant nibble first. See Tables 3, 2 and 6 for the field description.                                    |

| 11                       | 1                       | TAR                  | 1111b            | I             | The host drives LAD0-LAD3 to 1111b to indicate a turnaround cycle.                                                                                                         |

| 12                       | 1                       | TAR                  | 1111b<br>(float) | 0             | The LPC Flash Memory takes control of LAD0-LAD3 during this cycle.                                                                                                         |

| 13-14                    | 2                       | WSYNC                | 0101b            | 0             | The LPC Flash Memory drives LAD0-LAD3 to 0101b (short wait-sync) for two clock cycles, indicating that the data is not yet available. Two wait-states are always included. |

| 15                       | 1                       | RSYNC                | 0000b            | 0             | The LPC Flash Memory drives LAD0-LAD3 to 0000b, indicating that data will be available during the next clock cycle.                                                        |

| 16-17                    | 2                       | DATA                 | XXXX             | 0             | Data transfer is two CLK cycles, starting with the least significant nibble.                                                                                               |

| 18                       | 1                       | TAR                  | 1111b            | 0             | The LPC Flash Memory drives LAD0-LAD3 to 1111b to indicate a turnaround cycle.                                                                                             |

| 19                       | 1                       | TAR                  | 1111b<br>(float) | N/A           | The LPC Flash Memory floats its outputs, the host takes control of LAD0-LAD3.                                                                                              |

Figure 4. LPC Bus Read Waveforms

**Table 8. LPC Bus Write Field Definitions**

| Clock<br>Cycle<br>Number | Clock<br>Cycle<br>Count | Field                | LAD0-<br>LAD3    | Memory<br>I/O | Description                                                                                                                             |

|--------------------------|-------------------------|----------------------|------------------|---------------|-----------------------------------------------------------------------------------------------------------------------------------------|

| 1                        | 1                       | START                | 0000b            | I             | On the rising edge of CLK with LFRAME Low, the contents of LAD0-LAD3 must be 0000b to indicate the start of a LPC cycle.                |

| 2                        | 1                       | CYCTY<br>PE +<br>DIR | 011Xb            | I             | Indicates the type of cycle. Bits 3:2 must be 01b. Bit 1 indicates the direction of transfer: 1b for write. Bit 0 is don't care (X).    |

| 3-10                     | 8                       | ADDR                 | XXXX             | I             | A 32-bit address phase is transferred starting with the most significant nibble first. See Tables 3, 2 and 6 for the field description. |

| 11-12                    | 2                       | DATA                 | XXXX             | I             | Data transfer is two cycles, starting with the least significant nibble.                                                                |

| 13                       | 1                       | TAR                  | 1111b            | I             | The host drives LAD0-LAD3 to 1111b to indicate a turnaround cycle.                                                                      |

| 14                       | 1                       | TAR                  | 1111b<br>(float) | 0             | The LPC Flash Memory takes control of LAD0-LAD3 during this cycle.                                                                      |

| 15                       | 1                       | SYNC                 | 0000b            | 0             | The LPC Flash Memory drives LAD0-LAD3 to 0000b, indicating it has received data or a command.                                           |

| 16                       | 1                       | TAR                  | 1111b            | 0             | The LPC Flash Memory drives LAD0-LAD3 to 1111b, indicating a turnaround cycle.                                                          |

| 17                       | 1                       | TAR                  | 1111b<br>(float) | N/A           | The LPC Flash Memory floats its outputs and the host takes control of LAD0-LAD3.                                                        |

Figure 5. LPC Bus Write Waveforms

Table 9. A/A Mux Bus Operations

| Operation      | G                                  | W                                  | RP              | V <sub>PP</sub>                              | DQ7-DQ0     |

|----------------|------------------------------------|------------------------------------|-----------------|----------------------------------------------|-------------|

| Bus Read       | VIL                                | $V_{IH}$                           | V <sub>IH</sub> | Don't Care                                   | Data Output |

| Bus Write      | V <sub>IH</sub>                    | V <sub>IL</sub>                    | V <sub>IH</sub> | Float or V <sub>CC</sub> or V <sub>PPH</sub> | Data Input  |

| Output Disable | V <sub>IH</sub>                    | V <sub>IH</sub>                    | V <sub>IH</sub> | Don't Care                                   | Hi-Z        |

| Reset          | V <sub>IL</sub> or V <sub>IH</sub> | V <sub>IL</sub> or V <sub>IH</sub> | V <sub>IL</sub> | Don't Care                                   | Hi-Z        |

Table 10. Manufacturer and Device Codes

| Operation         | G               | W               | RP              | A18-A1          | A0              | DQ7-DQ0 |

|-------------------|-----------------|-----------------|-----------------|-----------------|-----------------|---------|

| Manufacturer Code | V <sub>IL</sub> | V <sub>IH</sub> | V <sub>IH</sub> | V <sub>IL</sub> | V <sub>IL</sub> | 20h     |

| Device Code       | VIL             | V <sub>IH</sub> | V <sub>IH</sub> | V <sub>IL</sub> | V <sub>IH</sub> | 3Bh     |

#### **COMMAND INTERFACE**

All Bus Write operations to the memory are interpreted by the Command Interface. Commands consist of one or more sequential Bus Write operations.

After power-up or a Reset operation the memory enters Read mode.

The commands are summarized in Table 12, Commands. Refer to Table 12 in conjunction with the text descriptions below.

Read Memory Array Command. The Read Memory Array command returns the memory to its Read mode where it behaves like a ROM or EPROM. One Bus Write cycle is required to issue the Read Memory Array command and return the memory to Read mode. Once the command is issued the memory remains in Read mode until another command is issued. From Read mode Bus Read operations will access the memory array.

While the Program/Erase Controller is executing a Program or Erase operation the memory will not accept the Read Memory Array command until the operation completes.

Read Status Register Command. The Read Status Register command is used to read the Status Register. One Bus Write cycle is required to issue the Read Status Register command. Once the command is issued subsequent Bus Read operations read the Status Register until another command is issued. See the section on the Status Register for details on the definitions of the Status Register bits.

Read Electronic Signature Command. The Read Electronic Signature command is used to read the Manufacturer Code and the Device Code. One Bus Write cycle is required to issue the Read Electronic Signature command. Once the

command is issued subsequent Bus Read operations read the Manufacturer Code or the Device Code until another command is issued.

After the Read Electronic Signature Command is issued the Manufacturer Code and Device Code can be read using Bus Read operations using the addresses in Table 11.

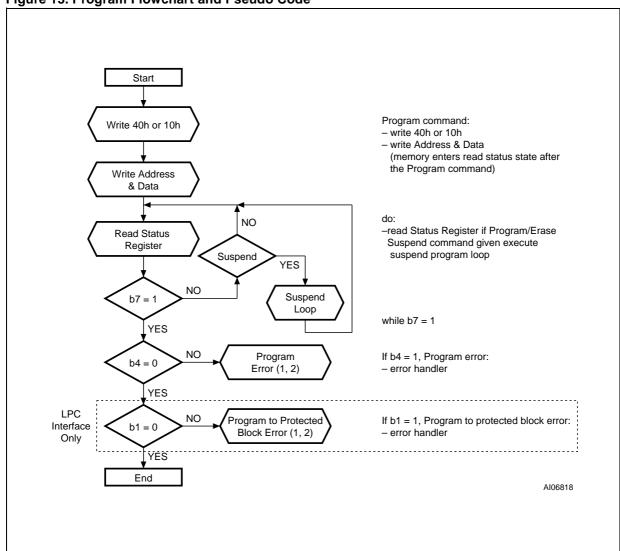

Program Command. The Program command can be used to program a value to one address in the memory array at a time. Two Bus Write operations are required to issue the command; the second Bus Write cycle latches the address and data in the internal state machine and starts the Program/Erase Controller. Once the command is issued subsequent Bus Read operations read the Status Register. See the section on the Status Register for details on the definitions of the Status Register bits.

If the address falls in a protected block then the Program operation will abort, the data in the memory array will not be changed and the Status Register will output the error.

During the Program operation the memory will only accept the Read Status Register command and the Program/Erase Suspend command. All other commands will be ignored. Typical Program times are given in Table 13.

Note that the Program command cannot change a bit set at '0' back to '1' and attempting to do so will not cause any modification on its value. One of the Erase commands must be used to set all of the bits in the block to '1'.

See Figure 13, Program Flowchart and Pseudo Code, for a suggested flowchart on using the Program command.

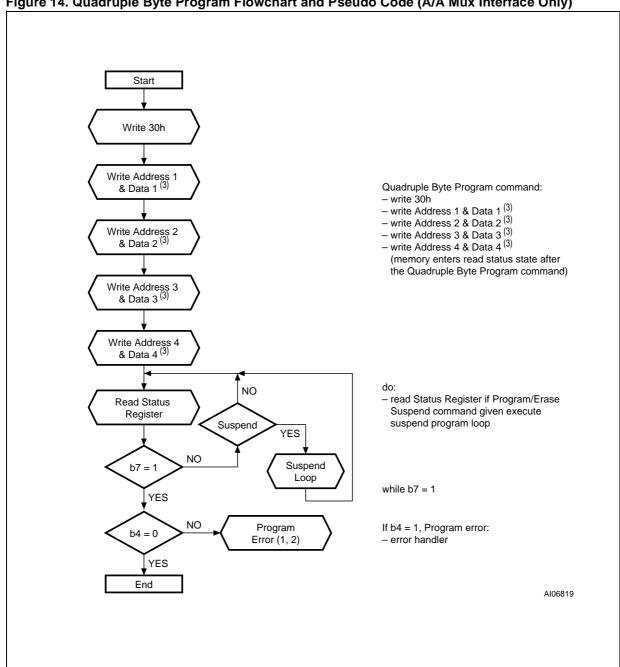

Quadruple Byte Program Command. The Quadruple Byte Program Command can be only used in A/A Mux mode to program four adjacent Bytes in the memory array at a time. The four Bytes must differ only for the addresses A0 and A1. Programming should not be attempted when VPP is not at V<sub>PPH</sub>. The operation can also be executed if V<sub>PP</sub> is below V<sub>PPH</sub>, but result could be uncertain. Five Bus Write operations are required to issue the command. The second, the third and the fourth Bus Write cycle latches respectively the address and data of the first, the second and the third Byte in the internal state machine. The fifth Bus Write cycle latches the address and data of the fourth Byte in the internal state machine and starts the Program/Erase Controller. Once the command is issued subsequent Bus Read operations read the Status Register. See the section on the Status Register for details on the definitions of the Status Register bits.

During the Quadruple Byte Program operation the memory will only accept the Read Status register command and the Program/Erase Suspend command. All other commands will be ignored. Typical Quadruple Byte Program times are given in Table 13

Note that the Quadruple Byte Program command cannot change a bit set to '0' back to '1' and attempting to do so will not cause any modification on its value. One of the Erase commands must be used to set all of the bits in the block to '1'.

See Figure 14, Quadruple Byte Program Flowchart and Pseudo Code, for a suggested flowchart on using the Quadruple Byte Program command.

Chip Erase Command. The Chip Erase Command can be only used in A/A Mux mode to erase the entire chip at a time. Erasing should not be attempted when V<sub>PP</sub> is not at V<sub>PPH</sub>. The operation can also be executed if VPP is below VPPH, but result could be uncertain. Two Bus Write operations are required to issue the command and start the Program/Erase Controller. Once the command is issued subsequent Bus Read operations read the Status Register. See the section on the Status Register for details on the definitions of the Status Register bits. During the Chip Erase operation the memory will only accept the Read Status Register command. All other commands will be ignored. Typical Chip Erase times are given in Table 13. The Chip Erase command sets all of the bits in the memory to '1'. See Figure 16, Chip Erase Flowchart and Pseudo Code, for a suggested flowchart on using the Chip Erase command.

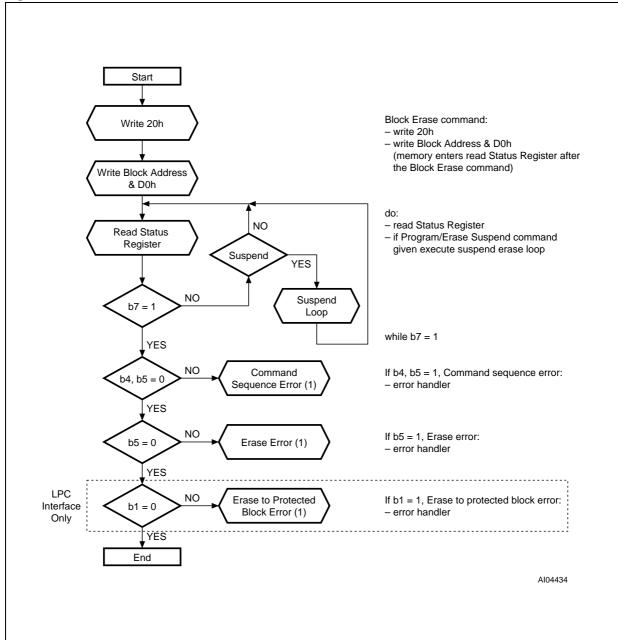

**Block Erase Command.** The Block Erase command can be used to erase a block. Two Bus Write operations are required to issue the command; the second Bus Write cycle latches the block address in the internal state machine and starts the Pro-

Table 11. Read Electronic Signature

| Code              | Address | Data |

|-------------------|---------|------|

| Manufacturer Code | 00000h  | 20h  |

| Device Code       | 00001h  | 3Bh  |

Note: For A19:18 values, see Table 2.

gram/Erase Controller. Once the command is issued subsequent Bus Read operations read the Status Register. See the section on the Status Register for details on the definitions of the Status Register bits.

If the block is protected then the Block Erase operation will abort, the data in the block will not be changed and the Status Register will output the error

During the Block Erase operation the memory will only accept the Read Status Register command and the Program/Erase Suspend command. All other commands will be ignored. Typical Block Erase times are given in Table 13.

The Block Erase command sets all of the bits in the block to '1'. All previous data in the block is lost.

See Figure 17, Block Erase Flowchart and Pseudo Code, for a suggested flowchart on using the Block Erase command.

Clear Status Register Command. The Clear Status Register command can be used to reset bits 1, 3, 4 and 5 in the Status Register to '0'. One Bus Write is required to issue the Clear Status Register command. Once the command is issued the memory returns to its previous mode, subsequent Bus Read operations continue to output the same data.

The bits in the Status Register are sticky and do not automatically return to '0' when a new Program or Erase command is issued. If an error occurs then it is essential to clear any error bits in the Status Register by issuing the Clear Status Register command before attempting a new Program or Erase command.

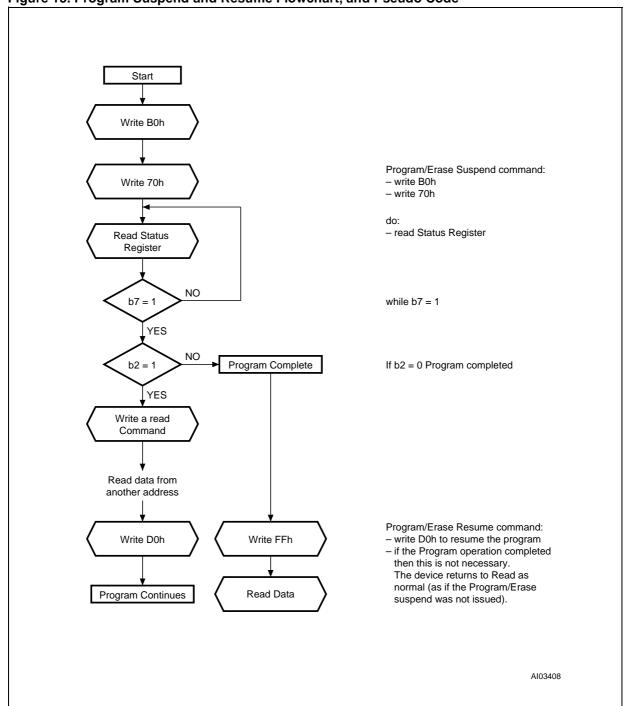

Program/Erase Suspend Command. The Program/Erase Suspend command can be used to pause a Program or Block Erase operation. One Bus Write cycle is required to issue the Program/Erase Suspend command and pause the Program/Erase Controller. Once the command is issued it is necessary to poll the Program/Erase Controller Status bit to find out when the Program/Erase Controller has paused; no other commands will be accepted until the Program/Erase Controller has paused. After the Program/Erase Controller has paused, the memory will continue to output the Status Register until another command is issued.

**Table 12. Commands**

|                           | s      |      | Bus Write Operations |                |      |                |      |                |      |                |      |

|---------------------------|--------|------|----------------------|----------------|------|----------------|------|----------------|------|----------------|------|

| Command                   |        | 1st  |                      | 2nd            |      | 3rd            |      | 4th            |      | 5th            |      |

|                           | Cycles | Addr | Data                 | Addr           | Data | Addr           | Data | Addr           | Data | Addr           | Data |

| Read Memory Array         | 1      | Х    | FFh                  |                |      |                |      |                |      |                |      |

| Read Status Register      | 1      | Х    | 70h                  |                |      |                |      |                |      |                |      |

| Dood Floatronia Cimpatura | 1      | Х    | 90h                  |                |      |                |      |                |      |                |      |

| Read Electronic Signature | 1      | Х    | 98h                  |                |      |                |      |                |      |                |      |

| D                         | 2      | Х    | 40h                  | PA             | PD   |                |      |                |      |                |      |

| Program                   | 2      | Х    | 10h                  | PA             | PD   |                |      |                |      |                |      |

| Quadruple Byte Program    | 5      | Х    | 30h                  | A <sub>1</sub> | PD   | A <sub>2</sub> | PD   | A <sub>3</sub> | PD   | A <sub>4</sub> | PD   |

| Chip Erase                | 2      | Х    | 80h                  | Х              | 10h  |                |      |                |      |                |      |

| Block Erase               | 2      | Х    | 20h                  | ВА             | D0h  |                |      |                |      |                |      |

| Clear Status Register     | 1      | Х    | 50h                  |                |      |                |      |                |      |                |      |

| Program/Erase Suspend     | 1      | Х    | B0h                  |                |      |                |      |                |      |                |      |

| Program/Erase Resume      | 1      | Х    | D0h                  |                |      |                |      |                |      |                |      |

|                           | 1      | Х    | 00h                  |                |      |                |      |                |      |                |      |

|                           | 1      | Х    | 01h                  |                |      |                |      |                |      |                |      |

| Invalid/Reserved          | 1      | Х    | 60h                  |                |      |                |      |                |      |                |      |

|                           | 1      | Х    | 2Fh                  |                |      |                |      |                |      |                |      |

|                           |        | Х    | C0h                  |                |      |                |      |                |      |                |      |

Note: X Don't Care, PA Program Address, PD Program Data, A<sub>1,2,3,4</sub> Consecutive Addresses, BA Any address in the Block.

Read Memory Array. After a Read Memory Array command, read the memory as normal until another command is issued.

Read Status Register. After a Read Status Register command, read the Status Register as normal until another command is issued.

Read Electronic Signature. After a Read Electronic Signature command, read Manufacturer Code, Device Code until another command is issued.

**Block Erase, Program.** After these commands read the Status Register until the command completes and another command is issued.

Quadruple Byte Program. This command is only valid in A/A Mux mode. Addresses  $A_1$ ,  $A_2$ ,  $A_3$  and  $A_4$  must be consecutive addresses differing only for address bit A0 and A1. After this command read the Status Register until the command completes and another command is issued.

Chip Erase. This command is only valid in A/A Mux mode. After this command read the Status Register until the command completes and another command is issued.

Clear Status Register. After the Clear Status Register command bits 1, 3, 4 and 5 in the Status Register are reset to '0'.

**Program/Erase Suspend.** After the Program/Erase Suspend command has been accepted, issue Read Memory Array, Read Status Register, Program (during Erase suspend) and Program/Erase resume commands.

**Program/Erase Resume.** After the Program/Erase Resume command the suspended Program/Erase operation resumes, read the Status Register until the Program/Erase Controller completes and the memory returns to Read Mode.

Invalid/Reserved. Do not use Invalid or Reserved commands.

Table 13. Program and Erase Times

$(T_A = 0 \text{ to } 70^{\circ} \bar{C}; V_{CC} = 3.0 \text{ to } 3.6 \text{V})$

| Parameter                                      | Interface | Test Condition             | Min | Typ <sup>(1)</sup> | Max | Unit |

|------------------------------------------------|-----------|----------------------------|-----|--------------------|-----|------|

| Byte Program                                   |           |                            |     | 10                 | 200 | μs   |

| Quadruple Byte Program                         | A/A Mux   | V <sub>PP</sub> = 12V ± 5% |     | 10 <sup>(4)</sup>  | 200 | μs   |

| Chip Erase                                     | A/A Mux   | V <sub>PP</sub> = 12V ± 5% |     | 3                  |     | sec  |

| Block Program (64 KBytes)                      | A/A Mux   | V <sub>PP</sub> = 12V ± 5% |     | 0.1 <sup>(2)</sup> | 5   | sec  |

| Block Flogram (04 RBytes)                      |           | V <sub>PP</sub> < 12V – 5% |     | 0.4                | 5   | sec  |

| Block Erase (64 KBytes)                        |           | $V_{PP} = 12V \pm 5\%$     |     | 0.75               | 8   | sec  |

| Block Liase (04 KBytes)                        |           | V <sub>PP</sub> < 12V – 5% |     | 1                  | 10  | sec  |

| Program/Erase Suspend to Program pause (3)     |           |                            |     |                    | 5   | μs   |

| Program/Erase Suspend to Block Erase pause (3) |           |                            |     |                    | 30  | μs   |

Note: 1.  $T_A = 25^{\circ}C$ ,  $V_{CC} = 3.3V$

- 2. This time is obtained executing the Quadruple Byte Program Command.

- 3. Sampled only, not 100% tested.

- 4. 10µs to program 4 Bytes.

During the polling period between issuing the Program/Erase Suspend command and the Program/Erase Controller pausing it is possible for the operation to complete. Once Program/Erase Controller Status bit indicates that the Program/Erase Controller is no longer active, the Program Suspend Status bit or the Erase Suspend Status bit can be used to determine if the operation has completed or is suspended. For timing on the delay between issuing the Program/Erase Suspend command and the Program/Erase Controller pausing see Table 13.

During Program/Erase Suspend the Read Memory Array, Read Status Register, Read Electronic Signature and Program/Erase Resume commands will be accepted by the Command Interface. Additionally, if the suspended operation was Block Erase then the Program command will also be accepted; only the blocks not being erased may be read or programmed correctly.

See Figures 15, Program Suspend & Resume Flowchart and Pseudo Code, and 18, Erase Suspend & Resume Flowchart and Pseudo Code, for suggested flowcharts on using the Program/ Erase Suspend command.

**Program/Erase Resume Command.** The Program/Erase Resume command can be used to restart the Program/Erase Controller after a Program/Erase Suspend has paused it. One Bus Write cycle is required to issue the Program/Erase Resume command. Once the command is issued subsequent Bus Read operations read the Status Register.

#### **STATUS REGISTER**

The Status Register provides information on the current or previous Program or Erase operation. Different bits in the Status Register convey different information and errors on the operation.

To read the Status Register the Read Status Register command can be issued. The Status Register is automatically read after Program, Erase and Program/Erase Resume commands are issued. The Status Register can be read from any address.

The Status Register bits are summarized in Table 14, Status Register Bits. Refer to Table 14 in conjunction with the text descriptions below.

Program/Erase Controller Status (Bit 7). The Program/Erase Controller Status bit indicates whether the Program/Erase Controller is active or inactive. When the Program/Erase Controller Status bit is '0', the Program/Erase Controller is active; when the bit is '1', the Program/Erase Controller is inactive.

The Program/Erase Controller Status is '0' immediately after a Program/Erase Suspend command is issued until the Program/Erase Controller pauses. After the Program/Erase Controller pauses the bit is '1'.

During Program and Erase operation the Program/Erase Controller Status bit can be polled to find the end of the operation. The other bits in the Status Register should not be tested until the Program/Erase Controller completes the operation and the bit is '1'.

**Table 14. Status Register Bits**

| Operation                                                        | Bit 7 | Bit 6            | Bit 5 | Bit 4 | Bit 2 | Bit 1 |

|------------------------------------------------------------------|-------|------------------|-------|-------|-------|-------|

| Program active                                                   | 0     | X <sup>(1)</sup> | 0     | 0     | 0     | 0     |

| Program suspended                                                | 1     | X <sup>(1)</sup> | 0     | 0     | 1     | 0     |

| Program completed successfully                                   | 1     | X <sup>(1)</sup> | 0     | 0     | 0     | 0     |

| Program failure due to Block Protection (LPC Interface only)     | 1     | X <sup>(1)</sup> | 0     | 0     | 0     | 1     |

| Program failure due to cell failure                              | 1     | X <sup>(1)</sup> | 0     | 1     | 0     | 0     |

| Erase active                                                     | 0     | 0                | 0     | 0     | 0     | 0     |

| Block Erase suspended                                            | 1     | 1                | 0     | 0     | 0     | 0     |

| Erase completed successfully                                     | 1     | 0                | 0     | 0     | 0     | 0     |

| Block Erase failure due to Block Protection (LPC Interface only) | 1     | 0                | 0     | 0     | 0     | 1     |

| Erase failure due to failed cell(s)                              | 1     | 0                | 1     | 0     | 0     | 0     |

Note: 1. For Program operations during Erase Suspend Bit 6 is '1', otherwise Bit 6 is '0'.

After the Program/Erase Controller completes its operation the Erase Status, Program Status and Block Protection Status bits should be tested for errors.

Erase Suspend Status (Bit 6). The Erase Suspend Status bit indicates that a Block Erase operation has been suspended and is waiting to be resumed. The Erase Suspend Status should only be considered valid when the Program/Erase Controller Status bit is '1' (Program/Erase Controller inactive); after a Program/Erase Suspend command is issued the memory may still complete the operation rather than entering the Suspend mode. When the Erase Suspend Status bit is '0' the Program/Erase Controller is active or has completed its operation; when the bit is '1' a Program/Erase Suspend command has been issued and the memory is waiting for a Program/Erase Resume command.

When a Program/Erase Resume command is issued the Erase Suspend Status bit returns to '0'.

**Erase Status (Bit 5).** The Erase Status bit can be used to identify if the memory has applied the maximum number of erase pulses to the block(s) and still failed to verify that the block(s) has erased correctly. The Erase Status bit should be read once the Program/Erase Controller Status bit is '1' (Program/Erase Controller inactive).

When the Erase Status bit is '0' the memory has successfully verified that the block(s) has erased correctly; when the Erase Status bit is '1' the Program/Erase Controller has applied the maximum number of pulses to the block(s) and still failed to verify that the block(s) has erased correctly. Once the Erase Status bit is set to '1' it can only be reset to '0' by a Clear Status Register command or

a hardware reset. If it is set to '1' it should be reset before a new Program or Erase command is issued, otherwise the new command will appear to fail.

**Program Status (Bit 4).** The Program Status bit can be used to identify if the memory has applied the maximum number of program pulses to the Byte and still failed to verify that the Byte has programmed correctly. The Program Status bit should be read once the Program/Erase Controller Status bit is '1' (Program/Erase Controller inactive).

When the Program Status bit is '0' the memory has successfully verified that the Byte has programmed correctly; when the Program Status bit is '1' the Program/Erase Controller has applied the maximum number of pulses to the Byte and still failed to verify that the Byte has programmed correctly.

Once the Program Status bit is set to '1' it can only be reset to '0' by a Clear Status Register command or a hardware reset. If it is set to '1' it should be reset before a new Program or Erase command is issued, otherwise the new command will appear to fail.

**Reserved (Bit 3).** This status bit is reserved for future use. Its value should be masked out whenever the status register is read.

Program Suspend Status (Bit 2). The Program Suspend Status bit indicates that a Program operation has been suspended and is waiting to be resumed. The Program Suspend Status should only be considered valid when the Program/Erase Controller Status bit is '1' (Program/Erase Controller inactive); after a Program/Erase Suspend command is issued the memory may still complete the operation rather than entering the Suspend mode.

When the Program Suspend Status bit is '0' the Program/Erase Controller is active or has completed its operation; when the bit is '1' a Program/Erase Suspend command has been issued and the memory is waiting for a Program/Erase Resume command.

When a Program/Erase Resume command is issued the Program Suspend Status bit returns to '0'.

Block Protection Status (Bit 1). The Block Protection Status bit can be used to identify if the Program or Block Erase operation has tried to modify the contents of a protected block. When the Block Protection Status bit is to '0' no Program or Block Erase operations have been attempted to protected blocks since the last Clear Status Register command or hardware reset; when the Block Protection Status bit is '1' a Program or Block Erase operation has been attempted on a protected block.

Once it is set to '1' the Block Protection Status bit can only be reset to '0' by a Clear Status Register command or a hardware reset. If it is set to '1' it should be reset before a new Program or Block Erase command is issued, otherwise the new command will appear to fail.

Using the A/A Mux Interface the Block Protection Status bit is always '0'.

**Reserved (Bit 0).** Bit 0 of the Status Register is reserved. Its value should be masked.

# LOW PIN COUNT (LPC) INTERFACE CONFIGURATION REGISTERS

When the Low Pin Count Interface is selected several additional registers can be accessed. These registers control the protection status of the Blocks and read the General Purpose Input pins. See Table 15 for an example of the Register Configuration map, valid for the boot memory, that is, ID0-ID3 can be left floating or driven Low,  $V_{\rm II}$ .

#### **Lock Registers**

The Lock Registers control the protection status of the Blocks. Each Block has its own Lock Register. Three bits within each Lock Register control the protection of each block, the Write Lock Bit, the Read Lock Bit and the Lock Down Bit.

The Lock Registers can be read and written, though care should be taken when writing as, once the Lock Down Bit is set, '1', further modifications to the Lock Register cannot be made until cleared, to '0', by a reset or power-up.

See Table 16 for details on the bit definitions of the Lock Registers.

Write Lock. The Write Lock Bit determines whether the contents of the Block can be modified (using the Program or Block Erase Command).

When the Write Lock Bit is set, '1', the block is write protected; any operations that attempt to change the data in the block will fail and the Status Register will report the error. When the Write Lock Bit is reset, '0', the block is not write protected through the Lock Register and may be modified unless write protected through some other means. If Top Block Lock,  $\overline{TBL}$ , is Low,  $V_{IL}$ , then the Boot

If Top Block Lock, TBL, is Low,  $V_{IL}$ , then the Boot Block (Block 6) is write protected and cannot be modified. Similarly, if Write Protect,  $\overline{WP}$ , is Low,  $V_{IL}$ , then the Main Blocks (Blocks 0 to 5) are write protected and cannot be modified.

After power-up or reset the Write Lock Bit is always set to '1' (write protected).

**Read Lock.** The Read Lock bit determines whether the contents of the Block can be read (from Read mode). When the Read Lock Bit is set, '1', the block is read protected; any operation that attempts to read the contents of the block will read 00h instead. When the Read Lock Bit is reset, '0', read operations in the Block return the data programmed into the block as expected.

After power-up or reset the Read Lock Bit is always reset to '0' (not read protected).

Lock Down. The Lock Down Bit provides a mechanism for protecting software data from simple hacking and malicious attack. When the Lock Down Bit is set, '1', further modification to the Write Lock, Read Lock and Lock Down Bits cannot be performed. A reset or power-up is required before changes to these bits can be made. When the Lock Down Bit is reset, '0', the Write Lock, Read Lock and Lock Down Bits can be changed.

#### **General Purpose Input Register**

The General Purpose Input Register holds the state of the General Purpose Input pins, GPI0-GPI4. When this register is read, the state of these pins is returned. This register is read-only and writing to it has no effect.

The signals on the General Purpose Input pins should remain constant throughout the whole Bus Read cycle in order to guarantee that the correct data is read.

### M50LPW012

Table 15. Low Pin Count Register Configuration Map<sup>(1)</sup>

| Mnemonic     | Register Name                          | Memory    | Address   | Default | Access |

|--------------|----------------------------------------|-----------|-----------|---------|--------|

| Willemonic   | Register Name                          | Тор       | Bottom    | Value   | Access |

| T_BLOCK_LK   | Top Block Lock Register (Block 6)      | FF7FC002h | 008FC002h | 01h     | R/W    |

| T_MINUS01_LK | Top Block [-1] Lock Register (Block 5) | FF7FA002h | 008FA002h | 01h     | R/W    |

| T_MINUS02_LK | Top Block [-2] Lock Register (Block 4) | FF7F8002h | 008F8002h | 01h     | R/W    |

| T_MINUS03_LK | Top Block [-3] Lock Register (Block 3) | FF7F0002h | 008F0002h | 01h     | R/W    |

| T_MINUS04_LK | Top Block [-4] Lock Register (Block 2) | FF7E0002h | 008E0002h | 01h     | R/W    |

| T_MINUS05_LK | Top Block [-5] Lock Register (Block 1) | FF7D0002h | 008D0002h | 01h     | R/W    |

| T_MINUS06_LK | Top Block [-6] Lock Register (Block 0) | FF7C0002h | 008C0002h | 01h     | R/W    |

| GPI_REG      | General Purpose Input Register         | FF7C0100h | 008C0100h | N/A     | R      |

Note: 1. This map is referred to the boot memory (ID0-ID3 floating or driven, Low).

Table 16. Lock Register Bit Definitions<sup>(1)</sup>

| Bit         | Bit Name     | Value                                                                                | Function                                                                                                                                                                                                                                |

|-------------|--------------|--------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7-3         |              |                                                                                      | Reserved                                                                                                                                                                                                                                |

|             |              | '1'                                                                                  | Bus Read operations in this Block always return 00h.                                                                                                                                                                                    |

| 2 Read-Lock | '0'          | Bus read operations in this Block return the Memory Array contents. (Default value). |                                                                                                                                                                                                                                         |

| 1           | 1 Lock-Down  | '1'                                                                                  | Changes to the Read-Lock bit and the Write-Lock bit cannot be performed. Once a '1' is written to the Lock-Down bit it cannot be cleared to '0'; the bit is always reset to '0' following a Reset (using RP or INIT) or after power-up. |

|             |              | '0'                                                                                  | Read-Lock and Write-Lock can be changed by writing new values to them. (Default value).                                                                                                                                                 |

| 0           | Write-Lock   | '1'                                                                                  | Program and Block Erase operations in this Block will set an error in the Status Register. The memory contents will not be changed. (Default value).                                                                                    |

|             | 0 Write-Lock | '0'                                                                                  | Program and Block Erase operations in this Block are executed and will modify the Block contents.                                                                                                                                       |

Note: 1. Applies to Top Block Lock Register (T\_BLOCK\_LK) and Top Block [-1] Lock Register (T\_MINUS01\_LK) to Top Block [-6] Lock Register (T\_MINUS06\_LK).

Table 17. General Purpose Input Register Definition<sup>(1)</sup>

| Bit | Bit Name | Value | Function                             |

|-----|----------|-------|--------------------------------------|

| 7-5 |          |       | Reserved                             |

| 4   | GPI4     | '1'   | Input Pin GPI4 is at V <sub>IH</sub> |

| 4   | GF14     | '0'   | Input Pin GPI4 is at V <sub>IL</sub> |

| 3   | GPI3     | '1'   | Input Pin GPI3 is at V <sub>IH</sub> |

| 3   | 3 GPI3   | '0'   | Input Pin GPI3 is at V <sub>IL</sub> |

| 2   | GPI2     | '1'   | Input Pin GPI2 is at V <sub>IH</sub> |

|     | GF12     | '0'   | Input Pin GPI2 is at V <sub>IL</sub> |

| 1   | GPI1     | '1'   | Input Pin GPI1 is at V <sub>IH</sub> |

| '   | GFII     | '0'   | Input Pin GPI1 is at V <sub>IL</sub> |

| 0   | GPI0     | '1'   | Input Pin GPI0 is at V <sub>IH</sub> |

|     | GFIU     | '0'   | Input Pin GPI0 is at V <sub>IL</sub> |

Note: 1. Applies to the General Purpose Input Register (GPI\_REG).

**A7/**

### M50LPW012

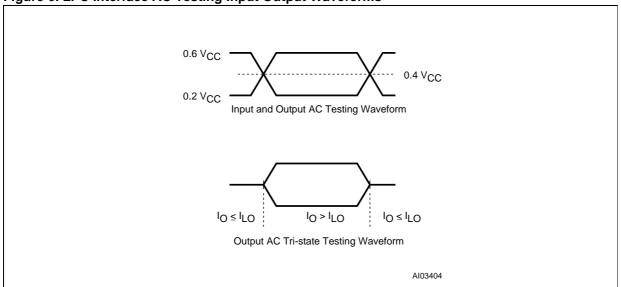

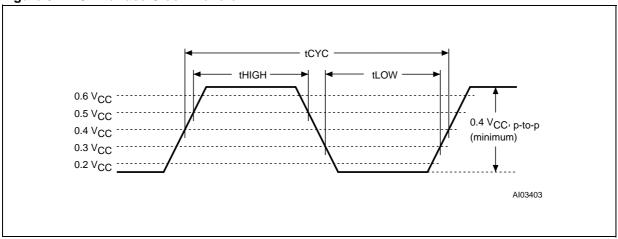

**Table 18. LPC Interface AC Measurement Conditions**

| Parameter                             | Value                                       | Unit |

|---------------------------------------|---------------------------------------------|------|

| V <sub>CC</sub> Supply Voltage        | 3.0 to 3.6                                  | V    |

| Load Capacitance (C <sub>L</sub> )    | 10                                          | pF   |

| Input Rise and Fall Times             | ≤ 1.4                                       | ns   |

| Input Pulse Voltages                  | 0.2 V <sub>CC</sub> and 0.6 V <sub>CC</sub> | V    |

| Input and Output Timing Ref. Voltages | 0.4 V <sub>CC</sub>                         | V    |

Figure 6. LPC Interface AC Testing Input Output Waveforms

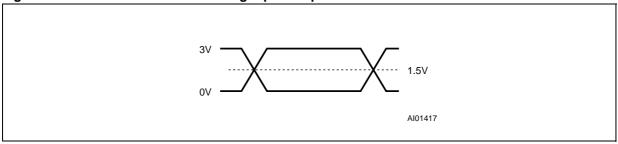

Table 19. A/A Mux Interface AC Measurement Conditions

| Parameter                             | Value      | Unit |

|---------------------------------------|------------|------|

| V <sub>CC</sub> Supply Voltage        | 3.0 to 3.6 | V    |

| Load Capacitance (C <sub>L</sub> )    | 30         | pF   |

| Input Rise and Fall Times             | ≤ 10       | ns   |

| Input Pulse Voltages                  | 0 to 3     | V    |

| Input and Output Timing Ref. Voltages | 1.5        | V    |

Figure 7. A/A Mux Interface AC Testing Input Output Waveform

Table 20. Impedance  $(T_A = 25 \text{ °C}, f = 1 \text{ MHz})$

| Symbol                          | Parameter                  | Test Condition       | Min | Max | Unit |

|---------------------------------|----------------------------|----------------------|-----|-----|------|

| C <sub>IN</sub> <sup>(1)</sup>  | Input Capacitance          | $V_{IN} = 0V$        |     | 13  | pF   |

| C <sub>CLK</sub> <sup>(1)</sup> | Clock Capacitance          | V <sub>IN</sub> = 0V | 3   | 12  | pF   |

| L <sub>PIN</sub> <sup>(2)</sup> | Recommended Pin Inductance |                      |     | 20  | nH   |

Note: 1. Sampled only, not 100% tested. 2. See PCI Specification.

**Table 21. DC Characteristics**

$(T_A = 0 \text{ to } 70^{\circ}\text{C}; V_{CC} = 3.0 \text{ to } 3.6\text{V})$

| Symbol                          | Parameter                                            | Interface | Test Condition                                                                                                                                                        | Min                   | Max                   | Unit |

|---------------------------------|------------------------------------------------------|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|-----------------------|------|

| V                               |                                                      | LPC       |                                                                                                                                                                       | 0.5 V <sub>CC</sub>   | V <sub>CC</sub> + 0.5 | V    |

| $V_{IH}$                        | Input High Voltage                                   | A/A Mux   |                                                                                                                                                                       | 0.7 V <sub>CC</sub>   | V <sub>CC</sub> + 0.3 | V    |

| V <sub>IL</sub>                 | Innut Lour Voltogo                                   | LPC       |                                                                                                                                                                       | -0.5                  | 0.3 V <sub>CC</sub>   | V    |

| V IL                            | Input Low Voltage                                    | A/A Mux   |                                                                                                                                                                       | -0.5                  | 0.8                   | V    |

| $V_{IH}(\overline{INIT})$       | INIT Input High Voltage                              | LPC       |                                                                                                                                                                       | 1.35                  | V <sub>CC</sub> + 0.5 | V    |

| $V_{IL}(\overline{INIT})$       | INIT Input Low Voltage                               | LPC       |                                                                                                                                                                       | -0.5                  | 0.2 V <sub>CC</sub>   | V    |

| I <sub>LI</sub> <sup>(2)</sup>  | Input Leakage Current                                |           | $0V \le V_{IN} \le V_{CC}$                                                                                                                                            |                       | ±10                   | μΑ   |

| I <sub>LI2</sub>                | IC, IDx Input Leakage<br>Current                     |           | IC, ID0, ID1, ID2, ID3 = V <sub>CC</sub>                                                                                                                              |                       | 200                   | μA   |

| $R_{IL}$                        | IC, IDx Input Pull Low<br>Resistor                   |           |                                                                                                                                                                       | 20                    | 100                   | kΩ   |

| Voн                             | Output High Voltage                                  | LPC       | I <sub>OH</sub> = -500μA                                                                                                                                              | 0.9 V <sub>CC</sub>   |                       | V    |

| νОН                             | Output High voltage                                  | A/A Mux   | I <sub>OH</sub> = -100μA                                                                                                                                              | V <sub>CC</sub> - 0.4 |                       | V    |

| V <sub>OL</sub>                 | Output Low Voltage                                   | LPC       | I <sub>OL</sub> = 1.5mA                                                                                                                                               |                       | 0.1 V <sub>CC</sub>   | V    |