COM'L: -7/10/12/15/20, Q-12/15/20 IND: -12/14/18/24

## MACH210A-7/10/12 MACH210-12/15/20 MACH210AQ-12/15/20

### **Lattice Semiconductor**

### **High-Density EE CMOS Programmable Logic**

### DISTINCTIVE CHARACTERISTICS

- 44 Pins

- 64 Macrocells

- 7.5 ns t<sub>PD</sub> Commercial

12 ns t<sub>PD</sub> Industrial

- 133 MHz fcnt

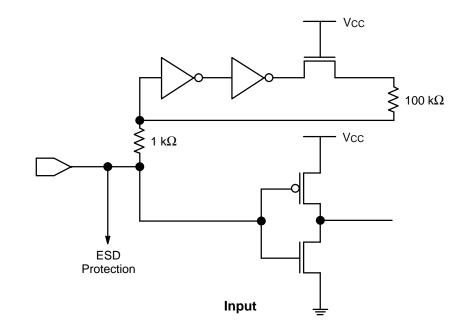

- 38 Inputs; 210A Inputs have built-in pull-up resistors

- Peripheral Component Interconnect (PCI) compliant

- 32 Outputs

- 64 Flip-flops; 2 clock choices

- 4 "PAL22V16" blocks with buried macrocells

- Pin-compatible with MACH110, MACH111, MACH211, and MACH215

#### **GENERAL DESCRIPTION**

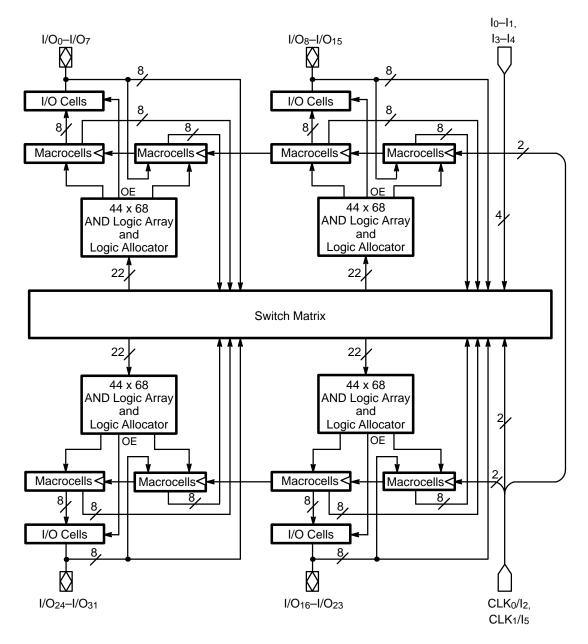

The MACH210 is a member of the high-performance EE CMOS MACH 2 device family. This device has approximately six times the logic macrocell capability of the popular PAL22V10 without loss of speed.

The MACH210 consists of four PAL blocks interconnected by a programmable switch matrix. The four PAL blocks are essentially "PAL22V16" structures complete with product-term arrays and programmable macrocells, including additional buried macrocells. The switch matrix connects the PAL blocks to each other and to all input pins, providing a high degree of connectivity between the fully-connected PAL blocks. This allows designs to be placed and routed efficiently.

The MACH210 has two kinds of macrocell: output and buried. The MACH210 output macrocell provides regis-

tered, latched, or combinatorial outputs with programmable polarity. If a registered configuration is chosen, the register can be configured as D-type or T-type to help reduce the number of product terms. The register type decision can be made by the designer or by the software. All output macrocells can be connected to an I/O cell. If a buried macrocell is desired, the internal feedback path from the macrocell can be used, which frees up the I/O pin for use as an input.

The MACH210 has dedicated buried macrocells which, in addition to the capabilities of the output macrocell, also provide input registers or latches for use in synchronizing signals and reducing setup time requirements.

Publication# 14128 Rev. I Amendment/0 Issue Date: May 1995

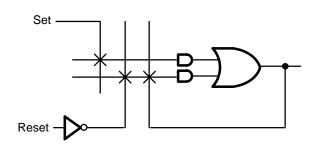

### **BLOCK DIAGRAM**

141281-1

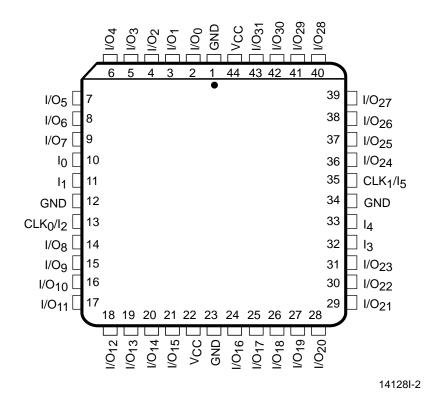

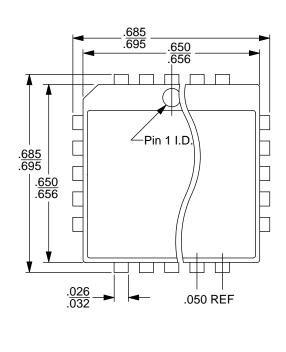

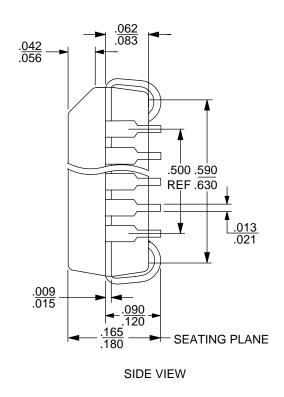

# **CONNECTION DIAGRAM Top View**

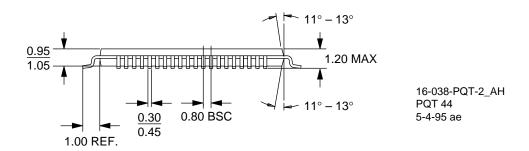

**PLCC**

Note: Pin-compatible with MACH110, MACH111, MACH211, and MACH215.

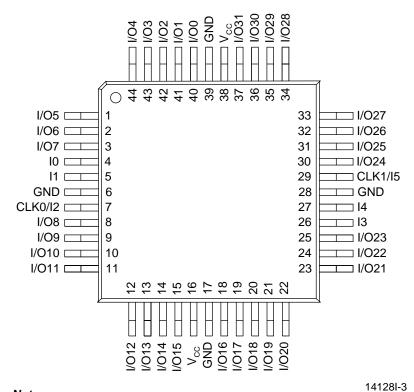

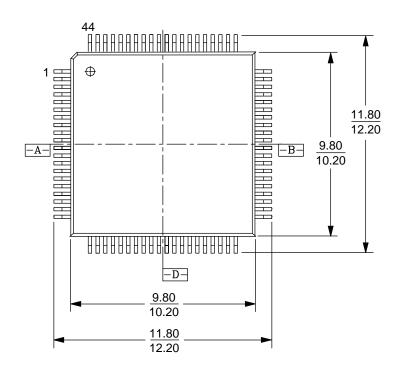

# CONNECTION DIAGRAM Top View

### **TQFP**

Note: Pin-compatible with MACH111 and MACH211.

### **PIN DESIGNATIONS**

CLK/I = Clock or Input

GND = Ground I = Input

I/O = Input/Output Vcc = Supply Voltage

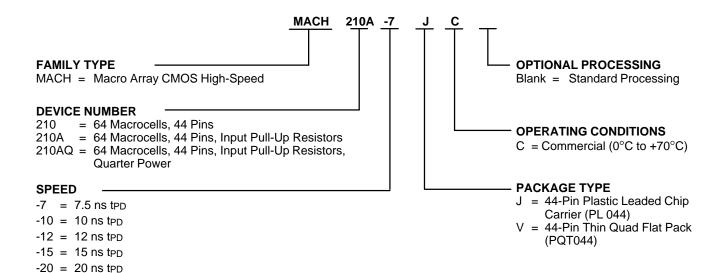

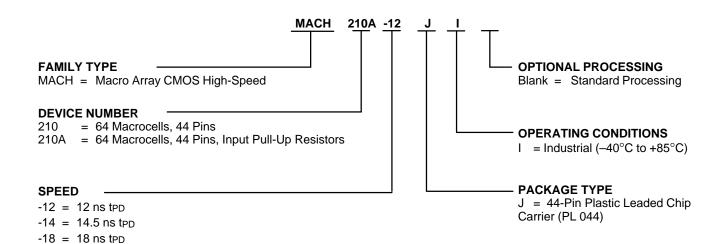

# ORDERING INFORMATION Commercial Products

Programmable logic products for commercial applications are available with several ordering options. The order number (Valid Combination) is formed by a combination of:

| Valid Combinations |           |  |  |  |

|--------------------|-----------|--|--|--|

| MACH210A-7         | 2         |  |  |  |

| MACH210A-10        | JC,<br>VC |  |  |  |

| MACH210A-12        | , 0       |  |  |  |

| MACH210-12         |           |  |  |  |

| MACH210-15         |           |  |  |  |

| MACH210-20         | JC        |  |  |  |

| MACH210AQ-12       | 30        |  |  |  |

| MACH210AQ-15       |           |  |  |  |

| MACH210AQ-20       |           |  |  |  |

#### **Valid Combinations**

The Valid Combinations table lists configurations planned to be supported in volume for this device. Consult your local sales office to confirm availability of specific valid combinations or to check on newly released combinations.

# ORDERING INFORMATION Industrial Products

Programmable logic products for industrial applications are available with several ordering options. The order number (Valid Combination) is formed by a combination of:

| Valid Combinations |    |  |  |  |

|--------------------|----|--|--|--|

| MACH210A-12        |    |  |  |  |

| MACH210A-14        |    |  |  |  |

| MACH210-14         | JI |  |  |  |

| MACH210-18         |    |  |  |  |

| MACH210-24         |    |  |  |  |

-24 = 24 ns tpd

#### **Valid Combinations**

The Valid Combinations table lists configurations planned to be supported in volume for this device. Consult your local sales office to confirm availability of specific valid combinations or to check on newly released combinations.

### **FUNCTIONAL DESCRIPTION**

The MACH210 consists of four PAL blocks connected by a switch matrix. There are 32 I/O pins and 4 dedicated input pins feeding the switch matrix. These signals are distributed to the four PAL blocks for efficient design implementation. There are two clock pins that can also be used as dedicated inputs.

The MACH210A inputs and I/O pins have built-in pull-up resistors. While it is always a good design practice to tie unused pins high, the 210A pull-up resistors provide design security and stability in the event that unused pins are left disconnected.

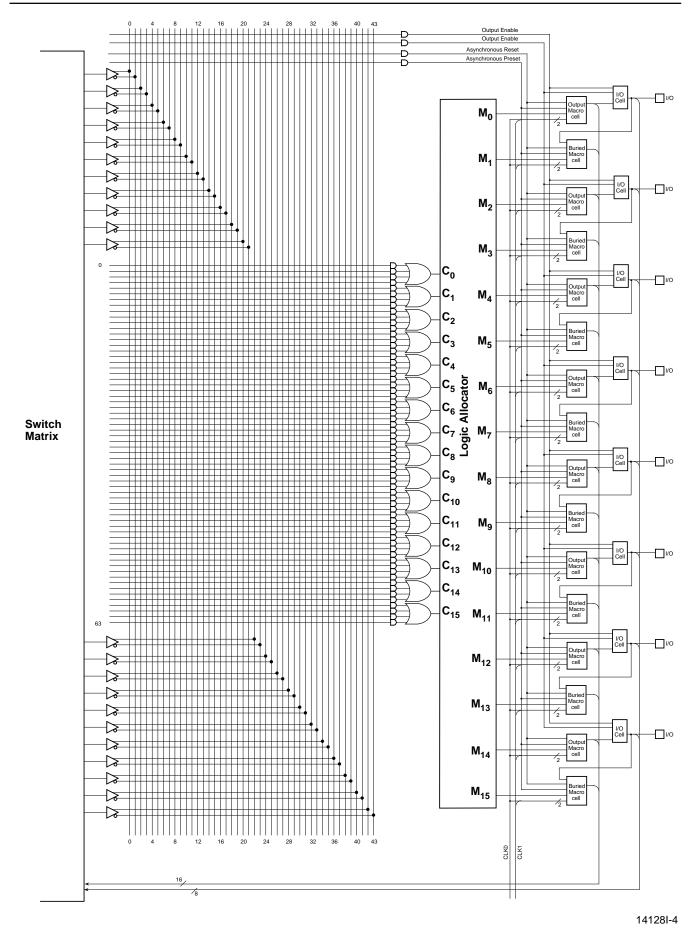

### The PAL Blocks

Each PAL block in the MACH210 (Figure 1) contains a 64-product-term logic array, a logic allocator, 8 output macrocells, 8 buried macrocells, and 8 I/O cells. The switch matrix feeds each PAL block with 22 inputs. This makes the PAL block look effectively like an independent "PAL22V16" with 8 buried macrocells.

In addition to the logic product terms, two output enable product terms, an asynchronous reset product term, and an asynchronous preset product term are provided. One of the two output enable product terms can be chosen within each I/O cell in the PAL block. All flip-flops within the PAL block are initialized together.

### The Switch Matrix

The MACH210 switch matrix is fed by the inputs and feedback signals from the PAL blocks. Each PAL block provides 16 internal feedback signals and 8 I/O feedback signals. The switch matrix distributes these signals back to the PAL blocks in an efficient manner that also provides for high performance. The design software automatically configures the switch matrix when fitting a design into the device.

### The Product-term Array

The MACH210 product-term array consists of 64 product terms for logic use, and 4 special-purpose product terms. Two of the special-purpose product terms provide programmable output enable; one provides asynchronous reset, and one provides asynchronous preset.

### The Logic Allocator

The logic allocator in the MACH210 takes the 64 logic product terms and allocates them to the 16 macrocells as needed. Each macrocell can be driven by up to 16 product terms. The design software automatically configures the logic allocator when fitting the design into the device.

Table 1 illustrates which product term clusters are available to each macrocell within a PAL block. Refer to Figure 1 for cluster and macrocell numbers.

**Table 1. Logic Allocation**

| Mac             | rocell          | Available                                                                                                                                     |

|-----------------|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| Output          | Buried          | Clusters                                                                                                                                      |

| M <sub>0</sub>  | M <sub>1</sub>  | C <sub>0</sub> , C <sub>1</sub> , C <sub>2</sub><br>C <sub>0</sub> , C <sub>1</sub> , C <sub>2</sub> , C <sub>3</sub>                         |

| M <sub>2</sub>  | Мз              | C <sub>1</sub> , C <sub>2</sub> , C <sub>3</sub> , C <sub>4</sub><br>C <sub>2</sub> , C <sub>3</sub> , C <sub>4</sub> , C <sub>5</sub>        |

| M4              | M <sub>5</sub>  | C <sub>3</sub> , C <sub>4</sub> , C <sub>5</sub> , C <sub>6</sub><br>C <sub>4</sub> , C <sub>5</sub> , C <sub>6</sub> , C <sub>7</sub>        |

| M <sub>6</sub>  | M <sub>7</sub>  | C <sub>5</sub> , C <sub>6</sub> , C <sub>7</sub> , C <sub>8</sub><br>C <sub>6</sub> , C <sub>7</sub> , C <sub>8</sub> , C <sub>9</sub>        |

| M <sub>8</sub>  | M <sub>9</sub>  | C <sub>7</sub> , C <sub>8</sub> , C <sub>9</sub> , C <sub>10</sub><br>C <sub>8</sub> , C <sub>9</sub> , C <sub>10</sub> , C <sub>11</sub>     |

| <b>M</b> 10     | M <sub>11</sub> | C <sub>9</sub> , C <sub>10</sub> , C <sub>11</sub> , C <sub>12</sub><br>C <sub>10</sub> , C <sub>11</sub> , C <sub>12</sub> , C <sub>13</sub> |

| M <sub>12</sub> | M <sub>13</sub> | C11, C12, C13, C14<br>C12, C13, C14, C15                                                                                                      |

| M <sub>14</sub> | M <sub>15</sub> | C <sub>13</sub> , C <sub>14</sub> , C <sub>15</sub><br>C <sub>14</sub> , C <sub>15</sub>                                                      |

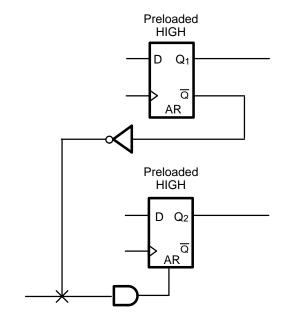

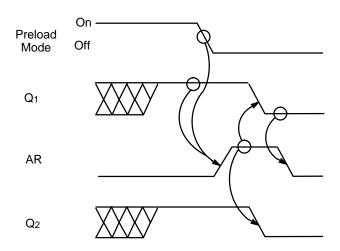

### The Macrocell

The MACH210 has two types of macrocell: output and buried. The output macrocells can be configured as either registered, latched, or combinatorial, with programmable polarity. The macrocell provides internal feedback whether configured with or without the flipflop. The registers can be configured as D-type or T-type, allowing for product-term optimization.

The flip-flops can individually select one of two clock/ gate pins, which are also available as data inputs. The registers are clocked on the LOW-to-HIGH transition of the clock signal. The latch holds its data when the gate input is HIGH, and is transparent when the gate input is LOW. The flip-flops can also be asynchronously initialized with the common asynchronous reset and preset product terms.

The buried macrocells are the same as the output macrocells if they are used for generating logic. In that case, the only thing that distinguishes them from the output macrocells is the fact that there is no I/O cell connection, and the signal is only used internally. The buried macrocell can also be configured as an input register or latch.

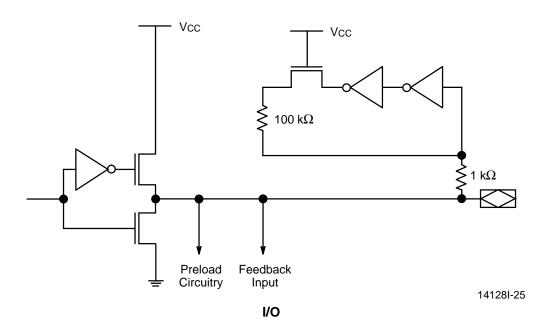

### The I/O Cell

The I/O cell in the MACH210 consists of a three-state output buffer. The three-state buffer can be configured in one of three ways: always enabled, always disabled, or controlled by a product term. If product term control is chosen, one of two product terms may be used to provide the control. The two product terms that are available are common to all I/O cells in a PAL block.

These choices make it possible to use the macrocell as an output, an input, a bidirectional pin, or a three-state output for use in driving a bus.

### **PCI Compliance**

The MACH210A-7/10 is fully compliant with the *PCI Local Bus Specification* published by the PCI Special Interest Group. The MACH210A-7/10's predictable timing ensures compliance with the PCI AC specifications independent of the design. On the other hand, in CPLD and FPGA architectures without predictable timing, PCI compliance is dependent upon routing and product term distribution.

Figure 1. MACH210 PAL Block

### **ABSOLUTE MAXIMUM RATINGS**

| Storage Temperature $\ \dots \ -65^{\circ}C$ to $+150^{\circ}C$    |

|--------------------------------------------------------------------|

| Ambient Temperature with Power Applied –55°C to +125°C             |

| Supply Voltage with Respect to Ground0.5 V to +7.0 V               |

| DC Input Voltage $-0.5$ V to Vcc + $0.5$ V                         |

| DC Output or                                                       |

| I/O Pin Voltage $\dots -0.5 \text{ V}$ to $V_{CC}$ + 0.5 V         |

| Static Discharge Voltage 2001 V                                    |

| Latchup Current                                                    |

| $(T_A = 0^{\circ}C \text{ to } +70^{\circ}C) \dots 200 \text{ mA}$ |

Stresses above those listed under Absolute Maximum Ratings may cause permanent device failure. Functionality at or above these limits is not implied. Exposure to Absolute Maximum Ratings for extended periods may affect device reliability. Programming conditions may differ.

### **OPERATING RANGES**

### **Commercial (C) Devices**

| Temperature (T <sub>A</sub> ) Operating in Free Air | 0°C to +70°C |

|-----------------------------------------------------|--------------|

| Supply Voltage (Vcc) with Respect to Ground +4.75   | V to +5.25 V |

Operating ranges define those limits between which the functionality of the device is guaranteed.

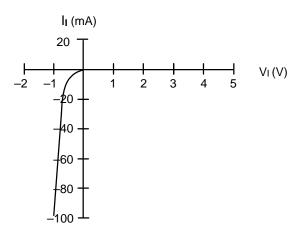

### DC CHARACTERISTICS over COMMERCIAL operating ranges unless otherwise specified

| Parameter<br>Symbol | Parameter Description                    | Test Conditions                                                                                                                         | Min | Тур | Max  | Unit |

|---------------------|------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|-----|-----|------|------|

| Voн                 | Output HIGH Voltage                      | IOH = -3.2 mA, VCC = Min<br>VIN = VIH or VIL                                                                                            | 2.4 |     |      | V    |

| Vol                 | Output LOW Voltage                       | I <sub>OL</sub> = 16 mA, V <sub>CC</sub> = Min<br>V <sub>IN</sub> = V <sub>IH</sub> or V <sub>IL</sub>                                  |     |     | 0.5  | V    |

| ViH                 | Input HIGH Voltage                       | Guaranteed Input Logical HIGH<br>Voltage for all Inputs (Note 1)                                                                        | 2.0 |     |      | V    |

| VIL                 | Input LOW Voltage                        | Guaranteed Input Logical LOW<br>Voltage for all Inputs (Note 1)                                                                         |     |     | 0.8  | V    |

| Іін                 | Input HIGH Leakage Current               | V <sub>IN</sub> = 5.25 V, V <sub>CC</sub> = Max (Note 2)                                                                                |     |     | 10   | μΑ   |

| lı∟                 | Input LOW Leakage Current                | VIN = 0 V, Vcc = Max (Note 2)                                                                                                           |     |     | -100 | μΑ   |

| Іоzн                | Off-State Output Leakage<br>Current HIGH | Vout = 5.25 V, Vcc = Max<br>V <sub>IN</sub> = V <sub>IH</sub> or V <sub>IL</sub> (Note 2)                                               |     |     | 10   | μΑ   |

| lozL                | Off-State Output Leakage<br>Current LOW  | Vout = 0 V, Vcc = Max<br>Vin = Vih or Vil (Note 2)                                                                                      |     |     | -100 | μΑ   |

| Isc                 | Output Short-Circuit Current             | V <sub>OUT</sub> = 0.5 V, V <sub>CC</sub> = Max (Note 3)                                                                                | -30 |     | -160 | mA   |

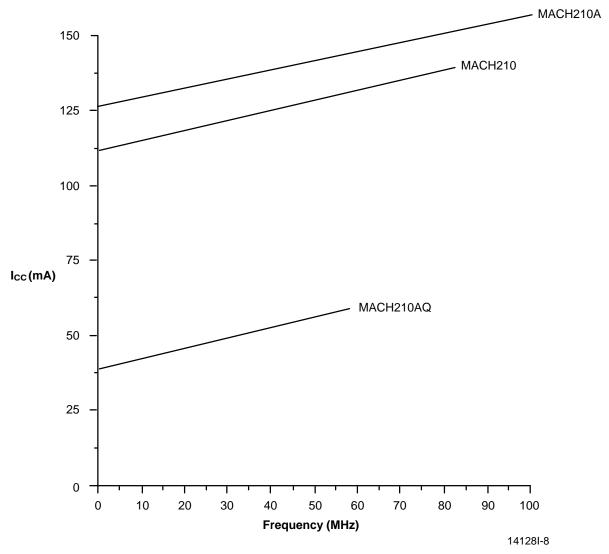

| Icc                 | Supply Current                           | V <sub>IN</sub> = 0 V, Outputs Open (I <sub>OUT</sub> = 0 mA)<br>V <sub>CC</sub> = 5.0 V, f = 25 MHz, T <sub>A</sub> = 25°C<br>(Note 4) |     | 130 |      | mA   |

- 1. These are absolute values with respect to device ground and all overshoots due to system or tester noise are included.

- 2. I/O pin leakage is the worst case of I<sub>IL</sub> and I<sub>OZL</sub> (or I<sub>I</sub>H and I<sub>OZ</sub>H).

- 3. Not more than one output should be shorted at a time and duration of the short-circuit should not exceed one second.  $V_{OUT} = 0.5 \text{ V}$  has been chosen to avoid test problems caused by tester ground degradation.

- 4. This parameter is measured with a 16-bit up/down counter pattern. This pattern is programmed in each PAL block and capable of being loaded, enabled, and reset.

## **CAPACITANCE (Note 1)**

| Parameter<br>Symbol | Parameter Description | Test Conditions         |                                                     | Тур | Unit |

|---------------------|-----------------------|-------------------------|-----------------------------------------------------|-----|------|

| CIN                 | Input Capacitance     | V <sub>IN</sub> = 2.0 V | $V_{CC} = 5.0 \text{ V}, T_A = 25^{\circ}\text{C},$ | 6   | pF   |

| Соит                | Output Capacitance    | Vout = 2.0 V            | f = 1 MHz                                           | 8   | pF   |

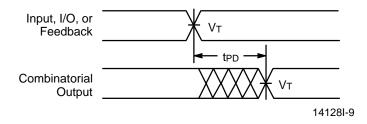

## **SWITCHING CHARACTERISTICS over COMMERCIAL operating ranges**

| Parameter       |                                                                             |                                                                               | -      | -7    |     | ]    |

|-----------------|-----------------------------------------------------------------------------|-------------------------------------------------------------------------------|--------|-------|-----|------|

| Symbol          | Parameter Description                                                       |                                                                               |        | Min   | Max | Unit |

| t <sub>PD</sub> | Input, I/O, or Feedback to Combinatorial Output                             |                                                                               |        | 7.5   | ns  |      |

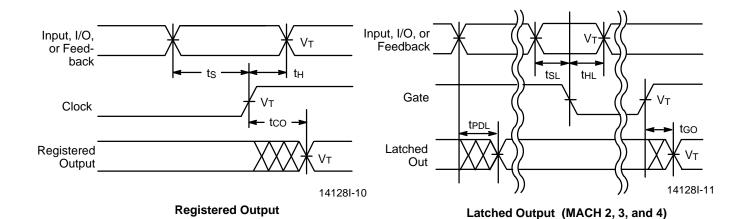

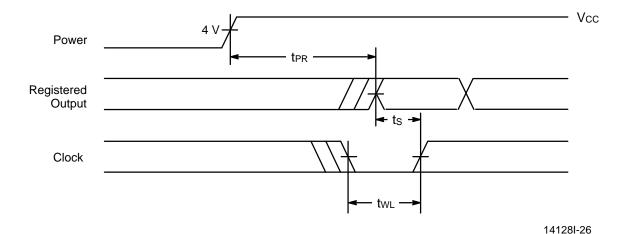

| ts              | Setup Time                                                                  | e from Input, I/O or Feedback to Clock                                        | D-Type | 5.5   |     | ns   |

|                 |                                                                             |                                                                               | T-Type | 6.5   |     | ns   |

| tн              | Register D                                                                  | ata Hold Time                                                                 |        | 0     |     | ns   |

| tco             | Clock to O                                                                  | utput                                                                         |        |       | 5   | ns   |

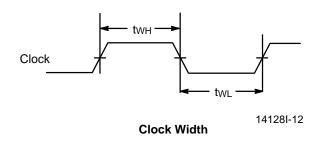

| tw∟             | Clock Widt                                                                  | h                                                                             | LOW    | 3     |     | ns   |

| twH             |                                                                             |                                                                               | HIGH   | 3     |     | ns   |

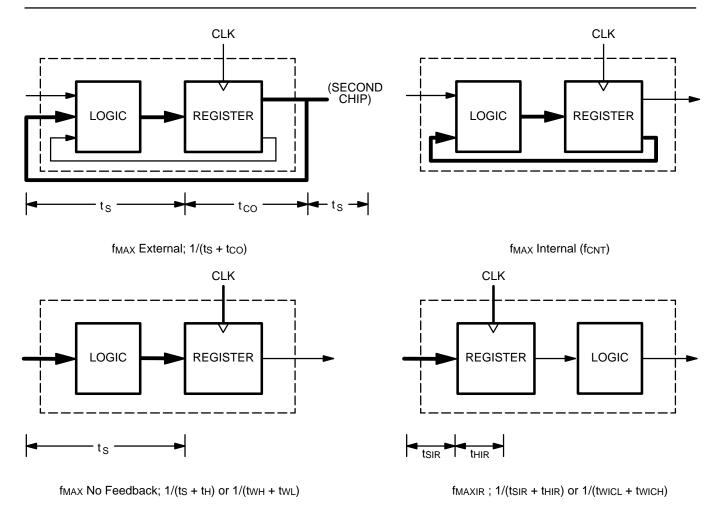

|                 |                                                                             | Futament Foodbook                                                             | D-Type | 100   |     | MHz  |

|                 | Maximum                                                                     | External Feedback                                                             | T-Type | 91    |     | MHz  |

| fmax            | Frequency                                                                   |                                                                               | D-Type | 133   |     | MHz  |

|                 |                                                                             | Internal Feedback (fcnt)                                                      | T-Type | 125   |     | MHz  |

|                 |                                                                             | No Feedback                                                                   |        | 166.7 |     | MHz  |

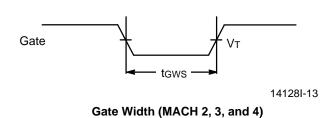

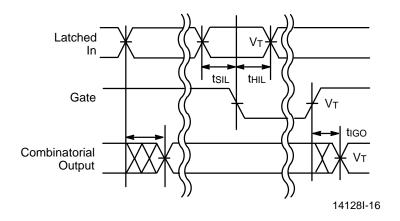

| tsL             | Setup Time from Input, I/O, or Feedback to Gate                             |                                                                               | 5.5    |       | ns  |      |

| tHL             | Latch Data Hold Time                                                        |                                                                               | 0      |       | ns  |      |

| tgo             | Gate to Output                                                              |                                                                               |        | 6     | ns  |      |

| tgwL            | Gate Width LOW                                                              |                                                                               | 3      |       | ns  |      |

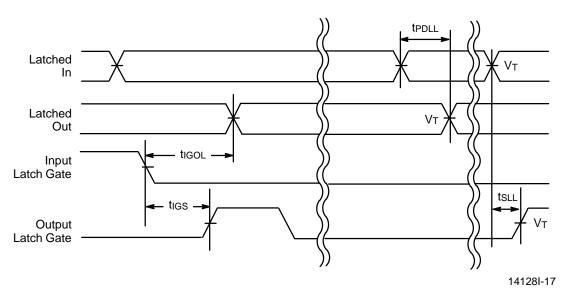

| tpDL            | Input, I/O, or Feedback to Output Through Transparent Input or Output Latch |                                                                               |        | 9.5   | ns  |      |

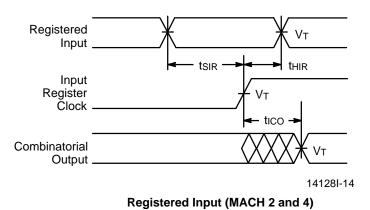

| tsır            | Input Regis                                                                 | ster Setup Time                                                               |        | 2     |     | ns   |

| thir            | Input Regis                                                                 | ster Hold Time                                                                |        | 2     |     | ns   |

| tico            | Input Regis                                                                 | ster Clock to Combinatorial Output                                            |        |       | 11  | ns   |

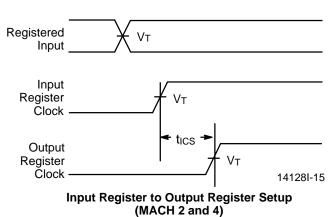

| tics            | Input Regis                                                                 | ster Clock to Output Register Setup                                           | D-Type | 9     |     | ns   |

|                 |                                                                             |                                                                               | T-Type | 10    |     | ns   |

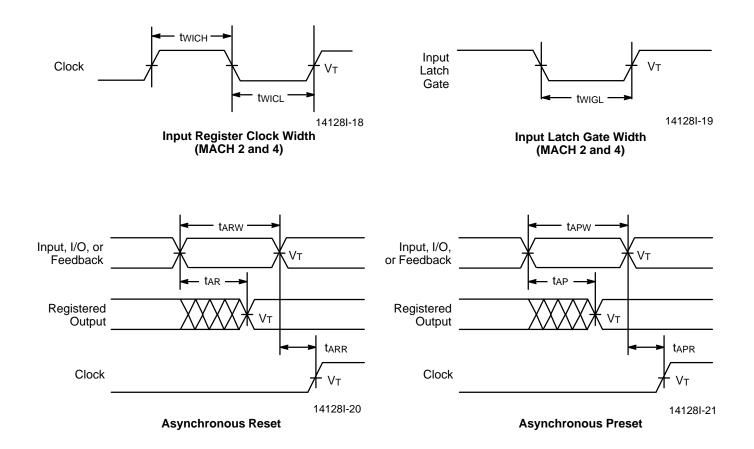

| twicl           | Input Regis                                                                 | ster Clock Width                                                              | LOW    | 3     |     | ns   |

| twich           |                                                                             |                                                                               | HIGH   | 3     |     | ns   |

| fmaxir          | Maximum                                                                     | Input Register Frequency                                                      |        | 166.7 |     | MHz  |

| tsıL            | Input Latch Setup Time                                                      |                                                                               | 2      |       | ns  |      |

| tHIL            | Input Latch Hold Time                                                       |                                                                               | 2      |       | ns  |      |

| tigo            | Input Latch Gate to Combinatorial Output                                    |                                                                               |        | 12    | ns  |      |

| tigoL           | Input Latch Gate to Output Through Transparent Output Latch                 |                                                                               |        | 14    | ns  |      |

| tsll            |                                                                             | e from Input, I/O, or Feedback Through<br>nt Input Latch to Output Latch Gate |        | 7.5   |     | ns   |

## **SWITCHING CHARACTERISTICS over COMMERCIAL operating ranges (continued)**

| Parameter       |                                                                                | -7  |      |      |

|-----------------|--------------------------------------------------------------------------------|-----|------|------|

| Symbol          | Parameter Description                                                          | Min | Max  | Unit |

| tigs            | Input Latch Gate to Output Latch Setup                                         | 10  |      | ns   |

| twigL           | Input Latch Gate Width LOW                                                     | 3   |      | ns   |

| tPDLL           | Input, I/O, or Feedback to Output Through Transparent Input and Output Latches |     | 11.5 | ns   |

| t <sub>AR</sub> | Asynchronous Reset to Registered or Latched Output                             |     | 12   | ns   |

| tarw            | Asynchronous Reset Width                                                       | 8   |      | ns   |

| tarr            | Asynchronous Reset Recovery Time                                               | 8   |      | ns   |

| t <sub>AP</sub> | Asynchronous Preset to Registered or Latched Output                            |     | 12   | ns   |

| tapw            | Asynchronous Preset Width                                                      | 8   |      | ns   |

| tapr            | Asynchronous Preset Recovery Time                                              | 8   |      | ns   |

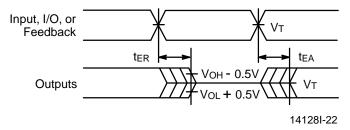

| tEA             | Input, I/O, or Feedback to Output Enable                                       |     | 7.5  | ns   |

| t <sub>ER</sub> | Input, I/O, or Feedback to Output Disable                                      |     | 7.5  | ns   |

<sup>1.</sup> These parameters are not 100% tested, but are evaluated at initial characterization and at any time the design is modified where capacitance may be affected.

### **ABSOLUTE MAXIMUM RATINGS**

| Storage Temperature $\ \dots \ -65^{\circ}C$ to +150°C                 |

|------------------------------------------------------------------------|

| Ambient Temperature with Power Applied55°C to +125°C                   |

| Supply Voltage with Respect to Ground $\dots -0.5 \text{ V}$ to +7.0 V |

| DC Input Voltage $-0.5~\text{V}$ to Vcc + 0.5 V                        |

| DC Output or I/O Pin Voltage0.5 V to V <sub>CC</sub> + 0.5 V           |

| Static Discharge Voltage 2001 V                                        |

| Latchup Current ( $T_A = 0^{\circ}C$ to $+70^{\circ}C$ ) 200 mA        |

Stresses above those listed under Absolute Maximum Ratings may cause permanent device failure. Functionality at or above these limits is not implied. Exposure to Absolute Maximum Ratings for extended periods may affect device reliability. Programming conditions may differ.

### **OPERATING RANGES**

### **Commercial (C) Devices**

| Temperature (T <sub>A</sub> ) Operating in Free Air 0°C to +70°C |

|------------------------------------------------------------------|

| Supply Voltage (Vcc) with Respect to Ground +4.75 V to +5.25 \   |

Operating ranges define those limits between which the functionality of the device is guaranteed.

### DC CHARACTERISTICS over COMMERCIAL operating ranges unless otherwise specified

| Parameter<br>Symbol | Parameter Description                    | Test Conditions                                                                                          | Min | Тур | Max  | Unit |

|---------------------|------------------------------------------|----------------------------------------------------------------------------------------------------------|-----|-----|------|------|

| Vон                 | Output HIGH Voltage                      | $I_{OH} = -3.2$ mA, $V_{CC} = Min$<br>$V_{IN} = V_{IH}$ or $V_{IL}$                                      | 2.4 |     |      | V    |

| VoL                 | Output LOW Voltage                       | $I_{OL}$ = 16 mA, $V_{CC}$ = Min $V_{IN}$ = $V_{IH}$ or $V_{IL}$                                         |     |     | 0.5  | V    |

| V <sub>IH</sub>     | Input HIGH Voltage                       | Guaranteed Input Logical HIGH<br>Voltage for all Inputs (Note 1)                                         | 2.0 |     |      | V    |

| V <sub>IL</sub>     | Input LOW Voltage                        | Guaranteed Input Logical LOW<br>Voltage for all Inputs (Note 1)                                          |     |     | 0.8  | V    |

| I <sub>IH</sub>     | Input HIGH Leakage Current               | $V_{IN} = 5.25 \text{ V}, V_{CC} = \text{Max (Note 2)}$                                                  |     |     | 10   | μΑ   |

| I <sub>IL</sub>     | Input LOW Leakage Current                | $V_{IN} = 0 \text{ V}, V_{CC} = \text{Max (Note 2)}$                                                     |     |     | -100 | μA   |

| l <sub>ozh</sub>    | Off-State Output Leakage<br>Current HIGH | $V_{OUT} = 5.25 \text{ V}, V_{CC} = \text{Max}$<br>$V_{IN} = V_{IH} \text{ or } V_{IL} \text{ (Note 2)}$ |     |     | 10   | μΑ   |

| l <sub>ozL</sub>    | Off-State Output Leakage<br>Current LOW  | $V_{OUT} = 0 \text{ V}, V_{CC} = \text{Max}$<br>$V_{IN} = V_{IH} \text{ or } V_{IL} \text{ (Note 2)}$    |     |     | -100 | μΑ   |

| I <sub>sc</sub>     | Output Short-Circuit Current             | $V_{OUT} = 0.5 \text{ V}, V_{CC} = \text{Max (Note 3)}$                                                  | -30 |     | -160 | mA   |

| Icc                 | Supply Current (Typical)                 | V <sub>CC</sub> = 5V, T <sub>A</sub> = 25°C, f = 25 MHz<br>(Note 4)                                      |     | 135 |      | mA   |

- 1. These are absolute values with respect to device ground and all overshoots due to system or tester noise are included.

- 2. I/O pin leakage is the worst case of I<sub>IL</sub> and I<sub>OZL</sub> (or I<sub>IH</sub> and I<sub>OZH</sub>).

- 3. Not more than one output should be shorted at a time and duration of the short-circuit should not exceed one second. Vout = 0.5 V has been chosen to avoid test problems caused by tester ground degradation.

- 4. Measured with a 16-bit up/down counter pattern. This pattern is programmed in each PAL block and is capable of being loaded, enabled, and reset.

## CAPACITANCE (Note 1)

| Parameter<br>Symbol | Parameter Description | Test Conditions          |                                                     | Тур | Unit |

|---------------------|-----------------------|--------------------------|-----------------------------------------------------|-----|------|

| C <sub>IN</sub>     | Input Capacitance     | V <sub>IN</sub> = 2.0 V  | $V_{CC} = 5.0 \text{ V}, T_A = 25^{\circ}\text{C},$ | 6   | pF   |

| Соит                | Output Capacitance    | V <sub>OUT</sub> = 2.0 V | f = 1 MHz                                           | 8   | pF   |

## **SWITCHING CHARACTERISTICS over COMMERCIAL operating ranges (Note 2)**

| Parameter        |                                                                                                            |                                                 |          |                  |             | -1            | 0   | -1:    | 2   |          |

|------------------|------------------------------------------------------------------------------------------------------------|-------------------------------------------------|----------|------------------|-------------|---------------|-----|--------|-----|----------|

| Symbol           | Parameter I                                                                                                | Description                                     |          |                  |             | Min           | Max | Min    | Max | Unit     |

| t <sub>PD</sub>  | Input, I/O, or<br>(Note 3)                                                                                 | r Feedback to Combi                             | natorial | Output           |             |               | 10  |        | 12  | ns       |

| 4                |                                                                                                            | from Input, I/O,                                |          |                  | D-Type      | 6.5           |     | 7      |     | ns       |

| ts               | or Feedback                                                                                                | to Clock                                        |          |                  | T-Type      | 7.5           |     | 8      |     | ns       |

| t <sub>H</sub>   | Register Dat                                                                                               | ta Hold Time                                    |          |                  |             | 0             |     | 0      |     | ns       |

| t <sub>CO</sub>  | Clock to Out                                                                                               | tput (Note 3)                                   |          |                  |             |               | 6   |        | 8   | ns       |

| tw∟              | Clock                                                                                                      |                                                 |          |                  | LOW         | 5             |     | 6      |     | ns       |

| t <sub>WH</sub>  | Width                                                                                                      |                                                 |          |                  | HIGH        | 5             |     | 6      |     | ns       |

|                  |                                                                                                            |                                                 |          |                  | D-Type      | 80            |     | 66.7   |     | MHz      |

|                  | Maximum                                                                                                    | External Feedback                               | 1/(ts +  | +tco)            | T-Type      | 74            |     | 62.5   |     | MHz      |

| f <sub>MAX</sub> | Frequency                                                                                                  |                                                 |          |                  | D-Type      | 100           |     | 83.3   |     | MHz      |

|                  | (Note 1)                                                                                                   | Internal Feedback (                             | fcnt)    |                  | T-Type      | 91            |     | 76.9   |     | MHz      |

|                  |                                                                                                            | No Feedback                                     | 1/(ts +  | t <sub>H</sub> ) |             | 100           |     | 83.3   |     | MHz      |

| tsL              | Setup Time                                                                                                 | Setup Time from Input, I/O, or Feedback to Gate |          |                  |             | 6.5           |     | 7      |     | ns       |

| t <sub>HL</sub>  | Latch Data Hold Time                                                                                       |                                                 |          | 0                |             | 0             |     | ns     |     |          |

| t <sub>GO</sub>  | Gate to Output (Note 3)                                                                                    |                                                 |          |                  | 7           |               | 10  | ns     |     |          |

| t <sub>GWL</sub> | Gate Width I                                                                                               | Gate Width LOW                                  |          |                  | 5           |               | 6   |        | ns  |          |

| t <sub>PDL</sub> |                                                                                                            | r Feedback to Output<br>Input or Output Latcl   |          | gh               |             |               | 12  |        | 14  | ns       |

| tsir             |                                                                                                            | er Setup Time                                   | 11       |                  |             | 2             | 12  | 2      | 14  |          |

|                  |                                                                                                            | er Hold Time                                    |          |                  |             | 2             |     | 2      |     | ns       |

| tHIR             |                                                                                                            | er Clock to Combinat                            | arial O  | utnut            |             |               | 13  |        | 15  | ns       |

| t <sub>ICO</sub> |                                                                                                            | er Clock to Combinat                            |          | •                | D-Type      | 10            | 13  | 12     | 10  | ns       |

| t <sub>ICS</sub> | input Kegist                                                                                               | er Clock to Output Re                           | egister  | Setup            | · ·         |               |     |        |     | ns       |

|                  |                                                                                                            |                                                 |          |                  | T-Type      | 11            |     | 13     |     | ns       |

| twich            | Input Register Clock Width                                                                                 |                                                 |          |                  | LOW<br>HIGH | <u>5</u><br>5 |     | 6<br>6 |     | ns<br>ns |

| fmaxir           |                                                                                                            | put Register Frequer                            | ncy 1    | /(twich + twich  | •           | 100           |     | 83.3   |     | MHz      |

| tsıL             | Input Latch                                                                                                | Setup Time                                      |          | •                | <u> </u>    | 2             |     | 2      |     | ns       |

| tHIL             | •                                                                                                          | nput Latch Hold Time                            |          |                  | 2           |               | 2   |        | ns  |          |

| tigo             | Input Latch Gate to Combinatorial Output                                                                   |                                                 |          |                  | 14          |               | 17  | ns     |     |          |

| tigoL            | Input Latch Gate to Output Through Transparent                                                             |                                                 |          |                  | 16          |               | 19  | ns     |     |          |

| tsll             | Output Latch  Setup Time from Input, I/O, or Feedback Through Transparent Input Latch to Output Latch Gate |                                                 |          | 8.5              | 10          | 9             | 10  | ns     |     |          |

| t <sub>IGS</sub> | •                                                                                                          | Gate to Output Latch                            |          | Jale             |             | 11            |     | 13     |     | ns       |

| นษร              | Input Later t                                                                                              | Cale to Output Later                            | Setup    |                  |             | ''            |     | 13     |     | 113      |

# **SWITCHING CHARACTERISTICS over COMMERCIAL operating ranges (Note 2) (continued)**

| Parameter         | ter -10 -12                                                                    |    | 2   |     |     |      |

|-------------------|--------------------------------------------------------------------------------|----|-----|-----|-----|------|

| Symbol            | Parameter Description                                                          |    | Max | Min | Max | Unit |

| twigL             | Input Latch Gate Width LOW                                                     | 5  |     | 6   |     | ns   |

| t <sub>PDLL</sub> | Input, I/O, or Feedback to Output Through Transparent Input and Output Latches |    | 14  |     | 16  | ns   |

| t <sub>AR</sub>   | Asynchronous Reset to Registered or Latched Output                             |    | 25  |     | 16  | ns   |

| tarw              | Asynchronous Reset Width (Note 1)                                              | 10 |     | 12  |     | ns   |

| t <sub>ARR</sub>  | Asynchronous Reset Recovery Time (Note 1)                                      | 10 |     | 8   |     | ns   |

| t <sub>AP</sub>   | Asynchronous Preset to Registered or Latched Output                            |    | 15  |     | 16  | ns   |

| tapw              | Asynchronous Preset Width (Note 1)                                             | 10 |     | 12  |     | ns   |

| t <sub>APR</sub>  | Asynchronous Preset Recovery Time (Note 1)                                     | 10 |     | 8   |     | ns   |

| t <sub>EA</sub>   | Input, I/O, or Feedback to Output Enable (Note 3)                              |    | 10  |     | 12  | ns   |

| ter               | Input, I/O, or Feedback to Output Disable (Note 3)                             |    | 10  |     | 12  | ns   |

- 1. These parameters are not 100% tested, but are evaluated at initial characterization and at any time the design is modified where capacitance may be affected.

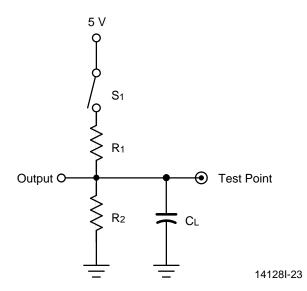

- 2. See Switching Test Circuit, for test conditions.

- 3. Parameters measured with 16 outputs switching.

### **ABSOLUTE MAXIMUM RATINGS**

| Storage Temperature –65°C to +150°C                             |

|-----------------------------------------------------------------|

| Ambient Temperature with Power Applied –55°C to +125°C          |

| Supply Voltage with Respect to Ground0.5 V to +7.0 V            |

| DC Input Voltage0.5 V to Vcc + 0.5 V                            |

| DC Output or                                                    |

| I/O Pin Voltage $-0.5 \text{ V}$ to $V_{CC} + 0.5 \text{ V}$    |

| Static Discharge Voltage 2001 V                                 |

| Latchup Current ( $T_A = 0^{\circ}C$ to $+70^{\circ}C$ ) 200 mA |

Stresses above those listed under Absolute Maximum Ratings may cause permanent device failure. Functionality at or above these limits is not implied. Exposure to Absolute Maximum Ratings for extended periods may affect device reliability. Programming conditions may differ.

### **INDUSTRIAL OPERATING RANGES**

| Temperature (T <sub>A</sub> ) Operating in Free Air | –40°C to +85°C   |

|-----------------------------------------------------|------------------|

| Supply Voltage (V <sub>CC</sub> ) with              | 40 0 10 100 0    |

| Respect to Ground                                   | +4.5 V to +5.5 V |

Operating ranges define those limits between which the functionality of the device is guaranteed.

### DC CHARACTERISTICS over COMMERCIAL operating ranges unless otherwise specified

| Parameter<br>Symbol | Parameter Description                    | Test Conditions                                                                                          | Min | Тур | Max  | Unit |

|---------------------|------------------------------------------|----------------------------------------------------------------------------------------------------------|-----|-----|------|------|

| V <sub>он</sub>     | Output HIGH Voltage                      | $I_{OH} = -3.2$ mA, $V_{CC} = Min$<br>$V_{IN} = V_{IH}$ or $V_{IL}$                                      | 2.4 |     |      | >    |

| V <sub>OL</sub>     | Output LOW Voltage                       | $I_{OL}$ = 16 mA, $V_{CC}$ = Min $V_{IN}$ = $V_{IH}$ or $V_{IL}$                                         |     |     | 0.5  | ٧    |

| ViH                 | Input HIGH Voltage                       | Guaranteed Input Logical HIGH<br>Voltage for all Inputs (Note 1)                                         | 2.0 |     |      | V    |

| V <sub>IL</sub>     | Input LOW Voltage                        | Guaranteed Input Logical LOW<br>Voltage for all Inputs (Note 1)                                          |     |     | 0.8  | V    |

| I <sub>IH</sub>     | Input HIGH Leakage Current               | $V_{IN} = 5.25 \text{ V}, V_{CC} = \text{Max (Note 2)}$                                                  |     |     | 10   | μΑ   |

| I <sub>IL</sub>     | Input LOW Leakage Current                | $V_{IN} = 0 \text{ V}, V_{CC} = \text{Max (Note 2)}$                                                     |     |     | -100 | μA   |

| Іохн                | Off-State Output Leakage<br>Current HIGH | $V_{OUT} = 5.25 \text{ V}, V_{CC} = \text{Max}$<br>$V_{IN} = V_{IH} \text{ or } V_{IL} \text{ (Note 2)}$ |     |     | 10   | μΑ   |

| l <sub>ozL</sub>    | Off-State Output Leakage<br>Current LOW  | $V_{OUT} = 0 \text{ V}, V_{CC} = \text{Max}$<br>$V_{IN} = V_{IH} \text{ or } V_{IL} \text{ (Note 2)}$    |     |     | -100 | μΑ   |

| Isc                 | Output Short-Circuit Current             | V <sub>OUT</sub> = 0.5 V, V <sub>CC</sub> = Max (Note 3)                                                 | -30 |     | -160 | mA   |

| Icc                 | Supply Current (Typical)                 | $V_{CC} = 5V$ , $T_A = 25$ °C, $f = 25$ MHz (Note 4)                                                     |     | 135 |      | mA   |

- 1. These are absolute values with respect to device ground and all overshoots due to system or tester noise are included.

- 2. I/O pin leakage is the worst case of IIL and IOZL (or IIH and IOZH).

- 3. Not more than one output should be shorted at a time and duration of the short-circuit should not exceed one second.  $V_{OUT} = 0.5 \text{ V}$  has been chosen to avoid test problems caused by tester ground degradation.

- 4. Measured with a 16-bit up/down counter pattern. This pattern is programmed in each PAL block and is capable of being loaded, enabled, and reset.

# CAPACITANCE (Note 1)

| Parameter<br>Symbol | Parameter Description | Test Conditions          |                                                     | Тур | Unit |

|---------------------|-----------------------|--------------------------|-----------------------------------------------------|-----|------|

| C <sub>IN</sub>     | Input Capacitance     | V <sub>IN</sub> = 2.0 V  | $V_{CC} = 5.0 \text{ V}, T_A = 25^{\circ}\text{C},$ | 6   | pF   |

| Соит                | Output Capacitance    | V <sub>OUT</sub> = 2.0 V | f = 1 MHz                                           | 8   | pF   |

# **SWITCHING CHARACTERISTICS over COMMERCIAL operating ranges (Note 2)**

| Parameter          |                                                             |                                                  |                          |          |        | -1     | 2     | -1-  | 4     |      |

|--------------------|-------------------------------------------------------------|--------------------------------------------------|--------------------------|----------|--------|--------|-------|------|-------|------|

| Symbol             | Parameter I                                                 | Description                                      |                          |          |        | Min    | Max   | Min  | Max   | Unit |

| t <sub>PD</sub>    | Input, I/O, or (Note 3)                                     | r Feedback to Combi                              | natorial Out             | tput     |        |        | 12    |      | 14.5  | ns   |

|                    |                                                             | from Input, I/O,                                 |                          |          | D-Type | 8      |       | 8.5  |       | ns   |

| <b>t</b> s         | or Feedback                                                 | to Clock                                         |                          |          | T-Type | 9      |       | 10   |       | ns   |

| t <sub>H</sub>     | Register Da                                                 | ta Hold Time                                     |                          |          | •      | 0      |       | 0    |       | ns   |

| tco                | Clock to Out                                                | tput (Note 3)                                    |                          |          |        |        | 7.5   |      | 10    | ns   |

| tw∟                | Clock                                                       |                                                  |                          |          | LOW    | 6      |       | 7.5  |       | ns   |

| t <sub>WH</sub>    | Width                                                       |                                                  |                          |          | HIGH   | 6      |       | 7.5  |       | ns   |

|                    |                                                             |                                                  |                          |          | D-Type | 64     |       | 53   |       | MHz  |

|                    | Maximum                                                     | External Feedback                                | 1/(ts + tcc              | o)       | T-Type | 59     |       | 50   |       | MHz  |

| f <sub>MAX</sub>   | Frequency                                                   |                                                  |                          |          | D-Type | 80     |       | 61.5 |       | MHz  |

|                    | (Note 1)                                                    | Internal Feedback (                              | fcnt)                    |          | T-Type | 72.5   |       | 57   |       | MHz  |

|                    |                                                             | No Feedback                                      | 1/(ts + t <sub>H</sub> ) |          |        | 80     |       | 66.5 |       | MHz  |

| tsL                | Setup Time                                                  | from Input, I/O, or Fe                           | edback to                | Gate     |        | 8      |       | 8.5  |       | ns   |

| t <sub>HL</sub>    | Latch Data Hold Time                                        |                                                  |                          |          | 0      |        | 0     |      | ns    |      |

| tgo                |                                                             | Gate to Output (Note 3)                          |                          |          |        | 8.5    |       | 12   | ns    |      |

| t <sub>GWL</sub>   |                                                             | Gate Width LOW                                   |                          |          | 6      |        | 7.5   |      | ns    |      |

| t <sub>PDL</sub>   |                                                             | Input, I/O, or Feedback to Output Through        |                          |          |        |        | - 110 |      | - 110 |      |

| -1 52              |                                                             | Input or Output Latel                            |                          |          |        |        | 14.5  |      | 17    | ns   |

| tsır               | Input Regist                                                | er Setup Time                                    |                          |          |        | 2.5    |       | 2.5  |       | ns   |

| t <sub>HIR</sub>   | Input Regist                                                | er Hold Time                                     |                          |          |        | 3      |       | 3    |       | ns   |

| t <sub>ICO</sub>   | Input Regist                                                | er Clock to Combinat                             | orial Outpu              | ıt       |        |        | 16    |      | 18    | ns   |

| t <sub>ICS</sub>   | Input Regist                                                | er Clock to Output Re                            | egister Setu             | qı       | D-Type | 12     |       | 14.5 |       | ns   |

|                    |                                                             |                                                  |                          |          | T-Type | 13     |       | 16   |       | ns   |

| twicl              | Input Regist                                                | er                                               |                          |          | LOW    | 6      |       | 7.5  |       | ns   |

| twich              | Clock Width                                                 |                                                  |                          |          | HIGH   | 6      |       | 7.5  |       | ns   |

| f <sub>MAXIR</sub> | Maximum In                                                  | nput Register Frequer                            | ncy 1/(twi               | cL + twi | сн)    | 80     |       | 66.5 |       | MHz  |

| tsıL               | Input Latch                                                 | Setup Time                                       |                          |          |        | 2.5    |       | 2.5  |       | ns   |

| tHIL               | Input Latch                                                 | ut Latch Hold Time                               |                          |          | 3      |        | 3     |      | ns    |      |

| tigo               | Input Latch                                                 | nput Latch Gate to Combinatorial Output          |                          |          |        | 17     |       | 20.5 | ns    |      |

| tigoL              | Input Latch Gate to Output Through Transparent Output Latch |                                                  |                          |          | 19.5   |        | 23    | ns   |       |      |

| tsll               | Setup Time                                                  | from Input, I/O, or Fe<br>t Input Latch to Outpu |                          |          |        | 10.5   |       | 11   |       | ns   |

| t <sub>IGS</sub>   | ·                                                           | Gate to Output Latch                             |                          |          |        | 13.5   |       | 16   |       | ns   |

| -,50               | input Lateri Gate to Gutput Lateri Getup                    |                                                  |                          |          |        | 1 .0.0 |       |      |       | •    |

# SWITCHING CHARACTERISTICS over COMMERCIAL operating ranges (Note 2) (continued)

| Parameter         | er                                                                             |    | -12  |      | -14  |      |

|-------------------|--------------------------------------------------------------------------------|----|------|------|------|------|

| Symbol            | Parameter Description                                                          |    | Max  | Min  | Max  | Unit |

| twigL             | Input Latch Gate Width LOW                                                     | 6  |      | 7.5  |      | ns   |

| t <sub>PDLL</sub> | Input, I/O, or Feedback to Output Through Transparent Input and Output Latches |    | 17   |      | 19.5 | ns   |

| t <sub>AR</sub>   | Asynchronous Reset to Registered or Latched Output                             |    | 19.5 |      | 19.5 | ns   |

| t <sub>ARW</sub>  | Asynchronous Reset Width (Note 1)                                              | 12 |      | 14.5 |      | ns   |

| tarr              | Asynchronous Reset Recovery Time (Note 1)                                      | 12 |      | 10   |      | ns   |

| t <sub>AP</sub>   | Asynchronous Preset to Registered or Latched Output                            |    | 18   |      | 19.5 | ns   |

| t <sub>APW</sub>  | Asynchronous Preset Width (Note 1)                                             | 12 |      | 14.5 |      | ns   |

| t <sub>APR</sub>  | Asynchronous Preset Recovery Time (Note 1)                                     | 12 |      | 10   |      | ns   |

| t <sub>EA</sub>   | Input, I/O, or Feedback to Output Enable (Note 3)                              |    | 12   |      | 14.5 | ns   |

| t <sub>ER</sub>   | Input, I/O, or Feedback to Output Disable (Note 3)                             |    | 12   |      | 14.5 | ns   |

- 1. These parameters are not 100% tested, but are evaluated at initial characterization and at any time the design is modified where capacitance may be affected.

- 2. See Switching Test Circuit, for test conditions.

- 3. Parameters measured with 16 outputs switching.

### **ABSOLUTE MAXIMUM RATINGS**

| Storage Temperature $\ \dots \ -65^{\circ}\text{C}$ to +150°C                         |

|---------------------------------------------------------------------------------------|

| Ambient Temperature with Power Applied55°C to +125°C                                  |

| Supply Voltage with Respect to Ground $\dots -0.5 \text{ V}$ to +7.0 V                |

| DC Input Voltage $-0.5$ V to Vcc + 0.5 V                                              |

| DC Output or I/O Pin Voltage $\dots -0.5 \text{ V}$ to $\text{V}_{\text{CC}}$ + 0.5 V |

| Static Discharge Voltage 2001 V                                                       |

| Latchup Current ( $T_A = 0$ °C to +70°C) 200 mA                                       |

Stresses above those listed under Absolute Maximum Ratings may cause permanent device failure. Functionality at or above these limits is not implied. Exposure to Absolute Maximum Ratings for extended periods may affect device reliability. Programming conditions may differ.

### **OPERATING RANGES**

### **Commercial (C) Devices**

| Temperature (T <sub>A</sub> ) Operating in Free Air 0° | C to +70°C   |

|--------------------------------------------------------|--------------|

| Supply Voltage (Vcc) with Respect to Ground +4.75 V    | ′ to +5.25 V |

Operating ranges define those limits between which the functionality of the device is guaranteed.

### DC CHARACTERISTICS over COMMERCIAL operating ranges unless otherwise specified

| Parameter<br>Symbol | Parameter Description                    | Test Conditions                                                                                                                             | Min | Тур | Max  | Unit |

|---------------------|------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|------|------|

| V <sub>он</sub>     | Output HIGH Voltage                      | $I_{OH} = -3.2$ mA, $V_{CC} = Min$<br>$V_{IN} = V_{IH}$ or $V_{IL}$                                                                         |     | 2.4 |      | V    |

| V <sub>OL</sub>     | Output LOW Voltage                       | $I_{OL} = 16 \text{ mA}, V_{CC} = \text{Min}$<br>$V_{IN} = V_{IH} \text{ or } V_{IL}$                                                       |     |     | 0.5  | V    |

| V <sub>IH</sub>     | Input HIGH Voltage                       | Guaranteed Input Logical HIGH<br>Voltage for all Inputs (Note 1)                                                                            | 2.0 |     |      | V    |

| VIL                 | Input LOW Voltage                        | Guaranteed Input Logical LOW<br>Voltage for all Inputs (Note 1)                                                                             |     |     | 8.0  | V    |

| I <sub>IH</sub>     | Input HIGH Leakage Current               | $V_{IN} = 5.25 \text{ V}, V_{CC} = \text{Max (Note 2)}$                                                                                     |     |     | 10   | μΑ   |

| I <sub>IL</sub>     | Input LOW Leakage Current                | $V_{IN} = 0 \text{ V}, V_{CC} = \text{Max (Note 2)}$                                                                                        |     |     | -10  | μΑ   |

| l <sub>ozh</sub>    | Off-State Output Leakage<br>Current HIGH | $V_{\text{OUT}} = 5.25 \text{ V}, V_{\text{CC}} = \text{Max}$<br>$V_{\text{IN}} = V_{\text{IH}} \text{ or } V_{\text{IL}} \text{ (Note 2)}$ |     |     | 10   | μА   |

| l <sub>OZL</sub>    | Off-State Output Leakage<br>Current LOW  | $V_{OUT} = 0 \text{ V}, V_{CC} = \text{Max}$<br>$V_{IN} = V_{IH} \text{ or } V_{IL} \text{ (Note 2)}$                                       |     |     | -10  | μΑ   |

| I <sub>sc</sub>     | Output Short-Circuit Current             | V <sub>OUT</sub> = 0.5 V, V <sub>CC</sub> = Max (Note 3)                                                                                    |     | -30 | -160 | mA   |

| Icc                 | Supply Current (Typical)                 | V <sub>CC</sub> = 5V, T <sub>A</sub> = 25°C, f = 25 MHz<br>(Note 4)                                                                         |     | 120 |      | mA   |

- 1. These are absolute values with respect to device ground and all overshoots due to system or tester noise are included.

- 2. I/O pin leakage is the worst case of I<sub>IL</sub> and I<sub>OZL</sub> (or I<sub>IH</sub> and I<sub>OZH</sub>).

- 3. Not more than one output should be shorted at a time and duration of the short-circuit should not exceed one second. Vout = 0.5 V has been chosen to avoid test problems caused by tester ground degradation.

- 4. Measured with a 16-bit up/down counter pattern. This pattern is programmed in each PAL block and is capable of being loaded, enabled, and reset.

## **CAPACITANCE (Note 1)**

| Parameter<br>Symbol | Parameter Description | Test Conditio            | ns                                                  | Тур | Unit |

|---------------------|-----------------------|--------------------------|-----------------------------------------------------|-----|------|

| C <sub>IN</sub>     | Input Capacitance     | V <sub>IN</sub> = 2.0 V  | $V_{CC} = 5.0 \text{ V}, T_A = 25^{\circ}\text{C},$ | 6   | pF   |

| Соит                | Output Capacitance    | V <sub>OUT</sub> = 2.0 V | f = 1 MHz                                           | 8   | pF   |

## **SWITCHING CHARACTERISTICS over COMMERCIAL operating ranges (Note 2)**

| Parameter          |                               | AOTEMOTIO                                      |                                                    |                |        | -1:  |      | -1   |      | -20  |     |      |

|--------------------|-------------------------------|------------------------------------------------|----------------------------------------------------|----------------|--------|------|------|------|------|------|-----|------|

| Symbol             | Parameter I                   | Description                                    |                                                    |                |        | Min  | Max  | Min  | Max  | Min  | Max | Unit |

| t <sub>PD</sub>    | Input, I/O, or<br>(Note 3)    | r Feedback to Combi                            | nator                                              | rial Output    |        |      | 12   |      | 15   |      | 20  | ns   |

| ,                  | Setup Time                    | from Input, I/O,                               |                                                    |                | D-type | 7    |      | 10   |      | 13   |     | ns   |

| ts                 | or Feedback                   | to Clock                                       |                                                    |                | T-type | 8    |      | 11   |      | 14   |     | ns   |

| t⊢                 | Register Daf                  | egister Data Hold Time                         |                                                    |                | 0      |      | 0    |      | 0    |      | ns  |      |

| tco                | Clock to Out                  | tput (Note 3)                                  |                                                    |                |        |      | 8    |      | 10   |      | 12  | ns   |

| tw∟                | Clock                         | Clock LOW                                      |                                                    |                | 6      |      | 6    |      | 8    |      | ns  |      |

| twн                | Width                         |                                                |                                                    |                | HIGH   | 6    |      | 6    |      | 8    |     | ns   |

|                    |                               | External Foodbook 4/                           |                                                    | ۱ <b>۱</b>     | D-type | 66.7 |      | 50   |      | 40   |     | MHz  |

|                    | Maximum                       | External Feedback                              | 1/(1                                               | ts + tco)      | T-type | 62.5 |      | 47.6 |      | 38.5 |     | MHz  |

| $f_{MAX}$          | Frequency                     |                                                |                                                    |                | D-type | 83.3 |      | 66.6 |      | 50   |     | MHz  |

|                    | (Note 1)                      | Internal Feedback (                            | fcnt)                                              |                | T-type | 76.9 |      | 62.5 |      | 47.6 |     | MHz  |

|                    |                               | No Feedback                                    | No Feedback 1/(t <sub>WL</sub> + t <sub>WH</sub> ) |                | 83.3   |      | 83.3 |      | 62.5 |      | MHz |      |

| tsL                | Setup Time                    | p Time from Input, I/O, or Feedback to Gate    |                                                    |                | 7      |      | 10   |      | 13   |      | ns  |      |

| t <sub>HL</sub>    |                               | Latch Data Hold Time                           |                                                    |                | 0      |      | 0    |      | 0    |      | ns  |      |

| t <sub>GO</sub>    | Gate to Outp                  | out (Note 3)                                   |                                                    |                |        |      | 10   |      | 11   |      | 12  | ns   |

| tgwL               | Gate Width I                  | LOW                                            |                                                    |                |        | 6    |      | 6    |      | 8    |     | ns   |

| t <sub>PDL</sub>   | Input, I/O, or                | r Feedback to Output                           | Thro                                               | ough           |        |      |      |      |      |      |     |      |

|                    | Transparent                   | Input or Output Late                           | h                                                  |                |        |      | 14   |      | 17   |      | 22  | ns   |

| tsir               | Input Regist                  | er Setup Time                                  |                                                    |                |        | 2    |      | 2    |      | 2    |     | ns   |

| thir               | Input Regist                  | er Hold Time                                   |                                                    |                |        | 2    |      | 2.5  |      | 3    |     | ns   |

| tico               | Input Regist                  | er Clock to Combinat                           | torial                                             | Output         |        |      | 15   |      | 18   |      | 23  | ns   |

| tics               | Input Regist                  | er Clock to Output Re                          | egiste                                             | er Setup       | D-type | 12   |      | 15   |      | 20   |     | ns   |

|                    |                               |                                                |                                                    |                | T-type | 13   |      | 16   |      | 21   |     | ns   |

| twicl              | Input Regist                  | er                                             |                                                    |                | LOW    | 6    |      | 6    |      | 8    |     | ns   |

| twich              | Clock Width                   |                                                |                                                    |                | HIGH   | 6    |      | 6    |      | 8    |     | ns   |

| f <sub>MAXIR</sub> | Maximum In                    | put Register Frequer                           | псу                                                | 1/(twicL + twi | сн)    | 83.3 |      | 83.3 |      | 62.5 |     | MHz  |

| t <sub>SIL</sub>   | Input Latch S                 | Setup Time                                     |                                                    |                |        | 2    |      | 2    |      | 2    |     | ns   |

| thiL               | Input Latch I                 | Hold Time                                      |                                                    |                |        | 2    |      | 2.5  |      | 3    |     | ns   |

| tigo               | Input Latch (                 | Gate to Combinatoria                           | ıl Out                                             | tput           |        |      | 17   |      | 20   |      | 25  | ns   |

| tigol              | Input Latch (<br>Output Latch | Input Latch Gate to Output Through Transparent |                                                    |                | 19     |      | 22   |      | 27   | ns   |     |      |

| t <sub>SLL</sub>   |                               | from Input, I/O, or Fe<br>Input Latch to Outpu |                                                    |                |        | 9    |      | 12   |      | 15   |     | ns   |

| tıgs               |                               | Gate to Output Latch                           |                                                    |                |        | 13   |      | 16   |      | 21   |     | ns   |

# **SWITCHING CHARACTERISTICS over COMMERCIAL operating ranges (Note 2) (continued)**

| Parameter         |                                                                                | -12 |     | -1  | 5   | -20 |     |      |

|-------------------|--------------------------------------------------------------------------------|-----|-----|-----|-----|-----|-----|------|

| Symbol            | Parameter Description                                                          | Min | Max | Min | Max | Min | Max | Unit |

| twigL             | Input Latch Gate Width LOW                                                     | 6   |     | 6   |     | 8   |     | ns   |

| t <sub>PDLL</sub> | Input, I/O, or Feedback to Output Through Transparent Input and Output Latches |     | 16  |     | 19  |     | 24  | ns   |

| t <sub>AR</sub>   | Asynchronous Reset to Registered or Latched Output                             |     | 16  |     | 20  |     | 25  | ns   |

| t <sub>ARW</sub>  | Asynchronous Reset Width (Note 1)                                              |     |     | 15  |     | 20  |     | ns   |

| tarr              | Asynchronous Reset Recovery Time (Note 1)                                      | 8   |     | 10  |     | 15  |     | ns   |

| t <sub>AP</sub>   | Asynchronous Preset to Registered or Latched Output                            |     | 16  |     | 20  |     | 25  | ns   |

| t <sub>APW</sub>  | Asynchronous Preset Width (Note 1)                                             | 12  |     | 15  |     | 20  |     | ns   |

| t <sub>APR</sub>  | Asynchronous Preset Recovery Time (Note 1)                                     |     |     | 10  |     | 15  |     | ns   |

| t <sub>EA</sub>   | Input, I/O, or Feedback to Output Enable (Note 3)                              |     | 12  |     | 15  |     | 20  | ns   |

| t <sub>ER</sub>   | Input, I/O, or Feedback to Output Disable (Note 3)                             |     | 12  |     | 15  |     | 20  | ns   |

- 1. These parameters are not 100% tested, but are evaluated at initial characterization and at any time the design is modified where capacitance may be affected.

- 2. See Switching Test Circuit, for test conditions.

- 3. Parameters measured with 16 outputs switching.

### **ABSOLUTE MAXIMUM RATINGS**

| Storage Temperature65°C to +150°C                                                                  |

|----------------------------------------------------------------------------------------------------|

| Ambient Temperature With Power Applied55°C to +125°C                                               |

| Supply Voltage with Respect to Ground0.5 V to +7.0 V                                               |

| DC Input Voltage $-0.5~\text{V}$ to Vcc+ 0.5 V                                                     |

| DC Output or I/O                                                                                   |

| Pin Voltage $-0.5$ V to V <sub>CC</sub> + $0.5$ V                                                  |

| Static Discharge Voltage 2001 V                                                                    |

| Latchup Current $ (T_A = -40^{\circ} \text{C to } +85^{\circ} \text{C}) \ \dots \ 200 \text{ mA} $ |

Stresses above those listed under Absolute Maximum Ratings may cause permanent device failure. Functionality at or above these limits is not implied. Exposure to Absolute Maximum Ratings for extended periods may affect device reliability. Programming conditions may differ.

### **INDUSTRIAL OPERATING RANGES**

Ambient Temperature ( $T_A$ )

Operating in Free Air ..... -40°C to +85°C

Supply Voltage ( $V_{CC}$ )

with Respect to Ground ..... +4.5 V to +5.5 V

Operating ranges define those limits between which the functionality of the device is guaranteed.

# DC CHARACTERISTICS over INDUSTRIAL operating ranges unless otherwise specified

| Parameter        |                                          |                                                                                                                   |     |     |      |        |

|------------------|------------------------------------------|-------------------------------------------------------------------------------------------------------------------|-----|-----|------|--------|

| Symbol           | Parameter Description                    | Test Conditions                                                                                                   | Min | Тур | Max  | Unit   |

| Vон              | Output HIGH Voltage                      | $I_{OH}$ = -3.2 mA, $V_{CC}$ = Min $V_{IN}$ = $V_{IH}$ or $V_{IL}$                                                | 2.4 |     |      | V      |

| Vol              | Output LOW Voltage                       | $I_{OL} = 16 \text{ mA}, V_{CC} = \text{Min}$<br>$V_{IN} = V_{IH} \text{or } V_{IL}$                              |     |     | 0.5  | \<br>\ |

| V <sub>IH</sub>  | Input HIGH Voltage                       | Guaranteed Input Logical HIGH<br>Voltage for all Inputs (Note 1)                                                  | 2.0 |     |      | V      |

| V <sub>IL</sub>  | Input LOW Voltage                        | Guaranteed Input Logical LOW<br>Voltage for all Inputs (Note 1)                                                   |     |     | 0.8  | V      |

| I <sub>IH</sub>  | Input HIGH Leakage Current               | V <sub>IN</sub> = 5.25 V, V <sub>CC</sub> = Max (Note 2)                                                          |     |     | 10   | μΑ     |

| I₁∟              | Input LOW Leakage Current                | V <sub>IN</sub> = 0 V, V <sub>CC</sub> = Max (Note 2)                                                             |     |     | -10  | μΑ     |

| lozh             | Off-State Output Leakage<br>Current HIGH | V <sub>OUT</sub> = 5.25 V, V <sub>CC</sub> = Max<br>V <sub>IN</sub> = V <sub>IH</sub> or V <sub>IL</sub> (Note 2) |     |     | 10   | μА     |

| l <sub>OZL</sub> | Off-State Output Leakage<br>Current LOW  | V <sub>OUT</sub> = 0 V, V <sub>CC</sub> = Max<br>V <sub>IN</sub> = V <sub>IH</sub> or V <sub>IL</sub> (Note 2)    |     |     | -10  | μА     |

| I <sub>SC</sub>  | Output Short-Circuit Current             | V <sub>OUT</sub> = 0.5 V, V <sub>CC</sub> = Max (Note 3)                                                          | -30 |     | -160 | mA     |

| Icc              | Supply Current (Typical)                 | $V_{CC} = 5 \text{ V}, T_A = 25^{\circ}\text{C}, f = 25 \text{ MHz (Note 4)}$                                     |     | 120 |      | mA     |