#### **General Description**

The MAX14515 high-voltage liquid lens driver features a high-voltage differential output controlled through an I<sup>2</sup>C interface. The MAX14515 uses a charge-pump-based boost converter and integrated H-bridge to provide a compact lens driver solution with minimal external components to achieve a small overall footprint suitable for small space constraints inside camera modules.

The MAX14515 features an 8-bit monotonic DAC with a single differential high-voltage output controlled by a 2-wire I<sup>2</sup>C interface to set the amplitude. The high-voltage outputs are capable of delivering up to 42VRMS (min) into a 220pF liquid lens load at 1.0kHz (min).

The MAX14515 also features two power-saving modes (shutdown mode and sleep mode) to minimize power consumption when the device is inactive. Shutdown mode places the device in a low-power state that resets all registers and disables the I<sup>2</sup>C interface to reduce current below 500nA (max). In sleep mode, the power-on reset circuit remains active. If no activity is detected on the I<sup>2</sup>C interface, current consumption is less than 3µA.

The MAX14515 operates over the +2.7V to +5.5V supply voltage range, ideal for portable applications using lithium ion battery sources. The MAX14515 is specified over the -40°C to +85°C extended temperature range and is available in a small (1mm x 2mm) 8-bump WLP package.

#### **Applications**

Autofocus Camera Modules **Barcode Readers** Webcams

#### **Features**

- ♦ Small Footprint for Placement Inside Camera **Modules**

- ♦ 47V<sub>RMS</sub> Maximum Output (C<sub>LENS</sub> = 220pF)

- ♦ I<sup>2</sup>C-Compatible Interface for Setting Output Voltage

- ♦ 8-Bit Output Voltage Resolution

- ♦ Guaranteed Monotonic Output

- ♦ ±15kV Human Body Model ESD Protection on Outputs

- ♦ Low 500nA (max) Shutdown Current

- ♦ +2.7V to +5.5V Input Voltage Range

- ♦ Space-Saving, 8-Bump WLP (1mm x 2mm) Package

### **Ordering Information**

| PART         | TEMP RANGE     | PIN-PACKAGE | TOP<br>MARK |

|--------------|----------------|-------------|-------------|

| MAX14515EWA+ | -40°C to +85°C | 8 WLP       | +AAA        |

<sup>+</sup>Denotes a lead-free/RoHS-compliant package.

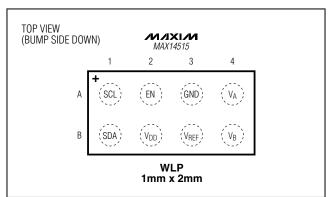

### **Pin Configuration**

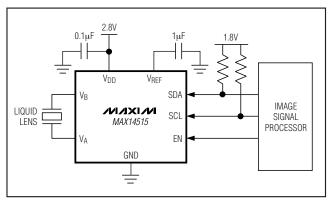

### **Typical Application Circuit**

#### **ABSOLUTE MAXIMUM RATINGS**

| (All voltages referenced to GND.)                             | Junction-to-Ambient Thermal Resistance (qJA | ) (Note 1)    |

|---------------------------------------------------------------|---------------------------------------------|---------------|

| V <sub>DD</sub> 0.3V to +6.0V                                 | 8-Bump WLP                                  | 192°C/W       |

| V <sub>A.</sub> V <sub>B</sub> 0.3V to +52V                   | Operating Temperature Range                 | 40°C to +85°C |

| V <sub>REF</sub> MAX (-0.3V, V <sub>DD</sub> - 0.3V) to +6.0V | Junction Temperature                        | +150°C        |

| SDA, SCL, EN0.3V to +6.0V                                     | Storage Temperature Range                   |               |

| Continuous Power Dissipation ( $T_A = +70^{\circ}C$ ):        | Lead Temperature (soldering, 10s)           | +300°C        |

| 8-Bump WLP (derate 5.2mW/°C above +70°C)416mW                 |                                             |               |

**Note 1:** Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-layer board. For detailed information on package thermal considerations, refer to <a href="https://www.maxim-ic.com/thermal-tutorial">www.maxim-ic.com/thermal-tutorial</a>.

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **ELECTRICAL CHARACTERISTICS**

$(V_{DD} = +2.7 \text{V to } +5.5 \text{V}, C_{VDD} = 0.1 \mu\text{F}, C_{REF} = 1 \mu\text{F}, C_{LENS} = 220 \mu\text{F}, T_{A} = -40 ^{\circ}\text{C}$  to  $+85 ^{\circ}\text{C}$ , unless otherwise noted. Typical values are at  $V_{DD} = +2.8 \text{V}$  and  $T_{A} = +25 ^{\circ}\text{C}$ .) (Note 2)

| PARAMETER                      | SYMBOL              | CONDITIONS                        |                                     | MIN | TYP  | MAX | UNITS |

|--------------------------------|---------------------|-----------------------------------|-------------------------------------|-----|------|-----|-------|

| Input Voltage                  | $V_{DD}$            |                                   |                                     | 2.7 |      | 5.5 | V     |

| Input Supply Current           | I <sub>DD</sub>     | Peak output v                     | oltage register (VP) = 0xFF         |     | 9    |     | mA    |

| Reference Output Voltage       | V <sub>REF</sub>    |                                   |                                     |     |      | 5.5 | V     |

| Shutdown Supply Current        | ISHDN               | EN = GND                          |                                     |     | 1    | 500 | nA    |

| Class Consider Comment         | 1                   | $\overline{SM} = 0,$<br>SDA = SCL | $V_{EN} = 1.8V, V_{DD} = 4.2V$      |     | 8    |     | μΑ    |

| Sleep Supply Current           | ISLEEP              |                                   | $V_{EN} = V_{DD}$ , $V_{DD} = 2.8V$ |     | 1.2  | 3   |       |

| POR Threshold                  | V <sub>TH_POR</sub> |                                   | <u> </u>                            |     |      | 2.6 | V     |

| HIGH-VOLTAGE OUTPUTS (VA, V    | / <sub>B</sub> )    |                                   |                                     |     |      |     |       |

| Dools Outrout Voltage (Note 2) | \/                  | VP = 0x01                         |                                     |     |      | 10  | V     |

| Peak Output Voltage (Note 3)   | VPEAK               | VP = 0xFF                         |                                     |     |      | 52  | 1 V   |

| O L L DMO V II                 | V                   | VP = 0x01                         |                                     | 10  |      | V   |       |

| Output RMS Voltage             | V <sub>RMS</sub>    | VP = 0xFF                         |                                     | 42  |      | 47  | - V   |

| Output Voltage Ripple          | V <sub>RPL</sub>    | C <sub>LENS</sub> = 120p          | oF                                  |     | ±250 |     | mV    |

| Pulldown Strength              | RL <sub>PD</sub>    | $\overline{SM} = 0$               |                                     |     |      | 2   | kΩ    |

| Output Switching Frequency     | fLENS               |                                   |                                     | 1   | 1.1  | 1.2 | kHz   |

| CONTROL INPUTS (SDA, SCL, E    | N)                  |                                   |                                     |     |      |     |       |

| Input Logic-High Voltage       | VIH                 |                                   |                                     | 1.5 |      |     | V     |

| Input Logic-Low Voltage        | VIL                 |                                   |                                     |     |      | 0.5 | V     |

| Output Logic-Low Voltage       | V <sub>OL</sub>     | I <sub>SINK</sub> = 3mA           |                                     |     |      | 0.4 | V     |

|                                | I.u                 | EN = V <sub>CC</sub>              |                                     |     | 0.01 | 6   |       |

| Input Low Leakage Current      | IIL                 | EN = GND                          |                                     |     | 0.01 | 0.5 | μΑ    |

| Input High Leakage Current     | lін                 |                                   |                                     |     | 0.01 | 2.5 | μΑ    |

| Input Capacitance              | CIN                 |                                   |                                     |     | 10   |     | рF    |

### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{DD}=+2.7V~to~+5.5V,~C_{VDD}=0.1\mu\text{F},~C_{REF}=1\mu\text{F},~C_{LENS}=220\text{pF},~T_{A}=-40^{\circ}\text{C}~to~+85^{\circ}\text{C},~unless~otherwise~noted.}$  Typical values are at  $V_{DD}=+2.8V~and~T_{A}=+25^{\circ}\text{C}.)$  (Note 2)

| PARAMETER                                      | SYMBOL          | CONDITIONS                                                                                          | MIN | TYP   | MAX | UNITS |

|------------------------------------------------|-----------------|-----------------------------------------------------------------------------------------------------|-----|-------|-----|-------|

| OUTPUT-VOLTAGE STATIC PERFOR                   | MANCE (V        | A, V <sub>B</sub> )                                                                                 |     |       |     |       |

| Resolution                                     | N               |                                                                                                     |     | 8     |     | Bits  |

| Least Significant Bit                          | LSB             | (Note 4)                                                                                            |     | 157.5 |     | mV    |

| Integral Nonlinearity                          | INL             |                                                                                                     | -4  |       | +4  | LSB   |

| Differential Nonlinearity                      | DNL             | (Note 5)                                                                                            | -1  |       | +1  | LSB   |

| OUTPUT VOLTAGE DYNAMIC PERFO                   | ORMANCE (       | (V <sub>A</sub> , V <sub>B</sub> )                                                                  |     |       |     |       |

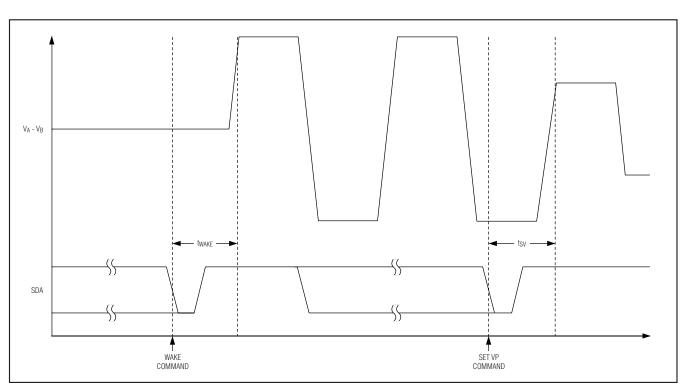

| Peak-Output Voltage Settling Time              | tsv             | VP = any value to any other value transition; time to settle within 7 LSBs of final value, Figure 1 |     |       | 1   | ms    |

| Output Slew Rate                               | SR <sub>V</sub> | Peak output voltage register = FFh                                                                  |     |       | 5   | V/µs  |

| Wake-Up Time                                   | twake           | Time to settle within 7 LSBs of peak value, Figure 1                                                |     |       | 2   | ms    |

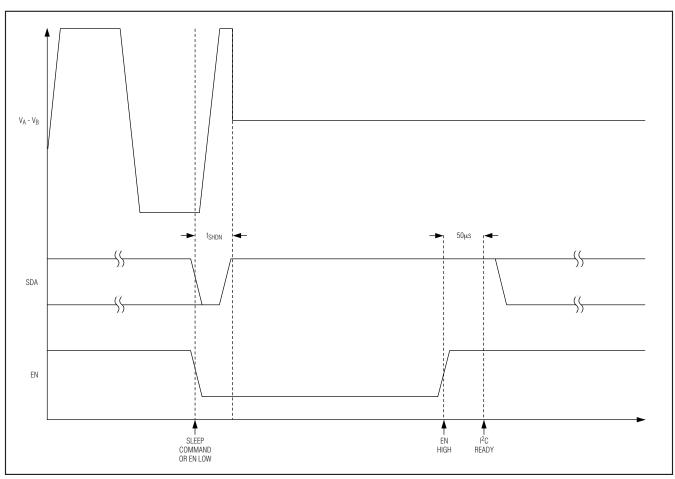

| Shutdown Time                                  | tshdn           | Figure 2                                                                                            |     | 100   |     | μs    |

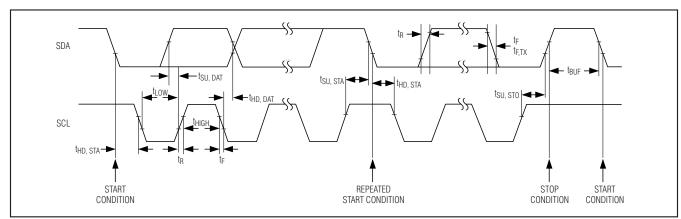

| I <sup>2</sup> C INTERFACE                     |                 |                                                                                                     |     |       |     |       |

| Serial-Clock Frequency                         | fscl            |                                                                                                     |     |       | 400 | kHz   |

| Bus Free Time Between START and STOP Condition | tBUF            |                                                                                                     | 1.3 |       |     | μs    |

| Hold Time for Repeated START Condition         | thd:STA         |                                                                                                     | 0.6 |       |     | μs    |

| Low Period for SCL Clock                       | tLOW            |                                                                                                     | 1.3 |       |     | μs    |

| High Period for SCL Clock                      | tHIGH           |                                                                                                     | 0.6 |       |     | μs    |

| Setup Time for Repeated START Condition        | tsu:sta         |                                                                                                     | 0.6 |       |     | μs    |

| Data Hold Time                                 | thd:dat         |                                                                                                     | 0   |       | 0.9 | μs    |

| Data Setup Time                                | tsu:dat         |                                                                                                     | 100 |       |     | ns    |

| Rise Time of Both SDA and SCL Signals          | t <sub>r</sub>  |                                                                                                     |     |       | 300 | ns    |

| Fall Time of Both SDA and SCL Signals          | t <sub>f</sub>  |                                                                                                     |     |       | 300 | ns    |

| Setup Time for STOP Condition                  | tsu:sto         |                                                                                                     | 0.6 |       |     | μs    |

| Capacitive Load for Each Bus Line              | Cb              |                                                                                                     |     |       | 400 | рF    |

| ESD PROTECTION                                 |                 |                                                                                                     |     |       |     |       |

| V <sub>A.</sub> V <sub>B</sub>                 |                 | Human Body Model                                                                                    | ±15 |       |     | kV    |

| ,                                              |                 | IEC 61000-4-2                                                                                       |     | ±4    |     |       |

| All Other Pins                                 |                 | Human Body Model                                                                                    |     | ±2    |     | kV    |

Note 2: All devices are tested at  $T_A = +25$  °C. All temperature limits are guaranteed by design.

**Note 3:**  $V_{PEAK}$  is the average peak output voltage of  $\dot{V}_A$  or  $V_B$ .

**Note 4:**  $V_{PEAK} = 9.5V + (N-1) \times 0.1575$ , (accuracy  $\pm 3\%$ ).

Note 5: Guaranteed monotonic.

### \_Timing Diagrams

Figure 1. Wake-Up and Peak Output Voltage Settling Timing Diagram

## Timing Diagrams (continued)

Figure 2. Shutdown/Sleep Mode Timing Diagram

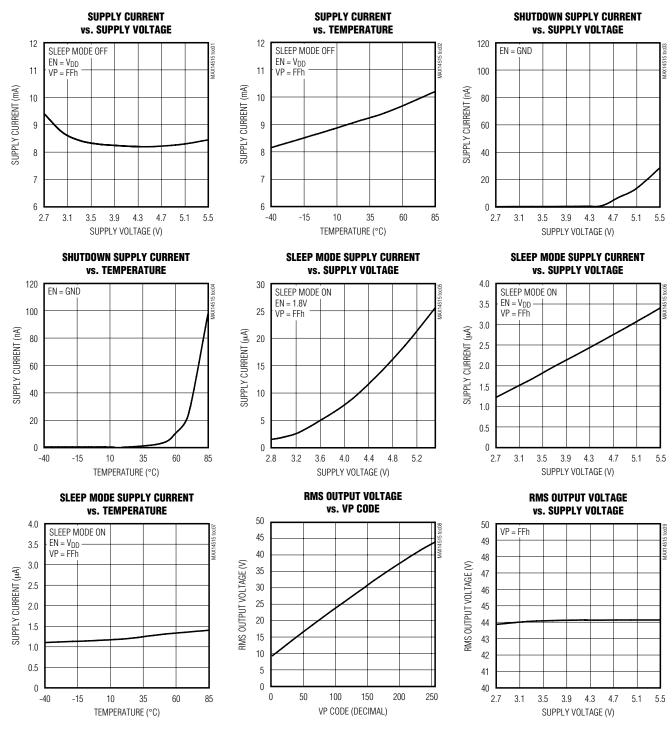

#### Typical Operating Characteristics

$(V_{DD} = +2.8V, T_A = +25$ °C,  $C_{LENS} = 220$ pF, unless otherwise noted.)

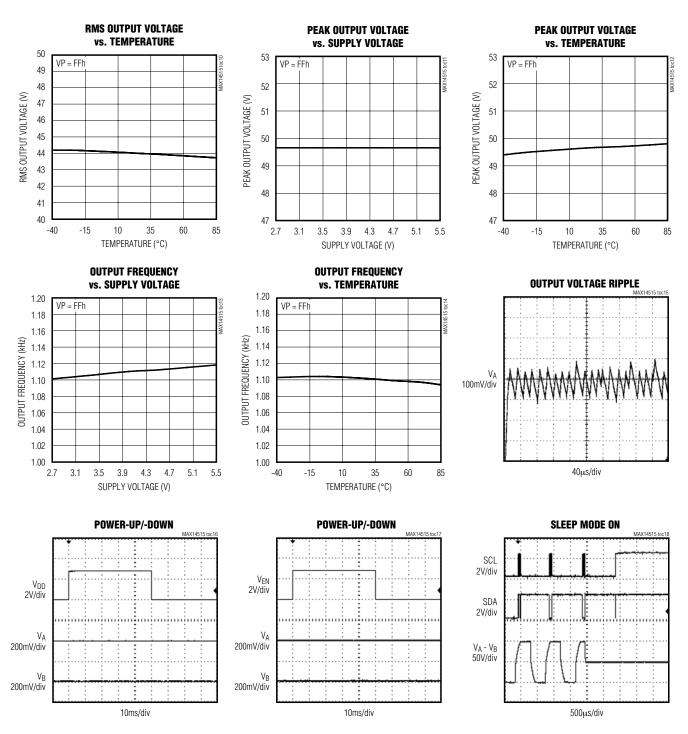

### Typical Operating Characteristics (continued)

$(V_{DD} = +2.8V, T_A = +25$ °C,  $C_{LENS} = 220$ pF, unless otherwise noted.)

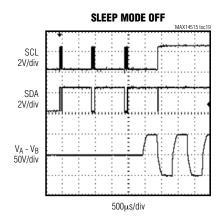

### Typical Operating Characteristics (continued)

$(V_{DD} = +2.8V, T_A = +25^{\circ}C, C_{LENS} = 220pF, unless otherwise noted.)$

### **Pin Description**

| PIN | NAME             | FUNCTION                                                                                                                                                                                                        |

|-----|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A1  | SCL              | I <sup>2</sup> C Open-Drain Serial Clock Input                                                                                                                                                                  |

| В1  | SDA              | I <sup>2</sup> C Open-Drain Serial Data Input/Output                                                                                                                                                            |

| A2  | EN               | Enable Input. Drive EN high for normal operation. Drive EN low to enter shutdown mode.                                                                                                                          |

| B2  | $V_{DD}$         | Input Supply Voltage. Bypass VDD to GND with a 0.1µF capacitor as close to the device as possible.                                                                                                              |

| А3  | GND              | Ground                                                                                                                                                                                                          |

| В3  | V <sub>REF</sub> | Reference Voltage. Connect a 1µF ceramic capacitor from V <sub>REF</sub> to GND as close to the device as possible. V <sub>REF</sub> is nominally +5V. Do not use V <sub>REF</sub> to drive external circuitry. |

| A4  | VA               | High-Voltage Output. Connect to terminal 1 of liquid lens.                                                                                                                                                      |

| В4  | V <sub>B</sub>   | High-Voltage Output. Connect to terminal 2 of liquid lens.                                                                                                                                                      |

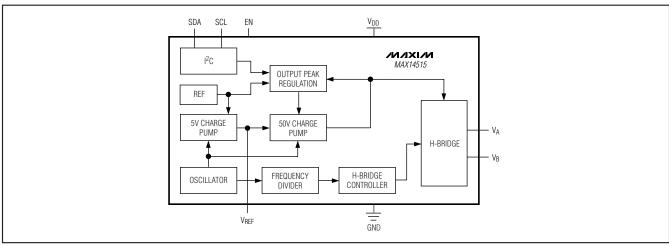

### **Functional Diagram**

8 \_\_\_\_\_\_ *NIXI/*M

### **Detailed Description**

The MAX14515 high-voltage liquid lens driver utilizes a charge-pump-based boost converter and integrated H-bridge to provide a compact lens driver solution with minimal external components. This device features an 8-bit monotonic DAC controlled by a simple 2-wire I<sup>2</sup>C interface to set the peak amplitude of the high-voltage output.

#### **Power-On Reset**

When the MAX14515 initially powers up, all the registers are cleared and the device is in sleep mode.

#### High-Voltage Outputs (VA, VB)

Connect a liquid lens in between the high-voltage outputs ( $V_A$ ,  $V_B$ ) of the MAX14515. The peak output voltage of  $V_A$  and  $V_B$  is controlled by the value set in the high-voltage output register (VP). (See *Register Definition*). The internal H-bridge that drives  $V_A$  and  $V_B$  switches at 1.1kHz (typ).

#### Reference Output (VREF)

VREF is the internal 5V charge-pump reference voltage of the MAX14515. Connect a 1 $\mu$ F ceramic capacitor from VREF to GND. VREF is not intended to drive external circuitry.

#### Shutdown Mode (EN)

The MAX14515 features a shutdown mode that reduces supply current to less than 500nA (max). In shutdown, all registers are in a reset state, and the I<sup>2</sup>C interface is disabled. Drive EN low to place the device in shutdown mode. Drive EN high for normal operation. Driving EN rail-to-rail minimizes power consumption.

#### Sleep Mode

When EN is high and the sleep mode bit (SM) in the power mode register (see *Register Definition*) is reset, the device is in sleep mode. During sleep mode, only the power-on reset circuit remains active. If no activity is detected on the  $I^2C$  interface, current consumption is less than  $3\mu A$ .

### I<sup>2</sup>C Serial Interface

#### Serial Addressing

The MAX14515 operates as a slave device that sends and receives data through an I<sup>2</sup>C-compatible 2-wire interface. The interface uses a serial-data line (SDA) and a serial-clock line (SCL) to achieve bidirectional communication between master(s) and slave(s). A master (typically a microcontroller) initiates all data transfers to and from the MAX14515, and generates the SCL clock that synchronizes the data transfer. The SDA line operates as both an input and an open-drain output. A pullup resistor is required on SDA. The SCL line

#### **Register Definition**

|              | DEVICE A                                                    | ADDRESS |                   | WRITE                                                                                                                                                                               | 0xEC                          |  |

|--------------|-------------------------------------------------------------|---------|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|--|

|              | DEVICE                                                      | IDDNESS |                   | READ                                                                                                                                                                                | 0xED                          |  |

| FIELD NAME   | READ WRITE                                                  | BITS    | POWER-ON<br>RESET | DESCRIPTION                                                                                                                                                                         |                               |  |

| POWER MODE   | (I <sup>2</sup> C ADDRESS =                                 | 0x00)   |                   |                                                                                                                                                                                     |                               |  |

| RSVD         | Read/Write                                                  | [7:1]   | 0000 000          | Reserved. All bits must be set to                                                                                                                                                   | o 0.                          |  |

| SM           | Read/Write                                                  | 0       | 0                 | Sleep Mode Bit 0 = Sleep Mode 1 = Normal Operation  All the registers keep the same a POR occurs.                                                                                   | values as before sleep unless |  |

| HIGH-VOLTAGI | HIGH-VOLTAGE OUTPUT LEVEL (I <sup>2</sup> C ADDRESS = 0x01) |         |                   |                                                                                                                                                                                     |                               |  |

| VP(7:0)      | Read/Write                                                  | [7:0]   | 0000 0000         | Code 0x00 = 0VPEAK Code 0x01 = 10VPEAK  Code 0xFF = 49.5VPEAK, linear scale.  VOUT(PEAK) = 9.5VPEAK + 0.1575VPEAK × (N - 1) where N = Code 0x01 to 0xFF in decimal. Accuracy (±3%). |                               |  |

Figure 3. I<sup>2</sup>C Interface Timing Details

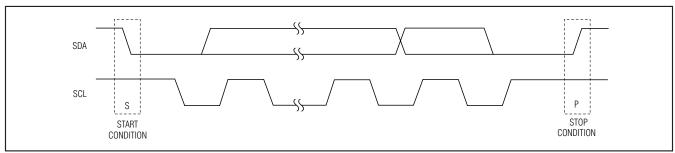

Figure 4. START and STOP Conditions

operates only as an input. A pullup resistor is required on SCL if there are multiple masters on the 2-wire interface, or if the master in a single-master system has an open-drain SCL output. Each transmission consists of a START condition sent by a master, followed by the MAX14515's 7-bit slave address plus R/W bit, a register address byte, 1 or more data bytes, and finally a STOP condition.

#### START and STOP Conditions

Both SCL and SDA remain high when the interface is not busy. A master signals the beginning of a transmission with a START (S) condition by transitioning SDA from high to low while SCL is high (Figure 4). When the master has finished communicating with the slave, it issues a STOP (P) condition by transitioning SDA from low to high while SCL is high. The bus is then free for another transmission.

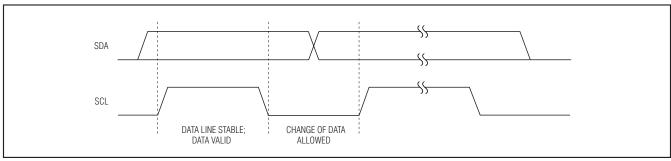

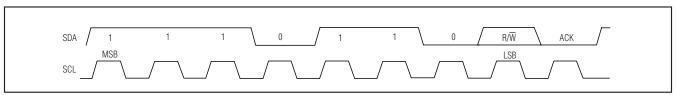

#### Bit Transfer

One data bit is transferred during each clock pulse (Figure 5). The data on SDA must remain stable while SCL is high.

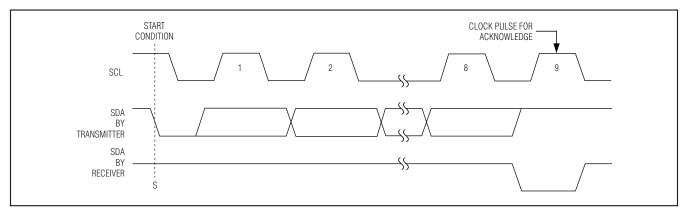

#### Acknowledge

The acknowledge bit is a clocked 9th bit (Figure 6), which the recipient uses to handshake receipt of each byte of data. Thus, each byte transferred effectively requires 9 bits. The master generates the 9th clock pulse, and the recipient pulls down SDA during the acknowledge clock pulse. The SDA line is stable low during the high period of the clock pulse. When the master is transmitting to the MAX14515, it generates the acknowledge bit because the MAX14515 is the recipient. When the MAX14515 is transmitting to the master, the master generates the acknowledge bit because the master is the recipient.

\_\_\_\_ /N/XI/N

Figure 5. Bit Transfer

Figure 6. Acknowledge

#### Slave Address

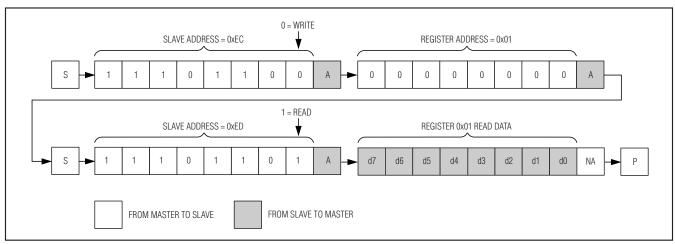

The MAX14515 has a 7-bit long slave address. The bit following a 7-bit slave address is the  $R/\overline{W}$  bit, which is low for a write command and high for a read command. The slave address is 0xEC for write commands and 0xED for read commands (Figure 7).

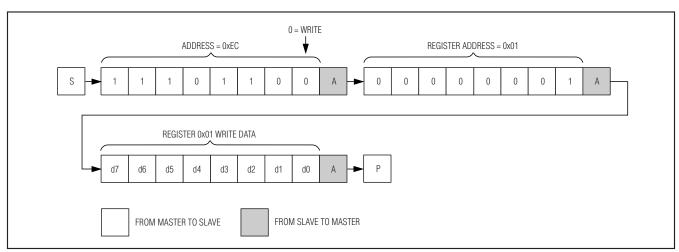

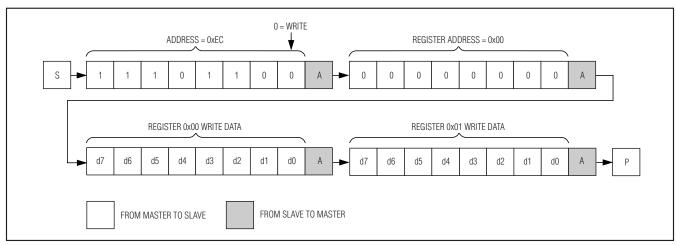

#### Format for Writing

A write to the MAX14515 comprises the transmission of the slave address with the R/W bit set to zero, followed by at least 1 byte of information. The first byte of information is the register address or command byte. The register address determines which register of the MAX14515 is to be written by the next byte, if received. If a STOP condition is detected after the register address is received, then the MAX14515 takes no further action beyond storing the register address (Figure 8). Any bytes received after the register address are data bytes. The first data byte goes into the register selected by the register address and subsequent data

bytes go into subsequent registers (Figure 9). If multiple data bytes are transmitted before a STOP condition, these bytes are stored in subsequent registers because the register address autoincrements.

#### Format for Reading

The MAX14515 is read using the internally stored register address as an address pointer, the same way the stored register address is used as an address pointer for a write. The pointer autoincrements after each data byte is read using the same rules as for a write. Thus, a read is initiated by first configuring the register address by performing a write (Figure 10). The master can now read consecutive bytes from the MAX14515, with the first data byte being read from the register address pointed by the previously written register address. Once the master sounds a NACK, the MAX14515 stops sending valid data.

Figure 7. Slave Address

Figure 8. Format for I<sup>2</sup>C Write

Figure 9. Format for Writing to Multiple Registers

Figure 10. Format for Reading

#### **Applications Information**

#### Layout

Circuit board layout can significantly affect the performance of the MAX14515. Ensure that bypass capacitors are as close to the device as possible. Keep PCB traces as short as possible and minimize trace inductances to VDD. Use large ground planes where possible.

#### **ESD Protection**

ESD performance depends on a number of conditions. The MAX14515 is rated for  $\pm 15 \text{kV}$  (Human Body Model) and  $\pm 4 \text{kV}$  (IEC 61000-4-2 Contact) typical ESD resistance on VA and VB. All other pins are rated for  $\pm 2 \text{kV}$  (HBM) typical ESD resistance.

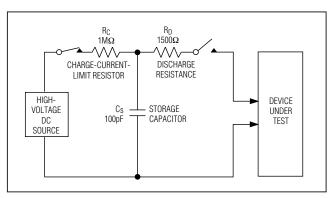

#### **Human Body Model**

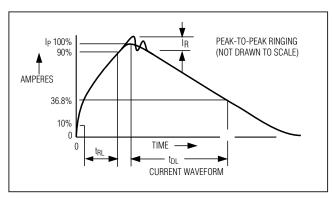

Figure 11 shows the Human Body Model, and Figure 12 shows the current waveform it generates when discharged into a low impedance. This model consists of a 100pF capacitor charged to the ESD voltage of interest that is then discharged into the device through a  $1.5 \mathrm{k}\Omega$  resistor.

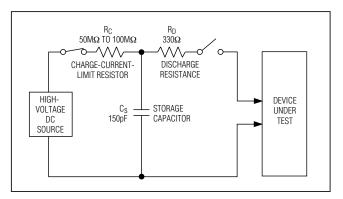

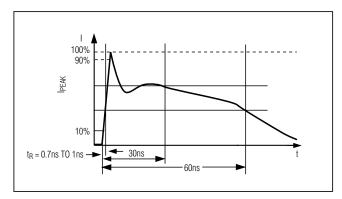

#### IEC 61000-4-2

The main difference between tests done using the Human Body Model and IEC 61000-4-2 is higher peak current in IEC 61000-4-2. Because series resistance is lower in the IEC 61000-4-2 ESD test model (Figure 13), the ESD-withstand voltage measured to this standard is generally lower than that measured using the Human Body Model. Figure 14 shows the current waveform for the IEC 61000-4-2 Level 4 ESD Contact Discharge test.

#### **Chip Information**

PROCESS: CMOS

Figure 11. Human Body ESD Test Model

Figure 12. Human Body Current Waveform

Figure 13. IEC 61000-4-2 ESD Test Model

Figure 14. IEC 61000-4-2 ESD Generator Current Waveform

### **Package Information**

For the latest package outline information and land patterns, go to <a href="www.maxim-ic.com/packages">www.maxim-ic.com/packages</a>.

| PACKAGE TYPE | PACKAGE CODE | DOCUMENT NO.   |

|--------------|--------------|----------------|

| 8 WLP        | W81A2-1      | <u>21-0210</u> |

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.

## Maxim Integrated:

MAX14515EWA+T MAX14515AEWA+T