## **IO-Link Device Transceiver**

### **General Description**

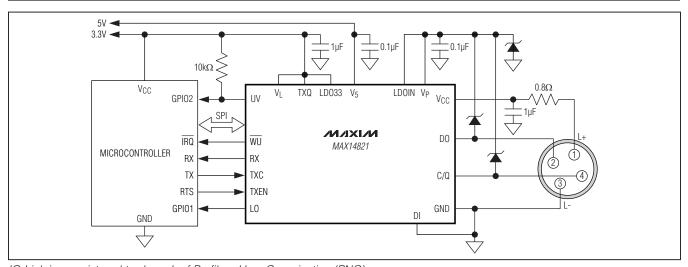

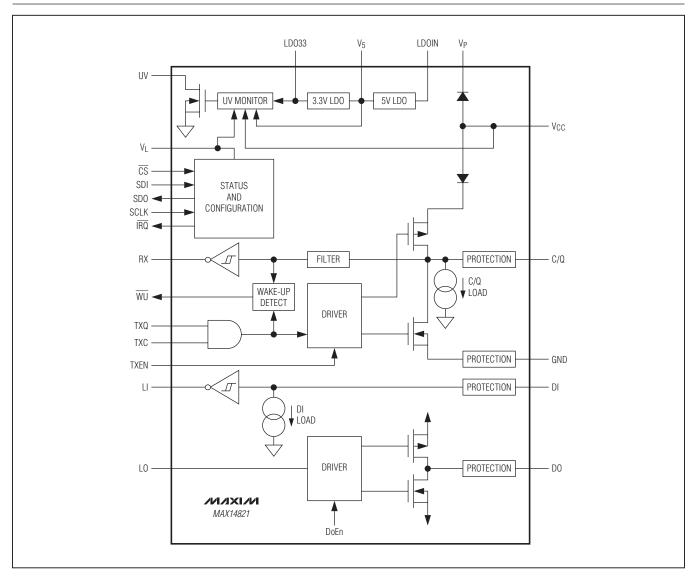

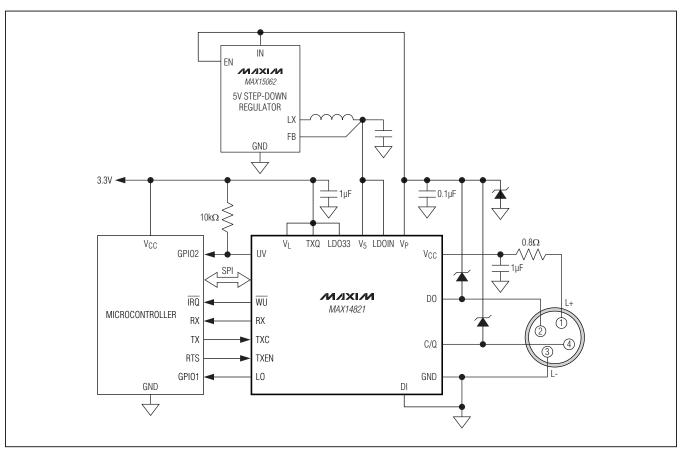

The MAX14821 transceiver is suitable for IO-Link® devices and 24V binary sensors/actuators. All specified IO-Link data rates are supported. In IO-Link applications, the transceiver acts as the physical layer interface to a microcontroller running the data-link layer protocol. Additional 24V digital inputs and outputs are provided. Two internal linear regulators generate common sensor and actuator power requirements: 5V and 3.3V.

On-board C/Q and DO drivers are independently configurable for push-pull, high-side (PNP), or low-side (NPN) operation. The device detects the IO-Link C/Q wake-up condition and generates a wake-up signal on the activelow WU output. The C/Q and DI inputs have selectable current loads for use in actuators.

An SPI™ interface allows configuration and monitoring of the device. Extensive alarm conditions are detected and communicated through the IRQ output and the SPI interface. The device features reverse-polarity, short-circuit, and thermal protection. All power lines are monitored for undervoltage conditions.

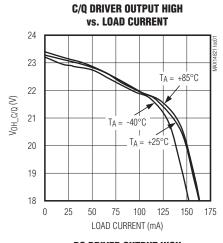

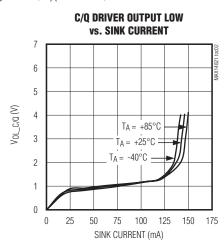

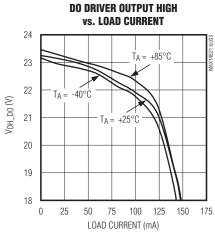

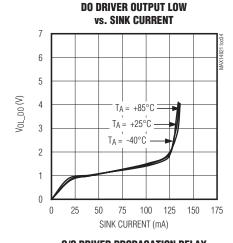

The C/Q and DO drivers are specified for sourcing/sinking up to 100mA.

The device is available in a 2.5mm x 2.5mm, 25-pin WLP and a 4mm x 4mm, 24-pin TQFN package. Both are specified over the extended -40°C to +85°C temperature range.

### **Applications**

**IO-Link Sensors** Industrial Sensors and Actuators IO-I ink Actuators

#### **Features**

- ♦ IO-Link Specification v.1.0 and v.1.1 Physical Layer-Compliant

- ♦ Supports COM1, COM2, and COM3 Data Rates

- ♦ IO-Link Device Wake-Up Detection

- ♦ Push-Pull, High-Side, or Low-Side Outputs

- ♦ 100mA Specified C/Q Output Drive

- ♦ Auxiliary 24V, 100mA Digital Output

- ♦ Auxiliary 24V Digital Input

- ♦ Optional 6mA/7mA Current Loads at Both 24V Inputs

- ♦ 5V and 3.3V Linear Regulators

- ♦ Reverse-Polarity Protected 24V Supply Output

- ♦ EMI Emission Control Through Slew-Controlled Driver

- ♦ SPI Interface for Configuration and Monitoring

- ♦ 2.5V to 5V Logic Interface Levels

- ♦ Reverse-Polarity and Short-Circuit Protection on All 24V Inputs/Outputs

- ♦ High-Temperature Warning and Thermal Shutdown

- **♦** Extensive Fault Monitoring and Reporting

- ♦ -40°C to +85°C Operating Temperature Range

- ♦ 2.5mm x 2.5mm WLP and 4mm x 4mm TQFN **Packages**

Ordering Information appears at end of data sheet.

### Typical Operating Circuit

IO-Link is a registered trademark of Profibus User Organization (PNO). SPI is a trademark of Motorola, Inc.

For related parts and recommended products to use with this part, refer to: www.maxim-ic.com/MAX14821.related

MIXIM

Maxim Integrated Products 1

# **IO-Link Device Transceiver**

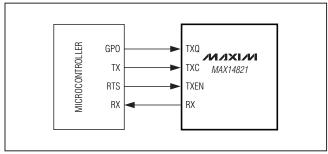

## **Functional Diagram**

#### **ABSOLUTE MAXIMUM RATINGS**

| (All voltages referenced to GND, unless otherwise noted.)                             | Logic Outputs                                                                        |

|---------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|

| V <sub>CC</sub> 40V to +40V                                                           | $\overline{RX}$ , $\overline{WU}$ , LI, SDO, $\overline{IRQ}$ 0.3V to $(V_1 + 0.3V)$ |

| $V_P$ ( $I_{VP}$ < 50mA) the higher of -0.3V and ( $V_{CC}$ - 1V) to +40V             | UV0.3V to +6V                                                                        |

| LDOIN0.3V to +40V                                                                     | Continuous Current Into Any Logic Pin±50mA                                           |

| $V_5$ 0.3V to the lesser of ( $V_{LDOIN}$ + 0.3V) and +6V                             | Continuous Power Dissipation                                                         |

| LDO330.3V to the lesser of $(V_5 + 0.3V)$ and +6V                                     | TQFN (derate 27.8mW/°C above +70°C)2222mW                                            |

| V <sub>L</sub> 0.3V to +6V                                                            | WLP (derate 22.7mW/°C above +70°C)1816mW                                             |

| DI40V to +40V                                                                         | Operating Temperature Range40°C to +85°C                                             |

| C/Q, DOMIN: the higher of -40V and (V <sub>CC</sub> - 40V)                            | Maximum Junction Temperature+150°C                                                   |

| MAX: the lesser of +40V and ( $V_{CC}$ + 40V)                                         | Storage Temperature Range65°C to +150°C                                              |

| Logic Inputs                                                                          | Lead Temperature (TQFN only; soldering, 10s)+300°C                                   |

| TXC, TXQ, TXEN, LO, $\overline{\text{CS}}$ , SDI, SCLK0.3V to (V <sub>L</sub> + 0.3V) | Soldering Temperature (reflow)+260°C                                                 |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### PACKAGE THERMAL CHARACTERISTICS (Note 1)

| TQFN                                                            | WLP                                                             |

|-----------------------------------------------------------------|-----------------------------------------------------------------|

| Junction-to-Ambient Thermal Resistance (θ <sub>JA</sub> )36°C/W | Junction-to-Ambient Thermal Resistance (θ <sub>JA</sub> )44°C/W |

| Junction-to-Case Thermal Resistance (θ ις)3°C/W                 | •                                                               |

Note 1: Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a fourlayer board. For detailed information on package thermal considerations, refer to www.maxim-ic.com/thermal-tutorial.

### DC ELECTRICAL CHARACTERISTICS

$(V_{CC}=18V\ to\ 36V,\ V_L=2.3V\ to\ 5.5V,\ V_{GND}=0V;\ all\ logic\ inputs\ at\ V_L\ or\ GND;\ T_A=-40^{\circ}C\ to\ +85^{\circ}C,\ unless\ otherwise\ noted.\ Typical\ values\ are\ at\ V_{CC}=24V,\ V_L=3.3V,\ and\ T_A=+25^{\circ}C,\ unless\ otherwise\ noted.)\ (Note\ 2)$

| PARAMETER                                                    | SYMBOL                   | CONDITIONS                                                                                                                  | MIN  | TYP  | MAX  | UNITS |

|--------------------------------------------------------------|--------------------------|-----------------------------------------------------------------------------------------------------------------------------|------|------|------|-------|

| V <sub>CC</sub> Supply Voltage                               | V <sub>CC</sub>          | For driver operation                                                                                                        | 9    |      | 36   | V     |

| V <sub>CC</sub> Supply Current                               | lcc                      | $V_{CC}$ = 24V, C/Q as input, no load on V <sub>5</sub> or LDO33, LDOIN not connected to V <sub>P</sub> , $V_{LDOIN}$ = 24V |      | 1    | 2.5  | mA    |

| V <sub>CC</sub> Undervoltage-Lockout<br>Threshold            | VCCUVLO                  | V <sub>CC</sub> falling                                                                                                     | 6    | 7.4  | 9    | V     |

| V <sub>CC</sub> Undervoltage-Lockout<br>Threshold Hysteresis | V <sub>CCUVLO_HYST</sub> |                                                                                                                             |      | 200  |      | mV    |

| V <sub>5</sub> Supply Current                                | <sup>1</sup> 5_IN        | LDOIN shorted to $V_5$ , external 5V applied to $V_5$ , no switching, LDO33 disabled                                        |      | 3    |      | mA    |

| V <sub>5</sub> Undervoltage-Lockout<br>Threshold             | V <sub>5UVLO</sub>       | V <sub>5</sub> falling                                                                                                      |      | 2.0  |      | V     |

| V <sub>L</sub> Logic-Level Supply Voltage                    | VL                       |                                                                                                                             | 2.3  |      | 5.5  | V     |

| V <sub>L</sub> Logic-Level Supply Current                    | IL                       | All logic inputs at V <sub>L</sub> or GND                                                                                   |      |      | 5    | μA    |

| V <sub>L</sub> Undervoltage Threshold                        | V <sub>LUVLO</sub>       | V <sub>L</sub> falling                                                                                                      | 0.65 | 0.95 | 1.30 | V     |

| 5V LDO (V <sub>5</sub> )                                     |                          |                                                                                                                             |      |      |      |       |

| LDOIN Input Voltage Range                                    | V <sub>LDOIN</sub>       |                                                                                                                             | 7    |      | 36   | V     |

| LDOIN Supply Current I <sub>LDOIN</sub>                      |                          | $V_{LDOIN}$ = 24V, C/Q is configured as an input, no load on $V_5$ or LDO33                                                 |      | 2.5  | 5    | mA    |

### **DC ELECTRICAL CHARACTERISTICS (continued)**

$(V_{CC} = 18V \text{ to } 36V, V_L = 2.3V \text{ to } 5.5V, V_{GND} = 0V;$  all logic inputs at  $V_L$  or GND;  $T_A = -40^{\circ}C$  to  $+85^{\circ}C$ , unless otherwise noted. Typical values are at  $V_{CC} = 24V, V_L = 3.3V$ , and  $T_A = +25^{\circ}C$ , unless otherwise noted.) (Note 2)

| PARAMETER                               | SYMBOL                 | CONDITIONS                                                                                                                                                                                                             | MIN               | TYP                   | MAX                   | UNITS |

|-----------------------------------------|------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|-----------------------|-----------------------|-------|

| V <sub>5</sub> Output Voltage Range     | V <sub>5</sub>         | No load on $V_5$ , $7V \le V_{LDOIN} \le 36V$                                                                                                                                                                          | 4.75              | 5.00                  | 5.25                  | V     |

|                                         |                        | $1 \text{mA} < I_{\text{LOAD}} < 10 \text{mA}, V_{\text{LDOIN}} = 7 \text{V},$ $0.1 \mu\text{F}$ bypass capacitor on $V_5$                                                                                             |                   | 0.8                   |                       |       |

| V <sub>5</sub> Load Regulation          |                        | $\begin{array}{l} 1\text{mA} < I_{LOAD} < 30\text{mA}, \ V_{LDOIN} = 7\text{V}, \\ 0.1\mu\text{F} \ \text{bypass capacitor on V}_5, \ 10\Omega - 1\mu\text{F} \\ \text{compensation network added to V}_5 \end{array}$ |                   | 0.8                   |                       | %     |

| 3.3V LDO (LDO33)                        |                        |                                                                                                                                                                                                                        |                   |                       |                       |       |

| LDO33 Output Voltage                    | V <sub>LDO33</sub>     | No load on LDO33                                                                                                                                                                                                       | 3.1               | 3.3                   | 3.5                   | V     |

| LDO33 Undervoltage-Lockout<br>Threshold | V <sub>LDO33UVLO</sub> | V <sub>LDO33</sub> falling                                                                                                                                                                                             |                   | 2.4                   |                       | V     |

| LDO33 Load Regulation                   |                        | 1mA < I <sub>LOAD</sub> < 20mA, V <sub>LDOIN</sub> = 7V                                                                                                                                                                |                   | 0.25                  |                       | %     |

| 24V INTERFACE                           |                        |                                                                                                                                                                                                                        |                   |                       |                       |       |

| C/Q Driver Output-Voltage High          | V <sub>OH_C/Q</sub>    | C/Q high-side enabled, $I_{C/Q} = -100 \text{mA}$ , $9V \le V_{CC} \le 36V$                                                                                                                                            | V <sub>CC</sub> - | V <sub>CC</sub> - 1.3 |                       | V     |

| C/Q Driver Output-Voltage Low           | V <sub>OL_C/Q</sub>    | C/Q low-side enabled, $I_{C/Q} = +100$ mA, $9V \le V_{CC} \le 36V$                                                                                                                                                     |                   | 1.4                   | 3                     | V     |

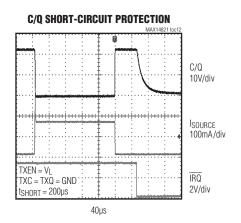

| C/Q Driver Source Current Limit         | I <sub>OH_C/Q</sub>    | C/Q high-side enabled, $V_{C/Q} < (V_{CC} - 3V)$ , $9V \le V_{CC} \le 36V$                                                                                                                                             | +100              | +140                  | +190                  | mA    |

| C/Q Driver Sink Current Limit           | I <sub>OL_C/Q</sub>    | C/Q low-side enabled, $V_{C/Q} > 3V$ , $9V \le V_{CC} \le 36V$                                                                                                                                                         | -190              | -140                  | -100                  | mA    |

| DO Driver Output-Voltage High           | V <sub>OH_DO</sub>     | DO high-side enabled, $I_{DO} = +100$ mA, $9V \le V_{CC} \le 36V$                                                                                                                                                      | V <sub>CC</sub>   | V <sub>CC</sub> - 1.6 |                       | V     |

| DO Driver Output-Voltage Low            | V <sub>OL_DO</sub>     | DO low-side enabled, $I_{DO}$ = -100mA, $9V \le V_{CC} \le 36V$                                                                                                                                                        |                   | 1.6                   | 3                     | V     |

| DO Driver Source Current Limit          | I <sub>OH_DO</sub>     | DO high-side enabled, V <sub>DO</sub> < (V <sub>CC</sub> - 3V)                                                                                                                                                         | +100              | +135                  | +190                  | mA    |

| DO Driver Sink Current Limit            | I <sub>OL_DO</sub>     | DO high-side enabled, V <sub>DO</sub> > 3V                                                                                                                                                                             | -190              | -135                  | -100                  | mA    |

| C/Q, DI Input Voltage Range             | V <sub>IN</sub>        | For valid RX, LI                                                                                                                                                                                                       | -1.0              |                       | V <sub>CC</sub> + 1.0 | V     |

| C/Q Input Threshold High                | V <sub>IH_C/Q</sub>    | C/Q driver disabled                                                                                                                                                                                                    | 10.5              |                       | 13.0                  | V     |

| C/Q Input Threshold Low                 | V <sub>IL_C/Q</sub>    | C/Q driver disabled                                                                                                                                                                                                    | 8.0               |                       | 11.5                  | V     |

| C/Q Input Hysteresis                    | V <sub>HYS_C/Q</sub>   | C/Q driver disabled                                                                                                                                                                                                    | 1.0               |                       |                       | V     |

| DI Input Threshold High                 | V <sub>IH_DI</sub>     |                                                                                                                                                                                                                        | 6.8               |                       | 8                     | V     |

| DI Input Threshold Low                  | V <sub>IL_DI</sub>     |                                                                                                                                                                                                                        | 5.2               |                       | 6.4                   | V     |

| DI Input Hysteresis                     | V <sub>HYS_DI</sub>    |                                                                                                                                                                                                                        | 1                 |                       |                       | V     |

| C/Q Weak Pulldown Current               | I <sub>PDC/Q</sub>     | C/Q driver disabled, $V_{C/Q} = (V_{CC} - 1V)$                                                                                                                                                                         | 100               |                       | 400                   | μΑ    |

### **DC ELECTRICAL CHARACTERISTICS (continued)**

$(V_{CC} = 18V \text{ to } 36V, V_L = 2.3V \text{ to } 5.5V, V_{GND} = 0V;$  all logic inputs at  $V_L$  or GND;  $T_A = -40^{\circ}C$  to  $+85^{\circ}C$ , unless otherwise noted. Typical values are at  $V_{CC} = 24V, V_L = 3.3V$ , and  $T_A = +25^{\circ}C$ , unless otherwise noted.) (Note 2)

| PARAMETER                               | SYMBOL                                                                                                         | CONDIT                                                                        | TIONS                   | MIN                     | TYP  | MAX                     | UNITS |

|-----------------------------------------|----------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|-------------------------|-------------------------|------|-------------------------|-------|

| DO Weak Pulldown Current                | I <sub>PDDO</sub>                                                                                              | DO driver disabled, V<br>V <sub>DO</sub> = (V <sub>CC</sub> - 1V)             | 40                      |                         | 120  | μΑ                      |       |

| DI Weak Pulldown Current                | I <sub>PDDI</sub>                                                                                              | DI load disabled, V <sub>CC</sub><br>V <sub>DI</sub> = (V <sub>CC</sub> - 1V) | ; = 36V,                | 50                      |      | 300                     | μΑ    |

| C/Q Input Capacitance                   | C <sub>C/Q</sub>                                                                                               | C/Q driver disabled                                                           |                         |                         | 40   |                         | рF    |

| DO Input Capacitance                    | C <sub>DO</sub>                                                                                                | DO driver disabled                                                            |                         |                         | 40   |                         | рF    |

| DI Input Capacitance                    | C <sub>DI</sub>                                                                                                |                                                                               |                         |                         | 20   |                         | рF    |

| C/Q, DI CURRENT SINK                    |                                                                                                                |                                                                               |                         |                         |      |                         |       |

| C/Q Load Current                        | I <sub>LLM_C/Q</sub>                                                                                           | C/Q load enabled                                                              | $0V \le V_{C/Q} \le 5V$ | 0                       |      | 9                       | mA    |

|                                         |                                                                                                                | (C/QLoad = 1)                                                                 | 5V ≤ V <sub>C/Q</sub>   | 5                       | 6.6  | 9                       |       |

| DI Load Current                         | I <sub>LLM_DI</sub>                                                                                            | DI load enabled                                                               | $0V \le V_{DI} \le 5V$  | 0                       |      | 9                       | mA    |

|                                         |                                                                                                                | (DiLoad = 1)                                                                  | 9V ≤ V <sub>DI</sub>    | 6                       | 7.5  | 9                       |       |

| LOGIC INPUTS (TXC, TXQ, TX              | EN, LO, CS, SDI,                                                                                               | SCLK)                                                                         |                         | 1                       |      | ,                       | 1     |

| Logic-Input Voltage Low                 | V <sub>IL</sub>                                                                                                |                                                                               |                         | 0.3 x<br>V <sub>L</sub> |      |                         | V     |

| Logic -Input Voltage High               | V <sub>IH</sub>                                                                                                |                                                                               |                         |                         |      | 0.7 x<br>V <sub>L</sub> | V     |

| Logic-Input Leakage Current             | I <sub>LEAK</sub>                                                                                              | Logic input = GND or                                                          | VL                      | -1                      |      | +1                      | μΑ    |

| Logic-Input Capacitance                 | C <sub>IN</sub>                                                                                                |                                                                               |                         |                         | 5    |                         | рF    |

| LOGIC OUTPUTS (RX, WU, LI,              | UV, SDO, IRQ)                                                                                                  |                                                                               |                         |                         |      |                         |       |

| Logic-Output Voltage Low                | V <sub>OL</sub>                                                                                                | I <sub>OUT</sub> = -5mA                                                       |                         |                         |      | 0.4                     | V     |

| Logic-Output Voltage High               | V <sub>OHRX</sub> ,<br>V <sub>OHWU</sub> , V <sub>OHLI</sub> ,<br>V <sub>OHSDO</sub> ,<br>V <sub>OHIRQ</sub> , | I <sub>OUT</sub> = 5mA (Note 3)                                               | V <sub>L</sub> - 0.6    |                         |      | V                       |       |

| SDO Leakage Current                     | I <sub>LK_SDO</sub>                                                                                            | SDO disabled, SDO =                                                           | -1                      |                         | +1   | μΑ                      |       |

| THERMAL SHUTDOWN                        | <u>. – –                                   </u>                                                                |                                                                               |                         |                         |      |                         |       |

| Thermal Warning Threshold               |                                                                                                                | Die temperature rising                                                        | g, OTemp bit is set     |                         | +115 |                         | °C    |

| Thermal Warning Threshold<br>Hysteresis |                                                                                                                | Die temperature falling cleared                                               |                         | 20                      |      | °C                      |       |

| Thermal Shutdown Threshold              |                                                                                                                | Die temperature rising                                                        | )                       |                         | +150 |                         | °C    |

| Thermal Shutdown Hysteresis             |                                                                                                                |                                                                               |                         |                         | 20   |                         | °C    |

### **AC ELECTRICAL CHARACTERISTICS**

$(V_{CC}=18V\ to\ 36V,\ V_L=2.3V\ to\ 5.5V,\ V_{GND}=0V;\ all\ logic\ inputs\ at\ V_L\ or\ GND;\ T_A=-40^{\circ}C\ to\ +85^{\circ}C,\ unless\ otherwise\ noted.\ Typical\ values\ are\ at\ V_{CC}=24V,\ V_L=3.3V,\ and\ T_A=+25^{\circ}C,\ unless\ otherwise\ noted.)\ (Note\ 2)$

| PARAMETER                         | SYMBOL             | CONDITIONS                       |            | MIN | TYP | MAX   | UNITS |

|-----------------------------------|--------------------|----------------------------------|------------|-----|-----|-------|-------|

| C/Q, DO, DI INTERFACES            | 1                  |                                  |            |     |     |       | l.    |

| Data Rate                         | DR                 | HiSlew = 1                       |            | 4.8 |     | 230.4 | kbps  |

| Dala nate                         |                    | HiSlew = 0                       |            | 4.8 |     | 38.4  | Kups  |

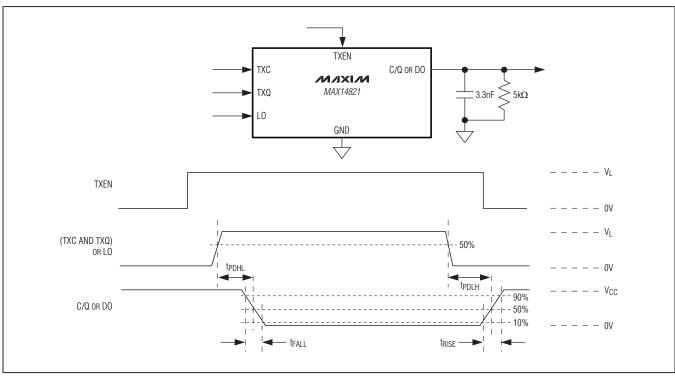

| DRIVER (C/Q, DO)                  |                    |                                  |            |     |     |       |       |

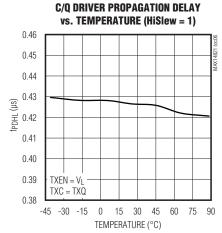

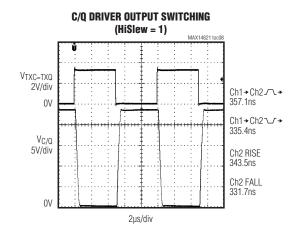

| Driver Low-to-High Propagation    | t                  | Push-pull or high-side (PNP)     | HiSlew = 1 |     | 0.5 | 2     | 110   |

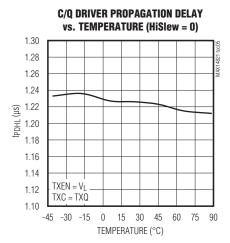

| Delay                             | t <sub>PDLH</sub>  | configuration, Figure 1          | HiSlew = 0 |     | 1.6 | 5     | μs    |

| Driver High-to-Low Propagation    | t·                 | Push-pull or low-side (NPN)      | HiSlew = 1 |     | 0.5 | 2     | 110   |

| Delay                             | <sup>t</sup> PDHL  | configuration, Figure 1          | HiSlew = 0 |     | 1.6 | 5     | μs    |

| Driver Skew                       | tSKEW              | ItpDLH - tpDHLI                  |            |     | 0.1 | 2     | μs    |

| Driver Rise Time                  |                    | Push-pull or high-side (PNP)     | HiSlew = 1 |     | 0.4 | 1.7   |       |

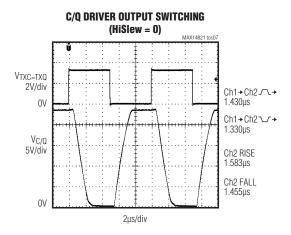

| Driver Rise Time                  | t <sub>RISE</sub>  | configuration, Figure 1          | HiSlew = 0 |     | 1.5 | 4     | μs    |

| Deixon Fall Time                  |                    | Push-pull or low-side (NPN)      | HiSlew = 1 |     | 0.4 | 1.7   |       |

| Driver Fall Time                  | tFALL              | configuration, Figure 1          | HiSlew = 0 |     | 1.4 | 4     | μs    |

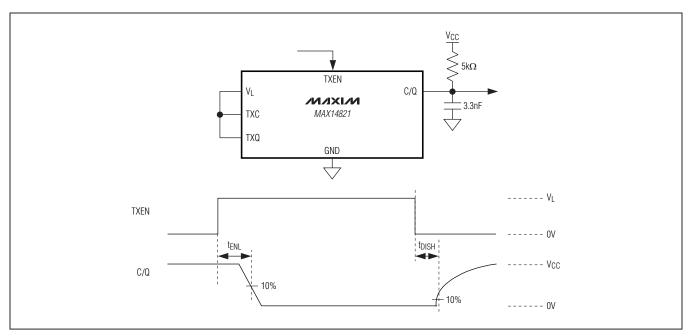

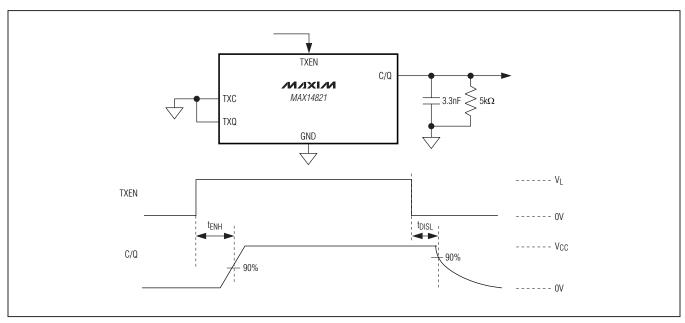

| Driver Enable Time High           |                    |                                  | HiSlew = 1 |     | 0.3 | 1     |       |

|                                   | tENH               | configuration, Figure 3          | HiSlew = 0 |     | 0.8 | 7     | μs    |

| Driver Enable Time Low            | +                  | I don pair of low side (141 14)  | HiSlew = 1 |     | 0.3 | 1     |       |

|                                   | t <sub>ENL</sub>   |                                  | HiSlew = 0 |     | 0.9 | 7     | μs    |

| D' - D' - I I - T' I I' - I       |                    | Push-pull or high-side (PNP)     | HiSlew = 1 |     | 1.6 | 3     |       |

| Driver Disable Time High          | t <sub>DISH</sub>  | configuration, Figure 2 (Note 4) | HiSlew = 0 |     | 1.6 | 3     | μs    |

| D: D: II T: I                     |                    | Push-pull or low-side (NPN)      | HiSlew = 1 |     | 0.1 | 3     |       |

| Driver Disable Time Low           | t <sub>DISL</sub>  | configuration, Figure 3 (Note 4) | HiSlew = 0 |     | 0.1 | 3     | μs    |

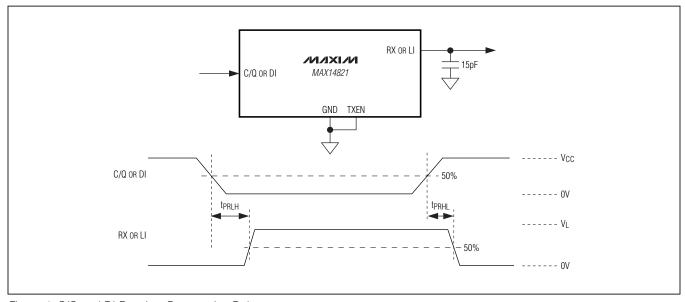

| RECEIVER (C/Q, DI) (Figure 4)     |                    |                                  | ,          |     |     |       | ,     |

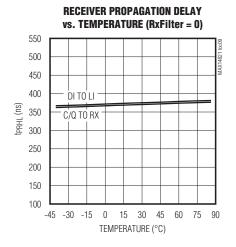

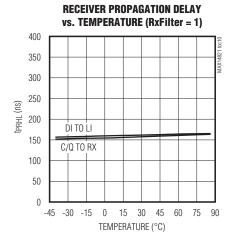

| Receiver Low-to-High              | _                  | RxFilter = 1                     |            |     | 0.2 | 2     |       |

| Propagation Delay                 | <sup>t</sup> PRLH  | RxFilter = 0                     |            |     | 0.4 | 2     | μs    |

| Receiver High-to-Low              |                    | RxFilter = 1                     |            |     | 0.3 | 2     |       |

| Propagation Delay                 | <sup>t</sup> PRHL  | RxFilter = 0                     |            |     | 0.5 | 2     | μs    |

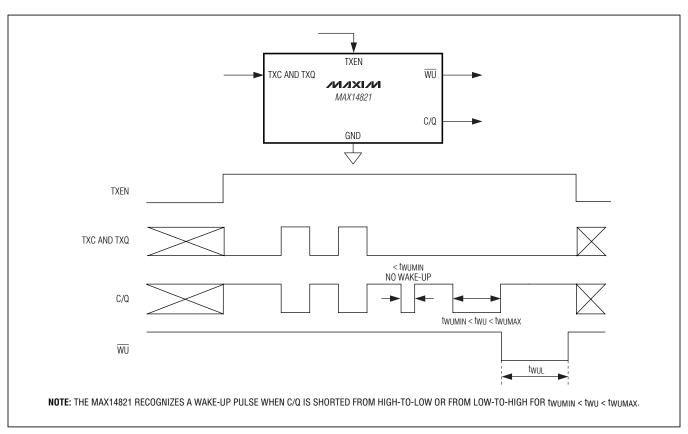

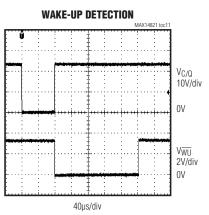

| WAKE-UP DETECTION (Figure 5       | 5)                 |                                  | ,          |     |     |       | ,     |

| Wake-Up Input Minimum Pulse Width | twumin             |                                  |            | 30  | 40  | 50    | μs    |

| Wake-Up Input Maximum Pulse Width | t <sub>WUMAX</sub> |                                  |            | 120 | 140 | 160   | μs    |

| WU Output Low Time                | t <sub>WUL</sub>   | Valid wake-up condition on C/    | Q          | 120 | 190 | 260   | μs    |

### **AC ELECTRICAL CHARACTERISTICS (continued)**

$(V_{CC} = 18V \text{ to } 36V, V_L = 2.3V \text{ to } 5.5V, V_{GND} = 0V;$  all logic inputs at  $V_L$  or GND;  $T_A = -40^{\circ}C$  to  $+85^{\circ}C$ , unless otherwise noted. Typical values are at  $V_{CC} = 24V, V_L = 3.3V,$  and  $T_A = +25^{\circ}C,$  unless otherwise noted.) (Note 2)

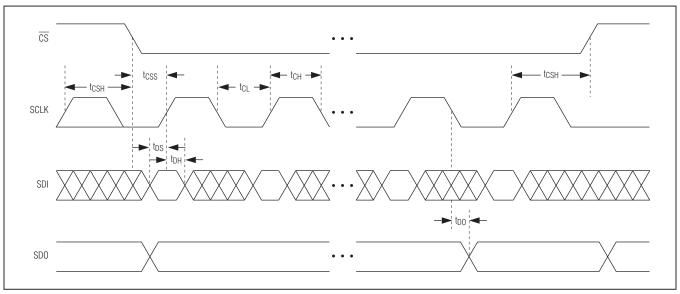

| PARAMETER                                  | SYMBOL             | CONDITIONS | MIN   | TYP | MAX | UNITS |  |  |  |  |

|--------------------------------------------|--------------------|------------|-------|-----|-----|-------|--|--|--|--|

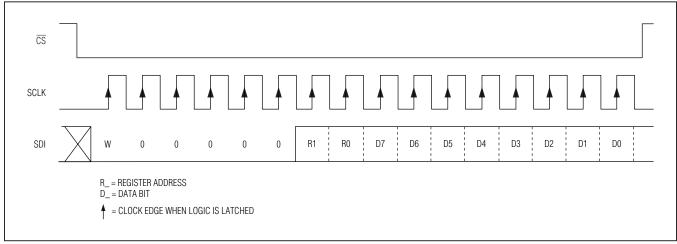

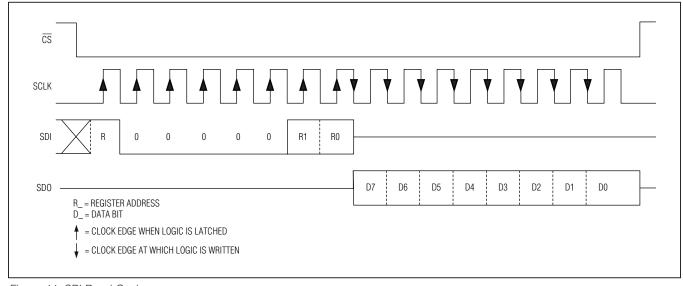

| SPI TIMING (CS, SCLK, SDI, SDO) (Figure 6) |                    |            |       |     |     |       |  |  |  |  |

| SCLK Clock Period                          | t <sub>CH+CL</sub> |            | 83.3  |     |     | ns    |  |  |  |  |

| SCLK Pulse-Width High                      | t <sub>CH</sub>    |            | 41.65 |     |     | ns    |  |  |  |  |

| SCLK Pulse-Width Low                       | t <sub>CL</sub>    |            | 41.65 |     |     | ns    |  |  |  |  |

| CS Fall to SCLK Rise Time                  | t <sub>CSS</sub>   |            | 20    |     |     | ns    |  |  |  |  |

| SCLK Rise to CS Rise Hold Time             | tCSH               |            | 20    |     |     | ns    |  |  |  |  |

| SDI Hold Time                              | t <sub>DH</sub>    |            | 10    |     |     | ns    |  |  |  |  |

| SDI Setup Time                             | t <sub>DS</sub>    |            | 10    |     |     | ns    |  |  |  |  |

| Output Data Propagation Delay              | t <sub>DO</sub>    |            |       |     | 32  | ns    |  |  |  |  |

| SDO Rise and Fall Times                    | t <sub>FT</sub>    |            |       |     | 20  | ns    |  |  |  |  |

| Minimum CS Pulse                           | tcsw               |            | 76.8  |     |     | ns    |  |  |  |  |

Note 2: All devices are 100% production tested at  $T_A = +25$ °C. Limits over the operating temperature range are guaranteed by

Note 3: UV is an open-drain output. Connect UV to a voltage less than 5.5V through an external pullup resistor.

Note 4: Disable time measurements are load dependent.

Figure 1. C/Q and LO Driver Propagation Delays and Rise/Fall Times

Figure 2. C/Q Driver Enable Low and Disable High Timing with External Pullup Resistor

Figure 3. C/Q Driver Enable High and Disable Low Timing

Figure 4. C/Q and DI Receiver Propagation Delays

Figure 5. Wake-Up Detection Timing

Figure 6. SPI Timing Diagram

## **IO-Link Device Transceiver**

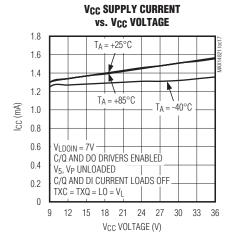

### **Typical Operating Characteristics**

(V<sub>CC</sub> = 24V, LDOIN = V<sub>P</sub>, V<sub>L</sub> = LDO33, C/Q and DO in push-pull configuration, T<sub>A</sub> = +25°C, unless otherwise noted.)

## **IO-Link Device Transceiver**

### **Typical Operating Characteristics (continued)**

$(V_{CC} = 24V, LDOIN = V_P, V_L = LDO33, C/Q$ and DO in push-pull configuration,  $T_A = +25$ °C, unless otherwise noted.)

## **IO-Link Device Transceiver**

### **Typical Operating Characteristics (continued)**

(V<sub>CC</sub> = 24V, LDOIN = V<sub>P</sub>, V<sub>L</sub> = LDO33, C/Q and DO in push-pull configuration, T<sub>A</sub> = +25°C, unless otherwise noted.)

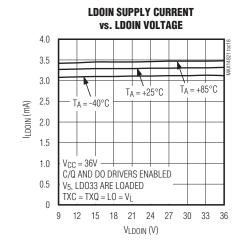

# **IO-Link Device Transceiver**

## **Pin/Bump Configurations**

## **Pin/Bump Descriptions**

| PIN     | N   | NAME           | FUNCTION                                                                                                                                                                                                                                                                                               |

|---------|-----|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TQFN-EP | WLP | NAME           | FUNCTION                                                                                                                                                                                                                                                                                               |

| 1       | A2  | LDOIN          | 5V Linear Regulator Input. Bypass LDOIN to GND with a 0.1μF ceramic capacitor.                                                                                                                                                                                                                         |

| 2       | А3  | V <sub>5</sub> | 5V Power-Supply Input and 5V Linear Regulator Output. Bypass $V_5$ to GND with a $0.1\mu F$ ceramic capacitor for 10mA load capability. Add the recommended compensation network to increase the source capability to 30mA. See the <i>5V and 3.3V Linear Regulators</i> section for more information. |

| 3       | A4  | LDO33          | 3.3V Linear Regulator Output. Bypass LDO33 to GND with a 1µF ceramic capacitor.                                                                                                                                                                                                                        |

| 4       | В3  | ĪRQ            | Active-Low Interrupt Request Output. $\overline{\text{IRQ}}$ is a push-pull output referenced to V <sub>L</sub> .                                                                                                                                                                                      |

| 5       | A5  | SCLK           | SPI Clock Input                                                                                                                                                                                                                                                                                        |

| 6       | B4  | CS             | Active-Low SPI Chip-Select Input                                                                                                                                                                                                                                                                       |

| 7       | B5  | SDO            | SPI Serial-Data Output                                                                                                                                                                                                                                                                                 |

| 8       | C4  | SDI            | SPI Serial-Data Input                                                                                                                                                                                                                                                                                  |

| 9       | C5  | VL             | Logic-Level Supply Input. $V_L$ defines the logic levels on all the logic inputs and outputs. Bypass $V_L$ to GND with a $0.1\mu F$ ceramic capacitor.                                                                                                                                                 |

| 10      | C3  | I.C.           | Internally Connected. Connect to V <sub>L</sub> or leave unconnected.                                                                                                                                                                                                                                  |

# **IO-Link Device Transceiver**

## Pin/Bump Descriptions (continued)

| PII     | N      |                 |                                                                                                                                                                                                                                                                                                                                                                  |

|---------|--------|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TQFN-EP | WLP    | NAME            | FUNCTION                                                                                                                                                                                                                                                                                                                                                         |

| 11      | D5     | TXQ             | Transmit Level Input. The logic on the C/Q output is the inverse logic level of the signals on the TXC and TXQ inputs. TXQ is ANDed with TXC. Drive TXQ high if not in use.                                                                                                                                                                                      |

| 12      | D4     | TXC             | Transmit Communication Input. The logic on the C/Q output is the inverse logic level of the signals on the TXC and TXQ inputs. TXC is ANDed with TXQ. Drive TXC high if not in use.                                                                                                                                                                              |

| 13      | E5     | TXEN            | Transmitter Enable. Drive TXEN high to enable the C/Q transmitter. TXEN is referenced to V <sub>L</sub> .                                                                                                                                                                                                                                                        |

| 14      | E4     | RX              | Receiver Output. RX is the inverse logic level of C/Q. RX is always high when the RxDis bit in the CQConfig register is set to 1.                                                                                                                                                                                                                                |

| 15      | D3     | WU              | Active-Low Wake-Up Output. WU is a push-pull output referenced to V <sub>L</sub> . WU pulses low for 190µs (typ) when a valid wake-up pulse is detected on the C/Q line.                                                                                                                                                                                         |

| 16      | E3     | LO              | Logic Input of the DO Output. LO is the logic input that drives DO. LO is referenced to V <sub>L</sub> .                                                                                                                                                                                                                                                         |

| 17      | E2     | LI              | Logic Output of the 24V DI Logic Input. LI is the inverse logic of DI. LI is referenced to V <sub>L</sub> .                                                                                                                                                                                                                                                      |

| 18      | D2     | UV              | Open-Drain Undervoltage Indicator Output. In case of an undervoltage, the UV open-drain transistor is off.                                                                                                                                                                                                                                                       |

| 19      | E1     | DI              | 24V Logic-Level Digital Input                                                                                                                                                                                                                                                                                                                                    |

| 20      | C1, C2 | GND             | Ground                                                                                                                                                                                                                                                                                                                                                           |

| 21      | B1     | C/Q             | SIO/IO-Link Data Input/Output. Drive TXEN high to enable the C/Q driver. The logic on the C/Q output is the inverse logic level of the signals on the TXC and TXQ inputs. RX is the logic inverse of C/Q. The C/Q driver output level can be set by the TXC/TXQ inputs or programmed by the Q bit. The level on C/Q can be read by the RX ouput or the QLvI bit. |

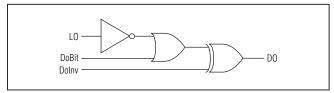

| 22      | D1     | DO              | 24V Logic-Level Digital Output. DO is the inverse logic level of the LO input and can be digitally controlled through the DIOConfig register.                                                                                                                                                                                                                    |

| 23      | A1     | V <sub>CC</sub> | Power-Supply Input. Bypass V <sub>CC</sub> to GND with a 1µF ceramic capacitor.                                                                                                                                                                                                                                                                                  |

| 24      | B2     | V <sub>P</sub>  | Protected 24V Supply Output. V <sub>P</sub> is one diode drop below V <sub>CC</sub> . V <sub>P</sub> is reverse-polarity protected and can be used as a 24V protected supply to the sensor or actuator electronics.                                                                                                                                              |

| _       | _      | EP              | Exposed Pad (TQFN Only). Connect EP to GND.                                                                                                                                                                                                                                                                                                                      |

### **Detailed Description**

The MAX14821 is a sensor/actuator transceiver designed for IO-Link device applications supporting all the specified IO-Link data rates. In IO-Link applications, the device acts as the physical layer interface to a microcontroller running the data-link layer protocol. The device contains an additional 24V digital input and an additional 24V digital output. Two internal linear regulators generate common sensor and actuator power requirements: 5V and 3.3V.

The device detects IO-Link wake-up conditions on the C/Q line and generates a wake-up signal on the WU output. The C/Q and DO drivers are independently configurable to any one of three driver output types: push-pull, high-side (PNP), or low-side (NPN).

The C/Q and DI inputs have selectable current sinks that can be enabled for use in actuators where the master requires a Type 2 load. The device is configured and monitored through an SPI interface. Extensive alarms are available through SPI.

#### 24V Interface

The device features an IO-transceiver interface capable of operating with voltages up to 36V. This is the 24V interface and includes the C/Q input/output, the logic-level digital output (DO), and the logic-level digital input (DI).

#### Configurable Drivers

The device features selectable push-pull, high-side (PNP), or low-side (NPN) switching drivers at C/Q and DO.

Set the C/Q N/P and C/Q PP bits in the CQConfig register to select the driver mode for the C/Q driver. When configured as a push-pull output, C/Q switches between VP and ground. Set the C/Q\_PP bit to 1 to select pushpull operation at C/Q. Set the C/Q\_PP bit to 0 to configure the C/Q output for open-drain operation. The C/Q\_N/P bit selects NPN or PNP operation when C/Q is configured as an open-drain output.

Set the DoN/P and DoPP bits in the DIOConfig register to select the driver mode for the DO output. When configured as a push-pull output, DO switches between V<sub>CC</sub> and ground. Set the DoPP bit to 1 for push-pull operation. The DoN/P bit selects NPN or PNP operation when DO is configured as an open-drain output. Set the DoPP bit to 0 to select high-side or low-side operation at DO.

#### C/Q Driver and Receiver

The TXEN input enables the C/Q driver. Drive TXEN high to enable the C/Q driver. Drive TXEN low to disable the driver.

The C/Q driver is specified to supply up to 100mA DC load current.

The HiSlew bit increases the slew rate of the C/Q and DO driver outputs. Set HiSlew to 1 for data rates of 230kbps or higher. Set HiSlew to 0 to reduce both the C/Q and DO driver slew rates to reduce EMI emission and reflections.

The C/Q receiver is always on. Disable the RX output through the RxDis bit in the CQConfig register. Set the RxDis bit to 1 to set the RX output high. Set the RxDis bit to 0 for normal receive operation.

The C/Q receiver has an analog lowpass filter to reduce high-frequency noise present on the line. Set the RxFilter bit in the CQConfig register to 0 to set the filter corner frequency to 500kHz (typ). Set the RxFilter bit to 1 to set the corner frequency of the filter to 1MHz (typ). Noise filters are present on both the C/Q and DI receivers and are controlled simultaneously by the RxFilter bit.

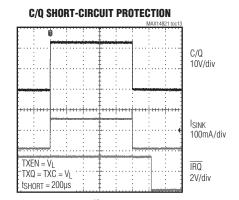

#### C/Q Fault Detection

The device registers a C/QFault condition under either of two conditions:

- 1) When it detects a short circuit for longer than 160µs (typ). A short condition exists when the C/Q driver's load current exceeds the 140mA (typ) current limit.

- 2) When it detects a voltage level error at the C/Q output. A voltage level error occurs when the C/Q driver is configured for open-drain operation (NPN or PNP), the driver is turned off, and the C/Q voltage is not pulled to exceed the C/Q receiver's threshold levels (< 8V or > 13V) by the external supply.

When a C/QFault error occurs, the C/QFault and C/QFaultInt bits are set, IRQ asserts, and the driver is turned off 240µs (typ) after the start of the fault condition.

When a short-circuit event occurs on C/Q, the driver enters autoretry mode. In autoretry mode the device periodically checks whether the short is still present and attempts to correct the driver output. Autoretry attempts last for 350µs (typ) and occur every 26ms (typ).

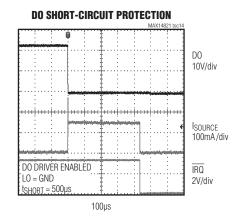

#### DO Fault Detection

The device registers a DoFault event when a short circuit is present at the DO output for longer than 30-440µs. A short condition exists when the load current on the DO driver exceeds the 135mA (typ) DO current limit. When a short-circuit condition is detected, the DO driver enters autoretry mode. In autoretry mode the device periodically checks whether the error is still present. Autoretry attempts last for 440µs (typ) and occur every 26ms (typ). When a DoFault error is detected, the DoFault and DoFaultInt bits are set. IRQ asserts, and the driver is turned off 440µs (typ) after the start of the DO faults.

#### Reverse-Polarity Protection

The device is protected against reverse-polarity connections on V<sub>CC</sub>, C/Q, DO, DI, and GND. Any combination of these pins can be connected to DC voltages up to 40V (max). A short to 40V results in a current flow of less than 500µA.

Ensure that the maximum voltage between any of these pins does not exceed 40V.

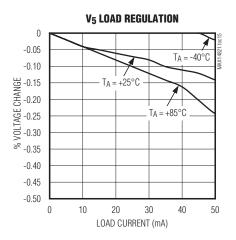

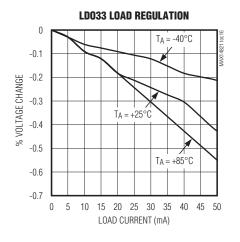

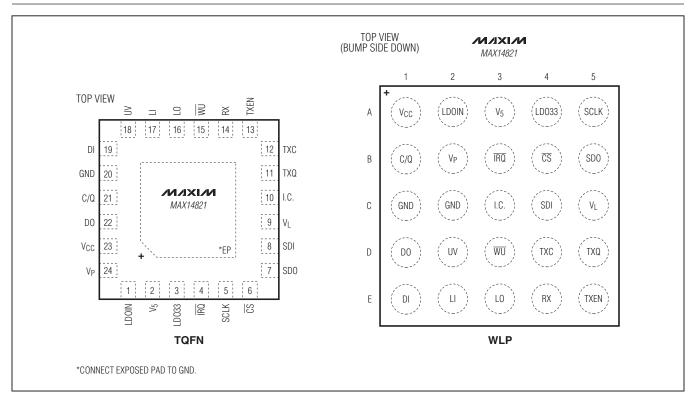

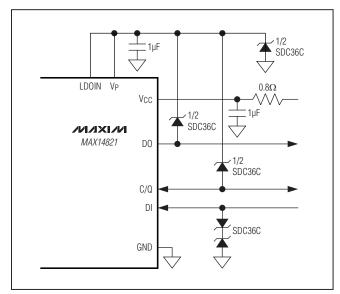

#### **5V and 3.3V Linear Regulators**

The device includes two internal current-limited regulators to generate 5V (V<sub>5</sub>) and 3.3V (LDO33). V<sub>5</sub> is specified at 10mA when bypassed with a 0.1µF capacitor to ground. Add the compensation network shown in Figure 7 to draw up to 30mA from V<sub>5</sub>. LDO33 is specified at 20mA. The input of V<sub>5</sub>, LDOIN, can be connected to V<sub>P</sub>, the protected 24V supply output, or to another voltage in the 7V to 36V range.

V<sub>5</sub> constitutes the supply for the logic block. The 5V LDO can be disabled by connecting LDOIN to V<sub>5</sub>. Apply an external voltage from 4.75V to 5.25V to V<sub>5</sub> when the LDO is disabled.

Figure 7. V<sub>5</sub> Compensation Network

Use the LDO33Dis bit in the Mode register to enable/ disable LDO33. See the *Mode Register [R1, R0] = [1,1]* section for more information. V<sub>5</sub> and LDO33 are not protected against short circuits.

#### **Power-Up**

The C/Q and DO driver outputs and the UV output are high impedance when V<sub>CC</sub>, V<sub>5</sub>, V<sub>L</sub>, and/or LDO33 voltages are below their respective undervoltage thresholds during power-up. UV goes low and the drivers are enabled when all these voltages exceed their respective undervoltage-lockout thresholds.

The drivers are automatically disabled if V<sub>CC</sub>, V<sub>5</sub>, or V<sub>L</sub> falls below its threshold.

#### **Undervoltage Detection**

The device monitors V<sub>CC</sub>, V<sub>5</sub>, V<sub>I</sub>, and optionally LDO33 for undervoltage conditions. UV is high impedance when any monitored voltage falls below its UVLO threshold.

V<sub>CC</sub>, V<sub>5</sub>, and V<sub>L</sub> undervoltage detection cannot be disabled. When V<sub>CC</sub> falls below the V<sub>CCUVLO</sub> threshold, the UV24 and UV24Int bits are set, UV asserts high, and IRQ asserts low.

The SPI register contents are unchanged while V<sub>5</sub> is present, regardless of the state of  $V_{\mbox{\footnotesize{CC}}}$  and LDO33. The SPI interface is not accessible and IRQ is not available when UV is asserted due to a V<sub>5</sub> or V<sub>L</sub> undervoltage event.

When the internal 3.3V LDO regulator voltage (V<sub>I DO33</sub>) falls below the LDO33 undervoltage-lockout threshold, the UV33Int bit in the Status register is set and IRQ asserts. UV asserts if the UV33En bit in the Mode register

The UV output deasserts once the undervoltage condition is removed; however, bits in the Status register and the IRQ output are not cleared until the Status register has been read.

#### **Wake-Up Detection**

The device detects an IO-Link wake-up condition on the C/Q line in push-pull, high-side (PNP), or low-side (NPN) operation modes. A wake-up condition is detected when the C/Q output is shorted for 80µs (typ). WU pulses low for 190µs (typ) when the device detects a wake-up pulse on C/Q (Figure 5).

Set the WulntEn bit in the Mode register to set the Wulnt bit in the Status register and generate an interrupt on IRQ when a wake-up pulse is detected. WuInt is set and IRQ asserts immediately after C/Q is released when WuIntEn = 1.

#### **Thermal Protection and Considerations**

The internal LDOs and drivers can generate more power than the package for the device can safely dissipate. Ensure that the driver LDO loading is less than the package can dissipate. Total power dissipation for the device is calculated using the following equation:

$$P_{TOTAL} = P_{C/Q} + P_{DO} + P_5 + P_{LDO33} + P_Q + P_{CLCQ} + P_{CLDI}$$

where P<sub>C/Q</sub> is the power generated in the C/Q driver, PDO is the power dissipated by the DO driver, P5 and  $P_{LDO33}$  are the power generated by the LDOs,  $P_Q$  is the quiescent power generated by the device, and PCLCQ and P<sub>CLDI</sub> are the power generated in the C/Q and DI current sinks.

Ensure that the total power dissipation is less than the limits listed in the Absolute Maximum Ratings section.

Use the following to calculate the power dissipation (in mW) due to the C/Q driver:

$$P_{C/Q} = [I_{C/Q}(max)] \times [0.5 + 7 \times I_{C/Q}(max)]$$

Calculate the internal power dissipation of the DO driver using the following equation:

$$P_{DO} = [I_{DO}(max)] \times [0.5 + 7 \times I_{DO}(max)]$$

Calculate the power dissipation in the 5V LDO, V5, using the following equation:

$$P_5 = (V_{LDOIN} - V_5) \times I_5$$

where I<sub>5</sub> includes the I<sub>1 DO33</sub> current sourced from LDO33.

Calculate the power dissipated in the 3.3V LDO, LDO33, using the following equation:

$$P_{LDO33} = 1.7V \times I_{LDO33}$$

Calculate the guiescent power dissipation in the device using the following equation:

$$P_Q = 5mA \times V_{CC}(max)$$

If the current sinks are enabled, calculate their associated power dissipation as:

$$P_{CLCQ} = 7mA \times V_{C/Q}(max)$$

$P_{CLDI} = 7mA \times V_{DI}(max)$

#### Overtemperature Warning

Bits in the Status and Mode registers are set when the temperature of the device exceeds +115°C (typ). The OTempInt bit in the Status register is set and IRQ asserts when the OTemp bit in the Mode register is set. Read the Status register to clear the OTempInt bit and IRQ.

The OTemp bit is cleared when the die temperature falls to +95°C.

The device continues to operate normally unless the die temperature reaches the +150°C thermal shutdown threshold, when the device enters thermal shutdown.

#### Thermal Shutdown

All regulators and the C/Q and DO output drivers are automatically switched off when the internal die temperature exceeds the +150°C (typ) thermal shutdown threshold. SPI communication is not available during a thermal shutdown event.

Regulators are automatically switched on when the internal die temperature falls below the thermal shutdown threshold plus hysteresis. The internal registers return to their default state when the V<sub>5</sub> regulator is switched on.

### **Register Functionality**

The device has four 8-bit-wide registers for configuration and monitoring (Table 1).

### **Table 1. Register Summary**

| REGISTER  | R1 | R0 | D7       | D6         | D5      | D4       | D3          | D2      | D1      | D0       |

|-----------|----|----|----------|------------|---------|----------|-------------|---------|---------|----------|

| Status    | 0  | 0  | WuInt    | DoFaultInt | DiLvl   | QLvI     | C/QFaultInt | UV33Int | UV24Int | OTempInt |

| CQConfig  | 0  | 1  | RxFilter | HiSlew     | C/Q_N/P | C/Q_PP   | C/QDEn      | Q       | RxDis   | C/QLoad  |

| DIOConfig | 1  | 0  | Dolnv    | DoAv       | DoN/P   | DoPP     | DoEn        | DoBit   | LiDis   | DiLoad   |

| Mode      | 1  | 1  | RST      | WuIntEn    | DoFault | C/QFault | UV24        | OTemp   | UV33En  | LDO33Dis |

R1/R0 = Register address.

### **Status Register [R1, R0] = [0,0]**

| Bit             | D7    | D6         | D5    | D4   | D3          | D2      | D1      | D0       |

|-----------------|-------|------------|-------|------|-------------|---------|---------|----------|

| Bit Name        | WuInt | DoFaultInt | DiLvI | QLvI | C/QFaultInt | UV33Int | UV24Int | OTempInt |

| Read/Write      | R     | R          | R     | R    | R           | R       | R       | R        |

| POR State       | 0     | 0          | X     | X    | 0           | 0       | 0       | 0        |

| Reset Upon Read | Yes   | Yes        | No    | No   | Yes         | Yes     | Yes     | Yes      |

X = Unknown. These bits are dependent on the DI logic and C/Q inputs.

The Status register reflects the logic levels of C/Q and DI and shows the source of interrupts that cause an IRQ hardware interrupt. The IRQ interrupt is asserted when an alarm condition (OTemp, UV33Int, UV24, C/QFault, DoFault, Wulnt) is detected. All bits in the Status register are read-only. The interrupt bits return to the default state after the Status register is read. If a C/Q or DO fault condition persists, the associated interrupt bits are immediately set after the Status register is read.

| BIT | NAME       | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                         |

|-----|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| D7  | Wulnt      | <b>Wake-Up Interrupt Request.</b> Wulnt is set when an IO-Link wake-up request pulse is detected on C/Q and the WulntEn bit in the Mode register is set. $\overline{\text{IRQ}}$ asserts when Wulnt is set to 1. Read the Status register to clear the Wulnt bit and deassert $\overline{\text{IRQ}}$ .                                                                                                                             |

| D6  | DoFaultInt | <b>DO Fault Interrupt.</b> DoFaultInt interrupt bit and DoFault bit (in the Mode register) are set when a fault condition occurs on the DO driver output. The device registers a fault condition when a short circuit or voltage fault is detected on DO (see the <i>DO Fault Detection</i> section for more information). IRQ asserts when DoFaultInt is 1. Read the Status register to clear the DoFaultInt bit and deassert IRQ. |

| D5  | DiLvl      | <b>DI Logic Level.</b> The DiLvI bit mirrors the current logic level at the DI input. It is the inverse of the LI output and is always active regardless of the state of the LiDis bit (Table 2). DiLvI does not affect $\overline{\mbox{IRQ}}$ . DiLvI is not changed when the Status register is read.                                                                                                                            |

| BIT | NAME        | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|-----|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| D4  | QLvl        | <b>C/Q Logic Level.</b> The $\overline{\mathbb{Q}}$ Lvl bit is the inverse of the logic level at C/Q. $\overline{\mathbb{Q}}$ Lvl is 1 when the C/Q input level is low (< 8V) and is 0 when the C/Q logic level is high (> 13V) (Table 3). $\overline{\mathbb{Q}}$ Lvl remains active when the C/Q receiver is disabled (RxDis = 1). $\overline{\mathbb{Q}}$ Lvl does not affect $\overline{\mathbb{R}}$ Q. $\overline{\mathbb{Q}}$ Lvl is not changed when the Status register is read.                                                                                                                               |

| D3  | C/QFaultInt | <b>C/Q Fault Interrupt.</b> The C/QFaultInt interrupt bit and C/QFault bit (in the Mode register) are set when a short circuit or voltage fault occurs on the C/Q driver output (see the C/Q Fault Detection section for more information). IRQ asserts when C/QFault is 1. Read the Status register to clear the C/QFaultInt bit and deassert IRQ.                                                                                                                                                                                                                                                                    |

| D2  | UV33Int     | Internal 3.3V LDO (LDO33) Undervoltage Warning. Both the UV33Int interrupt bit and the UV33En bit (in the Mode register) are set when $V_{LDO33}$ falls below the 2.4V LDO33 undervoltage threshold. If UV33En is set in the Mode register, $\overline{IRQ}$ asserts low when the UV33Int bit is 1. Read the Status register to clear the UV33Int bit and deassert $\overline{IRQ}$ . Set the UV33En bit to 1 in the Mode register to enable undervoltage monitoring for UV33Int. When enabled, UV asserts high when the UV33Int bit is 1. UV deasserts when $V_{LDO33}$ rises above the LDO33 undervoltage threshold. |

| D1  | UV24Int     | <b>V<sub>CC</sub> Undervoltage Interrupt.</b> The UV24Int interrupt bit and the UV24 bit (in the Mode register) are set when the V <sub>CC</sub> voltage falls below the 7.4V undervoltage threshold. $\overline{\text{IRQ}}$ asserts low when the UV24Int bit is 1. Read the Status register to clear the UV24Int bit and deassert $\overline{\text{IRQ}}$ . V <sub>CC</sub> undervoltage detection cannot be disabled.                                                                                                                                                                                               |

| D0  | OTempInt    | Overtemperature Warning. The OTempInt interrupt bit and the OTemp bit (in the Mode register) are set when a high-temperature condition is detected by the device. OTemp is set when the temperature of the die exceeds +115°C (typ). OTempInt is set and IRQ asserts when the OTemp bit is 1. The OTempInt bit is cleared and IRQ deasserts when the Status register is read.  Once cleared, OTempInt is not reset if the die temperature remains above the thermal warning threshold and does not fall below +95°C.                                                                                                   |

Table 2. DiLvI and LI Output

| V <sub>DI</sub> (V) | DiLvl BIT | LI OUTPUT |

|---------------------|-----------|-----------|

| < 5.2               | 0         | High      |

| > 8                 | 1         | Low       |

Table 3. QLvl and RX Output

| V <sub>C/Q</sub> (V) | QLvI BIT | RX OUTPUT |  |  |

|----------------------|----------|-----------|--|--|

| < 8                  | 1        | High      |  |  |

| >13                  | 0        | Low       |  |  |

### CQConfig Register [R1, R0] = [0,1]

| Bit        | D7       | D6     | D5      | D4     | D3     | D2  | D1    | D0      |

|------------|----------|--------|---------|--------|--------|-----|-------|---------|

| Bit Name   | RxFilter | HiSlew | C/Q_N/P | C/Q_PP | C/QDEn | Q   | RxDis | C/QLoad |

| Read/Write | R/W      | R/W    | R/W     | R/W    | R/W    | R/W | R/W   | R/W     |

| POR State  | 0        | 0      | 0       | 0      | 0      | 0   | 0     | 0       |

Use the CQConfig register to control the C/Q receiver and driver parameters. All bits in the CQConfig register are read-write and are set to 0 at power-up.

| BIT | NAME     | DESCRIPTION                                                                                                                                                                                                                                                                                                                                               |

|-----|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| D7  | RxFilter | <b>C/Q and DI Receiver Filter Control.</b> The C/Q and DI receivers have analog lowpass filters to reduce high-frequency noise on the receiver inputs. Set the RxFilter bit to 0 to set the filter corner frequency to 500kHz. Set the RxFilter bit to 1 to set the filter corner frequency to 1MHz (this setting is used for high-speed COM3 operation). |

|     |          | Noise filters on C/Q and DI are controlled simultaneously by the RxFilter bit.                                                                                                                                                                                                                                                                            |

| D6  | HiSlew   | <b>Slew-Rate Control.</b> The HiSlew bit increases the slew rate for the C/Q and DO drivers and is used for high-speed COM3 (230kbps) data rates. Set HiSlew to 0 for COM1 and COM2 operation.                                                                                                                                                            |

| D5  | C/Q_N/P  | <b>C/Q Driver NPN/PNP Mode.</b> The $C/Q_N/P$ bit selects between low-side (NPN) and high-side (PNP) modes when the $C/Q$ driver is configured as an opendrain output ( $C/Q_PP = 0$ ). Set $C/Q_N/P$ to 1 to configure the driver for low-side (NPN) operation. Set $C/Q_N/P$ to 0 for high-side (PNP) operation.                                        |

| D4  | C/Q_PP   | <b>C/Q Driver Push-Pull Operation.</b> Set C/Q_PP to 1 to enable push-pull operation on the C/Q driver. The C/Q output is open-drain when C/Q_PP is 0.                                                                                                                                                                                                    |

| D3  | C/QDEn   | <b>C/Q Driver Enable/Disable.</b> Set the C/QDEn bit to 1 to enable the C/Q driver. Set C/QDEn to 0 for hardware (TXEN) control. See Table 4.                                                                                                                                                                                                             |

| D2  | Q        | <b>C/Q Driver Output Logic.</b> The Q bit can be used to program the C/Q output driver through software. The C/Q driver must be enabled and TXC = TXQ must be high to control the C/Q driver through the Q bit (Figure 8). C/Q has the same logic polarity as the Q bit.                                                                                  |

|     |          | Set the Q bit to 0 to control the C/Q driver with TXC and TXQ.                                                                                                                                                                                                                                                                                            |

|     |          | The C/Q driver output state depends on the C/Q_PP and C/Q_N/P bits as shown in Table 5. Note that Table 5 assumes that the C/Q driver is enabled (TXEN = $V_L$ or C/QDEn = 1).                                                                                                                                                                            |

| D1  | RxDis    | <b>C/Q Receiver Enable/Disable.</b> Set the RxDis bit to 1 to disable the C/Q receiver. The RX output is high when RxDis is 1.                                                                                                                                                                                                                            |

| D0  | C/QLoad  | <b>C/Q Current Sink Enable.</b> Set the C/QLoad bit to 1 to enable the internal current sink at C/Q.                                                                                                                                                                                                                                                      |

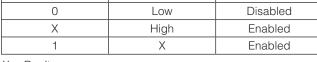

Table 4. C/QDEn and TXEN C/Q Driver **Control**

| C/QDEn | TXEN | C/Q DRIVER |  |  |

|--------|------|------------|--|--|

| 0      | Low  | Disabled   |  |  |

| X      | High | Enabled    |  |  |

| 1      | X    | Enabled    |  |  |

X = Don't care.

**Table 5. C/Q Driver Output State**

| TXC AND TXQ<br>(SEE NOTE) | Q | C/Q_PP | C/Q_N/P | C/Q CONFIGURATION | C/Q STATE                  |

|---------------------------|---|--------|---------|-------------------|----------------------------|

| High                      | 1 | 0      | 0       | PNP, open drain   | On, C/Q is high            |

| High                      | 0 | 0      | 0       | PNP, open drain   | Off, C/Q is high impedance |

| High                      | 1 | 0      | 1       | NPN, open drain   | Off, C/Q is high impedance |

| High                      | 0 | 0      | 1       | NPN, open drain   | On, C/Q is low             |

| High                      | 1 | 1      | Х       | Push-pull         | High                       |

| High                      | 0 | 1      | X       | Push-pull Low     |                            |

**Note:** TXC and TXQ =  $V_L$ .

X = Don't care.

### DIOConfig Register [R1, R0] = [1,0]

| Bit        | D7    | D6   | D5    | D4   | D3   | D2    | D1    | D0     |

|------------|-------|------|-------|------|------|-------|-------|--------|

| Bit Name   | Dolnv | DoAv | DoN/P | DoPP | DoEn | DoBit | LiDis | DiLoad |

| Read/Write | R/W   | R/W  | R/W   | R/W  | R/W  | R/W   | R/W   | R/W    |

| POR State  | 0     | 0    | 0     | 0    | 0    | 0     | 0     | 0      |

Use the DIOConfig register to control the DI and DO interfaces. All bits in the DIOConfig register are read-write and are set to 0 at power-up.

| BIT | NAME   | DESCRIPTION                                                                                                                                                                                                                                                                                        |

|-----|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| D7  | Dolnv  | <b>DO Output Polarity.</b> Set the Dolnv bit to 1 to invert the logic of the DO output. This bit also works in conjunction with the DoAv (Table 6). DO tracks the TXC and TXQ inputs with the opposite polarity when both the DoAv and Dolnv bits are set.                                         |

| D6  | DoAv   | <b>DO Antivalent Operation.</b> Set the DoAv bit to 1 to enable antivalent output operation on DO. DO tracks the TXC and TXQ inputs (and the Q bit) when DoAv is 1 (Table 6).                                                                                                                      |

|     |        | The LO input and the DoBit are ignored when the DoAv bit is 1.                                                                                                                                                                                                                                     |

| D5  | DoN/P  | <b>DO Driver NPN/PNP Operation.</b> The DoN/P bit selects between low-side (NPN) and high-side (PNP) modes when the DO driver is configured as an open-drain output (DoPP = 0). Set DoN/P to 1 to configure the driver for low-side (NPN) operation. Set DoN/P to 0 for high-side (PNP) operation. |

| D4  | DoPP   | <b>DO Driver Push-Pull Operation.</b> Set the DoPP bit to 1 to configure the DO driver output for push-pull operation. DO is an open-drain output when DoPP is 0.                                                                                                                                  |