### **General Description**

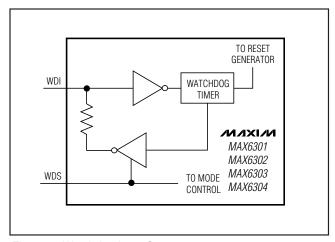

The MAX6301-MAX6304\* low-power microprocessor (µP) supervisory circuits provide maximum adjustability for reset and watchdog functions. The reset threshold can be adjusted to any voltage above 1.22V, using external resistors. In addition, the reset and watchdog timeout periods are adjustable using external capacitors. A watchdog select pin extends the watchdog timeout period to 500x. The reset function features immunity to power-supply transients.

These four devices differ only in the structure of their reset outputs (see the Selector Guide). The MAX6301-MAX6304 are available in the space-saving 8-pin µMAX® package, as well as 8-pin PDIP and SO packages.

### **Applications**

Medical Equipment Intelligent Instruments Portable Equipment Battery-Powered Computers/Controllers **Embedded Controllers** Critical µP Monitoring Set-Top Boxes Computers

#### Selector Guide

| FEATURE                    | MAX6301            | MAX6302            | MAX6303            | MAX6304            |

|----------------------------|--------------------|--------------------|--------------------|--------------------|

| Active-Low<br>Reset        | $\sqrt{}$          | _                  | $\sqrt{}$          | _                  |

| Active-High<br>Reset       | _                  | $\sqrt{}$          | _                  | <b>V</b>           |

| Open-Drain<br>Reset Output | V                  | $\sqrt{}$          | _                  | _                  |

| Push-Pull<br>Reset Output  | _                  | _                  | V                  | <b>V</b>           |

| Pin-Package                | 8-PDIP/SO/<br>µMAX | 8-PDIP/SO/<br>µMAX | 8-PDIP/SO/<br>µMAX | 8-PDIP/SO/<br>µMAX |

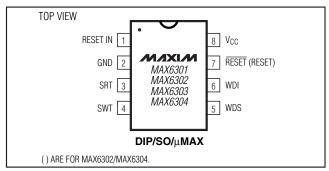

# **Pin Configuration**

µMAX is a registered trademark of Maxim Integrated Products, Inc.

## **Features**

- ◆ Adjustable Reset Threshold

- ♦ Adjustable Reset Timeout

- **♦ Adjustable Watchdog Timeout**

- **♦** 500x Watchdog Timeout Multiplier

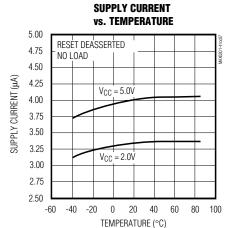

- ♦ 4µA Supply Current

- **♦ RESET or RESET Output Options**

- **♦ Push-Pull or Open-Drain Output Options**

- ♦ Guaranteed RESET Asserted At or Above  $V_{CC} = 1V (MAX6301/MAX6303)$

- **♦ Power-Supply Transient Immunity**

- ♦ Watchdog Function can be Disabled

- ♦ PDIP/SO/µMAX Packages Available

### **Ordering Information**

| PART       | TEMP RANGE     | PIN-PACKAGE |

|------------|----------------|-------------|

| MAX6301CPA | 0°C to +70°C   | 8 PDIP      |

| MAX6301CSA | 0°C to +70°C   | 8 SO        |

| MAX6301CUA | 0°C to +70°C   | 8 µMAX      |

| MAX6301EPA | -40°C to +85°C | 8 PDIP      |

| MAX6301ESA | -40°C to +85°C | 8 SO        |

Devices are available in both leaded and lead(Pb)-free/RoHScompliant packaging. Specify lead-free by adding the "+" symbol at the end of the part number when ordering.

Ordering Information continued at end of data sheet.

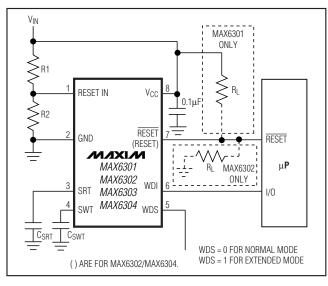

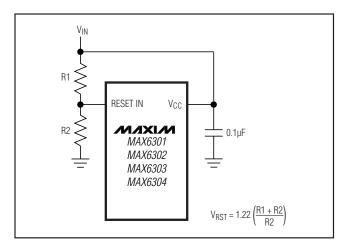

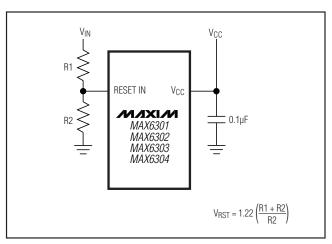

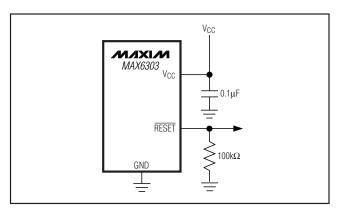

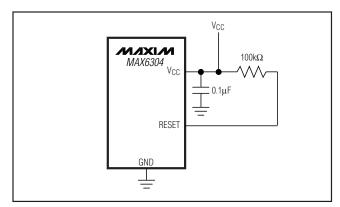

# Typical Operating Circuit

Maxim Integrated Products 1

### **ABSOLUTE MAXIMUM RATINGS**

| V <sub>C</sub> C        | -0.3V to +7.0V              |

|-------------------------|-----------------------------|

| RESET IN, SWT, SRT      | $0.3V$ to $(V_{CC} + 0.3V)$ |

| WDI, WDS                | 0.3V to +7.0V               |

| RESET, RESET            |                             |

| MAX6301                 | 0.3V to +7.0V               |

| MAX6302/MAX6303/MAX6304 | 0.3V to $(V_{CC} + 0.3V)$   |

| Input Current           |                             |

| V <sub>CC</sub>         | ±20mA                       |

| GND                     | ±20mA                       |

| Output Current          |                             |

| RESET, RESET            | ±20mA                       |

| Continuous Power Dissipation (T <sub>A</sub> = +70°C)<br>PDIP (derate 9.09mW/°C above +70°C)<br>SO (derate 5.88mW/°C above +70°C) | 471mW          |

|-----------------------------------------------------------------------------------------------------------------------------------|----------------|

| μMAX (derate 4.10mW/°C above +70°C)                                                                                               | 330mW          |

| Operating Temperature Range                                                                                                       |                |

| MAX630_C_A                                                                                                                        | 0°C to +70°C   |

| MAX630_E_A                                                                                                                        | 40°C to +85°C  |

| Storage Temperature Range                                                                                                         | 65°C to +160°C |

| Lead Temperature (soldering, 10s)                                                                                                 | +300°C         |

| Soldering Temperature (reflow)                                                                                                    |                |

| Lead(Pb)-free                                                                                                                     | +260°C         |

| Containing Lead (Pb)                                                                                                              |                |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **ELECTRICAL CHARACTERISTICS**

$(V_{CC} = +2V \text{ to } +5.5V, T_A = T_{MIN} \text{ to } T_{MAX}, \text{ unless otherwise noted.}$  Typical values are at  $V_{CC} = +5V$  and  $T_A = +25^{\circ}C.)$

| PARAMETER                                         | SYMBOL             |                                           | CONDITIONS                                                                  | MIN                                                                                   | TYP                   | MAX   | UNITS |  |

|---------------------------------------------------|--------------------|-------------------------------------------|-----------------------------------------------------------------------------|---------------------------------------------------------------------------------------|-----------------------|-------|-------|--|

|                                                   |                    | MAX6301C/I                                | MAX6303C                                                                    | 1.00                                                                                  |                       | 5.50  |       |  |

| Operating Voltage Range (Note 1)                  | Vcc                | MAX6301E/N                                | MAX6301E/MAX6303E                                                           |                                                                                       |                       | 5.50  | V     |  |

| (Note 1)                                          |                    | MAX6302/MAX6304                           |                                                                             | 1.31                                                                                  |                       | 5.50  |       |  |

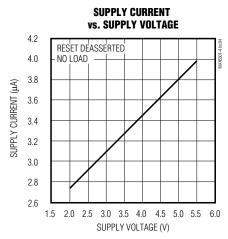

| Supply Current (Note 2)                           | Icc                | No load                                   |                                                                             |                                                                                       | 4.0                   | 7.0   | μΑ    |  |

| RESET TIMER                                       |                    |                                           |                                                                             |                                                                                       |                       |       |       |  |

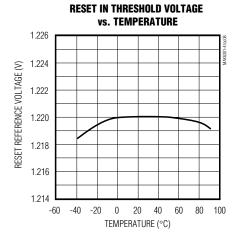

| Deact Input Threshold Voltage                     | \/                 | V <sub>RESET IN</sub> fa                  | lling, $V_{CC} = 5.0V$                                                      | 1.195                                                                                 | 1.220                 | 1.245 | V     |  |

| Reset Input Threshold Voltage                     | V <sub>TH</sub>    | V <sub>RESET IN</sub> ris                 | sing, V <sub>CC</sub> = 5.0V                                                |                                                                                       | 1.240                 | 1.265 | V     |  |

| Reset Input Hysteresis                            | V <sub>H</sub> YST |                                           |                                                                             |                                                                                       | 20                    |       | mV    |  |

| Reset Input Leakage Current                       | IRESET IN          |                                           |                                                                             |                                                                                       | ±0.01                 | ±1    | nA    |  |

|                                                   |                    | V <sub>CC</sub> ≥ 4.5V,                   | ISOURCE = 0.8mA                                                             | Vcc - 0.4                                                                             | 1                     |       |       |  |

| Reset Output-Voltage High                         | Vон                | VCC = 2V, ISOURCE = 0.4mA                 |                                                                             |                                                                                       | V <sub>C</sub> C - 0. | 4     |       |  |

| (MAX6302/MAX6303/MAX6304)                         |                    | MAX6302/MAX6304, V <sub>CC</sub> = 1.31V, |                                                                             | V <sub>CC</sub> -                                                                     |                       |       | ]     |  |

|                                                   |                    | $R_L = 10k\Omega$                         |                                                                             |                                                                                       |                       |       |       |  |

|                                                   | V <sub>OL</sub>    | $V_{CC} \ge 4.5V$ , $I_{SINK} = 3.2mA$    |                                                                             |                                                                                       |                       | 0.4   |       |  |

|                                                   |                    | VCC = 2V, ISINK = 1.6mA                   |                                                                             |                                                                                       |                       | 0.4   |       |  |

| Reset Output-Voltage Low (MAX6301/MAX6303/MAX6304 |                    | MAX6301/                                  | $V_{CC} = 1V$ , $I_{SINK} = 50\mu A$ , $T_A = 0^{\circ}C$ to $+70^{\circ}C$ |                                                                                       |                       | 0.3   | V     |  |

|                                                   |                    | MAX6303                                   | MAX6303                                                                     | V <sub>CC</sub> = 1.2V, I <sub>SINK</sub> = 100μA,<br>T <sub>A</sub> = -40°C to +85°C |                       |       | 0.3   |  |

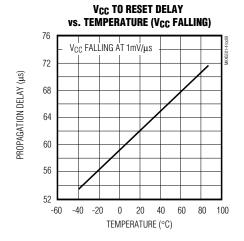

| V <sub>CC</sub> to Reset Delay                    | t <sub>RD</sub>    | V <sub>CC</sub> = falling at 1mV/μs       |                                                                             |                                                                                       | 63                    |       | μs    |  |

| Reset Input Pulse Width                           | t <sub>RI</sub>    | Comparator overdrive = 50mV               |                                                                             |                                                                                       | 26                    |       | μs    |  |

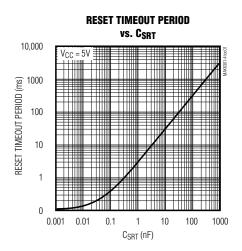

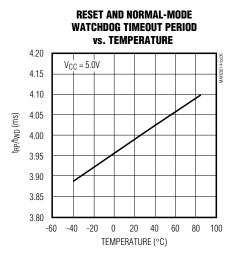

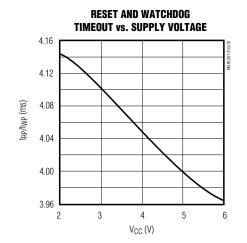

| Reset Timeout Period (Note 3)                     | t <sub>RP</sub>    | C <sub>SRT</sub> = 1500pF                 |                                                                             | 2.8                                                                                   | 4.0                   | 5.2   | ms    |  |

| Book Output Looks as Comment                      |                    | MAX6301, V                                | RESET = VCC                                                                 |                                                                                       |                       | ±1    |       |  |

| Reset Output Leakage Current                      |                    | MAX6302, V                                | RESET = VGND                                                                |                                                                                       |                       | ±1    | μΑ    |  |

## **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{CC} = +2V \text{ to } +5.5V, T_A = T_{MIN} \text{ to } T_{MAX}, \text{ unless otherwise noted.}$  Typical values are at  $V_{CC} = +5V$  and  $T_A = +25^{\circ}C.)$

| PARAMETER                        | SYMBOL          | CONDITIONS                                        | MIN                   | TYP | MAX                   | UNITS |  |

|----------------------------------|-----------------|---------------------------------------------------|-----------------------|-----|-----------------------|-------|--|

| WATCHDOG TIMER                   |                 |                                                   |                       |     |                       |       |  |

| WDI, WDS Input Threshold         | V <sub>IH</sub> |                                                   | 0.7 x V <sub>CC</sub> |     |                       | V     |  |

| WDI, WDS Input Threshold         | V <sub>IL</sub> |                                                   |                       |     | 0.3 x V <sub>CC</sub> | V     |  |

| WDI Pulse Width                  | t               | V <sub>CC</sub> = 4.5V to 5.5V                    | 30                    |     |                       | 200   |  |

|                                  | twp             | V <sub>CC</sub> = 2V to 4.5V                      | 60                    |     |                       | ns    |  |

| WDI, WDS Leakage Current         |                 | Extended mode disabled                            |                       |     | ±1                    | μΑ    |  |

| WDI Sink/Source Current (Note 4) |                 | Extended mode enabled                             |                       | ±70 |                       | μΑ    |  |

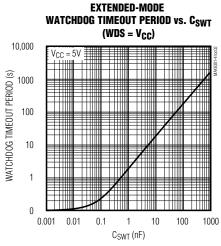

| Watchdog Timeout Period          | turo            | WDS = GND, C <sub>SWT</sub> = 1500pF              | 2.8                   | 4.0 | 5.2                   | ms    |  |

| (Note 3)                         | tw□             | WDS = V <sub>CC</sub> , C <sub>SWT</sub> = 1500pF | 1.4                   | 2.0 | 2.6                   | S     |  |

Note 1: Reset is guaranteed valid from the selected reset threshold voltage down to the minimum V<sub>CC</sub>.

**Note 2:** WDS =  $V_{CC}$ , WDI unconnected.

**Note 3:** Precision timing currents of 500nA are present at both the SRT and SWT pins. Timing capacitors connected to these nodes must have low leakage consistent with these currents to prevent timing errors.

Note 4: The sink/source is supplied through a resistor, and is proportional to V<sub>CC</sub> (Figure 8). At V<sub>CC</sub> = 2V, it is typically ±24µA.

# **Typical Operating Characteristics**

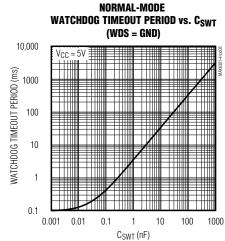

(CswT = CsRT = 1500pF, TA = +25°C, unless otherwise noted.)

### Typical Operating Characteristics (continued)

$(C_{SWT} = C_{SRT} = 1500pF, T_A = +25^{\circ}C, unless otherwise noted.)$

# **Pin Description**

| PIN | NAME                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                               | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                |  |  |  |  |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 1   | RESET IN                                                                                                                                                           | Reset Input. High-impedance input to the reset comparator. Connect this pin to the center point of an external resistor voltage-divider network to set the reset threshold voltage. The reset threshold voltage is calculated as follows: V <sub>RST</sub> = 1.22 x (R1 + R2)/R2 (see the <i>Typical Operating Circuit</i> ). |                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                |  |  |  |  |

| 2   | GND                                                                                                                                                                | Ground                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                |  |  |  |  |

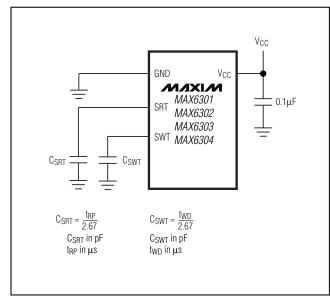

| 3   | SRT                                                                                                                                                                | •                                                                                                                                                                                                                                                                                                                             | ct a capacitor between this input and ground to select the reset timeout od as follows: $t_{RP}=2.67 \times C_{SRT}$ , with $C_{SRT}$ in pF and $t_{RP}$ in $\mu s$ (see the                                                                                                                                                                                                                                |                                                                                                                |  |  |  |  |

| 4   | SWT                                                                                                                                                                | watchdog timeout period (twD).                                                                                                                                                                                                                                                                                                | connect a capacitor between this input and ground to select the basic Determine the period as follows: $t_{WD} = 2.67 \times C_{SWT}$ , with $C_{SWT}$ in pF and n can be disabled by connecting this pin to ground.                                                                                                                                                                                        |                                                                                                                |  |  |  |  |

| 5   | WDS                                                                                                                                                                | Watchdog-Select Input. This input selects the watchdog mode. Connect to ground to select normal mand the basic watchdog timeout period. Connect to V <sub>CC</sub> to select extended mode, multiplying the batimeout period by a factor of 500. A change in the state of this pin resets the watchdog timer to zero.         |                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                |  |  |  |  |

| 6   | WDI                                                                                                                                                                | period, or a reset pulse will occu<br>the watchdog timeout period. The<br>WDS. The watchdog timer is cle                                                                                                                                                                                                                      | Ing transition must occur on this input within the selected watchdog timeout $\alpha$ are the capacitor value selected for SWT and the state of WDS determine the watchdog timer clears and restarts when a transition occurs on WDI or ared when reset is asserted and restarted after reset deasserts. In the $S = V_{CC}$ , the watchdog function can be disabled by driving WDI with a WDI unconnected. |                                                                                                                |  |  |  |  |

|     | RESET Output (MAX6301) Open-Drain, Active-Low Reset Idro                                                                                                           |                                                                                                                                                                                                                                                                                                                               | RESET changes from high to low whenever the monitored voltage (V <sub>IN</sub> ) drops below the selected reset threshold (V <sub>RST</sub> ). RESET remains low as long as V <sub>IN</sub> is below V <sub>RST</sub> . Once V <sub>IN</sub> exceeds V <sub>RST</sub> , RESET remains low for the reset timeout period and then goes high. The watchdog timer                                               |                                                                                                                |  |  |  |  |

| 7   | Push-Pull, Active-Low Reset Output (MAX6303)  RESET (MAX6302/ MAX6304  Push-Pull, Active-High Rese Output (MAX6302)  Push-Pull, Active-High Reset Output (MAX6304) | Output (MAX6303)                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                             | triggers a reset pulse (t <sub>RP</sub> ) whenever the watchdog timeout period (t <sub>WD</sub> ) is exceeded. |  |  |  |  |

| 7   |                                                                                                                                                                    | Open-Drain, Active-High Reset<br>Output (MAX6302)                                                                                                                                                                                                                                                                             | RESET changes from low to high whenever the monitored voltage (V <sub>IN</sub> ) drops below the selected reset threshold (V <sub>RST</sub> ). RESET remains high as long as V <sub>IN</sub> is below V <sub>RST</sub> . Once V <sub>IN</sub> exceeds V <sub>RST</sub> , RESET remains high for the reset timeout period and then goes low. The watchdog timer                                              |                                                                                                                |  |  |  |  |

|     |                                                                                                                                                                    | _                                                                                                                                                                                                                                                                                                                             | triggers a reset pulse (t <sub>RP</sub> ) whenever the watchdog timeout period (t <sub>WD</sub> ) is exceeded.                                                                                                                                                                                                                                                                                              |                                                                                                                |  |  |  |  |

| 8   | Vcc                                                                                                                                                                | Supply Voltage. Bypass to ground with a 0.1µF capacitor placed as close as possible to the pin.                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                |  |  |  |  |

### **Detailed Description**

#### **Reset Function/Output**

The reset output is typically connected to the reset input of a  $\mu P$ . A  $\mu P$ 's reset input starts or restarts the  $\mu P$  in a known state. The MAX6301–MAX6304  $\mu P$  supervisory circuits provide the reset logic to prevent code-execution errors during power-up, power-down, and brownout conditions (see the *Typical Operating Circuit*).

For the MAX6301/MAX6303, RESET changes from high to low whenever the monitored voltage (VIN) drops below the reset threshold voltage (VRST). RESET remains low as long as VIN is below VRST. Once VIN exceeds VRST, RESET remains low for the reset timeout period, then goes high. When a reset is asserted due to a watchdog timeout condition, RESET stays low for the reset timeout period. Any time reset asserts, the watchdog timer clears. At the end of the reset timeout period, RESET goes high and the watchdog timer is restarted from zero. If the watchdog timeout period is exceeded again, then RESET goes low again. This cycle continues unless WDI receives a transition.

On power-up, once  $V_{CC}$  reaches 1V,  $\overline{RESET}$  is guaranteed to be a logic-low. For information about applications where  $V_{CC}$  is less than 1V, see the *Ensuring a Valid RESET/RESET Output Down to V\_{CC} = 0V (MAX6303/MAX6304)* section. As  $V_{CC}$  rises,  $\overline{RESET}$  remains low. When  $V_{IN}$  rises above  $V_{RST}$ , the reset timer starts and  $\overline{RESET}$  remains low. When the reset timeout period ends,  $\overline{RESET}$  goes high.

On power-down, once  $V_{IN}$  goes below  $V_{RST}$ ,  $\overline{RESET}$  goes low and is guaranteed to be low until  $V_{CC}$  drops below 1V. For information about applications where  $V_{CC}$  is less than 1V, see the *Ensuring a Valid RESET/RESET Output Down to V\_{CC} = OV (MAX6303/MAX6304)* section.

The MAX6302/MAX6304 active-high RESET output is the inverse of the MAX6301/MAX6303 active-low  $\overline{\text{RESET}}$  output, and is guaranteed valid for  $V_{CC} > 1.31V$ .

#### Reset Threshold

These supervisors monitor the voltage on RESET IN. The MAX6301–MAX6304 have an adjustable reset threshold voltage (VRST) set with an external resistor voltage-divider (Figure 1). Use the following formula to calculate VRST (the point at which the monitored voltage triggers a reset):

$$V_{RST} = \frac{V_{TH} \times (R1 + R2)}{R2} (V)$$

where  $V_{RST}$  is the desired reset threshold voltage and  $V_{TH}$  is the reset input threshold (1.22V). Resistors R1

Figure 1. Calculating the Reset Threshold Voltage (V<sub>RST</sub>)

and R2 can have very high values to minimize current consumption. Set R2 to some conveniently high value (1M $\Omega$ , for example) and calculate R1 based on the desired reset threshold voltage, using the following formula:

$$R1 = R2 \times \left(\frac{VRST}{V_{TH}} - 1\right) \left(\Omega\right)$$

#### **Watchdog Timer**

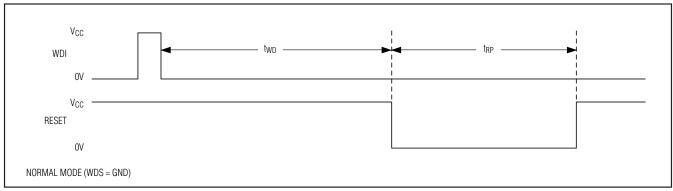

The watchdog circuit monitors the  $\mu P$ 's activity. If the  $\mu P$  does not toggle the watchdog input (WDI) within twp (user selected), reset asserts. The internal watchdog timer is cleared by reset, by a transition at WDI (which can detect pulses as short as 30ns), or by a transition at WDS. The watchdog timer remains cleared while reset is asserted; as soon as reset is released, the timer starts counting (Figure 2).

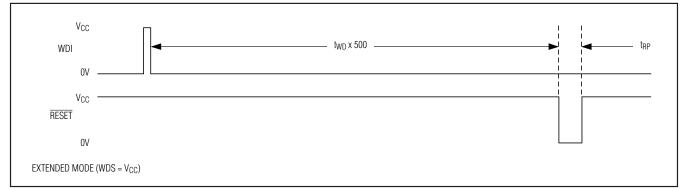

The MAX6301–MAX6304 feature two modes of watchdog timer operation: normal mode and extended mode. In normal mode (WDS = GND), the watchdog timeout period is determined by the value of the capacitor connected between SWT and ground (see the *Selecting the Reset and Watchdog Timeout Capacitor* section). In extended mode (WDS = VCC), the watchdog timeout period is multiplied by 500. For example, in the extended mode, a 1 $\mu$ F capacitor gives a watchdog timeout period of 22 minutes (see the Extended-Mode Watchdog Timeout Period vs. CSWT graph in the *Typical Operating Characteristics*).

In extended mode, the watchdog function can be disabled by leaving WDI unconnected or by three-stating the driver connected to WDI. In this mode, the watchdog input is internally driven low during the watchdog timeout period, then momentarily pulses high, resetting the

Figure 2a. Watchdog Timing Diagram, WDS = GND

Figure 2b. Watchdog Timing Diagram, WDS = VCC

watchdog counter. When WDI is left unconnected, the watchdog timer is cleared by this internal driver just before the timeout period is reached (the internal driver pulls WDI high at about 94% of  $t_{WD}$ ). When WDI is three-stated, the maximum allowable leakage current of the device driving WDI is  $t_{WD}$ .

In normal mode (WDS = GND), the watchdog timer cannot be disabled by three-stating WDI. WDI is a high-impedance input in this mode. Do not leave WDI unconnected in normal mode.

# \_Applications Information

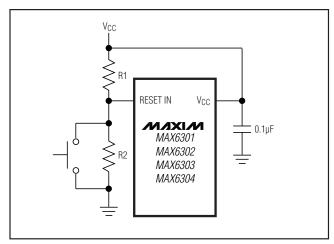

#### Selecting the Reset and Watchdog Timeout Capacitor

The reset timeout period is adjustable to accommodate a variety of  $\mu P$  applications. Adjust the reset timeout period (tRP) by connecting a specific value capacitor (CSRT) between SRT and ground (Figure 3). Calculate the reset timeout capacitor as follows:

$C_{SRT} = t_{RP}/2.67$

Figure 3. Calculating the Reset (C<sub>SRT</sub>) and Watchdog (C<sub>SWT</sub>) Timeout Capacitor Values

Figure 4. Monitoring Votlages Other than VCC

with CSRT in pF and tRP in  $\mu$ s. CSRT must be a low-leakage (< 10nA) type capacitor. Ceramic is recommended.

The watchdog timeout period is adjustable to accommodate a variety of  $\mu P$  applications. With this feature, the watchdog timeout can be optimized for software execution. The programmer can determine how often the watchdog timer should be serviced. Adjust the watchdog timeout period (twp) by connecting a specific value capacitor (CSWT) between SWT and ground (Figure 3). For normal-mode operation, calculate the watchdog timeout capacitor as follows:

$$C_{SWT} = t_{WD} / 2.67$$

where  $C_{SWT}$  is in pF and  $t_{WD}$  is in  $\mu s$ .  $C_{SWT}$  must be a low-leakage (< 10nA) type capacitor. Ceramic is recommended.

#### **Monitoring Voltages Other than Vcc**

The *Typical Operating Circuit* monitors V<sub>CC</sub>. Voltages other than V<sub>CC</sub> can easily be monitored, as shown in Figure 4. Calculate V<sub>RST</sub> as shown in the *Reset Threshold* section.

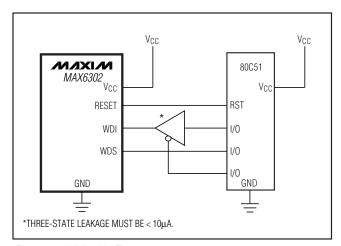

### Wake-Up Timer

In some applications, it is advantageous to put a  $\mu P$  into sleep mode, periodically wake it up to perform checks and/or tasks, then put it back into sleep mode. The MAX6301 family of supervisors can easily accommodate this technique. Figure 5 illustrates an example using the MAX6302 and an 80C51.

In Figure 5, just before the  $\mu C$  puts itself into sleep mode, it pulls WDS high. The  $\mu C$ 's I/O pins maintain their logic levels while in sleep mode and WDS remains high. This places the MAX6302 in extended mode, increasing the watchdog timeout 500 times. When the

Figure 5. Wake-Up Timer

watchdog timeout period ends, a reset is applied on the 80C51, waking it up to perform tasks. While the  $\mu P$  is performing tasks, the 80C51 pulls WDS low (selecting normal mode), and the MAX6302 monitors the  $\mu P$  for hang-ups. When the  $\mu P$  finishes its tasks, it puts itself back into sleep mode, drives WDS high, and starts the cycle over again. This is a power-saving technique, since the  $\mu P$  is operating only part of the time and the MAX6302 has very low quiescent current.

#### **Adding a Manual Reset Function**

A manual reset option can easily be implemented by connecting a normally open momentary switch in parallel with R2 (Figure 6). When the switch is closed, the voltage on RESET IN goes to zero, initiating a reset. When the switch is released, the reset remains asserted for the reset timeout period and then is cleared. The pushbutton switch is effectively debounced by the reset timer.

Figure 6. Adding a Manual Reset Function

Figure 7. Interfacing to µPs with Bidirectional Reset I/O Pins

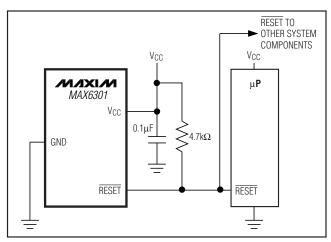

# Interfacing to µPs with Bidirectional Reset Pins

Since  $\overline{\text{RESET}}$  is open-drain, the MAX6301 interfaces easily with  $\mu\text{Ps}$  that have bidirectional reset pins, such as the Motorola 68HC11 (Figure 7). Connecting  $\overline{\text{RESET}}$  directly to the  $\mu\text{P's}$  reset pin with a single pullup allows either device to assert reset.

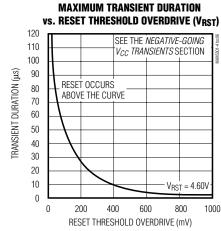

#### **Negative-Going Vcc Transients**

In addition to issuing a reset to the  $\mu P$  during power-up, power-down, and brownout conditions, these supervisors are relatively immune to short-duration negative-going transients (glitches). The Maximum Transient Duration vs. Reset Threshold Overdrive graph in the *Typical Operating Characteristics* shows this relationship.

The area below the curves of the graph is the region in which these devices typically do not generate a reset pulse. This graph was generated using a negative-going pulse applied to V<sub>IN</sub>, starting above the actual reset threshold (V<sub>RST</sub>) and ending below it by the magnitude indicated (reset-threshold overdrive). As the magnitude of the transient increases (farther below the reset threshold), the maximum allowable pulse width decreases. Typically, a V<sub>CC</sub> transient that goes 100mV below the reset threshold and lasts 50µs or less will not cause a reset pulse to be issued.

Figure 8. Watchdog Input Structure

### **Watchdog Input Current**

#### Extended Mode

In extended mode (WDS =  $V_{CC}$ ), the WDI input is internally driven through a buffer and series resistor from the watchdog counter (Figure 8). When WDI is left unconnected, the watchdog timer is serviced within the watchdog timeout period by a very brief low-high-low pulse from the counter chain. For minimum watchdog input current (minimum overall power consumption), leave WDI low for the majority of the watchdog timeout period, pulsing it low-high-low (> 30ns) once within the period to reset the watchdog timer. If instead WDI is externally driven high for the majority of the timeout period, typically 70 $\mu$ A can flow into WDI.

#### Normal Mode

In normal mode (WDS = GND), the internal buffer that drives WDI is disabled. In this mode, WDI is a standard CMOS input and leakage current is typically 100pA, regardless of whether WDI is high or low.

# Ensuring a Valid $\overline{RESET}/RESET$ Output Down to VCC = OV (MAX6303/MAX6304)

When V<sub>CC</sub> falls below 1V, RESET/RESET current sinking (sourcing) capabilities decline drastically. In the case of the MAX6303, high-impedance CMOS-logic inputs connected to RESET can drift to undetermined voltages. This presents no problem in most applications, since most µPs and other circuitry do not operate with V<sub>CC</sub> below 1V.

Figure 9. Ensuring  $\overline{RESET}$  Valid to  $V_{CC} = 0V$

In those applications where  $\overline{\text{RESET}}$  must be valid down to 0V, adding a pulldown resistor between  $\overline{\text{RESET}}$  and ground sinks any stray leakage currents, holding  $\overline{\text{RESET}}$  low (Figure 9). The value of the pulldown resistor is not critical;  $100\text{k}\Omega$  is large enough not to load  $\overline{\text{RESET}}$  and small enough to pull  $\overline{\text{RESET}}$  to ground. For applications using the MAX6304, a  $100\text{k}\Omega$  pullup resistor between RESET and VCC will hold RESET high when VCC falls below 1V (Figure 10).

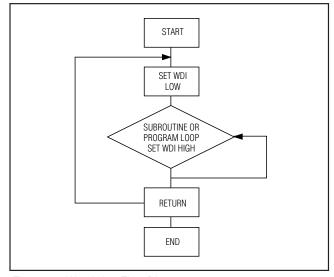

#### **Watchdog-Software Considerations**

To help the watchdog timer monitor software execution more closely, set and reset the watchdog input at different points in the program, rather than pulsing the watchdog input high-low-high or low-high-low. This technique avoids a stuck loop in which the watchdog timer would continue to be reset within the loop, keeping the watchdog from timing out.

Figure 11 shows an example of a flow diagram where the I/O driving the watchdog input is set high at the beginning of the program, set low at the beginning of every subroutine or loop, then set high again when the program returns to the beginning. If the program should hang in any subroutine the problem would quickly be corrected, since the I/O is continually set low and the watchdog timer is allowed to time out, causing a reset or interrupt to be issued. When using extended mode, as described in the *Watchdog Input Current* section, this scheme does result in higher average WDI input current than does the method of leaving WDI low for the majority of the timeout period and periodically pulsing it low-high-low.

## Layout Considerations

SRT and SWT are precision current sources. When developing the layout for the application, be careful to minimize board capacitance and leakage currents around these pins. Traces connected to these pins

Figure 10. Ensuring RESET Valid to VCC = 0V

Figure 11. Watchdog Flow Diagram

should be kept as short as possible. Traces carrying high-speed digital signals and traces with large voltage potentials should be routed as far from these pins as possible. Leakage currents and stray capacitance (e.g., a scope probe) at these pins could cause errors in the reset and/or watchdog timeout period. When evaluating these parts, use clean prototype boards to ensure accurate reset and watchdog timeout periods.

RESET IN is a high-impedance input that is typically driven by a high-impedance resistor-divider network (e.g.,  $1M\Omega$  to  $10M\Omega$ ). Minimize coupling to transient signals by keeping the connections to this input short. Any DC leakage current at RESET IN (e.g., a scope probe) causes errors in the programmed reset threshold. Note that sensitive pins are located on the GND side of the device, away from the digital I/O, to simplify board layout.

# **Ordering Information (continued)**

|            |                | - <i>-</i>  |

|------------|----------------|-------------|

| PART       | TEMP RANGE     | PIN-PACKAGE |

| MAX6302CPA | 0°C to +70°C   | 8 PDIP      |

| MAX6302CSA | 0°C to +70°C   | 8 SO        |

| MAX6302CUA | 0°C to +70°C   | 8 µMAX      |

| MAX6302EPA | -40°C to +85°C | 8 PDIP      |

| MAX6302ESA | -40°C to +85°C | 8 SO        |

| MAX6303CPA | 0°C to +70°C   | 8 PDIP      |

| MAX6303CSA | 0°C to +70°C   | 8 SO        |

| MAX6303CUA | 0°C to +70°C   | 8 µMAX      |

| MAX6303EPA | -40°C to +85°C | 8 PDIP      |

| MAX6303ESA | -40°C to +85°C | 8 SO        |

| MAX6304CPA | 0°C to +70°C   | 8 PDIP      |

| MAX6304CSA | 0°C to +70°C   | 8 SO        |

| MAX6304CUA | 0°C to +70°C   | 8 µMAX      |

| MAX6304EPA | -40°C to +85°C | 8 PDIP      |

| MAX6304ESA | -40°C to +85°C | 8 SO        |

Devices are available in both leaded and lead(Pb)-free/RoHS-compliant packaging. Specify lead-free by adding the "+" symbol at the end of the part number when ordering.

## \_Chip Information

PROCESS: CMOS

## Package Information

For the latest package outline information and land patterns, go to **www.maxim-ic.com/packages**. Note that a "+", "#", or "-" in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.

|   | PACKAGE<br>TYPE | PACKAGE<br>CODE | OUTLINE NO.    | LAND<br>PATTERN NO. |

|---|-----------------|-----------------|----------------|---------------------|

|   | 8 PDIP          | P8-1            | <u>21-0043</u> | _                   |

|   | 8 SO            | S8-2            | <u>21-0041</u> | <u>90-0096</u>      |

| I | 8 µMAX          | U8-1            | <u>21-0036</u> | 90-0092             |

### **Revision History**

| REVISION<br>NUMBER | REVISION DATE                           | DESCRIPTION                                                                           | PAGES<br>CHANGED |

|--------------------|-----------------------------------------|---------------------------------------------------------------------------------------|------------------|

| 0                  | 7/96                                    | Initial release                                                                       | _                |

| 1                  | 1 12/05 Added lead-free notation.       |                                                                                       | 1, 11            |

| 2                  | 3/07 Updated Typical Operating Circuit. |                                                                                       | 1                |

| 3                  | 3/09                                    | Updated Pin Description, Applications Information, Figure 3, and Package Information. | 5, 7, 11         |

| 4                  | 9/10                                    | Updated Absolute Maximum Ratings, correct part number.                                | 2, 9, 11, 12     |

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.