19-3594; Rev 0; 2/05

EVALUATION KIT AVAILABLE

# **EEPROM-Programmable, Hex Power-Supply Supervisory Circuits**

## **General Description**

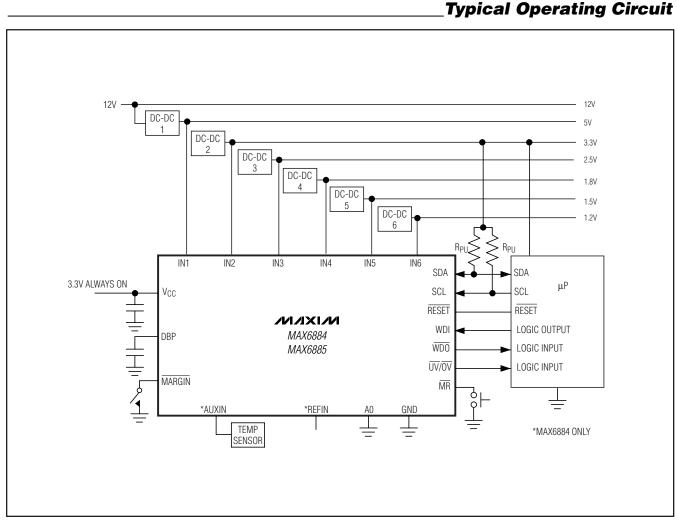

The MAX6884/MAX6885 EEPROM-configurable, multivoltage power-supply supervisors monitor six voltagedetector inputs, one auxiliary input, and one watchdog input, and feature three programmable outputs for highly configurable power-supply monitoring applications. Manual reset and margin disable inputs offer additional flexibility.

Each voltage-detector input offers a programmable primary undervoltage and secondary undervoltage/overvoltage threshold. Voltage-detector inputs IN1–IN6 monitor voltages from 1V to 5.8V in 20mV increments or 0.5V to 3.05V in 10mV increments.

Programmable outputs RESET, UV/OV, and WDO provide system resets/interrupts. Programmable output options include open-drain or weak pullup. Programmable timing delay blocks configure each output to wait between 25µs and 1600ms after their respective assertion-causing conditions have been cleared. A fault register logs condition-causing events (undervoltage, overvoltage, manual reset, etc.).

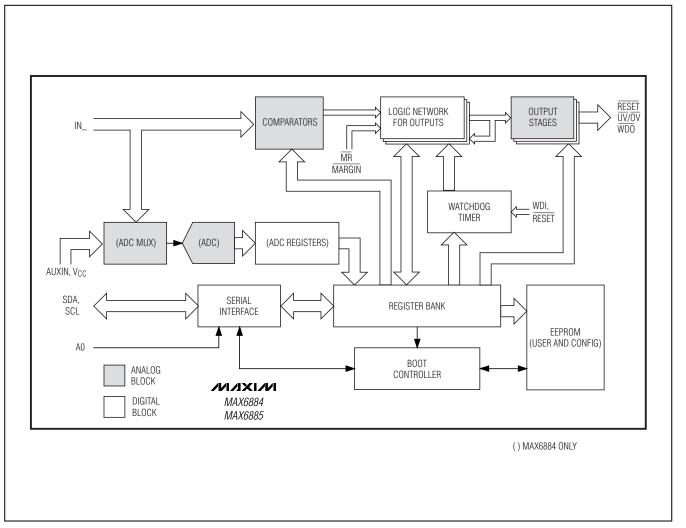

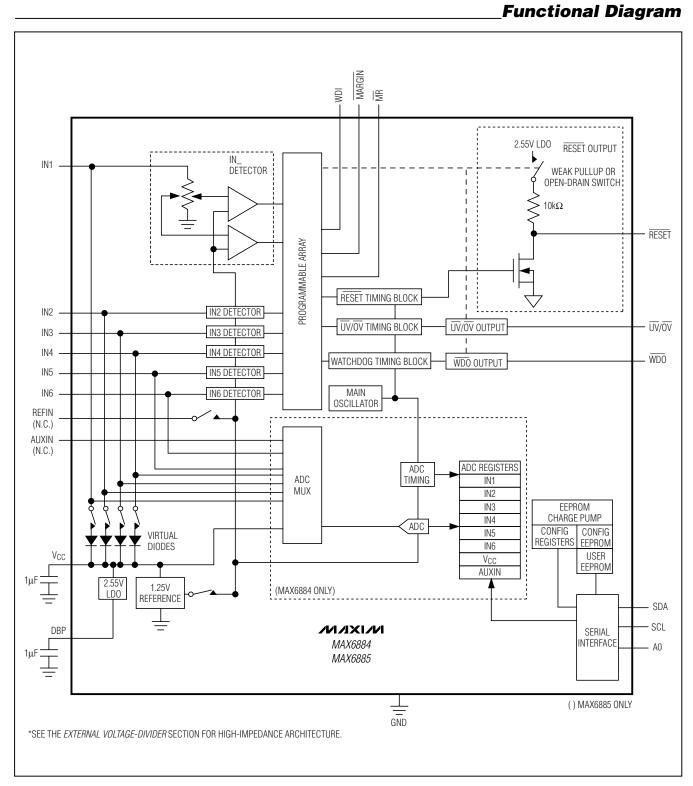

An internal 10-bit, 1% accurate ADC (MAX6884 only) converts the voltages at IN1–IN6, AUXIN, and V<sub>CC</sub> through a multiplexer that automatically sequences through all inputs every 200ms. An SMBus<sup>™</sup>/I<sup>2</sup>C-compatible serial data interface programs and communicates with the configuration EEPROM, configuration registers, internal 512-bit user EEPROM, and reads the ADC registers (MAX6884 only) and fault registers.

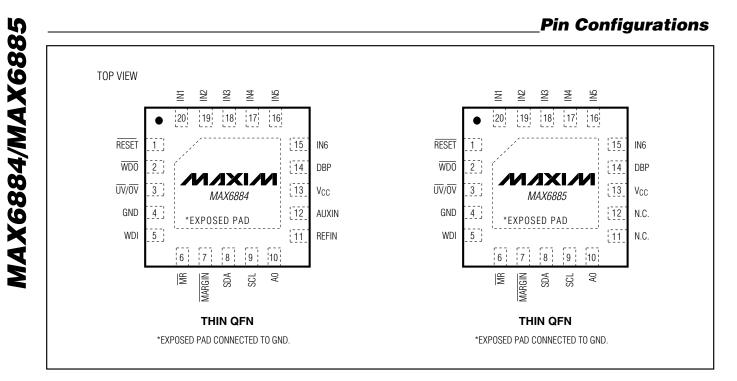

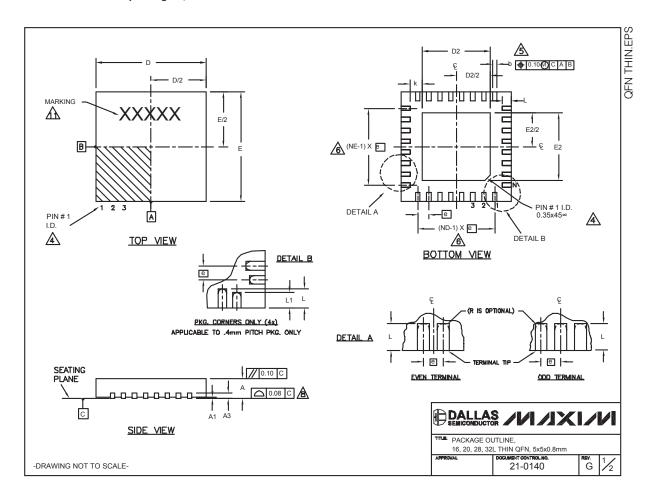

The MAX6884/MAX6885 are available in a 5mm x 5mm x 0.8mm 20-pin thin QFN package and operate over the extended temperature range (-40°C to +85°C).

## Applications

Telecommunications/Central-Office Systems Networking Systems Servers/Workstations Base Stations Storage Equipment Multimicroprocessor/Voltage Systems  6 Configurable Input Voltage Detectors Programmable Thresholds 0.5V to 3.05V (in 10mV Increments) or 1V to 5.8V (in 20mV Increments)

Primary UV and Secondary UV/OV Thresholds

- One Configurable Watchdog Timer from 6.25ms to 102.4s

- ♦ Configurable RESET, UV/OV, and WDO Outputs

- Three Programmable Outputs Open-Drain or Weak Pullup RESET, UV/OV, and WDO Active-Low Output Logic Timing Delays from 25µs to 1600ms

- Margining Disable and Manual Reset Controls

- Internal 1.25V Reference or External Reference Input

- 10-Bit Internal ADC Samples the Input Voltage Detectors, V<sub>CC</sub> and Auxiliary Input

- ♦ 512-Bit User EEPROM Endurance: 100,000 Erase/Write Cycles Data Retention: 10 Years

- SMBus/I<sup>2</sup>C-Compatible Serial Configuration/Communication Interface

- ±1% Threshold Accuracy

## **Ordering Information**

| PART       | TEMP RANGE     | P RANGE PIN-PACKAGE |         |

|------------|----------------|---------------------|---------|

| MAX6884ETP | -40°C to +85°C | 20 Thin QFN         | T2055-5 |

| MAX6885ETP | -40°C to +85°C | 20 Thin QFN         | T2055-5 |

Pin Configurations and Typical Operating Circuit appear at end of data sheet.

## Selector Guide

| PART       | VOLTAGE-<br>DETECTOR INPUTS |     |   | REFERENCE INPUT |     |  |

|------------|-----------------------------|-----|---|-----------------|-----|--|

| MAX6884ETP | 6                           | Yes | 3 | Yes             | Yes |  |

| MAX6885ETP | 6                           | No  | 3 | No              | No  |  |

##

Maxim Integrated Products 1

For pricing, delivery, and ordering information, please contact Maxim/Dallas Direct! at 1-888-629-4642, or visit Maxim's website at www.maxim-ic.com.

Features

# MAX6884/MAX6885

## **ABSOLUTE MAXIMUM RATINGS**

(All voltages referenced to GND.)

| IN1-IN6, V <sub>CC</sub> , RESET, UV/OV, WDO        | 0.3V to +6V |

|-----------------------------------------------------|-------------|

| WDI, MR, MARGIN, SDA, SCL, A0                       | 0.3V to +6V |

| AUXIN, DBP, REFIN                                   | 0.3V to +3V |

| Input/Output Current (all pins)                     | ±20mA       |

| Continuous Power Dissipation $(T_A = +70^{\circ}C)$ |             |

| 20-Pin (5mm x 5mm) Thin QFN                         |             |

| (derate 21.3mW/°C above +70°C)                      | 1702mW      |

|                                                     |             |

| Maximum Junction Temperature      | +150°C        |

|-----------------------------------|---------------|

| Operating Temperature Range       | 40°C to +85°C |

| Storage Temperature Range         |               |

| Lead Temperature (soldering, 10s) |               |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

## **ELECTRICAL CHARACTERISTICS**

$(V_{IN1}-V_{IN4} \text{ or } V_{CC} = 2.7V \text{ to } 5.8V, \text{AUXIN} = WDI = GND, \overline{MARGIN} = \overline{MR} = DBP, T_A = -40^{\circ}C \text{ to } +85^{\circ}C, \text{ unless otherwise noted. Typical values are at } T_A = +25^{\circ}C.)$  (Notes 1, 2, 3)

| PARAMETER                   | SYMBOL            | CONI                                                                               | DITIONS                                                      | MIN   | TYP  | МАХ   | UNITS |

|-----------------------------|-------------------|------------------------------------------------------------------------------------|--------------------------------------------------------------|-------|------|-------|-------|

| Operating Voltage Range     |                   | Voltage on either one guarantee the device                                         | e of IN1–IN4 or V <sub>CC</sub> to<br>e is fully operational | 2.7   |      | 5.8   | V     |

| Undervoltage Lockout        | V <sub>UVLO</sub> | <u> </u>                                                                           | one of IN1–IN4 or V <sub>CC</sub><br>is EEPROM configured    |       |      | 2.5   | V     |

| Digital Bypass Voltage      | VDBP              | No load                                                                            |                                                              | 2.48  | 2.55 | 2.67  | V     |

|                             |                   | V <sub>IN1</sub> = 5.8V, IN2–IN6                                                   | = GND, no load                                               |       | 0.9  | 1.2   | mA    |

| Supply Current              | ICC               | Writing to configuration EEPROM, no load                                           | on registers or                                              |       | 1.1  | 1.5   | mA    |

|                             |                   | VIN1-VIN6 (in 20mV ir                                                              | ncrements)                                                   | 1.0   |      | 5.8   |       |

| Threshold Panga             | \/                | V <sub>IN1</sub> –V <sub>IN6</sub> (in 10mV increments)                            |                                                              | 0.50  |      | 3.05  |       |

| Threshold Range             | V <sub>TH</sub>   | V <sub>IN1</sub> –V <sub>IN6</sub> (Inputs high impedance;<br>in 3.3mV increments) |                                                              | 0.167 |      | 1.017 | v     |

|                             |                   |                                                                                    | V <sub>IN</sub> = 2.5V to 5.8V<br>(20mV increments)          | -1    |      | +1    | %     |

|                             |                   | $T_A = +25^{\circ}C$ to                                                            | V <sub>IN</sub> = 1V to 2.5V<br>(20mV increments)            | -25   |      | +25   | mV    |

|                             |                   | +85°C, (V <sub>IN</sub> _falling)                                                  | V <sub>IN</sub> = 1.25V to 3.05V<br>(10mV increments)        | -1    |      | +1    | %     |

| IN1–IN6 Threshold Accuracy  |                   |                                                                                    | V <sub>IN</sub> = 0.5V to 1.25V<br>(10mV increments)         | -12.5 |      | +12.5 | mV    |

| IN I-ING THRESHOLD ACCURACY |                   |                                                                                    | V <sub>IN</sub> = 2.5V to 5.8V<br>(20mV increments)          | -1.5  |      | +1.5  | %     |

|                             |                   | $T_A = -40^{\circ}C$ to                                                            | V <sub>IN</sub> = 1V to 2.5V<br>(20mV increments)            | -25   |      | +25   | mV    |

|                             |                   | +85°C, (V <sub>IN</sub> _falling)                                                  | V <sub>IN</sub> = 1.25V to 3.05V<br>(10mV increments)        | -1.5  |      | +1.5  | %     |

|                             |                   |                                                                                    | V <sub>IN</sub> = 0.5V to 1.25V<br>(10mV increments)         | -12.5 |      | +12.5 | mV    |

## **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{IN1}-V_{IN4} \text{ or } V_{CC} = 2.7 \text{V to } 5.8 \text{V}, \text{AUXIN} = \text{WDI} = \text{GND}, \overline{\text{MARGIN}} = \overline{\text{MR}} = \text{DBP}, \text{T}_{A} = -40^{\circ}\text{C} \text{ to } +85^{\circ}\text{C}, \text{ unless otherwise noted}.$  Typical values are at T<sub>A</sub> = +25^{\circ}\text{C}.) (Notes 1, 2, 3)

| PARAMETER                                                                             | SYMBOL               | CONDITIONS                                                                                                   | MIN   | ТҮР    | МАХ   | UNITS             |

|---------------------------------------------------------------------------------------|----------------------|--------------------------------------------------------------------------------------------------------------|-------|--------|-------|-------------------|

| Threshold Hysteresis                                                                  | VTH-HYST             |                                                                                                              |       | 0.3    |       | % V <sub>TH</sub> |

| Threshold Tempco                                                                      | ∆V <sub>TH</sub> /°C |                                                                                                              |       | 10     |       | ppm/°C            |

| Threshold Differential Nonlinearity                                                   | V <sub>TH</sub> DNL  |                                                                                                              | -1    |        | +1    | LSB               |

| IN_ Input Impedance                                                                   | R <sub>IN</sub>      | For V <sub>IN_</sub> < highest of V <sub>IN1-IN4</sub> and V <sub>IN_</sub> < V <sub>CC</sub>                | 130   | 200    | 300   | kΩ                |

| IN_ Input Leakage Current                                                             | IIN_LKG              | IN_ high impedance                                                                                           | -150  |        | +150  | nA                |

| Power-Up Delay                                                                        | tD-PO                | V <sub>CC</sub> ≥ V <sub>UVLO</sub>                                                                          |       |        | 2.5   | ms                |

| IN_ to $\overline{\text{RESET}}$ or $\overline{\text{UV}}/\overline{\text{OV}}$ Delay | t <sub>D-R</sub>     | IN_ falling/rising, 100mV overdrive                                                                          |       | 20     |       | μs                |

| RESET and UV/OV Timeout                                                               |                      | 000                                                                                                          |       | 0.025  |       |                   |

|                                                                                       | trp, tup             | 001                                                                                                          | 1.406 | 1.5625 | 1.719 | ms                |

|                                                                                       |                      | 010                                                                                                          | 5.625 | 6.25   | 6.875 |                   |

|                                                                                       |                      | 011                                                                                                          | 22.5  | 25     | 27.5  |                   |

| Period (Tables 6 and 7)                                                               |                      | 100                                                                                                          | 45    | 50     | 55    |                   |

|                                                                                       |                      | 101                                                                                                          | 180   | 200    | 220   |                   |

|                                                                                       |                      | 110                                                                                                          | 360   | 400    | 440   |                   |

|                                                                                       |                      | 111                                                                                                          | 1440  | 1600   | 1760  |                   |

| RESET, UV/OV, WDO Output Low                                                          |                      | I <sub>SINK</sub> = 4mA, output asserted                                                                     |       |        | 0.4   | V                 |

| RESET, UV/OV, WDO Output<br>Open-Drain Leakage Current                                |                      | Output high impedance                                                                                        | -1    |        | +1    | μA                |

| RESET, UV/OV, WDO Output<br>Pullup Resistance                                         | R <sub>PU</sub>      | $V_{\overline{\text{RESET}}}, V_{\overline{\text{UV}}/\overline{\text{OV}}}, V_{\overline{\text{WDO}}} = 2V$ | 6.6   | 10     | 15.0  | kΩ                |

|                                                                                       | VIL                  |                                                                                                              |       |        | 0.6   | N/                |

| MR, MARGIN, WDI Input Voltage                                                         | VIH                  |                                                                                                              | 1.4   |        |       |                   |

| MR Input Pulse Width                                                                  | tMR                  |                                                                                                              | 1     |        |       | μs                |

| MR Glitch Rejection                                                                   |                      |                                                                                                              |       | 100    |       | ns                |

## **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{IN1}-V_{IN4} \text{ or } V_{CC} = 2.7V \text{ to } 5.8V, \text{AUXIN} = WDI = GND, \overline{MARGIN} = \overline{MR} = DBP, T_A = -40^{\circ}C \text{ to } +85^{\circ}C, \text{ unless otherwise noted. Typical values are at } T_A = +25^{\circ}C.)$  (Notes 1, 2, 3)

| PARAMETER                                         | SYMBOL           | CONDITIONS                                                             | MIN   | ТҮР    | MAX    | UNITS |

|---------------------------------------------------|------------------|------------------------------------------------------------------------|-------|--------|--------|-------|

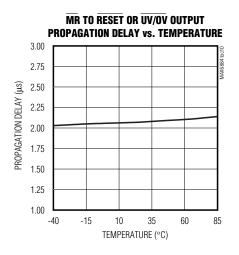

| MR to RESET or UV/OV Delay                        | td-MR            |                                                                        |       | 200    |        | ns    |

| MR to Internal V <sub>DBP</sub> Pullup<br>Current | IMR              | V <sub>MR</sub> = 1.4V                                                 | 5     | 10     | 15     | μA    |

| MARGIN to DBP Pullup Current                      | MARGIN           | VMARGIN = 1.4V                                                         | 5     | 10     | 15     | μA    |

| WDI Pulldown Current                              | Iwdi             | V <sub>WDI</sub> = 0.6V                                                | 5     | 10     | 15     | μA    |

| WDI Input Pulse Width                             | twdi             |                                                                        | 50    |        |        | ns    |

|                                                   |                  | 000                                                                    | 5.625 | 6.25   | 6.875  |       |

|                                                   |                  | 001                                                                    | 22.5  | 25     | 27.5   |       |

|                                                   |                  | 010                                                                    | 90    | 100    | 110    | ms    |

| Watchdog Timeout Period                           |                  | 011                                                                    | 360   | 400    | 440    |       |

| (Table 8)                                         | twD              | 100                                                                    | 1.44  | 1.60   | 1.76   | - S   |

|                                                   |                  | 101                                                                    | 5.76  | 6.40   | 7.04   |       |

|                                                   |                  | 110                                                                    | 23.04 | 25.60  | 28.16  |       |

|                                                   |                  | 111                                                                    | 92.16 | 102.40 | 112.64 |       |

| Reference Input Voltage Range                     | VREF             | MAX6884 only                                                           | 1.225 | 1.25   | 1.275  | V     |

| Reference Input Resistance                        | R <sub>REF</sub> | V <sub>REF</sub> = 1.25V, MAX6884 only                                 |       | 500    |        | kΩ    |

|                                                   |                  | IN1–IN6, V <sub>CC</sub> ; LSB = 7.32mV, MAX6884 only                  | 0     |        | 5.8    | V     |

| ADC Range                                         |                  | IN1–IN6; LSB = 3.66mV, MAX6884 only                                    | 0     |        | 3.746  |       |

| ADC hange                                         | ADCRANGE         | AUXIN, IN1–IN6 high-impedance mode;<br>LSB = 1.2mV, MAX6884 only       | 0     |        | 1.25   |       |

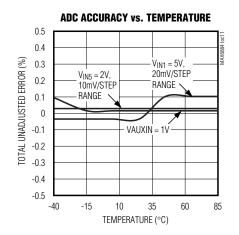

| ADC Total Unadjusted Error                        | TUE              | Internal reference, MAX6884 only                                       |       |        | ±1.0   |       |

| (Note 4)                                          | TUE              | External reference, MAX6884 only (Note 5)                              |       |        | ±1.0   | %FSR  |

| ADC Differential Nonlinearity                     | DNL              | MAX6884 only (Note 6)                                                  |       | ±1     |        | LSB   |

| ADC Total Monitoring Cycle Time                   | tc               | Converts all six IN_ inputs, AUXIN, and V <sub>CC</sub> , MAX6884 only |       | 200    | 266    | ms    |

| AUXIN Input Leakage Current                       | Iauxin           | V <sub>AUXIN</sub> = 1.25V, MAX6884 only                               | -1    |        | +1     | μA    |

| SERIAL INTERFACE LOGIC (SD                        | A, SCL, A0)      |                                                                        |       |        |        |       |

| Logic-Input Low Voltage                           | VIL              |                                                                        |       |        | 0.8    | V     |

| Logic-Input High Voltage                          | VIH              |                                                                        | 2.0   |        |        | V     |

| Input Leakage Current                             | I <sub>LKG</sub> |                                                                        |       |        | 1      | μA    |

| Output-Voltage Low                                | Vol              | I <sub>SINK</sub> = 3mA                                                |       |        | 0.4    | V     |

| Input/Output Capacitance                          | C <sub>I/O</sub> |                                                                        |       |        | 10     | pF    |

## TIMING CHARACTERISTICS

$(V_{IN1}-V_{IN4} \text{ or } V_{CC} = 2.7 \text{ to } 5.8 \text{V}, \text{ AUXIN} = \text{WDI} = \text{GND}, \overline{\text{MARGIN}} = \overline{\text{MR}} = \text{DBP}, T_{A} = -40^{\circ}\text{C} \text{ to } +85^{\circ}\text{C}, \text{ unless otherwise noted}. Typical values are at T_{IN1} = +25^{\circ}\text{C}.)$  (Notes 1, 2, 3)

| PARAMETER                            | SYMBOL         | CONDITIONS                        | MIN                          | ТҮР                                | МАХ | UNITS |

|--------------------------------------|----------------|-----------------------------------|------------------------------|------------------------------------|-----|-------|

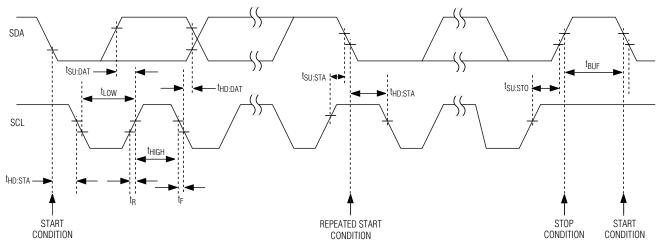

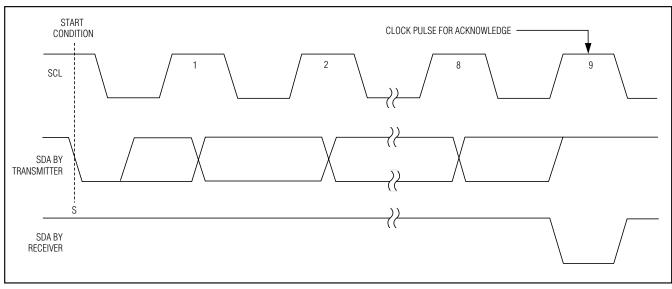

| TIMING CHARACTERISTICS (Fig          | ure 6)         |                                   |                              |                                    |     |       |

| Serial Clock Frequency               | fSCL           |                                   |                              |                                    | 400 | kHz   |

| Clock Low Period                     | tLOW           |                                   | 1.3                          |                                    |     | μs    |

| Clock High Period                    | thigh          |                                   | 0.6                          |                                    |     | μs    |

| Bus Free Time                        | tBUF           |                                   | 1.3                          |                                    |     | μs    |

| START Setup Time                     | tsu:sta        |                                   | 0.6                          |                                    |     | μs    |

| START Hold Time                      | thd:sta        |                                   | 0.6                          |                                    |     | μs    |

| STOP Setup Time                      | tsu:sto        |                                   | 0.6                          |                                    |     | μs    |

| Data In Setup Time                   | tsu:dat        |                                   | 100                          |                                    |     | ns    |

| Data In Hold Time                    | thd:dat        |                                   | 30                           |                                    | 900 | ns    |

| Receive SCL/SDA Minimum Rise<br>Time | t <sub>R</sub> | (Note 7)                          | C                            | 20 +<br>0.1 x C <sub>BUS</sub>     |     | ns    |

| Receive SCL/SDA Maximum Rise<br>Time | t <sub>R</sub> | (Note 7)                          |                              | 300                                |     |       |

| Receive SCL/SDA Minimum Fall<br>Time | tF             | (Note 7)                          | С                            | 20 +<br>0.1 x C <sub>BUS</sub>     |     |       |

| Receive SCL/SDA Maximum Fall<br>Time | tF             | (Note 7)                          |                              | 300                                |     | ns    |

| Transmit SDA Fall Time               | tF             | C <sub>BUS</sub> = 400pF (Note 5) | 20 +<br>0.1 x C <sub>B</sub> | 20 + 300<br>0.1 x C <sub>BUS</sub> |     |       |

| Pulse Width of Spike Suppressed      | tsp            | (Note 8)                          |                              | 50                                 |     |       |

| EEPROM Byte Write Cycle Time         | twR            | (Note 9)                          |                              |                                    | 11  | ms    |

**Note 1:** 100% production tested at  $T_A = +25^{\circ}C$  and  $T_A = +85^{\circ}C$ . Specifications at  $T_A = -40^{\circ}C$  are guaranteed by design.

Note 2: Device may be supplied from IN1–IN4 or V<sub>CC</sub>.

Note 3: The internal supply voltage, measured at VCC, equals the maximum of IN1-IN4.

Note 4:  $V_{IN} > 0.3 \times ADC$  range.

Note 5: Does not include the inaccuracy of the 1.25V input reference voltage (MAX6884 only).

**Note 6:** DNL is implicitly guaranteed by design in a  $\Sigma\Delta$  converter.

Note 7:  $C_{BUS}$  = total capacitance of one bus line in picofarads. Rise and fall times are measured between 0.1 x V<sub>BUS</sub> and 0.9 x V<sub>BUS</sub>.

Note 8: Input filters on SDA, SCL, and A0 suppress noise spikes <50ns.

Note 9: An additional cycle is required when writing to configuration memory for the first time.

## **Typical Operating Characteristics**

$(V_{IN1}-V_{IN4} \text{ or } V_{CC} = 5V, \text{AUXIN} = WDI = \text{GND}, \overline{\text{MARGIN}} = \overline{\text{MR}} = \text{DBP}.$  Typical values are at T<sub>A</sub> = +25°C, unless otherwise noted.)

V<sub>CC</sub> SUPPLY CURRENT **IN1-IN4 SUPPLY CURRENT** NORMALIZED RESET OR UV/OV vs. IN1-IN4 SUPPLY VOLTAGE **TIMEOUT PERIOD vs. TEMPERATURE** vs. V<sub>CC</sub> SUPPLY VOLTAGE 1.00 1.020 1.00 1.015 1.010 1.010 1.005 0.95 0.95  $T_A = +85^{\circ}C$ T<sub>A</sub> = +85°C SUPPLY CURRENT (mA) SUPPLY CURRENT (mA) 0.90 0.90 N0RMALIZED REST 0.992 0.990 0.985 0.85 0.85 0.80 0.80 +25°C +25°C TΑ -40°C 40°C TΔ 0.75 0.75 0.70 0.70 0.980 2.6 3.6 4.6 5.6 2.6 3.6 4.6 5.6 -40 35 60 85 -15 10 TEMPERATURE (°C) SUPPLY VOLTAGE (V) SUPPLY VOLTAGE (V) IN TO RESET OR UV/OV NORMALIZED IN THRESHOLD NORMALIZED WATCHDOG TIMEOUT PERIOD **PROPAGATION DELAY vs. TEMPERATURE** vs. TEMPERATURE vs. TEMPERATURE 30 1.005 1.020 100mV OVERDRIVE 1.015 1.010 1.010 1.000 1.000 1.000 1.000 1.000 1.000 0.995 0.990 0.985 29 1.004 28 1.003 THRESHOLD PROPAGATION DELAY (µs) 27 1.002 26 1.001 NORMALIZED IN 25 1.000 24 0.999 23 0.998 22 0.997 21 0.996 20 0.995 0.980 60 85 -15 60 85 -40 -15 10 35 -40 10 35 35 60 -40 -15 10 85 TEMPERATURE (°C) TEMPERATURE (°C) TEMPERATURE (°C) MAXIMUM IN\_ TRANSIENT **OUTPUT VOLTAGE LOW OUTPUT VOLTAGE HIGH** vs. IN THRESHOLD OVERDRIVE vs. SOURCE CURRENT (WEAK PULLUP) vs. SINK CURRENT 200 400 2.6 2.4 MAXIMUM TRANSIENT DURATION (μs) 175 350 2.2 (mV) **OUTPUT VOLTAGE HIGH (V)** 2.0 300 150 1.8 OUTPUT VOLTAGE LOW 250 125 1.6 1.4 100 200 1.2 RESET OR UV/OV ASSERTS 75 ABOVE THIS LINE 150 1.0 0.8 50 100 0.6 0.4 25 50 0.2 0 0 0 10 100 1000 0 2 4 6 8 10 12 14 0 0.05 0.10 0.15 0.20 0.25 0.30 1 SOURCE CURRENT (mA) IN\_ THRESHOLD OVERDRIVE (mV) SINK CURRENT (mA)

## **Typical Operating Characteristics (continued)**

$(V_{IN1}-V_{IN4} \text{ or } V_{CC} = 5V, \text{AUXIN} = \text{WDI} = \text{GND}, \overline{\text{MARGIN}} = \overline{\text{MR}} = \text{DBP}.$  Typical values are at T<sub>A</sub> = +25°C, unless otherwise noted.)

## Pin Description

| Р       | IN      |       | FUNCTION                                                                                                                                                                                                                                                                                                                                                                         |  |

|---------|---------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| MAX6884 | MAX6885 | NAME  | FUNCTION                                                                                                                                                                                                                                                                                                                                                                         |  |

| 1       | 1       | RESET | Reset Output. Configurable, active-low, open drain, or weak pullup. $\overline{\text{RESET}}$ assumes its programmed conditional output state when V_CC exceeds UVLO (2.5V).                                                                                                                                                                                                     |  |

| 2       | 2       | WDO   | Watchdog Timer Output. Configurable, active-low, open drain, or weak pullup. $\overline{\text{WDO}}$ asserts when WDI is not toggled with a valid high-to-low or low-to-high transition within the watchdog timeout period.                                                                                                                                                      |  |

| 3       | 3       | UV/OV | Undervoltage/Overvoltage Output. Configurable, active-low, open drain, or weak pullup. $\overline{\text{UV}/\text{OV}}$ assumes its programmed conditional output state when V <sub>CC</sub> exceeds UVLO (2.5V).                                                                                                                                                                |  |

| 4       | 4       | GND   | Ground                                                                                                                                                                                                                                                                                                                                                                           |  |

| 5       | 5       | WDI   | Watchdog Timer Input. Logic input for the watchdog timer function. If $\overline{\text{WDI}}$ is not toggled with a valid low-to-high or high-to-low transition within the watchdog timeout period, $\overline{\text{WDO}}$ asserts. Progam initial and normal watchdog timeout periods from 6.25ms to 102.4s. WDI is internally pulled down to GND through a 10µA current sink. |  |

| 6       | 6       | MR    | Manual Reset Input. Program $\overline{\text{MR}}$ to assert $\overline{\text{RESET}}$ and/or $\overline{\text{UV}/\text{OV}}$ when $\overline{\text{MR}}$ is asserted.<br>Leave $\overline{\text{MR}}$ unconnected or connect to DBP if unused. $\overline{\text{MR}}$ is internally pulled up to DBP through a 10µA current source.                                            |  |

## **Pin Description (continued)**

| P       | PIN     |        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|---------|---------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MAX6884 | MAX6885 | NAME   | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 7       | 7       | MARGIN | Margin Input. MARGIN holds RESET, UV/OV, and WDO in their existing states when MARGIN is driven low. Leave MARGIN unconnected or connect to DBP if unused. MARGIN is internally pulled up to DBP through a 10µA current source. MARGIN overrides MR if both are asserted at the same time.                                                                                                                                                                                                            |

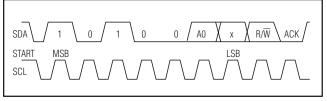

| 8       | 8       | SDA    | Serial Data Input/Output (Open Drain). SDA requires an external pullup resistor.                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 9       | 9       | SCL    | Serial-Interface Clock Input. SCL requires an external pullup resistor.                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 10      | 10      | A0     | Serial Address Input 0. Allows up to 2 devices to share a common bus. Connect A0 to ground or the serial-interface power supply.                                                                                                                                                                                                                                                                                                                                                                      |

| 11      | _       | REFIN  | Reference Voltage Input. Program the device for external or internal reference. Connect<br>an external +1.225V to +1.275V reference to REFIN when using an external reference.<br>Leave REFIN unconnected when using the internal reference.                                                                                                                                                                                                                                                          |

| 12      | _       | AUXIN  | Auxiliary Input. A 10-bit ADC converts the input voltage at AUXIN. The high-impedance AUXIN input accepts input voltages up to 1.25V. AUXIN does not affect programmable outputs.                                                                                                                                                                                                                                                                                                                     |

| _       | 11, 12  | N.C.   | No Connection. Not internally connected.                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 13      | 13      | Vcc    | Internal Power-Supply Voltage. Bypass V <sub>CC</sub> to GND with a 1µF ceramic capacitor as close to the device as possible. V <sub>CC</sub> supplies power to the internal circuitry. V <sub>CC</sub> is internally powered from the highest of the monitored IN1–IN4 voltages. Do not use V <sub>CC</sub> to supply power to external circuitry. To externally supply V <sub>CC</sub> , see the <i>Powering the MAX6884/MAX6885</i> section.                                                       |

| 14      | 14      | DBP    | Internal Digital Power-Supply Voltage. Bypass DBP to GND with a 1µF ceramic capacitor. DBP supplies power to the EEPROM memory, the internal logic circuitry, and the programmable outputs. Do not use DBP to supply power to external circuitry.                                                                                                                                                                                                                                                     |

| 15      | 15      | IN6    | Voltage-Detector Input 6. Program two thresholds per voltage-detector input (undervoltage UV and undervoltage/overvoltage UV/OV). Program IN6 detector thresholds from 1V to 5.8V in 20mV increments, 0.5V to 3.05V in 10mV increments. For improved noise immunity, bypass IN6 to GND with a 0.1µF capacitor installed as close to the device as possible.                                                                                                                                           |

| 16      | 16      | IN5    | Voltage-Detector Input 5. Program two thresholds per voltage-detector input (undervoltage UV and undervoltage/overvoltage UV/OV). Program IN5 detector thresholds from 1V to 5.8V in 20mV increments, 0.5V to 3.05V in 10mV increments. For improved noise immunity, bypass IN5 to GND with a 0.1µF capacitor installed as close to the device as possible.                                                                                                                                           |

| 17      | 17      | IN4    | Voltage-Detector Input 4. Program two thresholds per voltage-detector input (undervoltage UV and undervoltage/overvoltage UV/OV). Program IN4 detector thresholds from 1V to 5.8V in 20mV increments, 0.5V to 3.05V in 10mV increments. For improved noise immunity, bypass IN4 to GND with a $0.1\mu$ F capacitor installed as close to the device as possible. Program the device to receive power through IN1–IN4 inputs or V <sub>CC</sub> (see the <i>Powering the MAX6884/MAX6885</i> section). |

## Pin Description (continued)

| P       | IN      | NAME | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|---------|---------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MAX6884 | MAX6885 | NAME | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 18      | 18      | IN3  | Voltage-Detector Input 3. Program two thresholds per voltage-detector input (undervoltage UV and undervoltage/overvoltage UV/OV). Program IN3 detector thresholds from 1V to 5.8V in 20mV increments, or 0.5V to 3.05V in 10mV increments. For improved noise immunity, bypass IN3 to GND with a 0.1 $\mu$ F capacitor installed as close to the device as possible. Program the device to receive power through IN1–IN4 inputs or V <sub>CC</sub> (see the <i>Powering the MAX6884/MAX6885</i> section). |

| 19      | 19      | IN2  | Voltage-Detector Input 2. Program two thresholds per voltage-detector input (undervoltage UV and undervoltage/overvoltage UV/OV). Program IN2 detector thresholds from 1V to 5.8V in 20mV increments, or 0.5V to 3.05V in 10mV increments. For improved noise immunity, bypass IN2 to GND with a 0.1 $\mu$ F capacitor installed as close to the device as possible. Program the device to receive power through IN1–IN4 inputs or V <sub>CC</sub> (see the <i>Powering the MAX6884/MAX6885</i> section). |

| 20      | 20      | IN1  | Voltage-Detector Input 1. Program two thresholds per voltage-detector input (undervoltage UV and undervoltage/overvoltage UV/OV). Program IN1 detector thresholds from 1V to 5.8V in 20mV increments, or 0.5V to 3.05V in 10mV increments. For improved noise immunity, bypass IN1 to GND with a 0.1 $\mu$ F capacitor installed as close to the device as possible. Program the device to receive power through IN1–IN4 inputs or V <sub>CC</sub> (see the <i>Powering the MAX6884/MAX6885</i> section). |

| _       | _       | EP   | Exposed Paddle. Internally connected to GND. Connect EP to GND or leave floating.                                                                                                                                                                                                                                                                                                                                                                                                                         |

## **Detailed Description**

The MAX6884/MAX6885 EEPROM-configurable, multivoltage supply supervisors monitor six voltage-detector inputs, one auxiliary input, and one watchdog input, and feature three programmable outputs for highly configurable, power-supply monitoring applications (see Table 1 for programmable features). Manual reset and margin disable inputs offer additional flexibility.

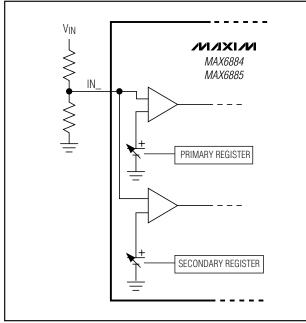

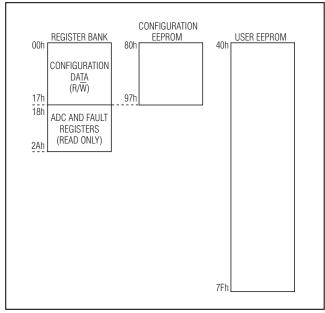

Each voltage detector provides a programmable primary undervoltage and secondary undervoltage/overvoltage threshold. Program thresholds from 0.5V to 3.05V in 10mV increments, 1.0V to 5.8V in 20mV increments, or from 0.1667V to 1.0167V in 3.3mV increments. To achieve thresholds from 0.1667V to 1.0167V in 3.3mV increments, the respective input voltage detector must be programmed for high impedance and an external voltage-divider must be connected. A fault register logs undervoltage and overvoltage conditions for each voltage-detector input. An internal 10-bit ADC (MAX6884 only) converts voltages at IN1–IN6, AUXIN, and V<sub>CC</sub> through a multiplexer that automatically sequences through all inputs every 200ms. Access the device's internal 512-bit user EEPROM, configuration EEPROM, configuration registers, ADC registers, and fault registers through an SMBus/I<sup>2</sup>C-compatible serial interface (see the *SMBus/I<sup>2</sup>C-Compatible Serial Interface* section). The MAX6884/MAX6885 also feature an accurate internal 1.25V reference. For greater accuracy, connect an external 1.25V reference to REFIN (MAX6884 only).

Program outputs RESET, UV/OV, and WDO for opendrain or weak pullup. Program RESET and UV/OV to assert on any voltage-detector input, MR, or each other. RESET can also depend on WDO. Programmable timing delay blocks configure each output to wait between 25µs and 1600ms before deasserting. Fault registers log the assertion of RESET, UV/OV, and WDO.

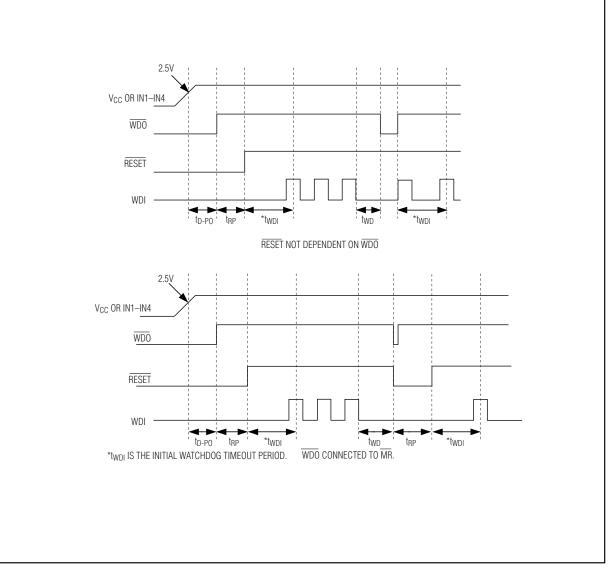

The MAX6884/MAX6885 feature a watchdog timer with programmable initial and normal timeout periods from 6.25ms to 102.4s. WDO asserts when WDI is not toggled from high-to-low or low-to-high within the appropriate watchdog timeout period. Program WDO to assert RESET.

Program the MAX6884/MAX6885 to receive power through IN1–IN4 or V<sub>CC</sub> (see the *Powering the MAX6884/MAX6885* section). Outputs remain asserted while the voltage that is supplying the device is below UVLO (2.5V) and above 1V (see Figure 1).

## Table 1. Programmable Features

| FEATURE                    | DESCRIPTION                                                                                                                                                                                                                                                                                         |

|----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Input Voltages IN1–IN6     | <ul> <li>Primary undervoltage threshold</li> <li>Secondary undervoltage or overvoltage threshold</li> <li>1V to 5.8V thresholds in 20mV increments</li> <li>0.5V to 3.05V thresholds in 10mV increments</li> <li>0.1667V to 1.017V thresholds in 3.3mV increments in high-impedance mode</li> </ul> |

| Programmable Output RESET  | <ul> <li>Dependency on IN1–IN6, MR, UV/OV, and/or WDO</li> <li>Active-low, weak pullup, or open-drain output</li> <li>Programmable timeout periods of 25µs, 1.5625ms, 6.25ms, 25ms, 50ms, 200ms, 400ms, or 1.6s</li> </ul>                                                                          |

| Programmable Output UV/OV  | <ul> <li>Dependency on IN1–IN6, MR, and/or RESET</li> <li>Active-low, weak pullup, or open-drain output</li> <li>Programmable timeout periods of 25µs, 1.5625ms, 6.25ms, 25ms, 50ms, 200ms, 400ms, or 1.6s</li> </ul>                                                                               |

| Programmable Output WDO    | Active-low, weak pullup, or open-drain output                                                                                                                                                                                                                                                       |

| Watchdog Timer             | <ul> <li>Initial watchdog timeout period of 6.25ms, 25ms, 100ms, 400ms, 1.6s, 6.4s, 25.6s, or 102.4s</li> <li>Normal watchdog timeout period of 6.25ms, 25ms, 100ms, 400ms, 1.6s, 6.4s, 25.6s, or 102.4s</li> <li>Watchdog enable/disable</li> </ul>                                                |

| V <sub>CC</sub> Power Mode | - Programs whether the device is powered from the highest IN_ input or from an external supply connected to $V_{CC}$                                                                                                                                                                                |

| Manual Reset Input MR      | Program RESET or UV/OV to assert while MR is asserted                                                                                                                                                                                                                                               |

| Reference Input REFIN      | <ul> <li>Internal +1.25V reference voltage</li> <li>Goes high impedance when internal reference is selected</li> <li>External reference voltage input from 1.225V to 1.275V</li> <li>Sets ADC voltage range</li> </ul>                                                                              |

| 10-Bit ADC*                | <ul> <li>Samples voltages at IN1–IN6, AUXIN, and V<sub>CC</sub></li> <li>Completes conversion of all eight inputs in 200ms</li> <li>Reference voltage sets ADC range</li> <li>Read ADC data from SMBus/I<sup>2</sup>C interface</li> </ul>                                                          |

| Write Disable              | Locks user EEPROM based on RESET or UV/OV assertion                                                                                                                                                                                                                                                 |

| Configuration Lock         | Locks configuration registers and EEPROM                                                                                                                                                                                                                                                            |

\*ADC does not affect programmable outputs.

M/IXI/M

Figure 1. Top-Level Block Diagram

MAX6884/MAX6885

MAX6884/MAX6885

M/IXI/M

#### Powering the MAX6884/MAX6885

The MAX6884/MAX6885 derive power from the voltagedetector inputs: IN1–IN4 or through an externally supplied VCC. A virtual diode-ORing scheme selects the positive input that supplies power to the device (see the *Functional Diagram*). The highest input voltage on IN1–IN4 supplies power to the device. One of V<sub>IN1</sub>–V<sub>IN4</sub> must be at least 2.7V to ensure proper operation.

Internal hysteresis ensures that the supply input that initially powered the device continues to power the device when multiple input voltages are within 50mV of each other.

V<sub>CC</sub> powers the analog circuitry and is the bypass connection for the MAX6884/MAX6885 internal supply. Bypass V<sub>CC</sub> to GND with a 1µF ceramic capacitor installed as close to the device as possible. The internal supply voltage, measured at V<sub>CC</sub>, equals the maximum of IN1–IN4. If V<sub>CC</sub> is externally supplied, V<sub>CC</sub> must be at least 200mV higher than any voltage applied to IN–IN4 and V<sub>CC</sub> must be brought up first. V<sub>CC</sub> always powers the device when all IN\_ are factory set as "ADJ." Do not use the internally generated V<sub>CC</sub> to provide power to external circuitry. Externally supply power through V<sub>CC</sub>. To externally supply power through V<sub>CC</sub>:

- 1) Apply a voltage to only one of V<sub>CC</sub> (2.7V to 5.5V) or IN1–IN4 (2.7V to 5.8V).

- 2) Program the internal/external V<sub>CC</sub> Power EEPROM at 96h, Bit[5] = 1 (see Table 2).

- 3) Power down the device.

Subsequent power-ups and software reboots require an externally supplied  $V_{CC}$  to ensure the device is fully operational.

| REGISTER<br>ADDRESS | EEPROM<br>MEMORY<br>ADDRESS | BIT<br>RANGE | DESCRIPTION                                                  |

|---------------------|-----------------------------|--------------|--------------------------------------------------------------|

| 104                 | OCh                         | [5]          | $1 = V_{CC}$ Powered<br>$0 = IN1-IN4$ or $V_{CC}$<br>Powered |

| 16h                 | 96h                         | [2]          | Not Used                                                     |

|                     |                             | [4]          | Not Used                                                     |

|                     |                             | [6]          | Not Used                                                     |

#### Table 2. Internal/External Vcc

The MAX6884/MAX6885 also generate a digital supply voltage (DBP) for the internal logic circuitry and the EEPROM. Bypass DBP to GND with a  $1\mu$ F ceramic capacitor installed as close to the device as possible. The nominal DBP output voltage is 2.55V. Do not use DBP to provide power to external circuitry.

##

#### ADC (MAX6884 Only)

An internal 10-bit ADC (MAX6884 only) converts voltages at IN1–IN4, AUXIN, and V<sub>CC</sub> through a multiplexer that automatically sequences through all inputs every 200ms. Registers 18h to 27h store the ADC data (see Table 3). Read the ADC data from the MAX6884 with the serial interface. The ADC has no effect on programmable outputs RESET,  $\overline{UV/OV}$ , or  $\overline{WDO}$ .

#### Inputs

The MAX6884/MAX6885 offer the following inputs: voltage-detector inputs IN1–IN4, auxiliary input AUXIN (MAX6884 only), manual reset input MR, margin input MARGIN, and reference input REFIN (MAX6884 only).

#### IN1–IN6

The MAX6884/MAX6885 offer six voltage-detector inputs: IN1–IN6. Each voltage-detector input offers a programmable primary undervoltage threshold and a secondary undervoltage/overvoltage threshold. Program thresholds from 0.5V to 3.05V in 10mV increments, 1.0V to 5.8V in 20mV increments, or from 0.1667V to 1.0167V in 3.3mV increments. Use the following equations to program thresholds in the appropriate registers:

$$X = \frac{V_{TH} - 1V}{0.02V}$$

for 1V to 5.8V range in 20mV increments (program bits R0Fh[5:0]).

$$X = \frac{V_{TH} - 0.5V}{0.01V}$$

for 0.5V to 3.05V range in 10mV increments (program bits R0Fh[5:0]).

$$X = \frac{V_{TH} - 0.1667V}{0.0033V}$$

for 0.1667V to 1.0167V in 3.3mV increments (see the *External Voltage-Divider* section).

where  $V_{TH}$  is the desired threshold voltage and X is the decimal code for the desired threshold (see Table 4). To set a threshold for the 1V to 5.8V range, X must equal 240 or less. Set the secondary threshold for an undervoltage or overvoltage threshold by programming bits R0Eh[5:0]. To achieve thresholds in between the 10mV and 20mV steps or to monitor voltages higher than 5.8V, program a voltage-detector input for high impedance through bits R10h[5:0] and add a resister voltage-divider (see the *External Voltage-Divider* section).

## Table 3. ADC Registers (MAX6884 Only)

| REGISTER ADDRESS | BIT RANGE | DESCRIPTION                                    |  |

|------------------|-----------|------------------------------------------------|--|

| 18h              | [7:0]     | ADC IN1 Conversion Result (8 MSBs)             |  |

| 101-             | [1:0]     | ADC IN1 Conversion Result (2 LSBs)             |  |

| 19h              | [7:2]     | Not Used                                       |  |

| 1Ah              | [7:0]     | ADC IN2 Conversion Result (8 MSBs)             |  |

|                  | [1:0]     | ADC IN2 Conversion Result (2 LSBs)             |  |

| 1Bh              | [7:2]     | Not Used                                       |  |

| 1Ch              | [7:0]     | ADC IN3 Conversion Result (8 MSBs)             |  |

| 104              | [1:0]     | ADC IN3 Conversion Result (2 LSBs)             |  |

| 1Dh              | [7:2]     | Not Used                                       |  |

| 1Eh              | [7:0]     | ADC IN4 Conversion Result (8 MSBs)             |  |

| 156              | [1:0]     | ADC IN4 Conversion Result (2 LSBs)             |  |

| 1Fh              | [7:2]     | Not Used                                       |  |

| 20h              | [7:0]     | ADC IN5 Conversion Result (8 MSBs)             |  |

| 016              | [1:0]     | ADC IN5 Conversion Result (2 LSBs)             |  |

| 21h              | [7:2]     | Not Used                                       |  |

| 22h              | [7:0]     | ADC IN6 Conversion Result (8 MSBs)             |  |

| 0.0k             | [1:0]     | ADC IN6 Conversion Result (2 LSBs)             |  |

| 23h              | [7:2]     | Not Used                                       |  |

| 24h              | [7:0]     | ADC AUXIN Conversion Result (8 MSBs)           |  |

| 0Eb              | [1:0]     | ADC AUXIN Conversion Result (2 LSBs)           |  |

| 25h              | [7:2]     | Not Used                                       |  |

| 26h              | [7:0]     | ADC V <sub>CC</sub> Conversion Result (8 MSBs) |  |

| 07b              | [1:0]     | ADC V <sub>CC</sub> Conversion Result (2 LSBs) |  |

| 27h              | [7:2]     | Not Used                                       |  |

## Table 4. IN1–IN6 Threshold Register Settings

| REGISTER<br>ADDRESS | EEPROM MEMORY<br>ADDRESS | BIT RANGE                                                                                    | DESCRIPTION                                                                                             |

|---------------------|--------------------------|----------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|

| 00h                 | 80h                      | [7:0]                                                                                        | IN1 Primary Undervoltage Detector Threshold (see equations in the <i>IN1–IN6</i> section)               |

| 01h                 | 81h                      | [7:0]                                                                                        | IN2 Primary Undervoltage Detector Threshold                                                             |

| 02h                 | 82h                      | [7:0]                                                                                        | IN3 Primary Undervoltage Detector Threshold                                                             |

| 03h                 | 83h                      | [7:0]                                                                                        | IN4 Primary Undervoltage Detector Threshold                                                             |

| 04h                 | 84h                      | [7:0]                                                                                        | IN5 Primary Undervoltage Detector Threshold                                                             |

| 05h                 | 85h                      | [7:0]                                                                                        | IN6 Primary Undervoltage Detector Threshold                                                             |

| 06h                 | 86h                      | [7:0]                                                                                        | IN1 Secondary Undervoltage/Overvoltage Detector Threshold (see equations in the <i>IN1–IN6</i> section) |

| 07h                 | 87h                      | [7:0]                                                                                        | IN2 Secondary Undervoltage/Overvoltage Detector Threshold                                               |

| 08h                 | 88h                      | [7:0]                                                                                        | IN3 Secondary Undervoltage/Overvoltage Detector Threshold                                               |

| 09h                 | 89h                      | [7:0]                                                                                        | IN4 Secondary Undervoltage/Overvoltage Detector Threshold                                               |

| 0Ah                 | 8Ah                      | [7:0]                                                                                        | IN5 Secondary Undervoltage/Overvoltage Detector Threshold                                               |

| 0Bh                 | 8Bh                      | [7:0]                                                                                        | IN6 Secondary Undervoltage/Overvoltage Detector Threshold                                               |

|                     |                          | [0]                                                                                          | IN1 Secondary Undervoltage or Overvoltage Selection<br>0 = Undervoltage<br>1 = Overvoltage              |

|                     |                          | [1]                                                                                          | IN2 Secondary Undervoltage or Overvoltage Selection                                                     |

| 0Eh                 | 8Eh                      | [2]                                                                                          | IN3 Secondary Undervoltage or Overvoltage Selection                                                     |

|                     | -                        | [3]                                                                                          | IN4 Secondary Undervoltage or Overvoltage Selection                                                     |

|                     |                          | [4]                                                                                          | IN5 Secondary Undervoltage or Overvoltage Selection                                                     |

|                     |                          | [5]                                                                                          | IN6 Secondary Undervoltage or Overvoltage Selection                                                     |

|                     |                          | [7:6]                                                                                        | Not Used                                                                                                |

|                     | [0]                      | IN1 Voltage Threshold Range<br>0 = 1V to 5.8V (20mV steps)<br>1 = 0.5V to 3.05V (10mV steps) |                                                                                                         |

|                     |                          | [1]                                                                                          | IN2 Voltage Threshold Range                                                                             |

| 0Fh                 | 8Fh                      | [2]                                                                                          | IN3 Voltage Threshold Range                                                                             |

|                     |                          | [3]                                                                                          | IN4 Voltage Threshold Range                                                                             |

|                     |                          | [4]                                                                                          | IN5 Voltage Threshold Range                                                                             |

|                     |                          | [5]                                                                                          | IN6 Voltage Threshold Range                                                                             |

|                     |                          | [7:6]                                                                                        | Not Used                                                                                                |

|                     |                          | [0]                                                                                          | IN1 Input Impedance<br>0 = Normal Mode<br>1 = High-Z Mode (connect external resistor voltage-divider)   |

|                     |                          | [1]                                                                                          | IN2 Input Impedance                                                                                     |

| 10h                 | 90h                      | [2]                                                                                          | IN3 Input Impedance                                                                                     |

| 1011                | 0011                     | [3]                                                                                          | IN4 Input Impedance                                                                                     |

|                     |                          | [4]                                                                                          | IN5 Input Impedance                                                                                     |

|                     |                          | [5]                                                                                          | IN6 Input Impedance                                                                                     |

|                     |                          | [7:6]                                                                                        | Not Used                                                                                                |

# MAX6884/MAX6885

#### External Voltage-Divider

To achieve thresholds from 0.1667V to 1.0167V in 3.3mV increments, program the respective input voltage detector for high impedance and use an external voltage-divider (see Figure 2). Set voltage-detector inputs for high impedance by programming bits R10h[5:0]. Design the resistor voltage-divider to scale the input voltage to between 0.1667V and 1.0167V at the input of the device. In this way, voltages higher than 5.8V and in between the 10mV and 20mV steps can be monitored. Program R00h through R0Eh to adjust the thresholds between 0.1667V and 1.0167V in 3.3mV steps.

#### AUXIN (MAX6884 Only)

The AUXIN high-impedance analog input is intended to monitor additional system voltages not required for reset purposes. The internal 10-bit ADC converts the voltage at AUXIN and stores the data in the ADC registers (see Table 3). AUXIN does not affect any of the programmable outputs. The AUXIN input accepts power-supply voltages or other system voltages scaled to the 1.25V ADC input voltage range.

Figure 2. External Voltage-Divider Architecture

#### MR

Program  $\overrightarrow{\text{RESET}}$  and/or  $\overrightarrow{\text{UV/OV}}$  to assert when manual reset input  $\overrightarrow{\text{MR}}$  is brought low (see Tables 5 and 6). Outputs programmed to assert when  $\overrightarrow{\text{MR}}$  is brought low remain asserted after  $\overrightarrow{\text{MR}}$  is brought high for their respective programmed timeout periods. An internal 10µA current source pulls  $\overrightarrow{\text{MR}}$  to V<sub>DBP</sub>. Leave  $\overrightarrow{\text{MR}}$  unconnected or connect to DBP if unused.

#### MARGIN

MARGIN allows system-level testing while power supplies exceed the normal ranges. Drive MARGIN low to hold the programmable outputs in their existing state while system-level testing occurs. Leave MARGIN unconnected or connect to DBP if unused. An internal 10µA current source pulls MARGIN to V<sub>DBP</sub>. The internal ADC continues to convert voltages while MARGIN is low. The state of each programmable output does not change while MARGIN = GND. MARGIN overrides MR if both are asserted at the same time.

#### REFIN (MAX6884 Only)

The MAX6884/MAX6885 feature an internal 1.25V voltage reference. The voltage reference sets the threshold of the voltage detectors and provides a reference voltage for the internal ADC. Program the MAX6884 to use an internal or external reference by programming bit R16h[7] (see Table 5). Leave REFIN unconnected when using the internal reference. REFIN accepts an external reference in the 1.225V to 1.275V range.

## Table 5. Internal/External Reference

| REGISTER<br>ADDRESS | EEPROM<br>MEMORY<br>ADDRESS | BIT<br>RANGE | DESCRIPTION                                                          |

|---------------------|-----------------------------|--------------|----------------------------------------------------------------------|

| 16h                 | 96h                         | [7]          | 1 = Enable External<br>Reference<br>0 = Enable Internal<br>Reference |

#### **Programmable Outputs**

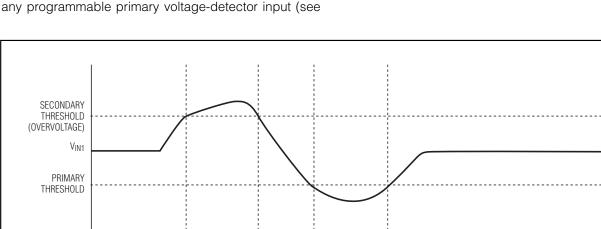

The MAX6884/MAX6885 feature three programmable active-low outputs: RESET, UV/OV, and WDO. Program each output for open-drain or weak pullup. An internal 10k $\Omega$  resistor connected from each output to a 2.55V internal LDO provides a weak pullup. During power-up, the outputs are held low for 1V < VCC < VUVLO. Any output programmed to depend on no condition always remains in its active state. For example, if the state of UV/OV is not programmed to depend on any condition, UV/OV will always be low. Figure 3 shows a timing diagram of a typical relationship between a monitored input voltage and outputs RESET and UV/OV. RESET and UV/OV are a function of only IN1.

Program RESET to depend on MR, UV/OV, WDO, or

Table 6). As an example, RESET may depend on the IN3 primary undervoltage threshold, MR, UV/OV, and WDO. Write 1's to R11h[1:0], R11h[4], and R12h[7] to configure as indicated. IN3 must be above the undervoltage threshold, MR must be high, UV/OV must be deasserted, and WDO must be deasserted to be a logic "1," then RESET deasserts. The logic state of RESET, in this example, is equivalent to the logical statement:

#### IN3 · MR · UV/OV · WDO

RESET remains low for its programmed timeout period (t<sub>RP</sub>) after all assertion-causing conditions are removed. Program timeout periods for RESET from 25µs to 1600ms (see Table 6). Configure RESET for open-drain or weak pullup through bit R12h[0].

RESET

Figure 3. Output Timing Diagram

UV/OV

RESET

## Table 6. Programmable **RESET** Options

| REGISTER<br>ADDRESS | EEPROM<br>MEMORY<br>ADDRESS | BIT RANGE | DESCRIPTION                                                                                                                                                                                                  |

|---------------------|-----------------------------|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                     |                             | [0]       | 1 = $\overline{\text{RESET}}$ Assertion Depends on $\overline{\text{MR}}$<br>0 = $\overline{\text{RESET}}$ Assertion Does Not Depend on $\overline{\text{MR}}$                                               |

|                     |                             | [1]       | 1 = $\overline{\text{RESET}}$ Assertion Depends on $\overline{\text{UV}/\text{OV}}$<br>0 = $\overline{\text{RESET}}$ Assertion Does Not Depend on $\overline{\text{UV}/\text{OV}}$                           |

|                     |                             | [2]       | 1 = RESET Assertion Depends on IN1 Primary Undervoltage<br>0 = RESET Assertion Does Not Depend on IN1 Primary Undervoltage                                                                                   |

| 11h                 | 91h                         | [3]       | 1 = RESET Assertion Depends on IN2 Primary Undervoltage<br>0 = RESET Assertion Does Not Depend on IN2 Primary Undervoltage                                                                                   |

|                     | 911                         | [4]       | 1 = RESET Assertion Depends on IN3 Primary Undervoltage<br>0 = RESET Assertion Does Not Depend on IN3 Primary Undervoltage                                                                                   |

|                     |                             | [5]       | 1 = RESET Assertion Depends on IN4 Primary Undervoltage<br>0 = RESET Assertion Does Not Depend on IN4 Primary Undervoltage                                                                                   |

|                     |                             | [6]       | 1 = RESET Assertion Depends on IN5 Primary Undervoltage<br>0 = RESET Assertion Does Not Depend on IN5 Primary Undervoltage                                                                                   |

|                     |                             | [7]       | 1 = RESET Assertion Depends on IN6 Primary Undervoltage<br>0 = RESET Assertion Does Not Depend on IN6 Primary Undervoltage                                                                                   |

|                     | 12h 92h                     | [0]       | RESET Output Type<br>1 = Open Drain<br>0 = Weak Pullup                                                                                                                                                       |

| 12h                 |                             | [3:1]     | RESET Deassertion Time Delay         000 = 25µs         001 = 1.56ms         010 = 6.25ms         011 = 25ms         100 = 50ms         101 = 200ms         110 = 400ms         111 = 1600ms                 |

|                     |                             | [6:4]     | Not Used                                                                                                                                                                                                     |

|                     |                             | [7]       | 1 = $\overrightarrow{\text{RESET}}$ Assertion Depends on $\overrightarrow{\text{WDO}}$ Assertion<br>0 = $\overrightarrow{\text{RESET}}$ Assertion Does Not Depend on $\overrightarrow{\text{WDO}}$ Assertion |

#### UV/OV

Program UV/OV to depend on MR, RESET, or any programmable secondary voltage detector input (see Table 7). As an example, UV/OV may depend on the IN1 secondary overvoltage threshold, MR, and RESET. Write 1's to R13h[2:0] and R0Eh[1] to configure as indicated. IN1 must be below the overvoltage threshold, MR must be high, and RESET must be deasserted to be a logic "1," then UV/OV deasserts. The logic state of  $\overline{\text{UV/OV}}$ , in this example, is equivalent to the logical statement:

#### IN1 · MR · RESET

$\overline{\text{UV/OV}}$  remains low for its programmed time delay (t<sub>UP</sub>) after all assertion-causing conditions are removed. Program time delays for  $\overline{\text{UV/OV}}$  from 25µs to 1600ms (see Table 7). Configure  $\overline{\text{UV/OV}}$  for open drain or weak pullup through bit R14h[0].

| REGISTER<br>ADDRESS | EEPROM<br>MEMORY<br>ADDRESS | BIT RANGE | DESCRIPTION                                                                                                                                                                                             |

|---------------------|-----------------------------|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                     |                             | [0]       | $1 = \overline{UV/OV}$ Assertion Depends on $\overline{MR}$<br>0 = $\overline{UV/OV}$ Assertion Does Not Depend on $\overline{MR}$                                                                      |

|                     |                             | [1]       | 1 = $\overline{UV/OV}$ Assertion Depends on $\overline{RESET}$<br>0 = $\overline{UV/OV}$ Assertion Does Not Depend on $\overline{RESET}$                                                                |

|                     |                             | [2]       | 1 = $\overline{UV/OV}$ Assertion Depends on IN1 Secondary Undervoltage/Overvoltage Threshold<br>0 = $\overline{UV/OV}$ Assertion Does Not Depend on IN1 Secondary Undervoltage/Overvoltage<br>Threshold |

|                     |                             | [3]       | 1 = $\overline{UV/OV}$ Assertion Depends on IN2 Secondary Undervoltage/Overvoltage Threshold<br>0 = $\overline{UV/OV}$ Assertion Does Not Depend on IN2 Secondary Undervoltage/Overvoltage<br>Threshold |

| 13h                 | 93h                         | [4]       | 1 = $\overline{UV/OV}$ Assertion Depends on IN3 Secondary Undervoltage/Overvoltage Threshold<br>0 = $\overline{UV/OV}$ Assertion Does Not Depend on IN3 Secondary Undervoltage/Overvoltage<br>Threshold |