### **General Description**

The MAX9680 high-speed amplifier and filter is optimized for portable video applications. It is specifically designed to be compatible with the video encoders embedded in application processors with 0.4VP-P video output. The input common-mode range includes GND, which allows a video DAC (digital-to-analog converter) to be DC-coupled to the MAX9680.

The output swings within 2mV of GND and 20mV to VDD with a standard back-terminated video load (150 $\Omega$ ). An internal level shift circuit prevents the output from saturating with 0V input, thus preventing sync-pulse clipping in common video circuits. Therefore, the MAX9680 is ideally suited for DC-coupling to the video load.

The MAX9680 has been optimized for space-sensitive applications by integrating internal gain setting resistors (G = 5.2V/V) and a 2-pole video-DAC reconstruction filter.

In shutdown mode, the guiescent current is reduced to less than 0.4µA, dramatically reducing power consumption and prolonging battery life.

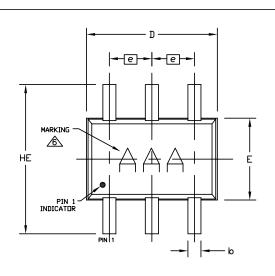

The MAX9680 is available in the tiny 2mm x 2.1mm, 6-pin, SC70 package.

#### **Applications**

Mobile Phones Digital Still Cameras Digital Video Cameras

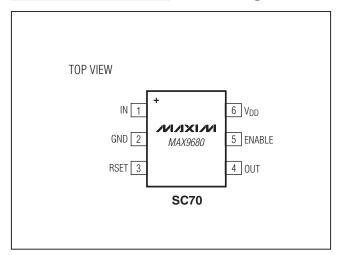

### **Pin Configuration**

#### Features

- ♦ 5.2V/V Internal Gain

- **♦ 2-Pole Reconstruction Filter**

- ♦ Input Range Includes Ground

- ♦ DC-Coupled Inputs and Outputs

- ♦ Rail-to-Rail Output

- ♦ 3.7mA Low Quiescent Current

- ♦ 0.4µA Shutdown Current

### **Ordering Information**

| PART         | TEMP            | PIN-    | TOP  |

|--------------|-----------------|---------|------|

|              | RANGE           | PACKAGE | MARK |

| MAX9680AXT+T | -40°C to +125°C | 6 SC70  | ADT  |

+Denotes a lead(Pb)-free/RoHS-compliant package.

T = Tape and reel.

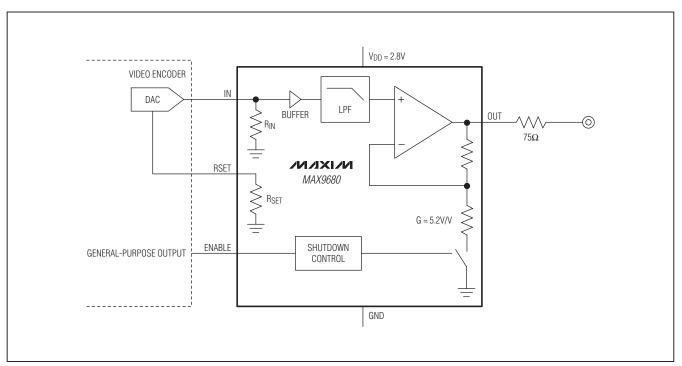

Typical Application Circuit appears at end of data sheet.

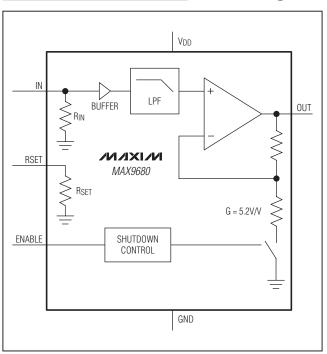

### **Block Diagram**

#### **ABSOLUTE MAXIMUM RATINGS**

| ADOOLO IL MAAMMOM           | 11/41111400                  |

|-----------------------------|------------------------------|

| Supply Voltage (VDD to GND) | 0.3V to +4V                  |

| ENABLE to GND               | 0.3V to +4V                  |

| IN to GND                   | $-0.3V$ to $(V_{DD} + 0.3V)$ |

| OUT to GND (ENABLE is high) | $-0.3V$ to $(V_{DD} + 0.3V)$ |

| OUT to GND (ENABLE is low)  | 0.3V to +3.2V                |

| ENABLE, IN                  | ±50mA                        |

| OUT                         | Continuous                   |

| Electrostatic Discharge     |                              |

| Human Body Model            | 2000V                        |

| Charged Device Model        | 500V                         |

| Continuous Power Dissipation (TA = +70°C) |                |

|-------------------------------------------|----------------|

| 6-Pin SC70 (derate 3.1mW/C above +70°C    | C)245mW        |

| Operating Temperature Range               | 40°C to +125°C |

| Junction Temperature                      | +150°C         |

| Storage Temperature Range                 | 65°C to +150°C |

| Lead Temperature (soldering, 10s)         | +300°C         |

| Soldering Temperature (reflow)            | +260°C         |

### PACKAGE THERMAL CHARACTERISTICS (Note 1)

SC.70

Junction-to-Ambient Thermal Resistance (θJA) .....326.5°C/W Junction-to-Case Thermal Resistance (θJC) .............115°C/W

**Note 1:** Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a 4-layer board. For detailed information on package thermal considerations, refer to <a href="https://www.maxim-ic.com/thermal-tutorial">www.maxim-ic.com/thermal-tutorial</a>.

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **ELECTRICAL CHARACTERISTICS**

$(V_{DD} = V_{ENABLE} = 2.8V, V_{GND} = 0V, R_L = 150\Omega \text{ to GND. T}_A = -40^{\circ}\text{C} \text{ to } +125^{\circ}\text{C}, \text{ unless otherwise noted. Typical values are at T}_A = +25^{\circ}\text{C}.)$  (Note 2)

| PARAMETER                               | SYMBOL | COND                                                                                                              | OITIONS      | MIN     | TYP  | MAX   | UNITS |

|-----------------------------------------|--------|-------------------------------------------------------------------------------------------------------------------|--------------|---------|------|-------|-------|

| OFFSET LEVEL-SHIFT VOLTAG               | GE     |                                                                                                                   |              |         |      |       |       |

| Output Level-Shift Voltage              | Vols   | VIN = VGND                                                                                                        |              | 0       | 120  | 250   | mV    |

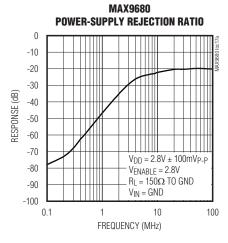

| Power-Supply Rejection Ratio            | PSRR   | VIN = VGND, VDD = 2                                                                                               | 2.7V to 3.6V |         | 200  |       | μV/V  |

| INPUT VOLTAGE RANGE                     |        |                                                                                                                   |              |         |      |       |       |

| January Valle and Danasa                | \/     | $V_{DD} = 2.7V$                                                                                                   |              | VGND    |      | 0.445 | - v   |

| Input Voltage Range                     | VCM    | V <sub>DD</sub> = 2.8V                                                                                            |              | VGND    |      | 0.464 |       |

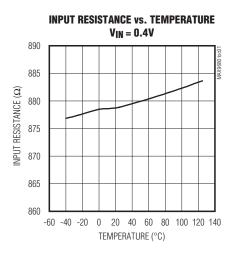

| Input Resistance (In+)                  | RIN    | V <sub>IN</sub> = 0.5V                                                                                            |              | 732     | 872  | 1012  | Ω     |

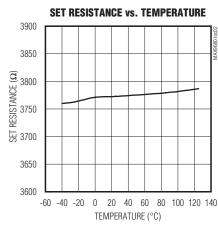

| RSET Resistance                         | RSET   | VRSET = 0.5V                                                                                                      |              | 3150    | 3750 | 4350  | Ω     |

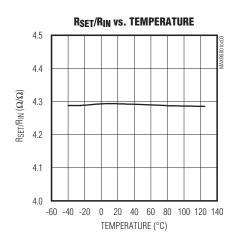

| R <sub>SET</sub> /R <sub>IN</sub> Ratio |        |                                                                                                                   |              | 4.214   | 4.3  | 4.386 |       |

| VOLTAGE GAIN                            |        |                                                                                                                   |              |         |      |       |       |

| DC Voltage Cain (Note 3)                | Δ.,    | V <sub>DD</sub> = 2.7V, V <sub>IN</sub> = V <sub>GND</sub> to 0.445V                                              |              | 5.00    | 5.17 | 5.34  | V/V   |

| DC Voltage Gain (Note 3)                | Av     | VDD = 2.8V, VIN = VGND to 0.464V                                                                                  |              | 5.00    | 5.17 | 5.34  |       |

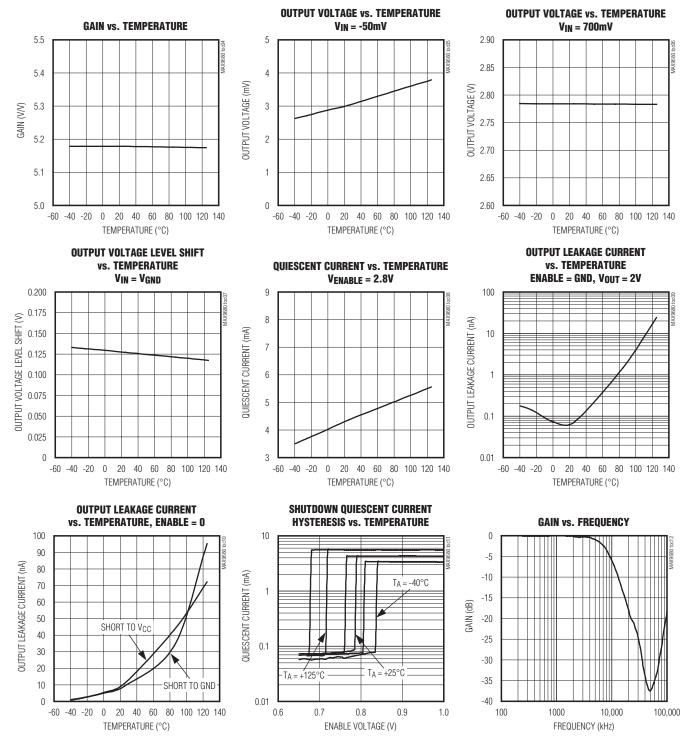

| FREQUENCY RESPONSE                      |        |                                                                                                                   |              |         |      |       |       |

|                                         |        |                                                                                                                   | f = 4.5MHz   |         | -0.2 |       |       |

| Filter Deepens                          |        | $V_{IN} = V_{GND}$ to                                                                                             | f = 9MHz     |         | -3.5 |       | dB    |

| Filter Response                         |        | 0.387V                                                                                                            | f = 27MHz    |         | -23  |       | a ab  |

|                                         |        |                                                                                                                   | f = 54MHz    |         | -45  |       |       |

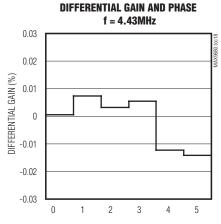

| Differential Gain Error                 |        | Five-step modulated staircase of 127.8mV step size and 305.3mV peak-to-peak subcarrier amplitude, f = 4.43MHz     |              |         | 0.2  |       | %     |

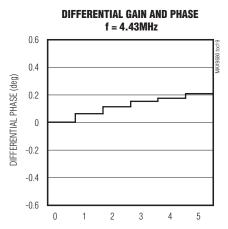

| Differential Phase Error                |        | Five-step modulated staircase of 127.8mV step size and 305.3mV peak-to-peak 0.3 subcarrier amplitude, f = 4.43MHz |              | degrees |      |       |       |

### **ELECTRICAL CHARACTERISTICS (continued)**

$(VDD = VENABLE = 2.8V, VGND = 0V, R_L = 150\Omega$  to GND. TA = -40°C to +125°C, unless otherwise noted. Typical values are at TA = +25°C.) (Note 2)

| PARAMETER                               | SYMBOL          | CONDITIONS                                                 | MIN | TYP | MAX             | UNITS |

|-----------------------------------------|-----------------|------------------------------------------------------------|-----|-----|-----------------|-------|

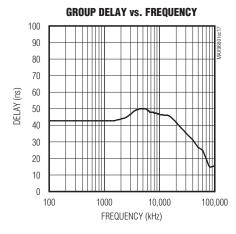

| Group Delay Variation                   |                 | $100kHz \le f \le 5.5MHz$ , $V_{IN} = V_{GND}$ to $0.387V$ |     | 15  |                 | ns    |

| Signal-to-Noise Ratio                   | SNR             | 100% white signal                                          |     | 65  |                 | dB    |

| OUTPUT                                  |                 |                                                            |     |     |                 |       |

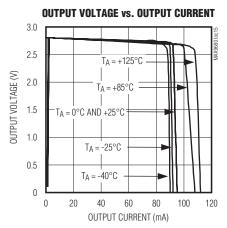

| Positive Voltage Output Swing from Rail |                 | V <sub>IN</sub> = 0.7V                                     |     | 20  | 250             | mV    |

| Negative Voltage Output Swing from Rail |                 | V <sub>IN</sub> = -0.05V                                   |     | 1.8 | 5               | mV    |

| Positive Voltage Output Swing from Rail |                 | $V_{IN}$ = 0.7V, $R_L$ = 75 $\Omega$ to GND                |     | 35  |                 | mV    |

| Negative Voltage Output Swing from Rail |                 | $V_{IN}$ = -0.05V, $R_L$ = 75 $\Omega$ to GND              |     | 1   |                 | mV    |

| Output Leakage                          |                 | Disabled, V <sub>OUT</sub> = 2V                            |     |     | 2               | μΑ    |

| Output Short-Circuit Current            | lout            | Short to GND                                               |     | 90  |                 | mA    |

| POWER SUPPLY                            |                 |                                                            |     |     |                 |       |

| Supply Voltage                          | V <sub>DD</sub> |                                                            | 2.7 |     | 3.6             | V     |

| Supply Current                          | IDD             | No load                                                    |     | 3.7 | 9               | mA    |

| ENABLE/SHUTDOWN FUNCTION                | N               |                                                            |     |     |                 |       |

| Disabled (Logic-Low Threshold)          |                 |                                                            | 0   |     | 0.45            | V     |

| Enabled (Logic-High Threshold)          |                 |                                                            | 1.3 |     | V <sub>DD</sub> | V     |

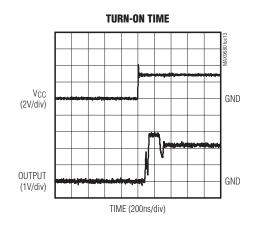

| Enable Time                             |                 |                                                            |     | 350 |                 | ns    |

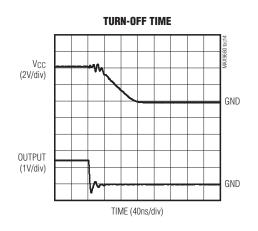

| Disable Time                            |                 |                                                            |     | 200 |                 | ns    |

| Shutdown Current                        |                 | Disabled                                                   |     | 0.4 | 4               | μA    |

Note 2: All devices are 100% production tested at  $T_A = +25$ °C. Specifications over temperature limits are guaranteed by design.

Note 3: Voltage gain (Ay) is a two-point measurement in which the output voltage swing is divided by the input voltage swing.

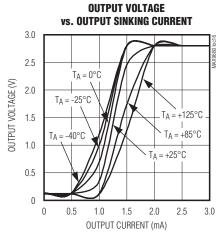

## Typical Operating Characteristics

$(V_{DD} = V_{ENABLE} = 2.8V, V_{GND} = 0V, R_L = 150\Omega$  to GND.  $T_A = +25$ °C, unless otherwise noted.)

## Typical Operating Characteristics (continued)

$(V_{DD} = V_{ENABLE} = 2.8V, V_{GND} = 0V, R_L = 150\Omega$  to GND.  $T_A = +25$ °C, unless otherwise noted.)

## Typical Operating Characteristics (continued)

$(V_{DD} = V_{ENABLE} = 2.8V, V_{GND} = 0V, R_L = 150\Omega$  to GND.  $T_A = +25$ °C, unless otherwise noted.)

### **Pin Description**

| PIN | NAME            | DESCRIPTION                                                                                                                                                                     |

|-----|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | IN              | Input                                                                                                                                                                           |

| 2   | GND             | Ground                                                                                                                                                                          |

| 3   | RSET            | Resistor Set. The reference voltage of the current digital-to-analog converter (DAC) is applied across the internal RSET resistor to generate the reference current of the DAC. |

| 4   | OUT             | Output                                                                                                                                                                          |

| 5   | ENABLE          | Enable. Drive high to enable the device. Pull low to disable the device.                                                                                                        |

| 6   | V <sub>DD</sub> | Positive Power Supply. Bypass to GND with a 0.1µF capacitor.                                                                                                                    |

## **Detailed Description**

The MAX9680 filters and amplifies the video DAC output in applications such as mobile phones. The MAX9680 consists of two resistors, an input buffer, lowpass filter, and output amplifier capable of driving a standard  $150\Omega$  video load to ground. The output amplifier provides a fixed gain of 5.17V/V.

#### RSET Resistor

The video current DAC imposes a reference voltage, VREF, across RSET. The resulting current (VREF/RSET) is the reference current for the video current DAC.

#### Input

The video input should be directly connected to the output of the video current DAC.  $R_{IN},$  the equivalent input resistance, is  $872\Omega$  to ground. The output current of the video DAC flows through  $R_{IN}$  to create the video signal in the voltage domain.

#### **Video Filter**

The filter bandwidth (-3dB) is typically 9MHz, making the device suitable for standard-definition video signals from all sources (e.g., broadcast and DVD). Broadcast video signals are channel limited: NTSC signals have 4.2MHz bandwidth, and PAL signals have 5MHz bandwidth. Video signals from a DVD player, however, are not channel limited; so the bandwidth of DVD video signals can approach the Nyquist limit of 6.75MHz. Recommendation: ITU-R BT.601-5 specifies 13.5MHz as the sampling rate

for standard-definition video. Therefore, the maximum bandwidth of the signal is 6.75MHz. To ease the filtering requirements, most modern video systems oversample by two times, clocking the video current DAC at 27MHz.

#### **Output**

The MAX9680 features 5.17V/V gain. Operating from a 2.7V to 3.6V supply, the output amplifier is able to drive a 2.3V signal into a 150 $\Omega$  video load to ground. The output is typically offset 120mV above ground to guarantee linear operation of the amplifier. The MAX9680 output only sources current; all loads should be connected to ground.

#### **Short-Circuit Protection**

The MAX9680 Typical Application Circuit includes a 75 $\Omega$  back-termination resistor that limits short-circuit currents for an external short applied at the video output. The MAX9680 features internal output short-circuit protection to prevent device damage in prototyping and applications where the amplifier output can be directly shorted.

Short-circuit protection activates if the output is short circuited and the output current exceeds 90mA. During short-circuit protection, the output of the MAX9680 is shut off for 18µs and then turns on for 0.6µs. If the short is still present, the MAX9680 output shuts off again. Extended short circuits result in a pulsed output. The device resumes normal operation after the short is removed.

## **Application Information**

#### **Input Considerations**

The MAX9680 input is DC-coupled. When the supply voltage is between 2.7V and 3.6V, the input voltage range extends from ground to 0.445V. When the supply voltage is between 2.8V and 3.6V, the input voltage range extends from ground to 0.464V. A typical current-output DAC that operates from a single supply usually creates a composite video signal with a sync tip very close to ground. Hence, the DAC output can be directly connected to the MAX9680 input. Keep the board trace as short as possible to minimize parasitic stray capacitance and prevent unintentional high-frequency attenuation.

#### **Output Considerations**

The MAX9680 output must be DC-coupled. No AC-coupled capacitors are allowed. The MAX9680 connects directly to the video cable through a  $75\Omega$  series back-termination resistor. The other end of the cable should be properly terminated with a  $75\Omega$  resistor as well. Because of this configuration, the peak-to-peak amplitude as well as the DC level of the signal is divided by two. The MAX9680 output signal is level-shifted up so the sync tip is approximately 120mV.

#### **Power-Supply Bypassing and Ground**

The MAX9680 operates from a single-supply voltage down to 2.7V, allowing for low-power operation. Bypass  $V_{DD}$  to GND with a 0.1 $\mu$ F capacitor. Place all external components as close as possible to the device.

## **Typical Application Circuit**

**Chip Information**

PROCESS: BICMOS

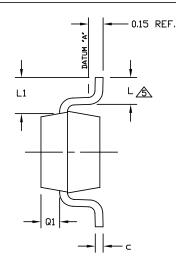

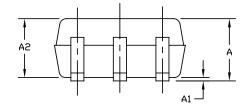

## **Package Information**

For the latest package outline information and land patterns, go to www.maxim-ic.com/packages. Note that a "+", "#", or "-" in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.

| PACKAGE TYPE | PACKAGE CODE | OUTLINE NO.    | LAND PATTERN NO. |

|--------------|--------------|----------------|------------------|

| 6 SC70       | X6SN+1       | <u>21-0077</u> | <u>90-0189</u>   |

| COMMON DIMENSIONS |                |      |      |  |  |  |

|-------------------|----------------|------|------|--|--|--|

| SYMBOL            | MIN            | NDM  | MAX  |  |  |  |

| Α                 | 0.80           | 0.95 | 1.10 |  |  |  |

| A1                | 0.00           | 0.07 | 0.10 |  |  |  |

| A2                | 0.80           | 0.90 | 1.00 |  |  |  |

| b                 | 0.15           | 0.22 | 0.30 |  |  |  |

| C                 | 0.10           | 0.14 | 0.18 |  |  |  |

| D                 | 1.85           | 2.00 | 2.15 |  |  |  |

| e                 | 0.65 BSC.      |      |      |  |  |  |

| Ε                 | 1.15 1.25 1.35 |      |      |  |  |  |

| HE                | 2.00           | 2.20 | 2.35 |  |  |  |

| L                 | 0.26           | 0.34 | 0.46 |  |  |  |

| L1                | 0.425 TYP.     |      |      |  |  |  |

| Q1                | 0.10           | 0.25 | 0.40 |  |  |  |

| PKG.<br>CODES     | X6SN-          | -1   |      |  |  |  |

#### NOTES:

- ALL DIMENSIONS ARE IN MILLIMETERS.

- DIMENSIONS ARE INCLUSIVE OF PLATING.

DIMENSIONS ARE EXCLUSIVE OF MOLD FLASH & METAL BURR.

- 4. COPLANARITY 4 MILS. MAX.

\$\frac{1}{2}\$\$ FOOT LENGTH MEASURED AT INTERCEPT POINT BETWEEN DATUM 'A' AND LEAD SURFACE.

- ⚠ MARKING IS FOR PACKAGE ORIENTATION REFERENCE ONLY. 7. LEAD CENTERLINES TO BE AT TRUE POSITION AS DEFINED BY

- BASIC DIMENSION' e', ±0.05.

ALL DIMENSIONS COMPLY TO JEDEC MO-203.

ALL DIMENSIONS APPLY TO BOTH LEADED (-) AND LEAD FREE (+) PACKAGE CODES.

PACKAGE DUTLINE, 6L SC70

DOCUMENT CONTROL NO. APPROVAL H 1/1 21-0077

-DRAWING NOT TO SCALE-

## Revision History

| REVISION<br>NUMBER | REVISION DATE | DESCRIPTION     | PAGES<br>CHANGED |

|--------------------|---------------|-----------------|------------------|

| 0                  | 9/09          | Initial release | _                |

| 1                  | 12/10         | Added PSRR TOC  | 5                |

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.