# ASSP Communication Network

# LAN Controller with PC Card, ISA Bus, and General-purpose Bus Interfaces

# **MB86967**

#### DESCRIPTION

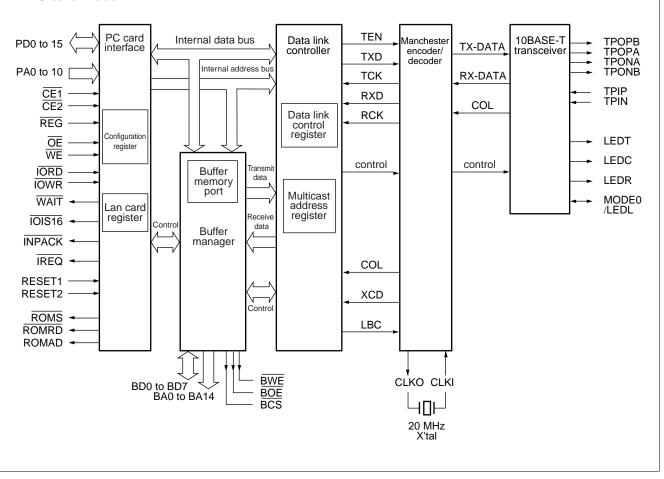

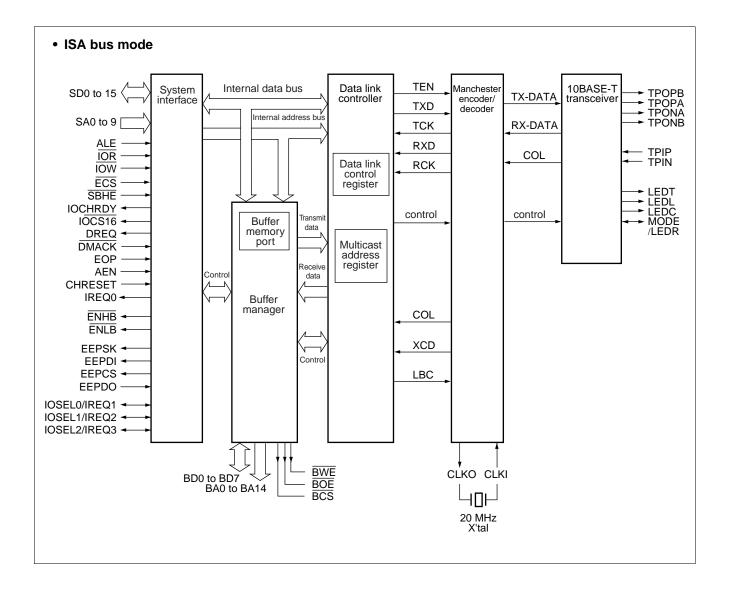

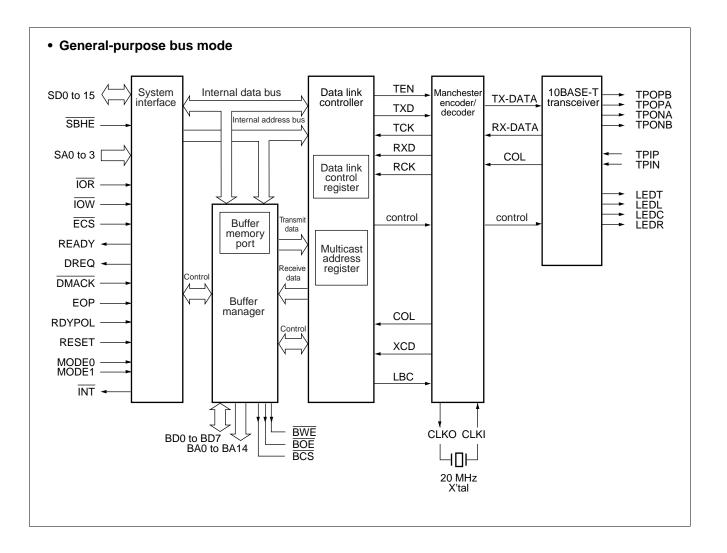

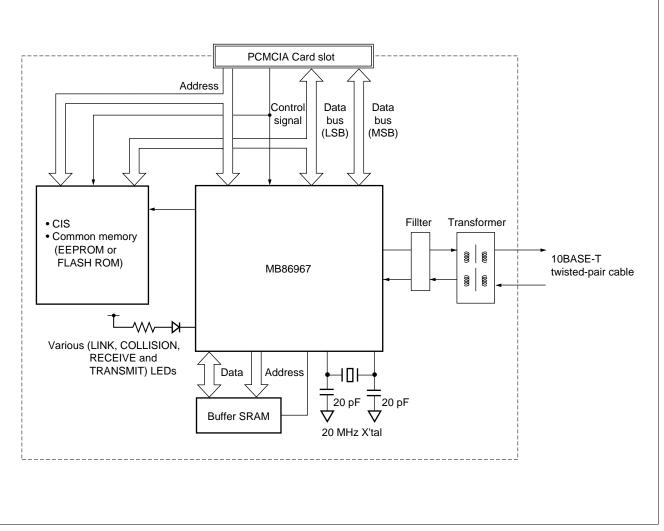

The MB86967 is a highly-integrated, high-performance single-chip Ethernet LAN controller which contains a PC card interface based on the JEIDA4.2 standard, an ISA bus interface that can be connected directly to the ISA bus, a general-purpose bus interface, a Manchester encoder/decoder based on the IEEE802.3 standard, and 10BASE-T transceiver.

The LAN controller and buffer manager are software compatible with the MB86965A and MB86964. The buffer manager has functions for arbitration and buffer management of external buffer memory (SRAM) which can be expanded to 32 KB. These functions provide simultaneous access from the host and data link controller and updating of transmit and receive buffer pointers. This permits substantial reduction of software overhead in buffer management.

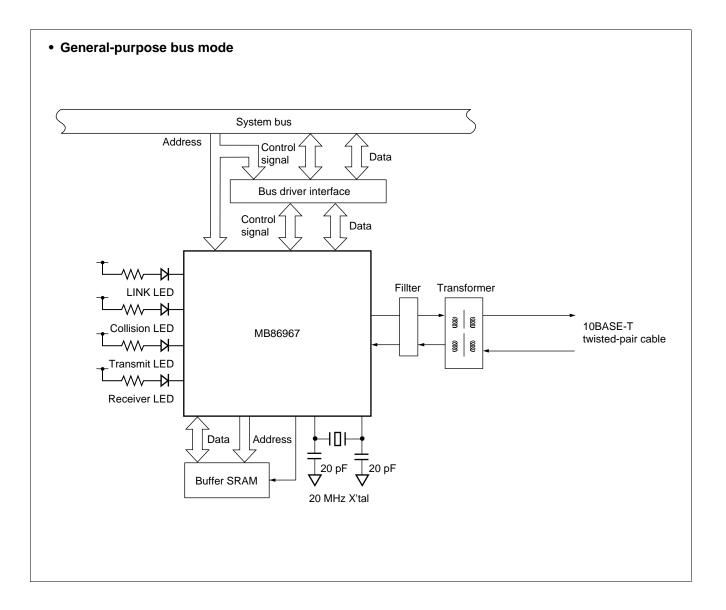

The Manchester encoder/decoder and 10BASE-T transceiver can be easily interfaced with twisted-pair cable just by addition of a pulse transformer and filter.

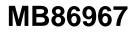

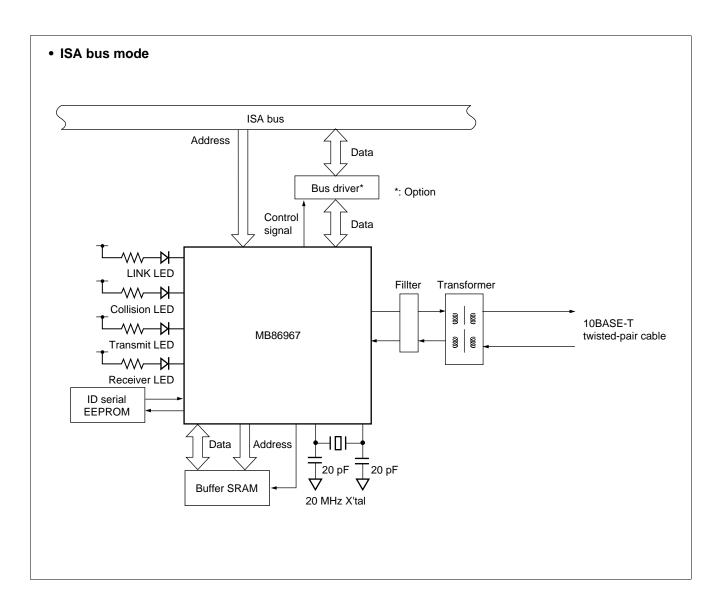

Mode pin setting allows the system interface to switch between the PC card interface, ISA bus interface, and general-purpose bus interface. When in the ISA bus interface mode, two modes can be selected: a jumperless mode allowing software setting of I/O addresses and interrupt signals, and a jumper mode allowing DIPswitch setting.

#### ■ FEATURES

System Interface

- Allows switching between PC card interface, ISA bus interface, and general-purpose bus interface

- Allows byte swapping of word data according to host CPU (in ISA bus mode and general-purpose bus mode)

- Has functions for high-speed burst DMA transfer and single DMA transfer (slave operation) (in ISA bus mode and general-purpose bus mode)

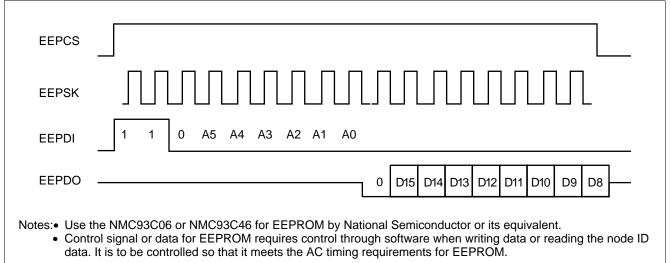

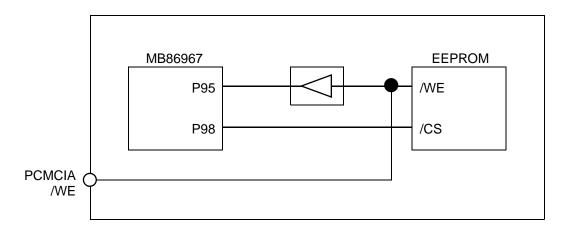

- Provides node ID EEPROM interface (in ISA bus mode)

- Allows software setting of I/O addresses and interrupt signals (in jumperless mode of ISA bus mode)

- Can be connected to 8-bit and 16-bit standard microprocessor buses (in general-purpose bus mode)

- Provides JEIDA protocol interface (in PC card mode)

- Has overlapping address window function (in PC card mode)

- Has memory control (common memory, attribute memory, I/O addresses) (in PC card mode)

#### LAN Interface

- Contains Manchester encoder/decoder based on IEEE802.3 standard and 10BASE-T transceiver

- Has functions for jabber control, link test, and SQE test

- Has functions for inversion detection and automatic correction

- Contains LED driver for monitoring network status (link test, collision, transmitting and receiving)

- Has function for 10BASE-T external loopback (full-duplex)

#### Controller

- Software compatible with MB86965A and MB86964

- Has dual-bank transmit buffer and ring receive buffer (expandable to 32 KB) set by program

- · Contains 64-bit hash table for multicast address filter

- Has function for removing receive long packets (1792-byte or more receive packets)

- Has two power-down modes; standby mode (continued crystal oscillation) and shut-down mode (stopped crystal oscillation)

#### Others

- Aluminum two-layer wiring CMOS technology

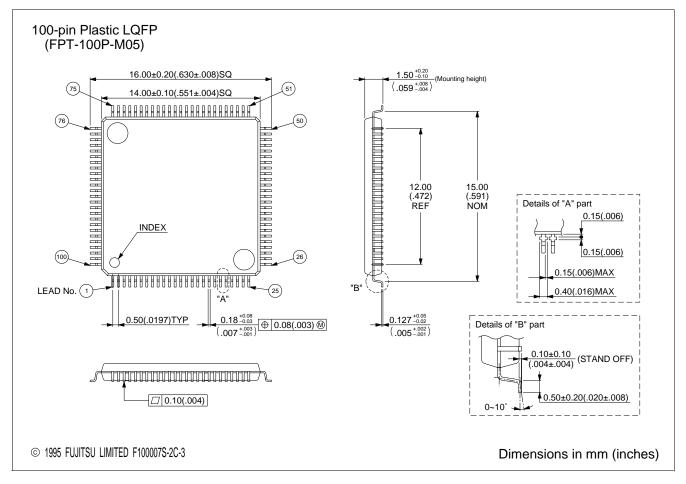

- 100-pin LQFP package

- Power-supply voltage of 5 V  $\pm$ 5%

#### PIN ASSIGNMENT

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | (Top view)                              |  |  |  |  |  |  |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|--|--|--|--|--|--|--|--|

| 0000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                         |  |  |  |  |  |  |  |  |

| 7         7         7         8         8         8         8         8         8         8         8         8         8         8         8         8         8         8         8         8         8         8         8         8         8         8         8         8         8         8         8         8         8         8         8         8         8         8         8         8         8         8         8         8         8         8         8         8         8         8         8         8         8         8         8         8         8         8         8         8         8         8         8         8         8         8         8         8         8         8         8         8         8         8         8         8         8         8         8         8         8         8         8         8         8         8         8         8         8         8         8         8         8         8         8         8         8         8         8         8         8         8         8         8         8         8         8 |                                         |  |  |  |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                         |  |  |  |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                         |  |  |  |  |  |  |  |  |

| 1<br>2<br>3<br>4<br>5<br>6<br>7<br>8<br>9<br>10<br>11<br>12<br>13<br>14<br>15<br>16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                         |  |  |  |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 73 🗄                                    |  |  |  |  |  |  |  |  |

| Ц <sup>4</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                         |  |  |  |  |  |  |  |  |

| <b>L</b> 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 71 🗖                                    |  |  |  |  |  |  |  |  |

| П6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 70 🏳                                    |  |  |  |  |  |  |  |  |

| Π7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 69 🗖                                    |  |  |  |  |  |  |  |  |

| □8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 68 🗖                                    |  |  |  |  |  |  |  |  |

| <b>□</b> 9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 67 🗖                                    |  |  |  |  |  |  |  |  |

| <b>d</b> 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 66 🏳                                    |  |  |  |  |  |  |  |  |

| □ 11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 65 🗖                                    |  |  |  |  |  |  |  |  |

| □ 12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                         |  |  |  |  |  |  |  |  |

| <b>d</b> 13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 63 🗖                                    |  |  |  |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                         |  |  |  |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 62 D<br>61 D                            |  |  |  |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 60 <b>E</b>                             |  |  |  |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                         |  |  |  |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                         |  |  |  |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                         |  |  |  |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 57 🗖                                    |  |  |  |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                         |  |  |  |  |  |  |  |  |

| □ 21                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 55 🗖                                    |  |  |  |  |  |  |  |  |

| □ 22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 54 🏳                                    |  |  |  |  |  |  |  |  |

| □ 23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 53 🗖                                    |  |  |  |  |  |  |  |  |

| □ 24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 53 ¤<br>52 ¤                            |  |  |  |  |  |  |  |  |

| □ 25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 51 🗖                                    |  |  |  |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 2 2 3 3 3 3 3 3 3 3 3 3 3 3 3 3 3 3 3 3 |  |  |  |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                         |  |  |  |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | (FPT-100P-M05)                          |  |  |  |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                         |  |  |  |  |  |  |  |  |

# **MB86967**

#### • PC card mode

| Pin no. | Symbol | I/O | Pin no. | Symbol | I/O | Pin no. | Symbol     | I/O   | Pin no. | Symbol            | I/O |

|---------|--------|-----|---------|--------|-----|---------|------------|-------|---------|-------------------|-----|

| 1       | Vdd1   | Р   | 26      | VDD2   | Р   | 51      | Vdd3       | Р     | 76      | GNDA2             | G   |

| 2       | INPACK | 0   | 27      | PD11   | BD  | 52      | MODE0/LEDL | IU/OD | 77      | TPOPB             | 0   |

| 3       | WAIT   | 0   | 28      | PD4    | BD  | 53      | BA6        | 0     | 78      | TPOPA             | 0   |

| 4       | PA0    | ID  | 29      | PD3    | BD  | 54      | BA5        | 0     | 79      | TPONA             | 0   |

| 5       | PA1    | ID  | 30      | BCS    | 0   | 55      | BA4        | 0     | 80      | TPONB             | 0   |

| 6       | PA2    | ID  | 31      | GND3   | G   | 56      | BA3        | 0     | 81      | VDDA2             | Р   |

| 7       | PA3    | ID  | 32      | BWE    | 0   | 57      | GND5       | G     | 82      | CE1               | IU  |

| 8       | PA4    | ID  | 33      | BOE    | 0   | 58      | BA2        | 0     | 83      | CE2               | IU  |

| 9       | PA5    | ID  | 34      | BD7    | В   | 59      | BA1        | 0     | 84      | IOIS16            | 0   |

| 10      | PA6    | ID  | 35      | BD6    | В   | 60      | BA0        | 0     | 85      | PD10              | BD  |

| 11      | PA7    | ID  | 36      | BD5    | В   | 61      | CLKO       | 0     | 86      | GND6              | G   |

| 12      | PA8    | ID  | 37      | BD4    | В   | 62      | CLKI       | Ι     | 87      | PD2               | BD  |

| 13      | PA9    | ID  | 38      | BD3    | В   | 63      | RESET2     | ISD   | 88      | PD9               | BD  |

| 14      | PA10   | ID  | 39      | BD2    | В   | 64      | RESET1     | ISU   | 89      | PD1               | BD  |

| 15      | IORD   | IU  | 40      | BD1    | В   | 65      | LEDR       | OD    | 90      | PD8               | BD  |

| 16      | GND1   | G   | 41      | BD0    | В   | 66      | LEDT       | OD    | 91      | PD0               | BD  |

| 17      | IOWR   | IU  | 42      | BA14   | 0   | 67      | GNDA1      | G     | 92      | IREQ              | 0   |

| 18      | PD15   | BD  | 43      | BA13   | 0   | 68      | LEDC       | OD    | 93      | REG               | IU  |

| 19      | PD14   | BD  | 44      | BA12   | 0   | 69      | NC0        | _     | 94      | V <sub>DD</sub> 4 | Р   |

| 20      | PD7    | BD  | 45      | BA11   | 0   | 70      | VDDA1      | Р     | 95      | WE                | IU  |

| 21      | PD13   | BD  | 46      | GND4   | G   | 71      | TPIP       | Ι     | 96      | OE                | IU  |

| 22      | PD6    | BD  | 47      | BA10   | 0   | 72      | TPIN       | I     | 97      | ROMAD             | 0   |

| 23      | PD12   | BD  | 48      | BA9    | 0   | 73      | GNDM       | I     | 98      | ROMS              | 0   |

| 24      | GND2   | G   | 49      | BA8    | 0   | 74      | NC1        | —     | 99      | ROMRD             | 0   |

| 25      | PD5    | BD  | 50      | BA7    | 0   | 75      | NC2        | —     | 100     | GND7              | G   |

I: Input O:Output ID: Input with pull-down resistorIS: Schmitt inputBD: Input/output with pull-down resistorIU: Input with pull-up resistor

P: Power supply G:Ground

B: Input/output OD:Open-drain output

#### • ISA bus mode

| Pin no. | Symbol  | I/O | Pin no. | Symbol | I/O | Pin no. | Symbol       | I/O  | Pin no. | Symbol | I/O |

|---------|---------|-----|---------|--------|-----|---------|--------------|------|---------|--------|-----|

| 1       | Vdd1    | Р   | 26      | Vdd2   | Р   | 51      | Vdd3         | Р    | 76      | GNDA2  | G   |

| 2       | DREQ    | 0   | 27      | SD11   | BD  | 52      | LEDL         | OD   | 77      | TPOPB  | 0   |

| 3       | IOCHRDY | OD  | 28      | SD4    | BD  | 53      | BA6          | 0    | 78      | TPOPA  | 0   |

| 4       | SA0     | ID  | 29      | SD3    | BD  | 54      | BA5          | 0    | 79      | TPONA  | 0   |

| 5       | SA1     | ID  | 30      | BCS    | 0   | 55      | BA4          | 0    | 80      | TPONB  | 0   |

| 6       | SA2     | ID  | 31      | GND3   | G   | 56      | BA3          | 0    | 81      | VDDA2  | Р   |

| 7       | SA3     | ID  | 32      | BWE    | 0   | 57      | GND5         | G    | 82      | SBHE   | IU  |

| 8       | SA4     | ID  | 33      | BOE    | 0   | 58      | BA2          | 0    | 83      | DMACK  | IU  |

| 9       | SA5     | ID  | 34      | BD7    | В   | 59      | BA1          | 0    | 84      | IOIS16 | OD  |

| 10      | SA6     | ID  | 35      | BD6    | В   | 60      | BA0          | 0    | 85      | SD10   | BD  |

| 11      | SA7     | ID  | 36      | BD5    | В   | 61      | CLKO         | 0    | 86      | GND6   | G   |

| 12      | SA8     | ID  | 37      | BD4    | В   | 62      | CLKI         | Ι    | 87      | SD2    | BD  |

| 13      | SA9     | ID  | 38      | BD3    | В   | 63      | AEN          | ISD  | 88      | SD9    | BD  |

| 14      | ALE     | ID  | 39      | BD2    | В   | 64      | CHRESET      | ISU  | 89      | SD1    | BD  |

| 15      | IOR     | IU  | 40      | BD1    | В   | 65      | EOP          | ID   | 90      | SD8    | BD  |

| 16      | GND1    | G   | 41      | BD0    | В   | 66      | LEDT         | OD   | 91      | SD0    | BD  |

| 17      | IOW     | IU  | 42      | BA14   | 0   | 67      | GNDA1        | G    | 92      | IREQ0  | 0   |

| 18      | SD15    | BD  | 43      | BA13   | 0   | 68      | LEDC         | OD   | 93      | ENHB   | 0   |

| 19      | SD14    | BD  | 44      | BA12   | 0   | 69      | IREQ1/IOSEL0 | IU/O | 94      | VDD4   | Р   |

| 20      | SD7     | BD  | 45      | BA11   | 0   | 70      | VDDA1        | Р    | 95      | ENLB   | 0   |

| 21      | SD13    | BD  | 46      | GND4   | G   | 71      | TPIP         | Ι    | 96      | EEPDO  | IU  |

| 22      | SD6     | BD  | 47      | BA10   | 0   | 72      | TPIN         | I    | 97      | EEPDI  | 0   |

| 23      | SD12    | BD  | 48      | BA9    | 0   | 73      | MODE/LEDR    | I/OD | 98      | EEPCS  | 0   |

| 24      | GND2    | G   | 49      | BA8    | 0   | 74      | IREQ2/IOSEL1 | IU/O | 99      | EEPSK  | 0   |

| 25      | SD5     | BD  | 50      | BA7    | 0   | 75      | IREQ3/IOSEL2 | IU/O | 100     | GND7   | G   |

I: Input O:Output ID: Input with pull-down resistor IS: Schmitt input BD: Input/output with pull-down resistor IU: Input with pull-up resistor

P: Power supply G:Ground

B: Input/output OD: Open-drain output

# **MB86967**

#### • General-purpose bus mode

| Pin no. | Symbol | I/O | Pin no. | Symbol | I/O | Pin no. | Symbol | I/O | Pin no. | Symbol        | I/O |

|---------|--------|-----|---------|--------|-----|---------|--------|-----|---------|---------------|-----|

| 1       | Vdd1   | Р   | 26      | Vdd2   | Р   | 51      | Vdd3   | Р   | 76      | GNDA2         | G   |

| 2       | DREQ   | 0   | 27      | SD11   | BD  | 52      | MODE0  | IU  | 77      | TPOPB         | 0   |

| 3       | READY  | 0   | 28      | SD4    | BD  | 53      | BA6    | 0   | 78      | TPOPA         | 0   |

| 4       | SA0    | ID  | 29      | SD3    | BD  | 54      | BA5    | 0   | 79      | TPONA         | 0   |

| 5       | SA1    | ID  | 30      | BCS    | 0   | 55      | BA4    | 0   | 80      | TPONB         | 0   |

| 6       | SA2    | ID  | 31      | GND3   | G   | 56      | BA3    | 0   | 81      | VDDA2         | Р   |

| 7       | SA3    | ID  | 32      | BWE    | 0   | 57      | GND5   | G   | 82      | ECS           | I   |

| 8       | MODE1  | ID  | 33      | BOE    | 0   | 58      | BA2    | 0   | 83      | N.C           | —   |

| 9       | N.C    | —   | 34      | BD7    | В   | 59      | BA1    | 0   | 84      | N.C           | —   |

| 10      | RDYPOL | ID  | 35      | BD6    | В   | 60      | BA0    | 0   | 85      | SD10          | BD  |

| 11      | BHE    | ID  | 36      | BD5    | В   | 61      | CLKO   | 0   | 86      | GND6          | G   |

| 12      | DMACK  | ID  | 37      | BD4    | В   | 62      | CLKI   | Ι   | 87      | SD2           | BD  |

| 13      | EOP    | ID  | 38      | BD3    | В   | 63      | N.C    | _   | 88      | SD9           | BD  |

| 14      | N.C    |     | 39      | BD2    | В   | 64      | HWRST  | ISU | 89      | SD1           | BD  |

| 15      | IOR    | lu  | 40      | BD1    | В   | 65      | LEDR   | OD  | 90      | SD8           | BD  |

| 16      | GND1   | G   | 41      | BD0    | В   | 66      | N.C    | _   | 91      | SD0           | BD  |

| 17      | IOW    | lu  | 42      | BA14   | 0   | 67      | GNDA1  | G   | 92      | INT           | 0   |

| 18      | SD15   | BD  | 43      | BA13   | 0   | 68      | N.C    | _   | 93      | LEDT          | OD  |

| 19      | SD14   | BD  | 44      | BA12   | 0   | 69      | N.C    | —   | 94      | Vdd4          | Р   |

| 20      | SD7    | BD  | 45      | BA11   | 0   | 70      | VDDA1  | Р   | 95      | LEDL          | OD  |

| 21      | SD13   | BD  | 46      | GND4   | G   | 71      | TPIP   | Ι   | 96      | LEDC          | OD  |

| 22      | SD6    | BD  | 47      | BA10   | 0   | 72      | TPIN   | I   | 97      | N.C           | —   |

| 23      | SD12   | BD  | 48      | BA9    | 0   | 73      | GNDM   | G   | 98      | <u>SB</u> /SW | 0   |

| 24      | GND2   | G   | 49      | BA8    | 0   | 74      | N.C    | _   | 99      | N.C           | —   |

| 25      | SD5    | BD  | 50      | BA7    | 0   | 75      | N.C    | —   | 100     | GND7          | G   |

I: Input O:Output ID: Input with pull-down resistorIS: Schmitt inputBD: Input/output with pull-down resistorIU: Input with pull-up resistor

IS: Schmitt input

P: Power supply G:Ground

B: Input/output OD:Open-drain output

#### ■ PIN DESCRIPTION

#### • System interface pins in PC card mode

| Pin no.                                          | Symbol      | Pin name                         | I/O | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|--------------------------------------------------|-------------|----------------------------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 18 to 23,<br>25,<br>27 to 29,<br>85,<br>87 to 91 | PD0 to PD15 | PC CARD DATA BUS                 | BD  | PD15 for most significant bit and PD0 for least significant bit. A built-in 150-k $\Omega$ pull-down resistor eliminates the need for any resistor on the card.                                                                                                                                                                                                                                                                                                                                     |

| 4 to 14                                          | PA0 to PA10 | PC CARD ADDRESS<br>BUS           | ID  | PA10 for most significant bit and PA0 for least significant bit. PA0 is invalid at word access. A built-in $150$ -k $\Omega$ pull-down resistor eliminates the need for any resistor on the card.                                                                                                                                                                                                                                                                                                   |

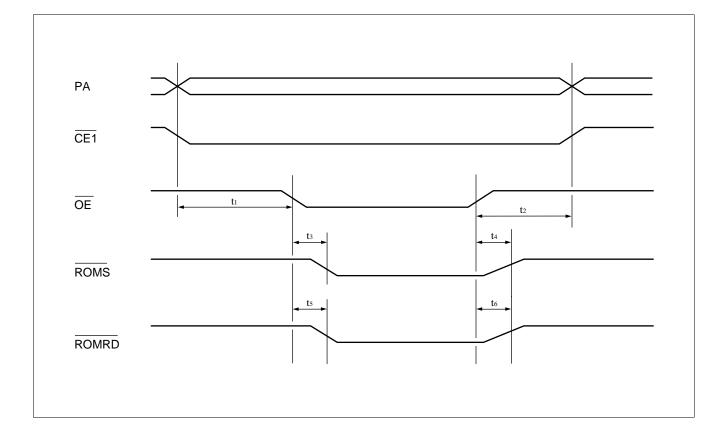

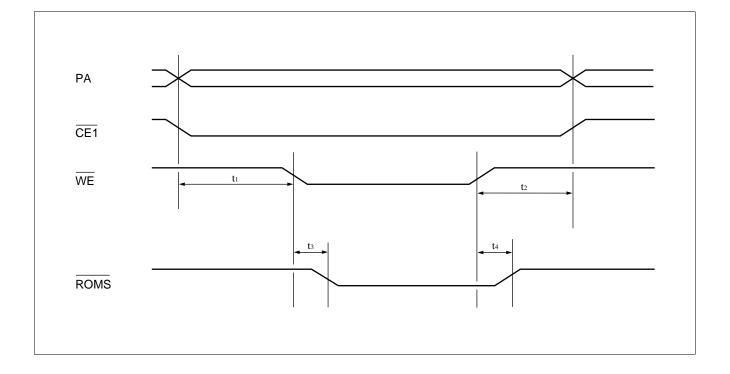

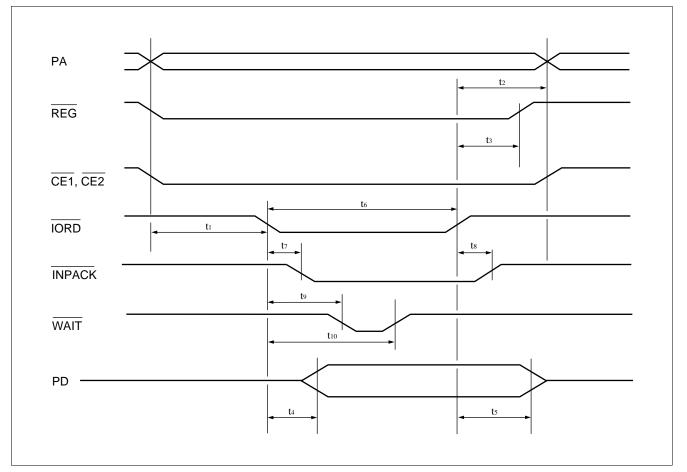

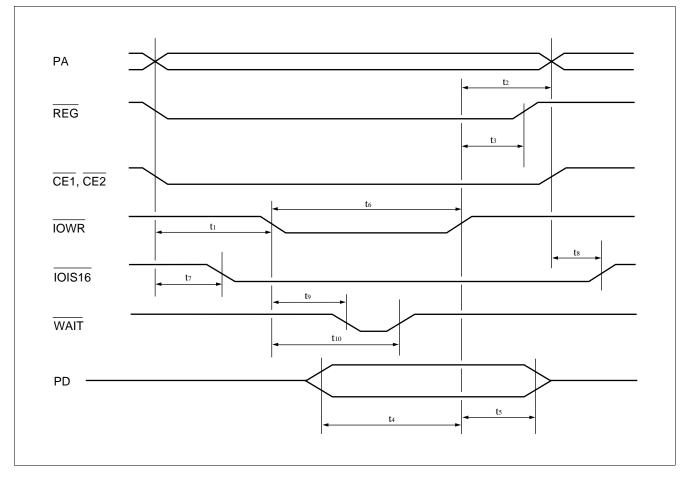

| 82<br>83                                         | CE1<br>CE2  | CARD ENABLE 1,2                  | IU  | CE1 controls even addresses and $\overline{CE2}$ controls odd<br>addresses. At power-on or after reset-canceling,<br>these pins must be kept High for 20 ms to initialize<br>the I/O card.                                                                                                                                                                                                                                                                                                          |

| 96                                               | OE          | OUTPUT ENABLE                    | IU  | This pin is used to control the output of read data from attribute memory space.                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 95                                               | WE          | WRITE ENABLE                     | IU  | This pin is used to control a write operation to attribute memory space.                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 93                                               | REG         | REGISTER SELECT                  | IU  | This pin must be kept Non-active High at access to<br>common memory. Keeping this pin Low accesses<br>attribute memory by OE/WE. The I/O area is<br>accessed by IORD/IOWE. Attribute memory is<br>allocated only to even addresses. Therefore, for word<br>access, data signals PD0 to PD7 are valid and PD8<br>to PD15 are invalid. Access to odd addresses is<br>disabled at byte access. When setting IORD/IOWE<br>Low during DMA operation, REG must be kept High<br>to prevent illegal access. |

| 64                                               | RESET1      | HARDWARE RESET1<br>(Active High) | ISU | This pin is used to clear the card configuration register (CCR), set the card to an unset state (IC card interface mode), and initialize the pointers and registers in the LAN controller and 10BASE-T transceiver. When power is applied to the card, the system must keep this pin High or high-impedance for 1 ms after the power supply has stabilized. A built-in 150-k $\Omega$ pull-down resistor eliminates the need for any resistor on the card.                                          |

| 63                                               | RESET2      | HARDWARE RESET2<br>(Active High) | ISD | This pin is internally ORed with RESET1 and contains a 50-k $\Omega$ pull-down resistor.                                                                                                                                                                                                                                                                                                                                                                                                            |

| 15                                               | IORD        | I/O READ                         | IU  | This pin is used to read data from the I/O area. The MB86967 sends no response to IORD until a write operation to the CCR sets the card to the I/O card interface mode.                                                                                                                                                                                                                                                                                                                             |

| 17                                               | IOWR        | I/O WRITE                        | IU  | This pin is used to write data to the I/O area. The MB86967 sends no response to IOWR until a write operation to the CCR sets the card to the I/O card interface mode.                                                                                                                                                                                                                                                                                                                              |

| 3                                                | WAIT        | WAIT                             | 0   | A Low level is output to this pin to delay the end of an I/O access cycle in progress.                                                                                                                                                                                                                                                                                                                                                                                                              |

| Pin no. | Symbol | Pin name             | I/O | Function                                                                                                                                                                                                                                                                                                                                                                                                        |

|---------|--------|----------------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2       | INPACK | INPUT RESPONSE       | 0   | When CE,REG, and IORD are 0s and the address on<br>the address bus agrees with the I/O port in the card,<br>a Low level is output to this pin. When I/O addresses<br>are independent, a Low level is always output to this<br>pin when CE,REG, and IORD are 0s.                                                                                                                                                 |

| 84      | IOIS16 | 16-BIT I/O PORT      | 0   | When 16-bit access (word access) to the I/O port is possible, a Low level is output to this pin. When a High level is output to this pin, the system has 8-bit access (byte access).                                                                                                                                                                                                                            |

|         |        |                      |     | Note: In the IC memory interface mode (no write<br>operation to the CCR) when power is applied<br>and a reset is canceled, this pin serves as a<br>WP+ (write-protect) pin. Under this condition, a<br>High level is output to this pin (write-protect).<br>1 should be set in the device ID tuple, WPS, in<br>the CIS to perform a write operation to the card.                                                |

| 92      | IREQ   | INTERRUPT<br>REQUEST | 0   | A Low level is output to this pin to request software<br>service from the system. For no interrupt request, a<br>High level is output to this pin. An interrupt signal is<br>sent to one of the interrupt request signals on the bus<br>in the system via the socket interface.                                                                                                                                 |

|         |        |                      |     | Note: In IC memory interface mode (no write<br>operation to the CCR) when power is applied<br>and a reset is canceled, this pin serves as a<br>+RDY/BSY pin. Under this condition, a High<br>level (+RDY) is output to this pin.                                                                                                                                                                                |

| 98      | ROMS   | ROM SELECT           | 0   | This pin is used for output of EEPROM OR FLASH chip select signals.                                                                                                                                                                                                                                                                                                                                             |

| 99      | ROMRD  | ROM READ             | 0   | This pin is used for output of EEPROM OR FLASH read signals.                                                                                                                                                                                                                                                                                                                                                    |

| 97      | ROMAD  | ROM ADDRESS          | 0   | This pin is used when I/O-reading the I/O number.<br>Connection of this pin to the most significant address<br>of EEPROM OR FLASH permits I/O-reading of<br>address space in the upper half of ROM. For a write<br>operation, both the write enable (WE) and I/O write<br>(IOWR) pins must be enabled. If there is no need to<br>set the ID number in the CIS for I/O-reading, this pin<br>should be kept open. |

• System interface pins in ISA bus mode

| Pin no.                                          | Symbol      | Pin name                                         | I/O |                                                                                                                                                                                                                                   |                        | Fu              | nction                                                                                                                   |  |

|--------------------------------------------------|-------------|--------------------------------------------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|-----------------|--------------------------------------------------------------------------------------------------------------------------|--|

| 18 to 23,<br>25,<br>27 to 29,<br>85,<br>87 to 91 | SD0 to SD15 | SYSTEM DATA BUS                                  | BD  | These pins are used as data buses for data<br>exchange between the host system and the<br>MB86967. They are also used for DMA transfer.<br>the 8-bit bus mode (bit 5 of DLCR6 = 1), only the<br>lower bits (SD0 to SD7) are used. |                        |                 |                                                                                                                          |  |

| 4 to 13                                          | SA0 to SA9  | SYSTEM ADDRESS<br>BUS                            | ID  |                                                                                                                                                                                                                                   |                        |                 | nput of system address controller registers.                                                                             |  |

| 64                                               | CHRESET     | CHIP RESET<br>(Active High)                      | ISU | This pin is                                                                                                                                                                                                                       | s used for             | r input         | of hardware reset signals.                                                                                               |  |

| 15                                               | IOR         | I/O READ<br>(Active Low)                         | IU  | This pin is                                                                                                                                                                                                                       | s used for             | r input         | of I/O read strobe signals.                                                                                              |  |

| 17                                               | IOW         | I/O WRITE<br>(Active Low)                        | IU  | This pin is                                                                                                                                                                                                                       | s used for             | r input         | of I/O write strobe signals.                                                                                             |  |

| 63                                               | AEN         | ADDRESS ENABLE<br>(Active High)                  | ISD | This pin is used for input of signals indicating the DMA controller controls the system bus.                                                                                                                                      |                        |                 |                                                                                                                          |  |

| 65                                               | EOP         | END OF PROCESS<br>(Active High or Active<br>Low) | ID  | This pin is used for input of signals indicating the er<br>of DMA transfer between the buffer memory and ho<br>system. At input of EOP, the next BREQ is not outp<br>and the handshaking cycle is terminated.                     |                        |                 |                                                                                                                          |  |

| 14                                               | ALE         | ADDRESS LATCH<br>ENABLE                          | ID  | This pin is used for input of signals indicating that the addresses of SA0 to SA9 are determined.                                                                                                                                 |                        |                 |                                                                                                                          |  |

| 82                                               | SBHE        | SYSTEM BUS HIGH<br>ENABLE                        | IU  | the 16-bit<br>0), this pir                                                                                                                                                                                                        | data bus<br>n, togethe | mode<br>er with | olling byte/word transfer. In<br>(bit 5 (SB/SW) of DLCR6 =<br>SA0, controls word transfer<br>and lower bytes on the data |  |

|                                                  |             |                                                  |     | SB/SW                                                                                                                                                                                                                             | SBHE                   | SA0             | Function                                                                                                                 |  |

|                                                  |             |                                                  |     | 0                                                                                                                                                                                                                                 | 0                      | 0               | Word transfer                                                                                                            |  |

|                                                  |             |                                                  |     | 0                                                                                                                                                                                                                                 | 0                      | 1               | Transfer of upper bytes on data bus (SD15 to SD8)                                                                        |  |

|                                                  |             |                                                  |     | 0                                                                                                                                                                                                                                 | 1                      | 0               | Transfer of lower bytes on data bus (SD7 to SD0)                                                                         |  |

|                                                  |             |                                                  |     | 0                                                                                                                                                                                                                                 | 1                      | 1               | Unused                                                                                                                   |  |

|                                                  |             |                                                  |     | 1                                                                                                                                                                                                                                 | ×                      | ×               | Byte transfer<br>(SD7 to SD0)                                                                                            |  |

|                                                  |             |                                                  |     | ×: don't ca                                                                                                                                                                                                                       | are                    |                 |                                                                                                                          |  |

| 2                                                | DREQ        | DMA REQUEST<br>(Active High)                     | 0   | This pin is signals.                                                                                                                                                                                                              | s used for             | r outpu         | ut of DMA transfer request                                                                                               |  |

| Pin no.              | Symbol                                                | Pin name                                                       | I/O  |                      |                       | Functio     | n                                                            |

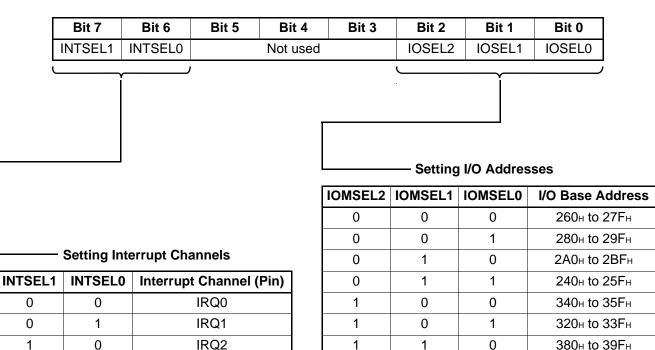

|----------------------|-------------------------------------------------------|----------------------------------------------------------------|------|----------------------|-----------------------|-------------|--------------------------------------------------------------|

| 69<br>74<br>75<br>92 | IREQ1/IOSEL0<br>IREQ2/IOSEL1<br>IREQ3/IOSEL2<br>IREQ0 | INTERRUPT<br>REQUEST 0 to 3<br>(Active High)                   | IU/O |                      | s are use<br>IREQ3 is |             | t of IR signals. One of<br>y configuration data in           |

|                      |                                                       | I/O ADDRESS<br>SELECT                                          |      |                      | s are use             |             | the I/O base<br>ontroller is allocated.                      |

|                      |                                                       |                                                                |      | IOSEL2               | IOSEL1                | IOSEL0      | I/O Base Address                                             |

|                      |                                                       |                                                                |      | 0                    | 0                     | 0           | 260н to 27Fн                                                 |

|                      |                                                       |                                                                |      | 0                    | 0                     | 1           | 280н to 29Fн                                                 |

|                      |                                                       |                                                                |      | 0                    | 1                     | 0           | 2A0н to 2BFн                                                 |

|                      |                                                       |                                                                |      | 0                    | 1                     | 1           | 240н to 25Fн                                                 |

|                      |                                                       |                                                                |      | 1                    | 0                     | 0           | 340н to 35Fн                                                 |

|                      |                                                       |                                                                |      | 1                    | 0                     | 1           | 320н to 33Fн                                                 |

|                      |                                                       |                                                                |      | 1                    | 1                     | 0           | 380н to 39Fн                                                 |

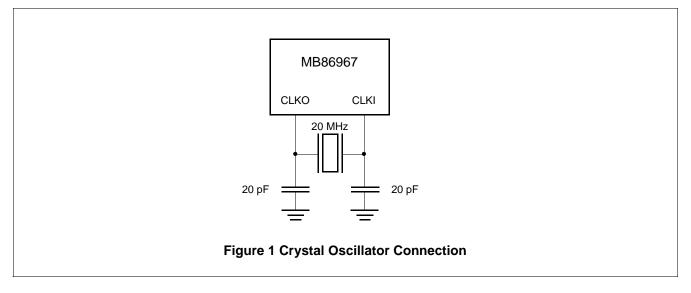

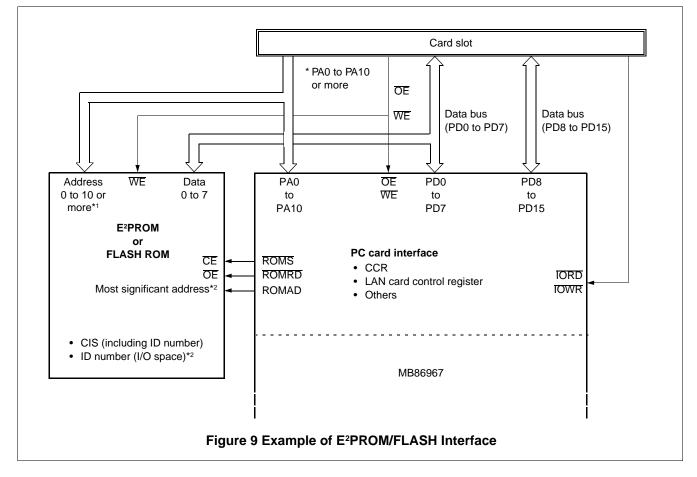

|                      |                                                       |                                                                |      | 1                    | 1                     | 1           | 300н to 31Fн                                                 |