# 16-bit Constant Current LED Sink Driver with Error Detection

#### **Features**

- Error Detection mode to detect LED open-circuit errors

- 16 constant-current output channels

- Constant output current invariant to load voltage change

- Excellent output current accuracy: between channels: ±3% (max.), and between ICs: ±6% (max.)

- Output current adjusted through an external resistor

- Constant output current range: 5-90 mA

- Fast response of output current,  $\overline{OE}$  (min.): 200 ns

- 25MHz clock frequency

- Schmitt trigger input

- 5V supply voltage

| Current                      | Conditions |                                  |  |  |

|------------------------------|------------|----------------------------------|--|--|

| Between Channels Between ICs |            | Conditions                       |  |  |

| < ±3%                        | < ±6%      | I <sub>OUT</sub> = 10 mA ~ 60 mA |  |  |

### **Product Description**

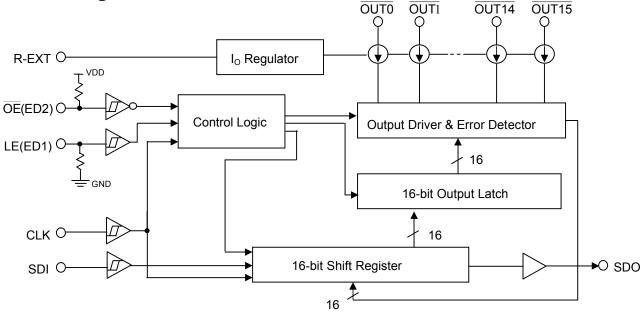

MBI5027 succeeds MBI5026 and is designed for LED displays with open-circuit Error Detection extension. MBI5027 exploits PrecisionDrive™ technology to enhance its output characteristics. MBI5027 contains a serial buffer and data latches, which convert serial input data into parallel output format. At MBI5027 output stage, sixteen regulated current ports are designed to provide uniform and constant current sinks for driving LEDs within a wide range of Vf variations.

While MBI5027 is used in their system design for LED display applications, e.g. LED panels, it provides users with great flexibility and device performance. Users may adjust the output current from 5 mA to 90 mA through an external resistor, R<sub>ext</sub>, which gives users flexibility in controlling the light intensity of LEDs. MBI5027 guarantees to endure maximum 17V at the output port. The high clock frequency, 25 MHz, also satisfies the system requirements of high volume data transmission.

MBI5027 exploits the idea of Share-I-O™ technology to extend its performance; in addition, MBI5027 is backward compatible with MBI5026 in both electrical characteristics and package aspect. With Share-I-O™ technology, users can, without changing the printed circuit board originally for MBI5026, let MBI5027 enter a special function mode, an Error Detection mode, just by setting a sequence of signals on LE(ED1),  $\overline{OE}$  (ED2) and CLK input pins. In the Error Detection mode, MBI5027 detects the status of individual LED connected to MBI5027. The status will be saved in a built-in register. Then, a system controller may read, through SDO pin, the error status from the register to know whether LEDs are properly lit or not. By setting another sequence of signals on LE(ED1),  $\overline{OE}$  (ED2) and CLK input pins, MBI5027 may resume to a Normal mode and perform as MBI5026. In **Application Information**, users can get detailed ideas about how MBI5027 works in the Error Detection mode.

A Share-I-O™ technique is specifically applied to MBI5027. By means of the Share-I-O™ technique, an additionally effective function, Error Detection, can be added to LED drivers, however, without any extra pins. Thus, MBI5027 could be a drop-in replacement of MBI5026. The printed circuit board originally designed for MBI5026 may be also applicable for MBI5027.

For MBI5027, the pin 4, LE(ED1), and the pin 21,  $\overline{OE}$  (ED2), can be acted as different functions as follows:

- 2 -

| Pin Device Name                | MBI5027                    |

|--------------------------------|----------------------------|

| Function Description of Pin 4  | LE + Error Detection (ED1) |

| Function Description of Pin 21 | OE + Error Detection (ED2) |

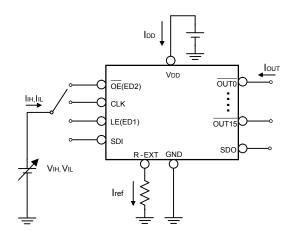

# **Block Diagram**

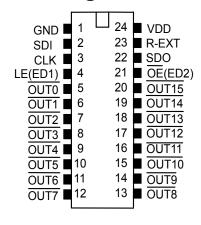

### **Terminal Description**

| Pin No. | Pin Name     | Function                                                                                                                                                                                                             |

|---------|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | GND          | Ground terminal for control logic and current sink                                                                                                                                                                   |

| 2       | SDI          | Serial-data input to the Shift Register                                                                                                                                                                              |

| 3       | CLK          | Clock input terminal for data shift on rising edge                                                                                                                                                                   |

|         |              | Data strobe input terminal                                                                                                                                                                                           |

| 4       | LE(ED1)      | Serial data is transferred to the respective latch when LE(ED1) is high. The data is latched when LE(ED1) goes low.                                                                                                  |

|         |              | Also, a control signal input for Error<br>Detection mode (See <b>Timing Diagram</b> )                                                                                                                                |

| 5~20    | OUT0 ~ OUT15 | Constant current output terminals                                                                                                                                                                                    |

| 21      | OE (ED2)     | Output enable terminal When (active) low, the output drivers are enabled; when high, all output drivers are turned OFF (blanked). Also, a control signal input for Error Detection mode (See <b>Timing Diagram</b> ) |

| 22      | SDO          | Serial-data output to the following SDI of next driver IC                                                                                                                                                            |

| 23      | R-EXT        | Input terminal used to connect an external resistor for setting up all output current                                                                                                                                |

| 24      | VDD          | 5V supply voltage terminal                                                                                                                                                                                           |

# **Pin Configuration**

# **Equivalent Circuits of Inputs and Outputs**

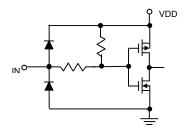

OE(ED2) terminal

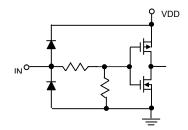

LE(ED1) terminal

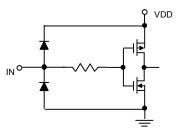

**CLK**, SDI terminal

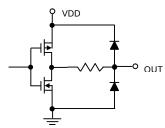

#### **SDO terminal**

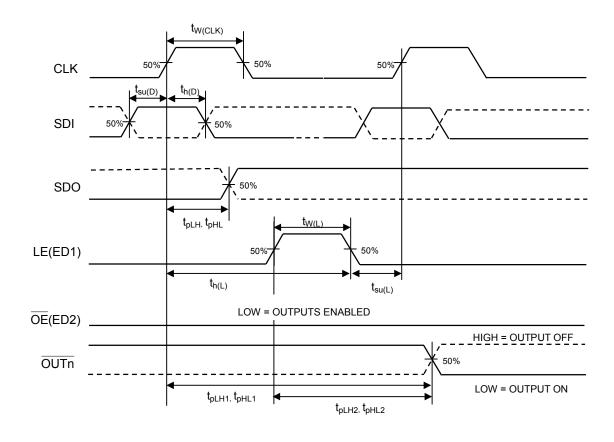

# **Timing Diagram**

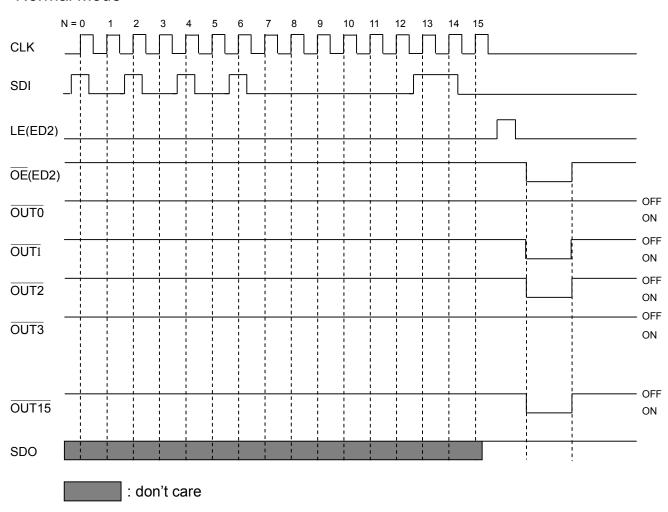

### **Normal Mode**

### **Truth Table (In Normal Mode)**

| CLK      | LE | ŌĒ | SDI              | OUT0OUT7OUT15                                                           | SDO               |

|----------|----|----|------------------|-------------------------------------------------------------------------|-------------------|

|          | Н  | L  | $D_n$            | Dn Dn - 7 Dn - 15                                                       | D <sub>n-15</sub> |

| <u>_</u> | L  | L  | D <sub>n+1</sub> | No Change                                                               | D <sub>n-14</sub> |

|          | Н  | L  | D <sub>n+2</sub> | $\overline{D}_{n+2} \dots \overline{D}_{n-5} \dots \overline{D}_{n-13}$ | D <sub>n-13</sub> |

|          | Х  | L  | D <sub>n+3</sub> | Dn + 2 Dn - 5 Dn - 13                                                   | D <sub>n-13</sub> |

| <b>—</b> | Х  | Н  | D <sub>n+3</sub> | Off                                                                     | D <sub>n-13</sub> |

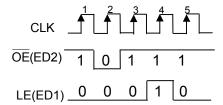

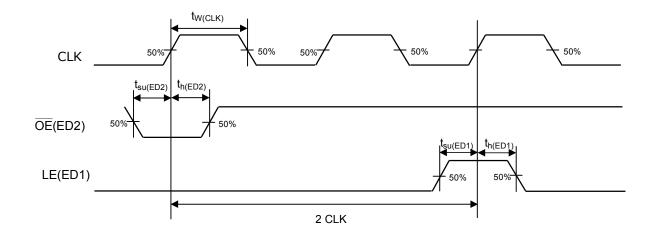

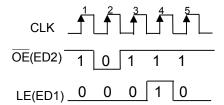

### **Entering Error Detection Mode**

The signal sequence makes MBI5027 enter an Error Detection mode.

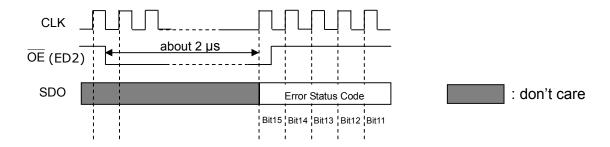

### **Reading Error Status Code**

A system controller can read Error Status codes through SDO pin.

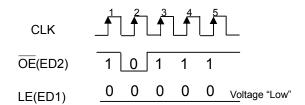

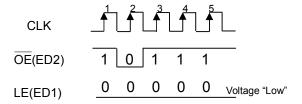

### **Resuming to Normal Mode**

The signal sequence makes MBI5027 resume to the Normal mode.

#### Note:

If users want to know the whole process, that is how to enter the Error Detection mode, read Error Status codes and resume to the Normal mode, please refer to the contents in **Application Information**.

# **Maximum Ratings**

| Character                                      | Symbol     | Rating           | Unit                       |      |

|------------------------------------------------|------------|------------------|----------------------------|------|

| Supply Voltage                                 | $V_{DD}$   | 0~7.0            | V                          |      |

| Input Voltage                                  |            | V <sub>IN</sub>  | -0.4~V <sub>DD</sub> + 0.4 | V    |

| Output Current                                 |            | I <sub>OUT</sub> | +90                        | mA   |

| Output Voltage                                 |            | V <sub>DS</sub>  | -0.5~+20.0                 | V    |

| Clock Frequency                                |            | F <sub>CLK</sub> | 25                         | MHz  |

| GND Terminal Current                           |            | I <sub>GND</sub> | 1440                       | mA   |

|                                                | CNS – type |                  | 1.52                       |      |

| Power Dissipation<br>(On PCB, Ta=25°C)         | CF – type  | $P_{D}$          | 1.30                       | W    |

| (6 62, 16. 26 6)                               | CP – type  |                  | 1.11                       |      |

|                                                | CNS – type |                  | 82                         |      |

| Thermal Resistance (On PCB, Ta=25°C) CF – type |            | $R_{th(j-a)}$    | 96                         | °C/W |

| (5 52, 12 20 0)                                | CP – type  |                  | 112                        |      |

| Operating Temperature                          |            | T <sub>opr</sub> | -40~+85                    | °C   |

| Storage Temperature                            |            | T <sub>stg</sub> | -55~+150                   | °C   |

# **Recommended Operating Conditions**

| Characteristic          | Symbol                          | Condition                                | Min.               | Тур. | Max.                 | Unit |

|-------------------------|---------------------------------|------------------------------------------|--------------------|------|----------------------|------|

| Supply Voltage          | $V_{DD}$                        | -                                        | 4.5                | 5.0  | 5.5                  | V    |

| Output Voltage          | V <sub>DS</sub>                 | OUT0∼ OUT15                              | -                  | -    | 17.0                 | V    |

|                         | I <sub>OUT</sub>                | DC Test Circuit                          | 5                  | -    | 60                   | mA   |

| Output Current          | I <sub>OH</sub>                 | SDO                                      | -                  | -    | -1.0                 | mA   |

|                         | I <sub>OL</sub>                 | SDO                                      | -                  | -    | 1.0                  | mA   |

| Input Voltage           | V <sub>IH</sub>                 | CLK, OE (ED2),<br>LE(ED1) and SDI        | 0.8V <sub>DD</sub> | -    | V <sub>DD</sub> +0.3 | V    |

| input voltage           | V <sub>IL</sub>                 | CLK, OE (ED2),<br>LE(ED1) and SDI        | -0.3               | -    | 0.3V <sub>DD</sub>   | V    |

| LE(ED1) Pulse Width     | $t_{w(L)}$                      |                                          | 40                 | -    | -                    | ns   |

| CLK Pulse Width         | t <sub>w(CLK)</sub>             |                                          | 20                 | -    | -                    | ns   |

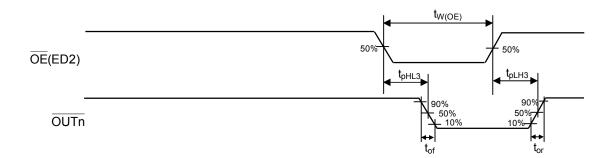

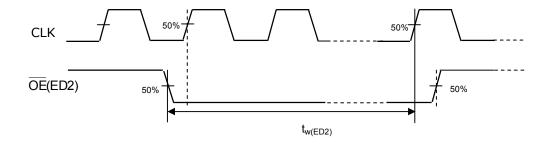

| OE (ED2) Pulse Width    | t <sub>w(OE)</sub>              |                                          | 200                | -    | -                    | ns   |

| Setup Time for SDI      | t <sub>su(D)</sub>              | Normal Mode<br>V <sub>DD</sub> =4.5~5.5V | 5                  | -    | -                    | ns   |

| Hold Time for SDI       | t <sub>h(D)</sub>               |                                          | 10                 | -    | -                    | ns   |

| Setup Time for LE(ED1)  | t <sub>su(L)</sub>              |                                          | 15                 | -    | -                    | ns   |

| Hold Time for LE(ED1)   | t <sub>h(L)</sub>               |                                          | 15                 | -    | -                    | ns   |

| OE (ED2) Pulse Width    | t <sub>w(ED2)</sub>             |                                          | 2                  | -    | -                    | us   |

| CLK Pulse Width         | t <sub>w(CLK)</sub>             |                                          | 20                 | -    | -                    | ns   |

| Setup Time for LE(ED1)  | t <sub>su(ED1)</sub>            | Error Detection Mode                     | 5                  | -    | -                    | ns   |

| Hold Time for LE(ED1)   | t <sub>h(ED1)</sub>             | V <sub>DD</sub> =4.5~5.5V                | 10                 | -    | -                    | ns   |

| Setup Time for OE (ED2) | t <sub>su(ED2)</sub>            |                                          | 5                  | -    | -                    | ns   |

| Hold Time for OE (ED2)  | t <sub>h(ED2)</sub>             |                                          | 10                 | -    | -                    | ns   |

| Clock Frequency         | F <sub>CLK</sub>                | Cascade Operation                        | -                  | -    | 25.0                 | MHz  |

|                         |                                 | Ta=85°C (CNS type)                       | -                  | -    | 0.79                 |      |

| Power Dissipation       | ower Dissipation P <sub>D</sub> | Ta=85°C (CF type)                        | -                  | -    | 0.67                 | W    |

|                         |                                 | Ta=85°C (CP type)                        | -                  | -    | 0.57                 |      |

#### **Electrical Characteristics**

| Characteristic                    |                                              | Symbol                  | Conc                                                                                        | lition                  | Min.               | Тур. | Max.               | Unit  |

|-----------------------------------|----------------------------------------------|-------------------------|---------------------------------------------------------------------------------------------|-------------------------|--------------------|------|--------------------|-------|

| Input "H" level Voltage "L" level |                                              | V <sub>IH</sub>         | Ta = -4                                                                                     | 0~85°C                  | 0.8V <sub>DD</sub> | -    | $V_{DD}$           | V     |

|                                   |                                              | V <sub>IL</sub>         | Ta = -40~85°C                                                                               |                         | GND                | 1    | 0.3V <sub>DD</sub> | V     |

| Output Leakage Current            |                                              | I <sub>OH</sub>         | V <sub>OH</sub> =17.0V                                                                      |                         | -                  | -    | 0.5                | μΑ    |

| Output                            | SDO                                          | V <sub>OL</sub>         | I <sub>OL</sub> =+1.0mA                                                                     |                         | -                  | -    | 0.4                | V     |

| Voltage                           | 300                                          | V <sub>OH</sub>         | I <sub>OH</sub> =-1.0mA                                                                     |                         | 4.6                | -    | -                  | V     |

| Output                            | Current 1                                    | I <sub>OUT1</sub>       | V <sub>DS</sub> =0.6V                                                                       | R <sub>ext</sub> =720 Ω | -                  | 25.0 | -                  | mA    |

| Curre                             | nt Skew                                      | dl <sub>OUT1</sub>      | I <sub>OL</sub> =25mA<br>V <sub>DS</sub> =0.6V                                              | R <sub>ext</sub> =720 Ω | -                  | ±1   | ±3                 | %     |

| Output                            | Current 2                                    | I <sub>OUT2</sub>       | V <sub>DS</sub> =0.8V                                                                       | R <sub>ext</sub> =360 Ω | -                  | 50.0 | -                  | mA    |

| Current Skew                      |                                              | dl <sub>OUT2</sub>      | I <sub>OL</sub> =50mA<br>V <sub>DS</sub> =0.8V                                              | R <sub>ext</sub> =360 Ω | -                  | ±1   | ±3                 | %     |

|                                   | Output Current vs. Output Voltage Regulation |                         | V <sub>DS</sub> within 1.0V and 3.0V                                                        |                         | -                  | ±0.1 | -                  | % / V |

| Output Curre<br>Supply Volta      | ent vs.<br>ge Regulation                     | %/dV <sub>DD</sub>      | V <sub>DD</sub> within 4.                                                                   | 5V and 5.5V             | -                  | ±1   | -                  | % / V |

| Pull-up Res                       | sistor                                       | R <sub>IN</sub> (up)    | ŌE (                                                                                        | ED2)                    | 250                | 500  | 800                | ΚΩ    |

| Pull-down F                       | Resistor                                     | R <sub>IN</sub> (down)  | LE(I                                                                                        | ED1)                    | 250                | 500  | 800                | ΚΩ    |

|                                   |                                              | $V_{DS, Th1}$           | When all output ports sink 20mA simultaneously                                              |                         | 1.0                | ı    | -                  | V     |

| Open Circu                        | it Error***                                  | $V_{DS, Th2}$           | When a single output port sinks 20mA                                                        |                         | 0.8                | ı    | -                  | V     |

| Discrimination                    | n Voltage                                    | $V_{DS, Th3}$           | When all output p simultaneously                                                            | 1.2                     | -                  | -    | V                  |       |

|                                   |                                              | V <sub>DS, Th4</sub>    | When a single output port sinks 50mA                                                        |                         | 1.0                | ı    | -                  | V     |

|                                   |                                              | I <sub>DD</sub> (off) 1 | R <sub>ext</sub> =Open, OU                                                                  | <br>Γ0 ~ OUT15 =Off     | -                  | 9    | 9 -                |       |

| 0                                 | "OFF"                                        | I <sub>DD</sub> (off) 2 | $R_{ext}$ =720 $\Omega$ , $\overline{OUT0} \sim \overline{OUT15}$ =Off                      |                         | -                  | 11   | -                  |       |

| Supply<br>Current                 |                                              | I <sub>DD</sub> (off) 3 | $R_{\text{ext}}$ =360 $\Omega$ , $\overline{\text{OUT0}} \sim \overline{\text{OUT15}}$ =Off |                         | -                  | 14   | -                  | mA    |

|                                   | "ON"                                         | I <sub>DD</sub> (on) 1  | R <sub>ext</sub> =720 Ω, OU                                                                 | T0 ~ OUT15 =On          | -                  | 11   | -                  |       |

|                                   | 511                                          | I <sub>DD</sub> (on) 2  | $R_{\text{ext}}$ =360 $\Omega$ , $\overline{OU}$                                            | T0 ~ OUT15 =On          | -                  | 14   | -                  |       |

<sup>\*\*\*</sup> To effectively detect the error occurring at the output port, MBI5027 has a built-in current detection circuit. The current detection circuit will detect the effective current  $I_{OUT, \text{ effective}}$ , and compare the effective current  $I_{OUT, \text{ effective}}$ , to the target current  $I_{OUT, \text{ target}}$ , defined by  $R_{\text{ext}}$ . If  $I_{OUT, \text{ effective}}$ , is much less than the target current  $I_{OUT, \text{ target}}$ , an error flag will be asserted in the built-in Shift Register. The minimum voltage requirement for such current detection is VDs, Th1, VDs, Th2, VDs, Th3 and VDs, Th4.

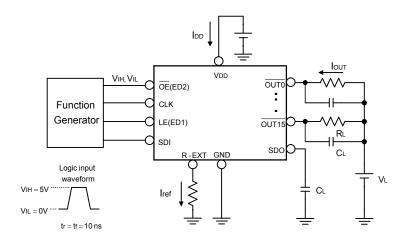

# **Test Circuit for Electrical Characteristics**

# **Switching Characteristics**

| Characteristic           |                 | Symbol              | Condition                                                    | Min. | Тур. | Max. | Unit |

|--------------------------|-----------------|---------------------|--------------------------------------------------------------|------|------|------|------|

|                          | CLK - OUTn      | t <sub>pLH1</sub>   |                                                              | -    | 50   | 100  | ns   |

| Propagation Delay Time   | LE(ED1) - OUTn  | t <sub>pLH2</sub>   |                                                              | -    | 50   | 100  | ns   |

| ("L" to "H")             | OE (ED2) - OUTn | t <sub>pLH3</sub>   |                                                              | -    | 20   | 100  | ns   |

|                          | CLK - SDO       | t <sub>pLH</sub>    |                                                              | 15   | 20   | -    | ns   |

|                          | CLK - OUTn      | t <sub>pHL1</sub>   | $V_{DD}$ =5.0 V $V_{DS}$ =0.8 V                              | -    | 100  | 150  | ns   |

| Propagation Delay Time   | LE(ED1) - OUTn  | t <sub>pHL2</sub>   | $V_{IH}=V_{DD}$                                              | -    | 100  | 150  | ns   |

| ("H" to "L")             | OE (ED2) - OUTn | t <sub>pHL3</sub>   | $V_{IL}$ =GND<br>$R_{ext}$ =300 $\Omega$<br>$V_{L}$ =4.0 $V$ | -    | 50   | 150  | ns   |

|                          | CLK - SDO       | t <sub>pHL</sub>    |                                                              | 15   | 20   | -    | ns   |

|                          | CLK             | t <sub>w(CLK)</sub> | $R_L$ =52 Ω $C_L$ =10 pF                                     | 20   | -    | -    | ns   |

| Pulse Width              | LE(ED1)         | t <sub>w(L)</sub>   |                                                              | 20   | -    | -    | ns   |

|                          | OE (ED2)        | t <sub>w(OE)</sub>  |                                                              | 200  | -    | -    | ns   |

| Hold Time for L          | -E(ED1)         | t <sub>h(L)</sub>   |                                                              | 5    | -    | -    | ns   |

| Setup Time for           | LE(ED1)         | t <sub>su(L)</sub>  |                                                              | 5    | -    | -    | ns   |

| Maximum CLK Rise Time    |                 | t <sub>r</sub> **   |                                                              | -    | -    | 500  | ns   |

| Maximum CLK Fall Time    |                 | t <sub>f</sub> **   |                                                              | -    | -    | 500  | ns   |

| Output Rise Time of lout |                 | t <sub>or</sub>     |                                                              | -    | 70   | 200  | ns   |

| Output Fall Tim          | e of lout       | t <sub>of</sub>     |                                                              | -    | 40   | 120  | ns   |

<sup>\*\*</sup>If the devices are connected in cascade and  $t_r$  or  $t_f$  is large, it may be critical to achieve the timing required for data transfer between two cascaded devices.

### **Test Circuit for Switching Characteristics**

# **Timing Waveform**

### **Normal Mode**

# **Entering Error Detection Mode**

# **Reading Error Status Code**

### **Application Information**

#### **Constant Current**

To design LED displays, MBI5027 provides nearly no variations in current from channel to channel and from IC to IC. This can be achieved by:

- 1) The maximum current variation between channels is less than  $\pm 3\%$  and that between ICs is less than  $\pm 6\%$ .

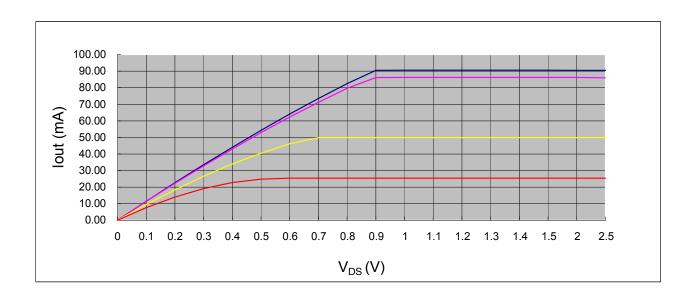

- 2) In addition, the current characteristic of output stage is flat and users can refer to the figure as shown below. The output current can be kept constant regardless of the variations of LED forward voltages (Vf). This performs as a complete function of the load regulation.

### **Adjusting Output Current**

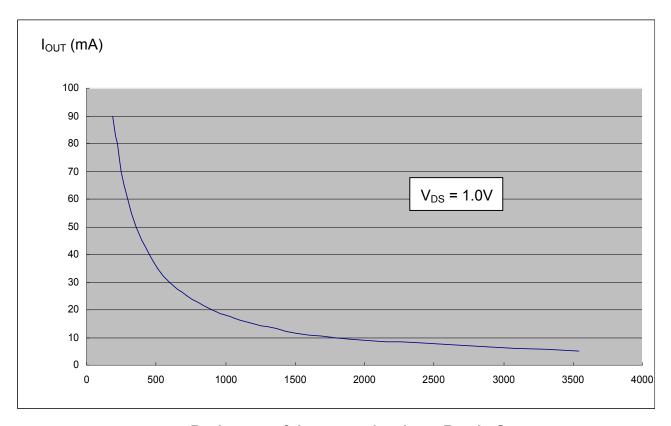

The output current of each channel ( $I_{OUT}$ ) is set by an external resistor,  $R_{ext}$ . The relationship between  $I_{out}$  and  $R_{ext}$  is shown in the following figure.

Resistance of the external resistor,  $R_{\text{ext}}$ , in  $\Omega$

Also, the output current in milliamps can be calculated from the equation:

$I_{OUT}$  is (625/  $R_{ext}$ ) x 28.8, approximately,

where  $R_{\text{ext}}$ , in  $\Omega$ , is the resistance of the external resistor connected to R-EXT terminal.

The magnitude of current is around 50mA at 360 $\Omega$  and 25mA at 720 $\Omega$ .

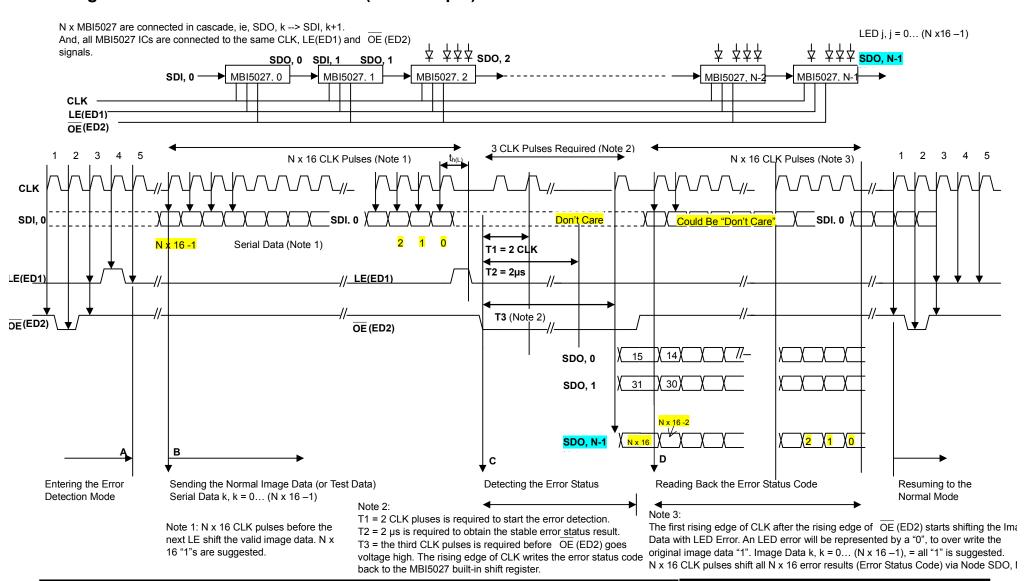

### **Entering Error Detection Mode**

Each time the system controller sends the sequence patterns shown above, MBI5027 can enter the Error Detection mode. During this phase, the system controller can still send data through SDI pin.

The state of  $\overline{OE}$  (ED2) and LE(ED1) is sampled by the rising edge of each CLK. We use "0" and "1" to represent the state of "Voltage Low" and "Voltage High" respectively. The states of the successive five  $\overline{OE}$  (ED2) and LE(ED1) are (1, 0), (0, 0), (1, 0), (1, 1) and (1, 0).

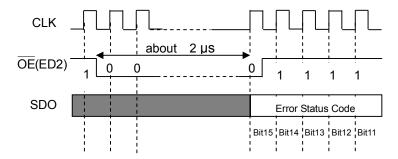

### **Reading Error Status Code**

Once entering the Error Detection mode, the Error Detection takes place by changing the state of  $\overline{OE}$  (ED2) from "Voltage High" to "Voltage Low". The built-in current detection circuit will detect the effective current  $I_{OUT, \text{ effective}}$  of each output channel, and compare it to the target current  $I_{OUT, \text{ target}}$ , defined by  $R_{\text{ext}}$ . If the  $I_{OUT, \text{ effective}}$ , is much less than the target current  $I_{OUT, \text{ target}}$ , an error status code will be represented as "0" state. During the period of detecting errors, data cannot be sent into MBI5027 through SDI pin. The "Voltage Low" state of  $\overline{OE}$  (ED2) requires at least three "0" of which the last "0" should be at least 2µs after the falling edge of  $\overline{OE}$  (ED2). The occurrence of the last "0" results in the event that MBI5027 saves the error status in the built-in register. The mentioned state of each "0" is sampled by the rising edge of each CLK. Before the error status saved in the built-in register is read, the state of  $\overline{OE}$  (ED2) should be pulled up from "Voltage Low" to "Voltage High". Then, by sending CLK, MBI5027 shifts out, through SDO pin, the error status bit by bit.

### **Resuming to Normal Mode**

Each time the system controller sends the sequence patterns shown above, MBI5027 can resume to the Normal mode. During this phase, the system controller can still send data through SDI pin.

The state of OE (ED2) and LE(ED1) is sampled by the rising edge of each CLK. We use "0" and "1" to represent the state of "Voltage Low" and "Voltage High" respectively. The states of the successive five  $\overline{OE}$  (ED2) and LE(ED1) are (1, 0), (0, 0), (1, 0), (1, 0) and (1, 0).

### **Timing Chart for Error Detection Mode (An Example)**

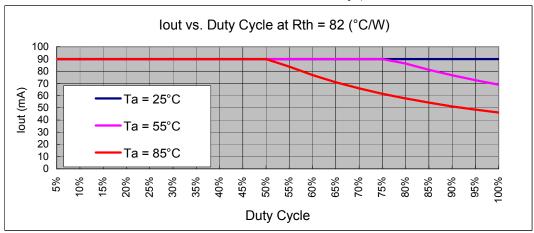

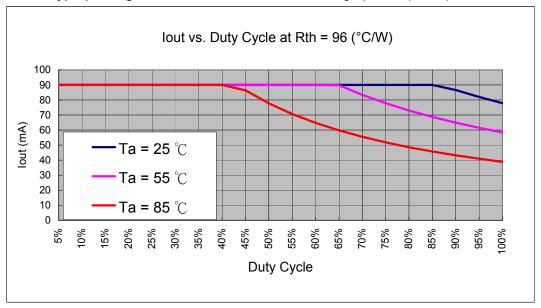

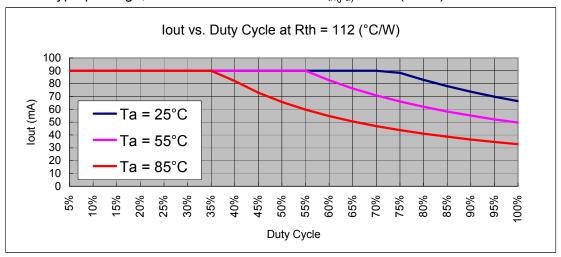

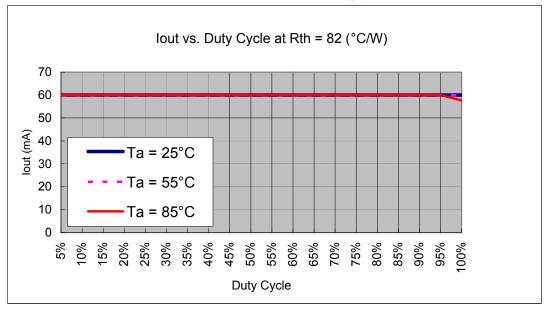

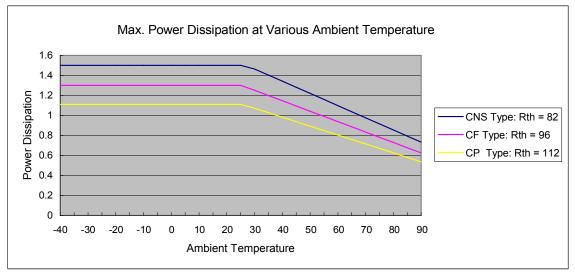

### Package Power Dissipation (P<sub>D</sub>)

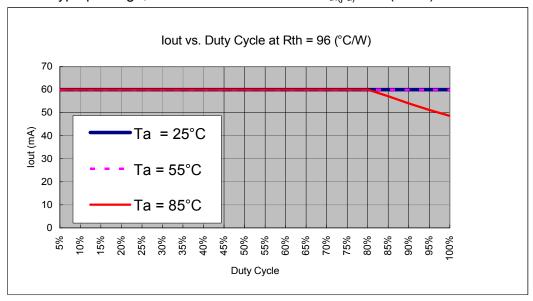

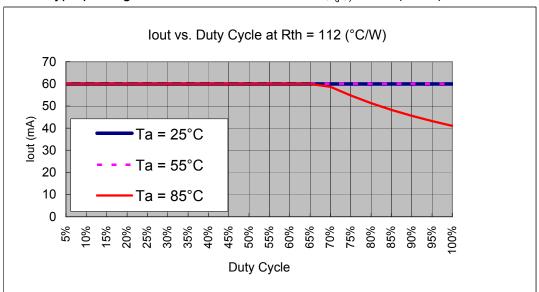

The maximum allowable package power dissipation is determined as  $P_D(max) = (Tj - Ta) / R_{th(j-a)}$ . When 16 output channels are turned on simultaneously, the actual package power dissipation is  $P_D(act) = (I_{DD} \times V_{DD}) + (I_{OUT} \times Duty \times V_{DS} \times 16)$ . Therefore, to keep  $P_D(act) \le P_D(max)$ , the allowable maximum output current as a function of duty cycle is:

$$I_{OUT} = \{ [ (Tj - Ta) / R_{th(j-a)} ] - (I_{DD} \times V_{DD}) \} / V_{DS} / Duty / 16,$$

where Tj = 150°C.

### (A) $I_{out} = 90 \text{mA}$ , $V_{DS} = 1.0 \text{V}$ , 16 output channels active

For CNS type package, the thermal resistance is  $R_{th(j-a)}$  = 82 (°C/W)

For CF type package, the thermal resistance is Rth(j-a) = 96 (°C/W)

For CP type package, the thermal resistance is  $R_{th(j-a)} = 112$  (°C/W)

## (B) $I_{out}$ = 60mA, $V_{DS}$ = 0.8V, 16 output channels active

For CNS type package, the thermal resistance is  $R_{th(j-a)} = 82$  (°C/W)

For CF type package, the thermal resistance is R<sub>th(j-a)</sub>= 96 (°C/W)

For CP type package, the thermal resistance is  $R_{th(j-a)}$  = 112 (°C/W)

The maximum power dissipation,  $P_D(max) = (Tj-Ta) / R_{th(j-a)}$ , decreases as the ambient temperature increases.

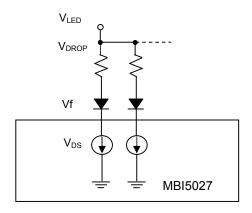

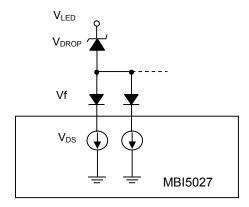

### Load Supply Voltage (V<sub>LED</sub>)

MBI5027 are designed to operate with  $V_{DS}$  ranging from 0.4V to 1.0V considering the package power dissipating limits.  $V_{DS}$  may be higher enough to make  $P_{D(act)} > P_{D(max)}$  when  $V_{LED} = 5V$  and  $V_{DS} = V_{LED} - Vf$ , in which  $V_{LED}$  is the load supply voltage. In this case, it is recommended to use the lowest possible supply voltage or to set an external voltage reducer,  $V_{DROP}$ .

A voltage reducer lets  $V_{DS} = (V_{LED} - Vf) - V_{DROP}$ .

Resistors or Zener diode can be used in the applications as the following figures.

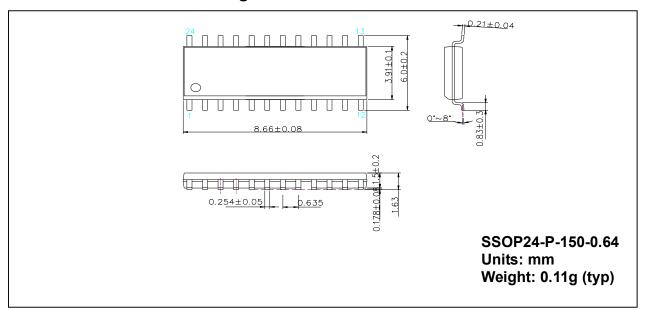

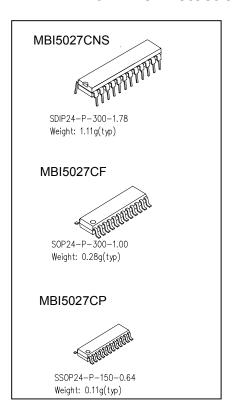

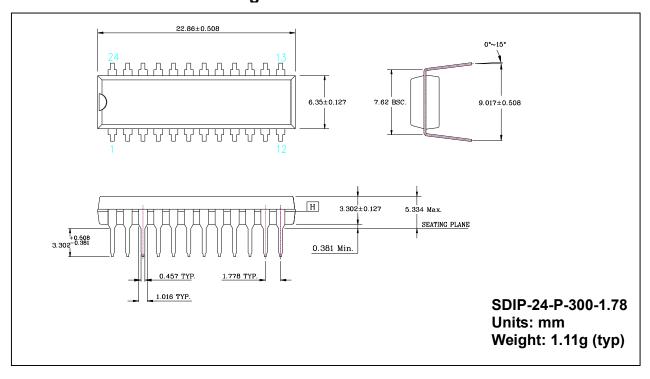

# **Package Outlines**MBI5027CNS Outline Drawing

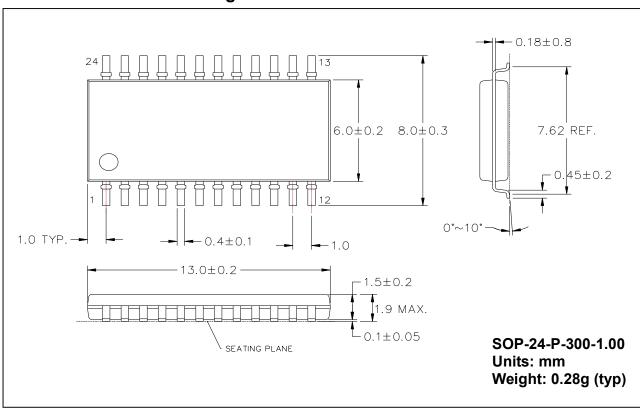

### **MBI5027CF Outline Drawing**

# **MBI5027CP Outline Drawing**