#### **Product Preview**

MC13180PP/D Rev. 2, 08/2002

2.4 GHz Low Power Wireless Transceiver IC for Bluetooth™ Applications

# MC13180

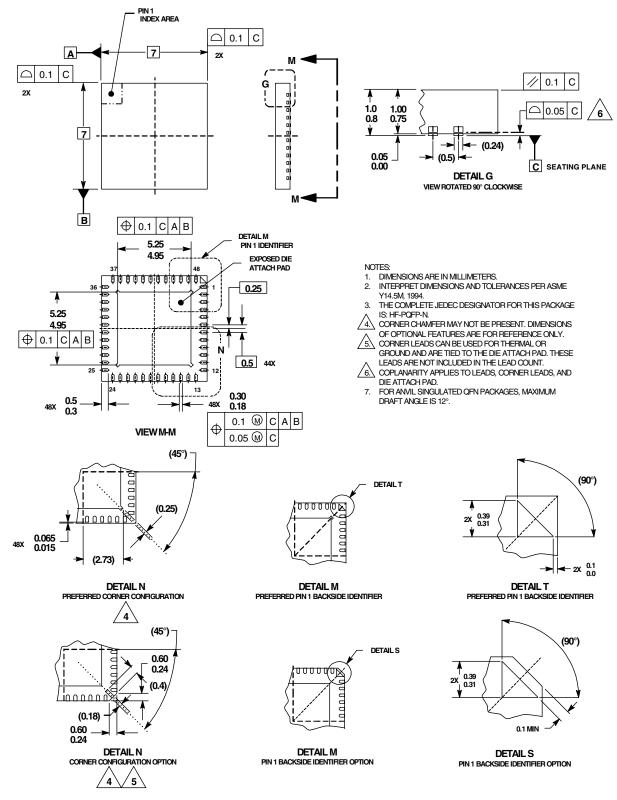

# Package Information Plastic Package Case 1314 (QFN-48)

#### **Ordering Information**

| Device    | Marking   | Package |

|-----------|-----------|---------|

| PC13180FC | PC13180FC | QFN-48  |

The MC13180 2.4 GHz Low Power Wireless Transceiver for Bluetooth<sup>TM</sup> is a part of the comprehensive Bluetooth platform from Motorola that provides a complete, low-power Bluetooth Radio System for Bluetooth Class 1 or 2 power systems. The design is based on Motorola's third-generation Bluetooth architecture that has set the industry standard for interoperability, complete functionality, and compliance with the Bluetooth specification. When combined with a specified Motorola baseband controller such as the MC71000 or MC9328MX1, a complete Bluetooth solution can be realized.

The MC13180 provides a unique combination of sensitivity, excellent C/I performance, and low power consumption. These performance parameters are extremely important to maintaining a robust link in high RF interference environments such as mobile phones, high density Bluetooth networks, 802.11b networks, microwave ovens, etc.

- Power Supply Range: 2.5 to 3.1 V

- Low Current Drain in Transmit (27 mA Peak) or Receive (37 mA Peak) Mode

- Minimum External Components

- Low IF Receiver with On-Chip Filters

- Fully Integrated Demodulator with A/D

- Direct Launch Transmitter

- Multi-Accumulator, Dual-Port, Fractional-N Synthesizer

- RSSI with A/D

- Bluetooth Class I Compatible

- Crystal Independent (12 to 15 MHz) Reference Oscillator or 12 to 26 MHz if supplied externally

This document contains information on a product under development. Motorola reserves the right to change or discontinue this product without notice. © Motorola, Inc., 2002. All rights reserved.

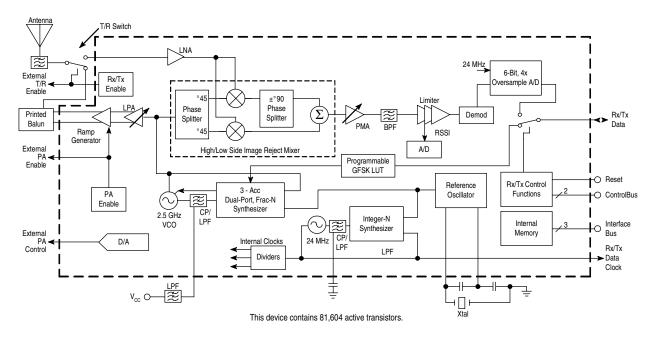

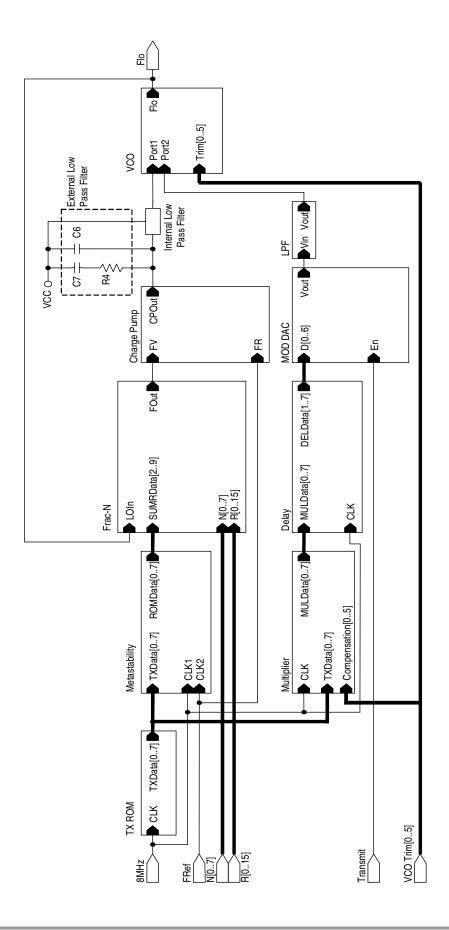

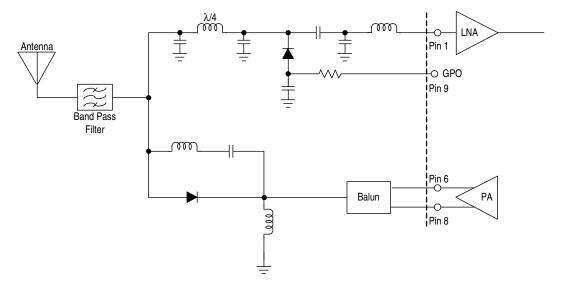

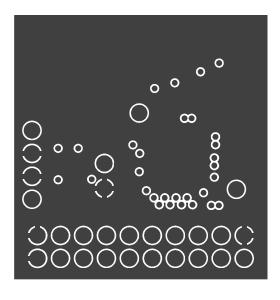

Figure 1. Simplified Block Diagram

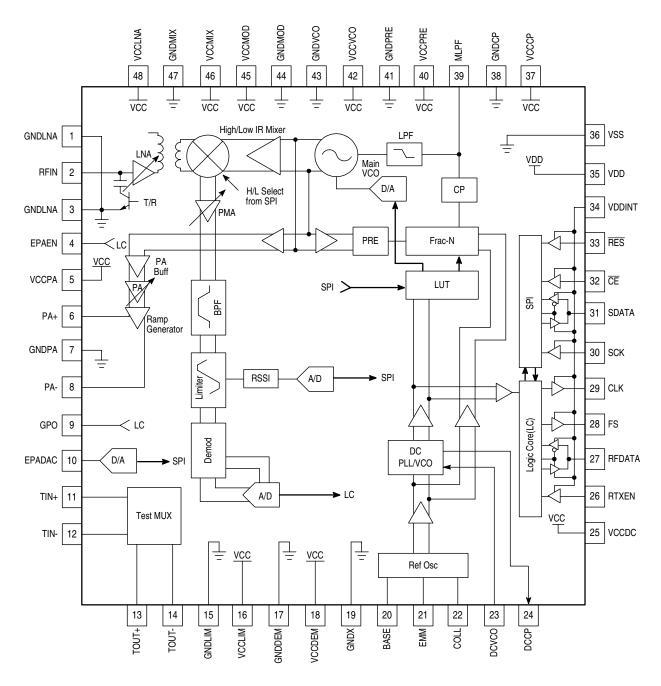

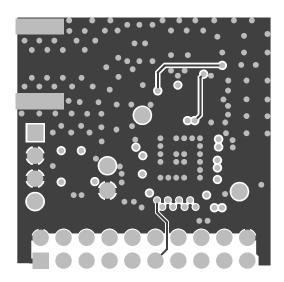

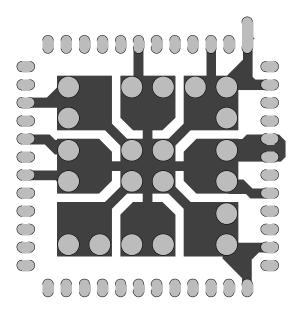

Figure 2. Device Pinout

# 1 Electrical Characteristics

**Table 1. Maximum Ratings**

| Ratings                                              | Symbol           | Value      | Unit |

|------------------------------------------------------|------------------|------------|------|

| Supply Voltage V <sub>CC</sub> RF V <sub>DDINT</sub> |                  | 3.2<br>3.2 | V    |

| Junction Temperature                                 | TJ               | 150        | °C   |

| Storage Temperature Range                            | T <sub>stg</sub> | -60 to 150 | °C   |

NOTES: 1. Maximum Ratings are those values beyond which damage to the device may occur. Functional operation should be restricted to the limits in the Recommended Operating Conditions and Electrical Characteristics tables.

**Table 2. Recommended Operating Conditions**

| Characteristic                                                                                       | Symbol             | Min      | Тур     | Max                | Unit |

|------------------------------------------------------------------------------------------------------|--------------------|----------|---------|--------------------|------|

| Power Supply Voltage                                                                                 | V <sub>CC</sub> RF | 2.5      | 2.7     | 3.1                | Vdc  |

| Power Supply Voltage, Logic Interface ( $V_{DDINT} \le V_{CC}RF$ )                                   | $V_{DDINT}$        | 1.65     | -       | V <sub>CC</sub> RF | Vdc  |

| Input Frequency                                                                                      | f <sub>in</sub>    | 2.4      | -       | 2.5                | GHz  |

| Ambient Temperature Range                                                                            | T <sub>A</sub>     | -20      | 25      | 85                 | °C   |

| Ref Osc Frequency Range (only integral multiples of 20 kHz may be used) With Crystal External Source | f <sub>ref</sub>   | 12<br>12 | 13<br>- | 15<br>26           | MHz  |

### Table 3. Digital DC Electrical Specifications

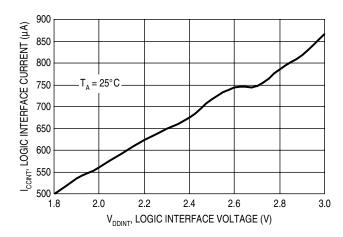

$(V_{CC}RF = 2.7 \text{ Vdc}, V_{DDINT} = 1.8 \text{ Vdc}, TA = 25^{\circ}C$ , Reference Crystal = 13 MHz, Register bit settings according to specified defaults in Figure 4, unless otherwise noted. See Figure 3 Test Circuit.)

| Characteristic                                                                                                                                                                                                                                                | Symbol                 | Min    | Тур        | Max        | Unit     |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|--------|------------|------------|----------|

| Supply Current $\overline{\text{CE}}$ , SDATA, SCK, RFDATA, RTXEN, $V_{\text{in}} = 0 \text{ V or } 1.8 \text{ V}$ $\overline{\text{RES}}$ , $V_{\text{in}} = 0 \text{ V (Reset Mode)}$ $\overline{\text{RES}}$ , $V_{\text{in}} = 1.8 \text{ V (Idle Mode)}$ | I <sub>CCINT</sub>     | -<br>- | 0.2<br>0.5 | 2.0<br>3.0 | μA<br>mA |

| Radio Power Supply Current, Sleep Mode                                                                                                                                                                                                                        | I <sub>CCRFsleep</sub> | -      | 2.0        | 10         | μΑ       |

| Radio Power Supply Current, Idle Mode                                                                                                                                                                                                                         | I <sub>CCRFidle</sub>  | -      | 3.4        | 4.0        | mA       |

<sup>2.</sup> Meets Human Body Model (HBM) ≤2.0 kV and Machine Model (MM) ≤200 V except RF & I/O Pins = 50 V MM, RF Pins = 100 V HBM, and I/O Pins <500 V. RF pins have no ESD protection. Additional ESD data available upon request.

$\textbf{Table 3. Digital DC Electrical Specifications (Continued)} \\ (V_{CC}RF = 2.7 \ \text{Vdc}, \ V_{DDINT} = 1.8 \ \text{Vdc}, \ TA = 25^{\circ}\text{C}, \ \text{Reference Crystal} = 13 \ \text{MHz}, \ \text{Register bit settings according to specified defaults in Figure 4, unless otherwise noted. See Figure 3 Test Circuit.)}$

| Characteristic                                                                                     | Symbol                                       | Min                              | Тур                  | Max                              | Unit    |

|----------------------------------------------------------------------------------------------------|----------------------------------------------|----------------------------------|----------------------|----------------------------------|---------|

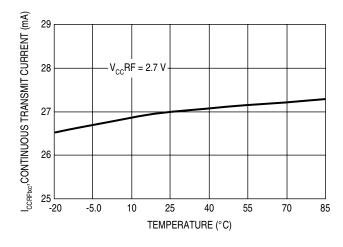

| Radio Power Supply Current Transmit, 1 Slot Transmit, 3 Slot Transmit, 5 Slot Transmit, Continuous | ICCRFtx1<br>ICCRFtx3<br>ICCRFtx5<br>ICCRFtxc | -<br>-<br>-                      | 22<br>25<br>26<br>27 | -<br>-<br>-<br>33                | mA      |

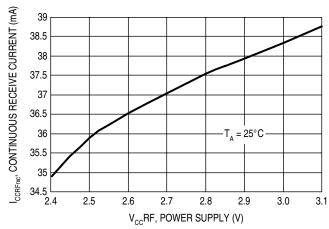

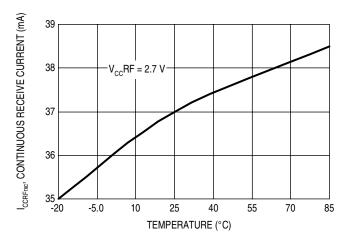

| Radio Power Supply Current Receive, 1 Slot Receive, 3 Slot Receive, 5 Slot Receive, Continuous     | ICCRFrx1<br>ICCRFrx3<br>ICCRFrx5<br>ICCRFrxc |                                  | 30<br>34<br>35<br>37 | -<br>-<br>-<br>47.5              | mA      |

| Output Voltage Low<br>SDATA, CLK, FS, RFDATA<br>ILoad = 0 μA<br>ILoad = 100 μA                     | V <sub>OL</sub>                              | -                                | 20<br>-              | -<br>0.2 x<br>V <sub>DDINT</sub> | mV<br>V |

| Output Voltage High<br>SDATA, CLK, FS, RFDATA<br>ILoad = 0 μA<br>ILoad = 100 μA                    | V <sub>OH</sub>                              | -<br>0.8 x<br>V <sub>DDINT</sub> | 1.78<br>-            |                                  | V       |

| Output Voltage Low<br>EPAEN, GPO<br>ILoad = 0 μA<br>ILoad = 100 μA                                 | V <sub>OL</sub>                              | -                                | 20<br>-              | -<br>0.2 x<br>V <sub>CC</sub> RF | mV<br>V |

| Output Voltage High EPAEN, GPO ILoad = 0 μA ILoad = 100 μA                                         | V <sub>OH</sub>                              | -<br>0.8 x<br>V <sub>CC</sub> RF | 2.68                 | -                                | V       |

| Input Voltage Low RES, CE, SDATA, SCK, RFDATA, RTXEN                                               | V <sub>IL</sub>                              | -                                | 0                    | 0.3 x<br>V <sub>DDINT</sub>      | V       |

| Input Voltage High RES, CE, SDATA, SCK, RFDATA, RTXEN                                              | V <sub>IH</sub>                              | 0.7 x<br>V <sub>DDINT</sub>      | V <sub>DDINT</sub>   | -                                | V       |

| Input Current RES, CE, SDATA, SCK, RFDATA, RTXEN, Vin = 0 V or 1.8 V                               | I <sub>in</sub>                              | -                                | ±1.0                 | -                                | μА      |

#### **Electrical Characteristics**

#### Table 4. EPA DAC Electrical Specifications

$(V_{CC}RF = 3.1 \text{ Vdc}, V_{DDINT} = 1.8 \text{ Vdc}, T_A = 25^{\circ}C$ , Reference Crystal = 13 MHz, Register bit settings according to specified defaults in Figure 4 except R11/7 = 1, unless otherwise noted.)

| Characteristic                                                                      | Symbol             | Min           | Тур                  | Max           | Unit |

|-------------------------------------------------------------------------------------|--------------------|---------------|----------------------|---------------|------|

| Output Voltage EPADAC, ILoad = ±100 μA PADAC = 000000 PADAC = 100000 PADAC = 111111 | V <sub>out</sub>   | -<br>-<br>2.5 | 0.02<br>1.60<br>3.08 | 0.4<br>-<br>- | >    |

| Resolution                                                                          | RESOL              | -             | 6                    | -             | Bits |

| Linearity                                                                           | INL/DNL            | -             | ±1.0                 | ±2.0          | LSB  |

| Average Supply Current (1-slot packet)                                              | I <sub>CCDAC</sub> | -             | 197                  | 500           | μΑ   |

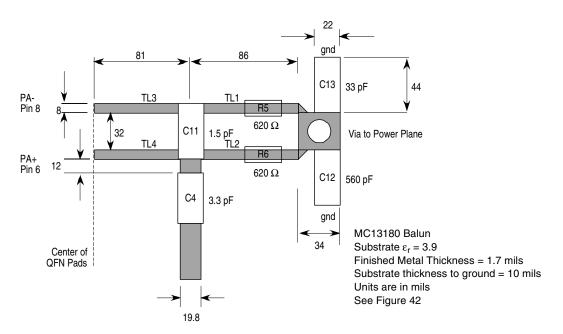

#### Table 5. Digital AC Electrical Specifications

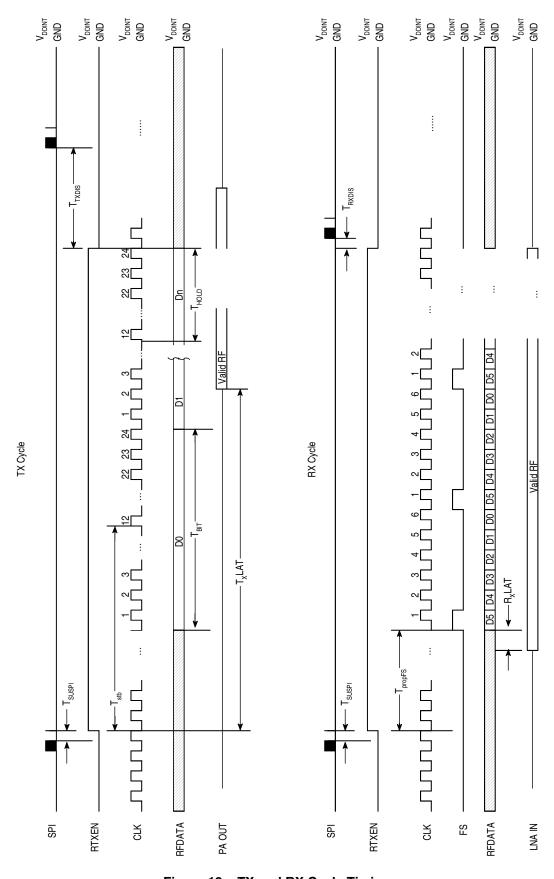

$(V_{CC}RF = 2.7 \text{ Vdc}, V_{DDINT} = 1.8 \text{ Vdc}, T_A = 25^{\circ}\text{C}, \text{ Reference Crystal} = 13 \text{ MHz}, \text{ Register bit settings according to specified defaults in Figure 4, unless otherwise noted. See Figure 3 Test Circuit and Figure 12 Timing Diagram.)}$

| Characteristic                                                 | Symbol              | Min | Тур             | Max | Unit |

|----------------------------------------------------------------|---------------------|-----|-----------------|-----|------|

| Propagation Delay, RTXEN to FS, receive mode                   | T <sub>propFS</sub> | -   | 168             | -   | μs   |

| Receiver Latency, LNA In to RFDATA, receive mode               | R <sub>X</sub> LAT  | -   | 1.0             | -   | μs   |

| Receive Disable Time                                           | T <sub>RXDIS</sub>  | -   | 0               | -   | μs   |

| Strobe Delay, RTXEN to RFDATA, transmit mode                   | T <sub>stb</sub>    | -   | TXsync<br>+ 0.5 | -   | μs   |

| Transmit Sync Delay (i.e., R8/15-8)                            | TXsync              | 182 | 184             | 192 | μs   |

| Hold Time, RTXEN to RFDATA, transmit mode                      | T <sub>hold</sub>   | -   | 4.0             | -   | μs   |

| Transmit Latency, RTXEN to PAout, transmit mode                | T <sub>X</sub> LAT  | -   | TXsync<br>+ 2.5 | -   | μs   |

| Transmit Data Rate, Bit transfer rate to RFDATA, transmit mode | T <sub>Bit</sub>    | -   | 1.0             | -   | μs   |

| Transmit Disable Time                                          | T <sub>TXDIS</sub>  | -   | 20              | -   | μs   |

| CLK Duty Cycle                                                 |                     | 30  | 40/60           | 70  | %    |

#### Table 6. Receiver AC Electrical Specifications

$(V_{CC}RF=2.7\ Vdc,\ V_{DDINT}=1.8\ Vdc,\ Desired\ RF_{in}=2.441\ GHz\ @\ f_{dev}=157.5\ kHz,\ Interferer\ f_{dev}=160\ kHz,\ Modulation=GFSK,\ BT=0.5,\ Bit\ Rate=1.0\ Mbps,\ Modulating\ data\ for\ desired\ signal=PRBS9,\ Modulating\ data\ for\ interfering\ signal=PRBS15,\ Measured\ BER<0.1\%,\ Reference\ Crystal=13\ MHz,\ Register\ bit\ settings\ according\ to\ Figure\ 4,\ T_A=25°C,\ unless\ otherwise\ noted.\ Measurements\ made\ from\ LNA_{in}\ to\ Recovered\ Data\ out.\ See\ Figure\ 3\ Test\ Circuit.)$

| Characteristics                                                                                                                                                                            | Symbol              | Min                      | Тур                       | Max         | Bluetooth<br>Specs               | Unit |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|--------------------------|---------------------------|-------------|----------------------------------|------|

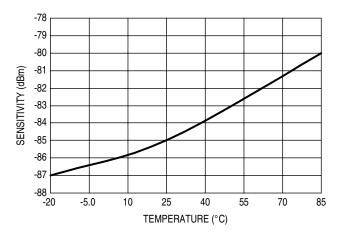

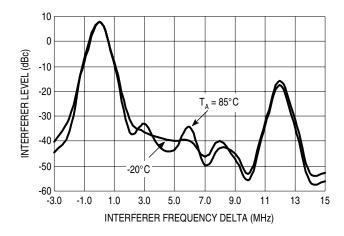

| Receiver Sensitivity  T <sub>A</sub> = 25°C  T <sub>A</sub> = -20 to 85°C                                                                                                                  | SENS <sub>min</sub> |                          | -85<br>-80                | -75         | ≤ -70                            | dBm  |

| Receiver Sensitivity degradation in the presence of a dirty transmitter                                                                                                                    |                     | -                        | -1.5                      | -           |                                  | dB   |

| Maximum Usable Signal Level                                                                                                                                                                | SENS <sub>max</sub> | -20                      | > 0                       | -           | ≥ -20                            | dBm  |

| Co-Channel Interference @ -60 dBm                                                                                                                                                          | C/I co              | -                        | 8.0                       | 11          | ≤ 11                             | dB   |

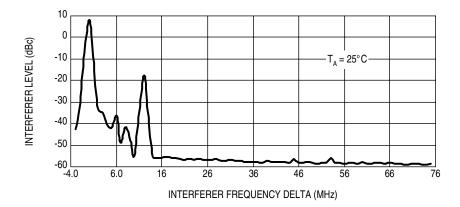

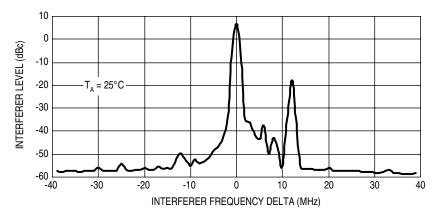

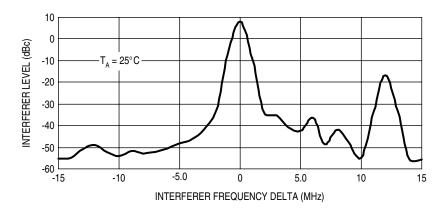

| Adjacent Channel Interference Adjacent (±1 MHz) Interference @ -60 dBm                                                                                                                     | C/I 1MHz            | -                        | -8.0                      | 0           | ≤ 0                              | dB   |

| Adjacent (±2 MHz) Interference @ -60 dBm                                                                                                                                                   | C/I 2MHz            | -                        | -33                       | -30         | ≤ -30                            |      |

| Adjacent (≥3 MHz) Interference<br>@ -67 dBm                                                                                                                                                | C/I ≥3MHz           | -                        | -46                       | -40         | ≤ -40                            |      |

| Image Frequency Interference<br>@ -67 dBm                                                                                                                                                  | C/I image           | -                        | -17                       | -9.0        | ≤ -9.0                           | dB   |

| Adjacent Interference to In-Band Image Frequency @ -67 dBm                                                                                                                                 | C/I image<br>±1     | -                        | -33                       | -20         | ≤ -20                            | dB   |

| Spurious Response Frequencies                                                                                                                                                              |                     | -                        | 2                         | 5           | 5                                |      |

| Intermodulation Performance [Note 1]                                                                                                                                                       |                     | -39                      | -31                       | -           | ≥ -39                            | dBm  |

| Receiver Spurious Emissions<br>30 MHz to 1.0 GHz<br>1.0 GHz to 12.75 GHz                                                                                                                   |                     |                          | -70<br>-56                | -57<br>-47  | ≤ -57<br>≤ -47                   | dBm  |

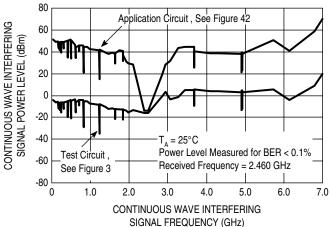

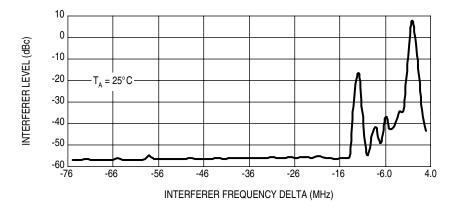

| Receiver Blocking Performance (See<br>Figure 29) [Note 2]<br>30 MHz to 2.0 GHz (1.999 GHz)<br>2.0 to 2.399 GHz (2.399 GHz)<br>2.498 to 3.0 GHz (2.498 GHz)<br>3.0 to 12.75 GHz (3.001 GHz) |                     | -25<br>-27<br>-27<br>-10 | -9.0<br>-16<br>-16<br>2.0 | -<br>-<br>- | ≥ -10<br>≥ -27<br>≥ -27<br>≥ -10 | dBm  |

**NOTE:** 1. Measured at  $f_2$  -  $f_1$  = 5.0 MHz in accordance to Bluetooth specification.

<sup>2.</sup> As allowed by the Bluetooth Specification, up to 5 exceptions may be taken for spurious response.

#### **Electrical Characteristics**

#### Table 6. Receiver AC Electrical Specifications (Continued)

$(V_{CC}RF = 2.7 \text{ Vdc}, V_{DDINT} = 1.8 \text{ Vdc}, Desired RF_{in} = 2.441 \text{ GHz} @ f_{dev} = 157.5 \text{ kHz}, Interferer f_{dev} = 160 \text{ kHz}, Modulation = GFSK, BT = 0.5, Bit Rate = 1.0 Mbps, Modulating data for desired signal = PRBS9, Modulating data for interfering signal = PRBS15, Measured BER < 0.1%, Reference Crystal = 13 MHz, Register bit settings according to Figure 4, <math>T_A = 25^{\circ}\text{C}$ , unless otherwise noted. Measurements made from LNA<sub>in</sub> to Recovered Data out. See Figure 3 Test Circuit.)

| Characteristics                                                                                              | Symbol              | Min | Тур        | Max        | Bluetooth<br>Specs | Unit   |

|--------------------------------------------------------------------------------------------------------------|---------------------|-----|------------|------------|--------------------|--------|

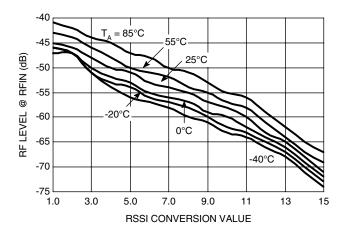

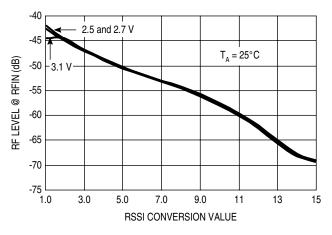

| RSSI Conversion Value, (R4/6 and R9/8 = 1) RF level at LNA input to maintain conversion value of:  1000 1111 | RSSI                | -60 | -56<br>-70 | -52<br>-66 |                    | dBm    |

| 1111                                                                                                         |                     | -   | -70        | -00        |                    |        |

| RSSI Resolution (R4/6 and R9/8 = 1)                                                                          | RSSI <sub>res</sub> | -   | 1.8        | 1          |                    | dB/bit |

| RSSI Dynamic Range                                                                                           |                     | 20  | -          | -          |                    | dB     |

| RSSI Average Supply Current (R4/6 and R9/8 = 1)                                                              |                     | -   | 40         | -          |                    | μА     |

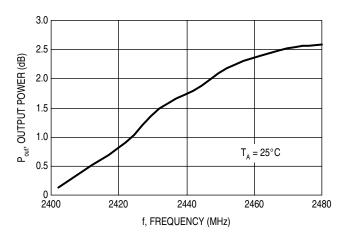

#### **Table 7. Transmitter AC Electrical Specifications**

$(V_{CC}RF = 2.7 \text{ Vdc}, V_{DDINT} = 1.8 \text{ Vdc}, \text{Modulation} = \text{GFSK}, \text{BT} = 0.5, \text{Bit Rate} = 1.0 \text{ Mbps}, \text{Reference Crystal} = 13 \text{ MHz}, \text{Register bit settings according to Figure 4, } T_A = -20 \text{ to } 85^{\circ}\text{C}, \text{ unless otherwise noted.}$  Measurements made at PA<sub>out</sub>. See Figure 3 Test Circuit.)

| Characteristics                                | Symbol           | Min  | Тур   | Max  | Bluetooth<br>Specs | Unit |

|------------------------------------------------|------------------|------|-------|------|--------------------|------|

| RF Transmit Output Power                       | P <sub>out</sub> |      |       |      |                    | dBm  |

| T <sub>A</sub> = 25°C                          | Out              | -3.5 | 1.9   | 4.0  | -6.0 to 4.0        |      |

| $T_A = 85^{\circ}C$                            |                  | -3.5 | 0.1   | 4.0  | -6.0 to 4.0        |      |

| $T_A = -20^{\circ}C$                           |                  | -3.5 | 2.4   | 4.0  | -6.0 to 4.0        |      |

| -20 dBc Occupied Bandwidth                     | OccBW            | -    | 930   | 1000 | ≤1000              | kHz  |

| In-Band Spurious Emissions                     |                  |      |       |      |                    | dBm  |

| Adjacent Channel ±2.0 MHz Offset               | lnb2             | -    | -59   | -20  | ≤ -20              |      |

| Adjacent Channel ±3.0 MHz Offset               | Inb3             | -    | -65   | -40  | ≤ -40              |      |

| Adjacent Channel ≥3.0 MHz Offset               | Inbg3            | -    | -70   | -40  | ≤ -40              |      |

| In Band Spurious Emission Exceptions           | Inbex            | -    | 0     | 3    | ≤ 3                |      |

| Out of Band Spurious Emissions                 |                  |      |       |      |                    | dBm  |

| 30 MHz to 1.0 GHz                              | Outb1            | -    | -57   | -36  | ≤ -36              |      |

| 1.0 to 12.75 GHz (2nd Harmonic)                | Outb2            | -    | -19   | -5.0 | ≤ -30              |      |

| 1.8 to 1.9 GHz                                 | Outb3            | -    | -58   | -47  | ≤ -47              |      |

| 5.15 to 5.3 GHz                                | Outb4            | -    | -56   | -47  | ≤ -47              |      |

| Peak Frequency Deviation                       | Dev              | 140  | 157.5 | 175  | 140 to 175         | kHz  |

| Minimum Frequency Deviation                    | DevMin           | 11.5 | 148   | -    | 115                | kHz  |

| High vs Low Frequency Modulation<br>Percentage | ModIn            | 80   | 93    | -    | ≥ 80               | %    |

| Initial Frequency Accuracy                     | InitFA           | -75  | ±5.0  | -75  | ±75                | kHz  |

#### Table 7. Transmitter AC Electrical Specifications (Continued)

$(V_{CC}RF = 2.7 \text{ Vdc}, V_{DDINT} = 1.8 \text{ Vdc}, \text{Modulation} = \text{GFSK}, \text{BT} = 0.5, \text{Bit Rate} = 1.0 \text{ Mbps}, \text{Reference Crystal} = 13 \text{ MHz}, \text{Register bit settings according to Figure 4, } T_A = -20 \text{ to } 85^{\circ}\text{C}, \text{ unless otherwise noted.}$  Measurements made at PA<sub>out</sub>. See Figure 3 Test Circuit.)

| Characteristics                                                                       | Symbol         | Min               | Тур                  | Max            | Bluetooth<br>Specs | Unit          |

|---------------------------------------------------------------------------------------|----------------|-------------------|----------------------|----------------|--------------------|---------------|

| Transmitter Center Frequency Drift One-slot packet Three-slot packet Five-slot packet | d1<br>d3<br>d5 | -25<br>-40<br>-40 | ±3.0<br>±6.0<br>±6.0 | 25<br>40<br>40 | ±25<br>±40<br>±40  | kHz           |

| Maximum Frequency Drift                                                               | Dmax           | -                 | 3.0                  | 20             | 20                 | kHz/<br>50 μs |

| PA Output Impedance                                                                   | S22            | 9                 | See Table 2          |                | dB                 |               |

#### Table 8. Receiver AC Electrical Specifications

$(V_{CC}RF = 2.7 \text{ Vdc}, V_{DDINT} = 1.8 \text{ Vdc}, \text{Modulation} = \text{GFSK}, \text{BT} = 0.5, \text{Bit Rate} = 1.0 \text{ Mbps}, \text{Reference Crystal} = 13 \text{ MHz}, \text{Register bit settings according to Figure 4}, T_A = -20 \text{ to } 85^{\circ}\text{C}, \text{ unless otherwise noted}.$  Measurements made at PA<sub>out</sub>. See Figure 3 Test Circuit.)

| Characteristic                                                                                                                                                          | Symbol                            | Min         | Тур                | Max         | Unit |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|-------------|--------------------|-------------|------|

| Maximum Usable Signal Level, T <sub>A</sub> = -20 to 85°C                                                                                                               | SENSmax                           | -           | ≥ 0                | -           | dBm  |

| Receiver Blocking Performance, T <sub>A</sub> = 25°C<br>W-CDMA 1.8 GHz<br>W-CDMA 2.2 GHz<br>GSM 1.8 GHz                                                                 |                                   |             | -14<br>-13<br>-13  |             | dBm  |

| Co-Channel Interference @ -60 dBm, T <sub>A</sub> = -20 to 85°C                                                                                                         | C/I co                            | -           | 8.0                | -           | dB   |

| Adjacent Interference, T <sub>A</sub> = 25°C Adjacent (±1 MHz) Interference @ -70 dBm Adjacent (±2 MHz) Interference @ -70 dBm Adjacent (≥3 MHz) Interference @ -77 dBm | C/I 1MHz<br>C/I 2MHz<br>C/I ≥3MHz | -<br>-<br>- | -8.0<br>-41<br>-47 | -<br>-<br>- | dB   |

| Image Frequency Interference @ -77 dBm, T <sub>A</sub> = 25°C                                                                                                           | C/I image                         | -           | -17                | -           | dB   |

| Adjacent Interference to In-Band Image Frequency<br>@ -77 dBm, T <sub>A</sub> = 25°C                                                                                    | C/I image<br>±1                   | -           | -33                | -           | dB   |

| LNA Input Impedance                                                                                                                                                     | S11                               | See         | Tables 20 a        | nd 21       | dB   |

#### **Electrical Characteristics**

#### Table 9. MC7100/MC13180 Receive Characteristics

$(V_{CC}RF = 2.7 \text{ Vdc}, V_{DDINT} = 1.8 \text{ Vdc}, \text{Reference Crystal} = 13 \text{ MHz}, \text{Register bit settings according to specified defaults, unless otherwise noted, interfering access code at the minimum Hamming distance of 14 according to Bluetooth specifications. See Figure 3 Test Circuit.)$

| Characteristic                                                                                                                     | Symbol | Min         | Тур           | Max         | Unit |

|------------------------------------------------------------------------------------------------------------------------------------|--------|-------------|---------------|-------------|------|

| False Detection Rate In Presence of Noise In Presence of Interfering Access Code @ Actual Sensitivity @ Actual Sensitivity + 10 dB |        | -<br>-<br>- | 0<br>0<br>0   | -<br>-<br>- | %    |

| Missed Detection Rate @ Actual Sensitivity @ Actual Sensitivity + 10 dB @ Actual Sensitivity - 16 dB                               |        | -<br>-<br>- | 0<br>0<br>100 | -<br>-<br>- | %    |

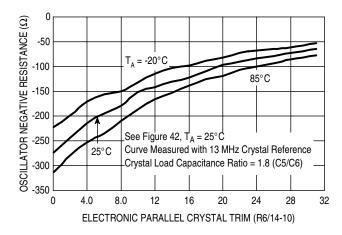

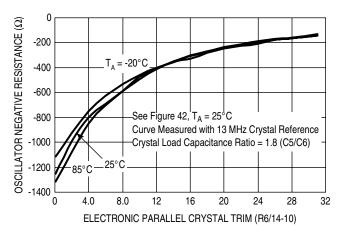

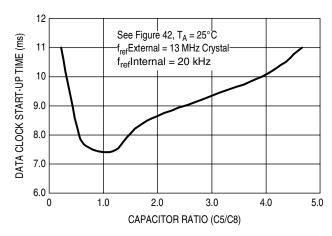

#### **Table 10. Reference Oscillator Receive Characteristics**

$(V_{CC}RF = 2.7 \text{ Vdc}, V_{DDINT} = 1.8 \text{ Vdc}, T_A = 25^{\circ}C$ , Reference Crystal = 13 MHz, Register bit settings according to specified defaults, unless otherwise noted. See Figure 3 Test Circuit.)

| Characteristic                                                                                                   | Symbol                   | Min         | Тур                       | Max         | Unit            |

|------------------------------------------------------------------------------------------------------------------|--------------------------|-------------|---------------------------|-------------|-----------------|

| Crystal Frequency Range (SeeTable 19 for supported frequencies)                                                  | f <sub>RefXtal</sub>     | 12          | -                         | 15          | MHz             |

| External Drive Frequency Range (See Table 19 for supported frequencies)                                          | f <sub>RefExternal</sub> | 12          | -                         | 26          | MHz             |

| Oscillator Drive Level External Reference Crystal Reference                                                      |                          | 0.2         | - 0.8                     | 1.0         | V <sub>pp</sub> |

| Crystal Load Capacitance (Resonant Parallel)                                                                     |                          | -           | 13                        | -           | pF              |

| Maximum Crystal Equivalent Series Resistance (ESR)                                                               |                          | -           | -                         | 100         | W               |

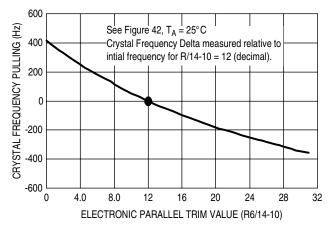

| Typical Crystal Adjustment Range                                                                                 |                          | -           | See Fig                   | gure 19     |                 |

| Recommended Crystal Tolerance over Temperature (-20 to 85°C)                                                     |                          | -           | ±10                       | -           | ppm             |

| Electronic Parallel Trim Capacitance Range                                                                       | C <sub>PT</sub>          | -           | 0 to 9.3                  | -           | pF              |

| Electronic Parallel Trim Capacitance Resolution                                                                  |                          | -           | 0.3                       | -           | pF              |

| Oscillator Bias Current<br>(R11/0) = 0, (R11/4) = 0 or 1<br>(R11/0) = 1, (R11/4) = 0<br>(R11/0) = 1, (R11/4) = 1 |                          | -<br>-<br>- | 0<br>50<br>200            | -<br>-<br>- | μА              |

| Input Impedance at Base (Reference Frequency = 12 to 26 MHz, R11/0 = 0 or 1) Parallel Capacitance                | C <sub>P</sub>           | -           | 1.0 +<br>Parallel<br>Trim | -           | pF              |

| Parallel Resistance                                                                                              | R <sub>P</sub>           | -           | Capacitance<br>20         | -           | kΩ              |

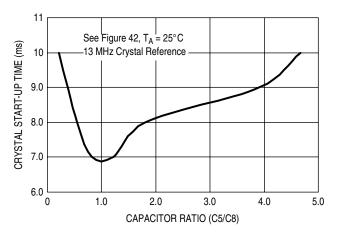

#### Table 10. Reference Oscillator Receive Characteristics (Continued)

$(V_{CC}RF = 2.7 \text{ Vdc}, V_{DDINT} = 1.8 \text{ Vdc}, T_A = 25^{\circ}\text{C}, \text{ Reference Crystal} = 13 \text{ MHz}, \text{ Register bit settings according to specified defaults, unless otherwise noted. See Figure 3 Test Circuit.)}$

| Characteristic                | Symbol            | Min | Тур | Max | Unit |

|-------------------------------|-------------------|-----|-----|-----|------|

| Input Bias Voltage (Base)     |                   | -   | 1.2 | -   | V    |

| Start-up Time (using Crystal) | T <sub>WAIT</sub> | -   | 7.5 | -   | ms   |

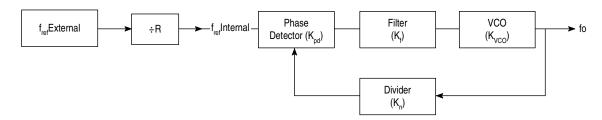

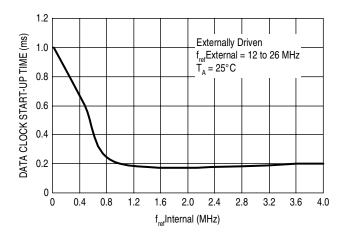

#### **Table 11. Data Clock Electrical Specifications**

$(V_{CC}RF = 2.7 \text{ Vdc}, V_{DDINT} = 1.8 \text{ Vdc}, T_A = 25^{\circ}\text{C}, \text{Reference Crystal} = 13 \text{ MHz}, \text{Register bit settings according to specified defaults, unless otherwise noted. See Figure 3 Test Circuit.)}$

| Characteristic                                     | Symbol           | Min    | Тур        | Max  | Unit            |

|----------------------------------------------------|------------------|--------|------------|------|-----------------|

| Internal Reference Frequency                       |                  | -      | 20         | 4000 | kHz             |

| Data Clock Output Frequency                        |                  | -      | 24         | -    | MHz             |

| R Counter (R6/9-0) (Base 10)                       |                  | 3      | 650        | 1023 |                 |

| N Counter (R7/10-0) (Base 10)                      |                  | 3      | 1200       | 2047 |                 |

| Loop Filter Bandwidth                              |                  | -      | 1.0        | 200  | kHz             |

| Phase Detector Gain Constant                       | K <sub>pd</sub>  | -      | 15.9       | -    | μ <b>A</b> /rad |

| VCO Gain Constant                                  | K <sub>VCO</sub> | -      | 15         | -    | MHz/V           |

| Start-up Time External Reference Crystal Reference |                  | -<br>- | 1.0<br>7.5 |      | ms              |

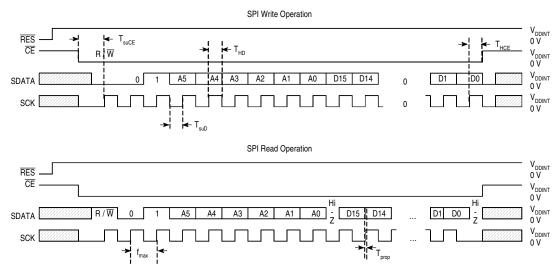

#### Table 12. SPI AC Electrical Specifications

$(V_{CC}RF = 2.7 \ Vdc, \ V_{DDINT} = 1.8 \ Vdc, \ T_A = 25^{\circ}C, \ unless \ otherwise \ noted.$  See Figure 13 Timing Diagram.)

| Characteristic                           | Symbol                                | Min | Тур      | Max | Unit |

|------------------------------------------|---------------------------------------|-----|----------|-----|------|

| CE to SCK Setup Time Hold Time           | T <sub>suCE</sub><br>T <sub>HCE</sub> | -   | 20<br>20 | -   | ns   |

| SDATA to SCK<br>Setup Time<br>Hold Time  | T <sub>suD</sub><br>T <sub>HD</sub>   |     | 20<br>20 |     | ns   |

| SCK to SDATA Propagation Delay           | T <sub>prop</sub>                     | -   | 20       | -   | ns   |

| SCK Operating Frequency (50% Duty Cycle) | f <sub>max</sub>                      | -   | -        | 20  | MHz  |

| SPI Setup Time to RTXEN (See Figure 12)  | T <sub>SUSPI</sub>                    | -   | 20       | -   | ns   |

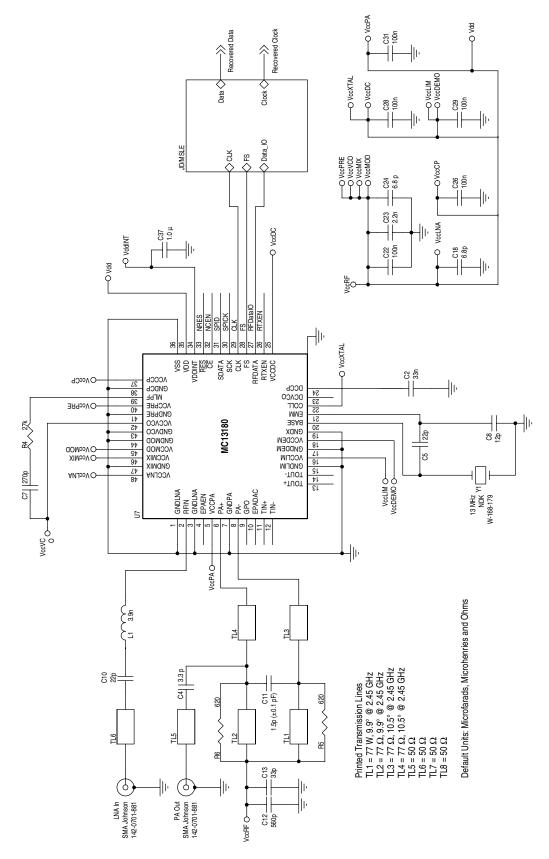

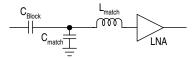

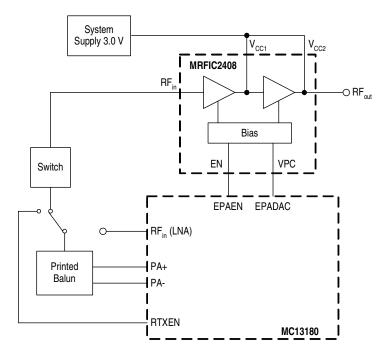

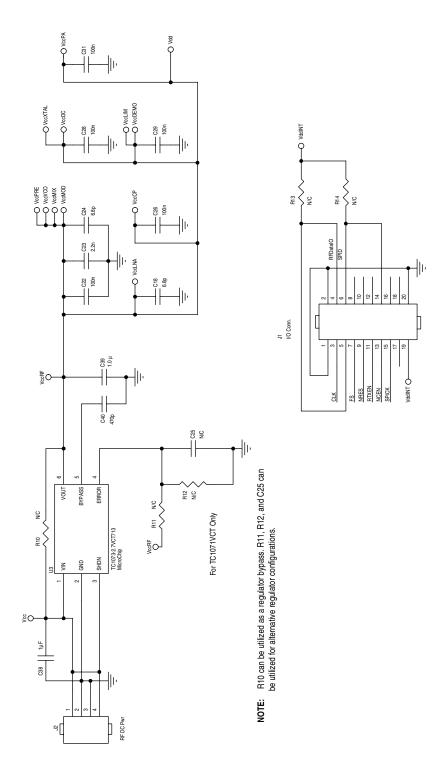

Figure 3. Test Circuit

| MC13180:        |                            |                             |              |                                            | Byte 1                                          | 31                                   |                              |       |                                |                                            |                                  |                  | Byte 0                                          |                     |       |                |                |

|-----------------|----------------------------|-----------------------------|--------------|--------------------------------------------|-------------------------------------------------|--------------------------------------|------------------------------|-------|--------------------------------|--------------------------------------------|----------------------------------|------------------|-------------------------------------------------|---------------------|-------|----------------|----------------|

| Docioto:        | Docistor                   |                             |              |                                            |                                                 |                                      |                              |       |                                |                                            |                                  |                  |                                                 |                     |       |                |                |

| Address         | Number                     | MSB Bit 15                  | Bit 14       | Bit 13                                     | Bit 12                                          | Bit 11                               | Bit 10                       | Bit 9 | Bit 8                          | Bt 7                                       | Bit 6                            | Bit5             | Bit 4                                           | Bit3                | Bit 2 | Bit 1          | LSB Bit0       |

| \$0<br>Programm | \$00<br>Programmable Reset |                             |              |                                            |                                                 |                                      |                              |       |                                |                                            |                                  |                  |                                                 |                     |       |                |                |

| \$Ot            | F                          | WSB                         |              |                                            |                                                 |                                      |                              |       | 16 Bit Frac-N Numi             | 16 Bit Frac-N Numerator Divide Value - num |                                  |                  |                                                 |                     |       |                | 887            |

|                 | RxTest                     | 0                           | 0            |                                            | +                                               | 0                                    | ļ                            | -     | F                              | F                                          | -                                | -                | F                                               | F                   | 0     | F              | 0              |

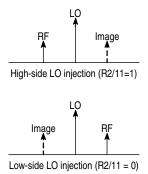

| 808             | Tx Test                    | Sleep<br>Enable             | T. T. Enable | 0<br>Enable                                | Narrow<br>Bandwidth<br>Fnable                   | 0<br>High/Low<br>Injection<br>Frable | 0                            | 0     | 1<br>General Purpose<br>Output | WSB -                                      | -                                | 0                | 1<br>Frac-N Integer Divide Valu                 | 0<br>Nvide Valu     | 0     | -              | 0<br>883       |

|                 | Rx Test<br>Tx Test         | 0 0                         | 0 +          | - 0                                        | 0 -                                             | - 0                                  |                              | 00    | 0 +                            |                                            | 0 0                              |                  |                                                 |                     | 0 0   | 0              | - 0            |

| \$0\$           | 8                          |                             |              |                                            |                                                 |                                      | External PA<br>Enable Invert |       |                                |                                            | General Purpose<br>Output Invert | WSB              |                                                 | PA DAC Setting      |       |                | 8S7            |

|                 |                            | 0                           | F            | 0                                          | 0                                               | 0                                    | 0                            | 0     | -                              | -                                          | 0                                | 0                | 0                                               | 0                   | 0     | 0              | 0              |

| \$0\$           | 4                          |                             |              |                                            |                                                 |                                      |                              |       |                                |                                            | RSSI Read<br>Enable              |                  |                                                 |                     |       |                |                |

|                 |                            | -                           | -            | -                                          | -                                               | -                                    | 0                            | 0     | 0                              | -                                          | 0                                | 0                | -                                               | -                   | 0     | 0              | -              |

| \$00            | ιo                         |                             |              |                                            |                                                 |                                      |                              |       |                                |                                            |                                  |                  |                                                 |                     |       | PA Bias Adjust |                |

|                 |                            | 0                           | 0            | F                                          | 0                                               | -                                    | 0                            | 0     | 0                              | -                                          | 0                                | -                | F                                               | F                   | 0     | F              | 0              |

| 90\$            | 9                          | External PA<br>Enable = GPO | MSB          |                                            | Xtal Trim                                       |                                      | ESB.                         | MSB   |                                |                                            |                                  | DC PII R Counter |                                                 |                     |       |                | 887            |

|                 |                            | F                           | F            | 0                                          | 0                                               | 0                                    | 0                            | -     | 0                              | F                                          | 0                                | 0                | 0                                               | F                   | 0     | F              | 0              |

| \$07            | 7                          |                             | Dualf        | Dual Port Programmable Delay<br>For Tx PLL | elay                                            |                                      | MSB                          |       |                                |                                            | _                                | DCPII NCounter   |                                                 |                     |       |                | 887            |

|                 |                            | F                           | 0            | 0                                          | -                                               | F                                    | F                            | 0     | 0                              | -                                          | 0                                | -                | F                                               | 0                   | 0     | 0              | 0              |

| 808             | 8                          | MSB                         |              | T                                          | Transmit Synchronization Time Delay Value       | n Time Delay Value                   |                              |       | LSB                            | MSB                                        |                                  | ₽E               | B-Dual Port Digital Multiplier Value For Tx PUL | er Value For Tx PLL |       |                | RS1            |

|                 |                            | -                           | 0            | -                                          | +                                               | -                                    | 0                            | 0     | 0                              | 0                                          | -                                | +                | 0                                               | 0                   | 1     | 0              | 0              |

| 808             | 6                          |                             |              |                                            |                                                 |                                      |                              |       | RSSI Enable                    |                                            |                                  |                  |                                                 |                     |       |                |                |

|                 |                            | 0                           | 1            |                                            | +                                               | 1                                    | +                            | +     | 0                              | 1                                          | -                                | 0                | -                                               | -                   | -     | +              | -              |

| SOA             | 9                          |                             |              |                                            | ,                                               |                                      |                              | -     |                                | ·                                          | ·                                | ,                | *                                               |                     |       | -              | <del>,</del>   |

|                 |                            |                             |              |                                            | -                                               |                                      | -                            | -     | -                              | - 1                                        | Edomo                            |                  | -                                               |                     |       | -              | -              |

| 808             | E                          |                             |              |                                            |                                                 |                                      |                              |       |                                | External<br>PA DAC<br>Enable               | External<br>PA<br>Enable         |                  | Xtal Boost<br>Enable                            |                     |       |                | Xtal<br>Enable |

|                 |                            | -                           | F            | -                                          | +                                               | F                                    | -                            | -     | F                              | 0                                          | -                                | -                | 0                                               | -                   | -     | -              | -              |

| 200             | 2                          | WSB                         |              |                                            | ROM_R2_c2                                       | ය ය                                  |                              |       | 887                            | MSB                                        |                                  |                  | ROM_⊓_c1                                        | 101                 |       |                | 881            |

|                 |                            | -                           | -            | 0                                          | 0                                               | 0                                    | -                            | -     | 0                              | F                                          | -                                | 0                | 0                                               | 0                   | -     | -              | 0              |

| 00%             | £                          | WSB                         |              |                                            | HOM_12_04                                       | 12.04                                |                              |       | 851                            | MSB                                        |                                  |                  | ROM_12_c3                                       | 2.03                |       |                | 887            |

|                 |                            | -                           | -            | 0                                          | 0                                               | 0                                    | 0                            | 0     | 0                              | F                                          | F                                | 0                | 0                                               | 0                   | -     | 0              | -              |

| \$0E            | 41                         | MSB                         |              |                                            | ROM_13_02                                       | 13_c2                                |                              |       | 138                            | MSB                                        |                                  |                  | ROM_R3_c1                                       | 3_c1                |       |                | LSB            |

|                 |                            | 0                           | -            | -                                          | 0                                               | -                                    | 0                            | 0     | 0                              | 0                                          | 0                                | +                | 0                                               | 0                   | 1     | 0              |                |

| SOF             | 15                         | MSB                         |              |                                            | ROM_13_04                                       | 13_04                                |                              |       | 88                             | MSB                                        |                                  |                  | ROM_r3_c3                                       | 3_63                |       |                | 8S.            |

|                 |                            | -                           | 0            | -                                          | F                                               | 0                                    | F                            | 0     | 0                              | -                                          | 0                                | 0                | -                                               | _                   | 0     | 0              | 0              |

| \$10            | 91                         | WSB                         |              |                                            | ROM_r4_c3                                       | 74_C3                                |                              |       | 883                            | MSB                                        |                                  |                  | ROM_r4_c2                                       | 4 c2                |       |                | 883            |

|                 |                            | -                           | 0            | 0                                          | F                                               | 0                                    | -                            | -     | 0                              | 0                                          | -                                | -                | 0                                               | -                   | 0     | 0              | 0              |

| \$11            | 17                         |                             |              | Ä                                          | M-Dual Port Digital Multiplier Value for Tx PLL | lier Value for Tx PLL                |                              |       |                                | MSB                                        |                                  |                  | ROM_r4_04                                       | 4.04                |       |                | 881            |

| 1               |                            | 0                           | -            | -                                          | 0                                               | -                                    | -                            | 0     | 0                              | -                                          | 0                                | -                | 0                                               | -                   | -     | 0              | -              |

| \$12            | 18                         |                             |              |                                            |                                                 |                                      |                              |       |                                |                                            |                                  |                  |                                                 |                     |       |                |                |

|                 |                            | 0                           | 0            | 0                                          | 0                                               | 0                                    | 0                            | 0     | 0                              | 0                                          | 0                                | 0                | 0                                               | 0                   | 0     | 0              | 0              |

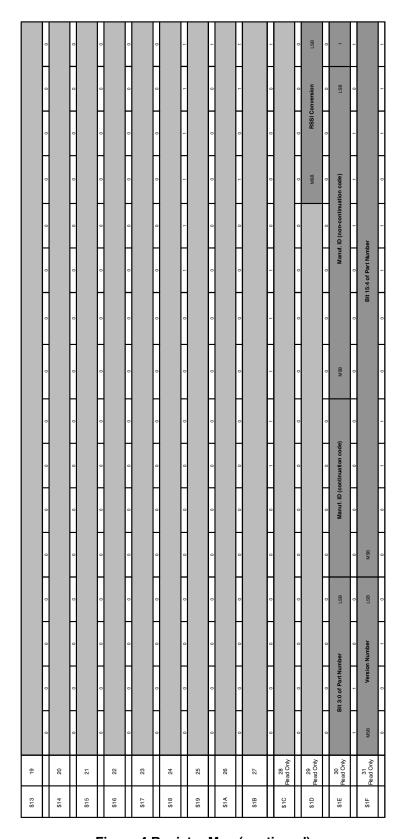

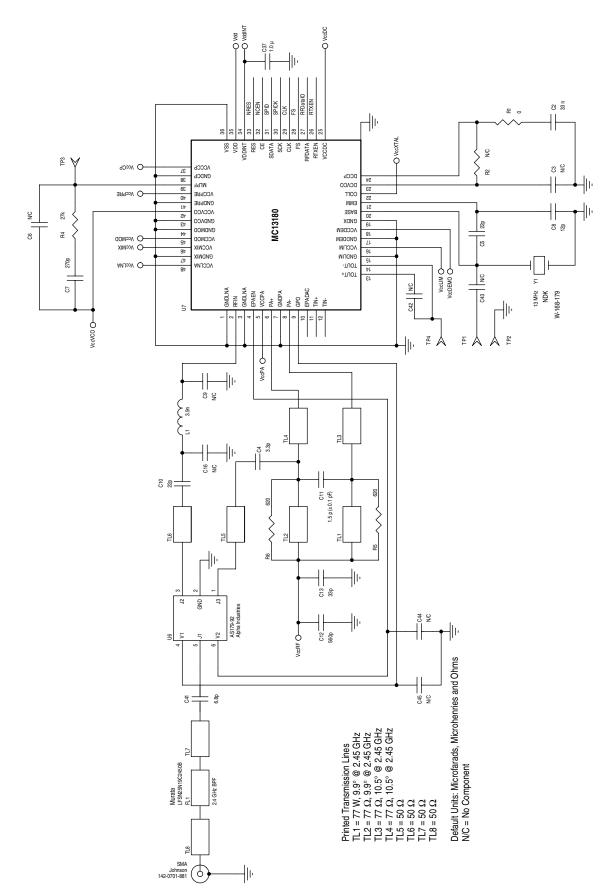

Figure 4. Register Map

Figure 4 Register Map (continued)

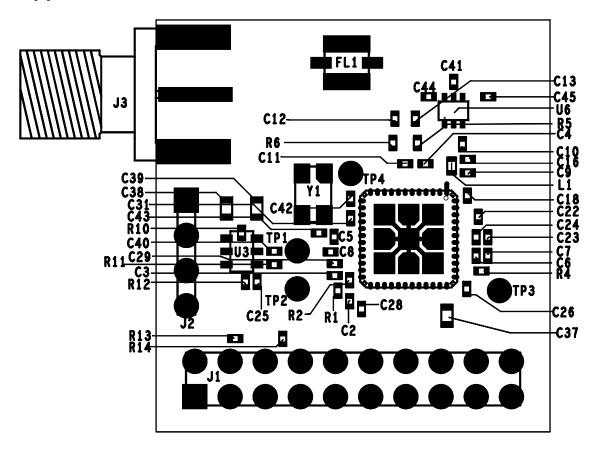

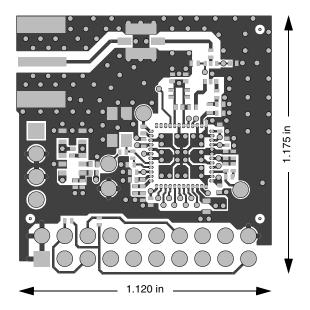

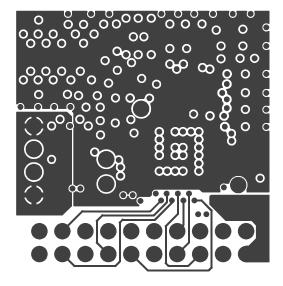

# 2 Pin Connections

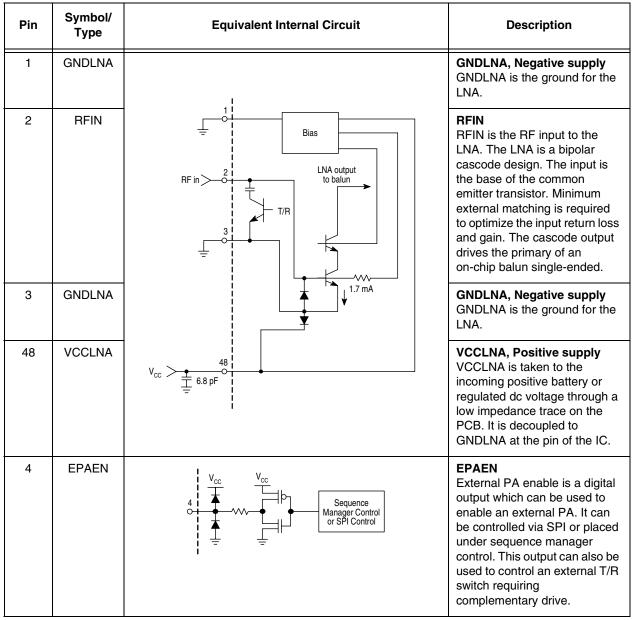

**Table 13. Pin Function Description**

NOTE: V<sub>CC</sub> = V<sub>CC</sub>RF

Table 13. Pin Function Description (Continued)

| Pin | Symbol/<br>Type | Equivalent Internal Circuit                    | Description                                                                                                                                                                                                                                     |

|-----|-----------------|------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

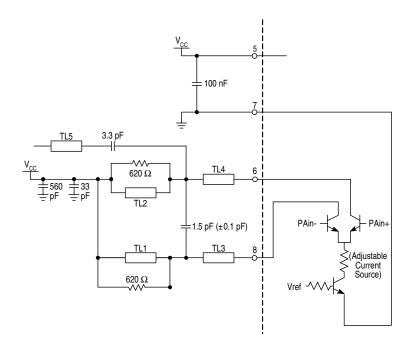

| 5   | VCCPA           | See Figure 5.                                  | VCCPA, Positive Supply VCCPA pin is taken to the incoming positive battery or regulated dc voltage through a low impedance trace on the PCB. It is decoupled to GNDPA at the pin of the IC.                                                     |

| 7   | GNDPA           |                                                | GNDPA, Negative Supply GNDPA pin is taken to an ample dc ground plane through a low impedance path. The path should be kept as short as possible. A multi-sided PCB is implemented so that ground returns can be easily made through via holes. |

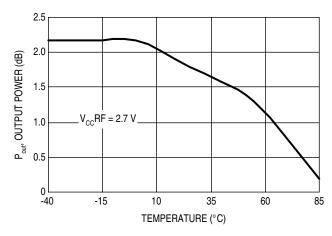

| 6   | PA+             |                                                | PA + Positive differential PA output. An external differential-to-single-ended matching network is desired.                                                                                                                                     |

| 8   | PA -            |                                                | PA - Negative differential PA output. An external differential-to-single-ended matching network is desired.                                                                                                                                     |

| 9   | GPO             | 9 V <sub>CC</sub> V <sub>CC</sub> SPI Control  | GPO The General Purpose Output is a digital output. GPO can be controlled by the SPI. This signal can also be used to control an external T/R Switch.                                                                                           |

| 10  | EPADAC          | 10 V <sub>CC</sub> V <sub>CC</sub> SPI Control | EPADAC External PA driver. Analog output ranges from 0.02 to V <sub>CC</sub> RF - 0.02. The EPADAC is linearly scaled to a maximum V <sub>CC</sub> of 3.1 V.                                                                                    |

Table 13. Pin Function Description (Continued)

| Pin | Symbol/<br>Type | Equivalent Internal Circuit                                                 | Description                                                                 |

|-----|-----------------|-----------------------------------------------------------------------------|-----------------------------------------------------------------------------|

| 11  | TIN +           | Inject/Monitor Decoder → SPI                                                | TIN + This pin is for factory use only. It can be grounded or left open.    |

| 12  | TIN -           | 11 RX/TX Chain                                                              | TIN - This pin is for factory use only. It can be grounded or left open.    |

| 13  | TOUT +          |                                                                             | TOUT + This pin is for factory use only. It must be left open.              |

| 14  | TOUT -          | 13 V <sub>CC</sub> 14 V <sub>CC</sub> 14 V <sub>CC</sub> 14 V <sub>CC</sub> | TOUT - This pin is for factory use only. It must be left open.              |

| 15  | GNDLIM          | 15 1<br>V <sub>20</sub> 100 nF                                              | GNDLIM, Negative supply GNDLIM is the ground for limiter.                   |

| 16  | VCCLIM          | 16                                                                          | VCCLIM, Positive supply VCCLIM is decoupled to GNDLIM at the pin of the IC. |

| 17  | GNDDEM          | 17 17 100 nF                                                                | GNDDEM, Negative supply<br>GNDDEM is the ground for<br>demodulator.         |

| 18  | VCCDEM          | V <sub>cc</sub> 18                                                          | VCCDEM, Positive supply VCCDEM is decoupled to GNDDEM at the pin of the IC. |

Table 13. Pin Function Description (Continued)

| Pin | Symbol/<br>Type | Equivalent Internal Circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Description                                                                                                                                                                              |

|-----|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 19  | GNDX            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | GNDX Reference oscillator ground.                                                                                                                                                        |

| 20  | BASE            | 19 VCC 22 100 nF 13 MHz 20 110 mA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | BASE Reference oscillator base. The base is the reference oscillator input. An on-chip capacitor trim network is also included to allow the user to use relatively inexpensive crystals. |

| 21  | ЕММ             | 13 MHz 20 22 pF 21 3 lias Current Current Copy  Trim C | EMM Reference oscillator emitter. A bias current of 50 μA is supplied internally to the emitter.                                                                                         |

| 22  | COLL            | Shown for 13 MHz reference oscillator.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | COLL Reference oscillator collector. The collector is tied to VCC. The pin of the IC is bypassed to gnd.                                                                                 |

| 23  | DCVCO           | 23 DC VCO Control Voltage Charge                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | DCVCO Data Clock Loop Filter VCO control voltage. This pin can be used to raise/lower the loop corner frequency in conjunction with the DCCP pin and external components.                |

| 24  | DCCP            | 33 nF = 9.0 kΩ Pump  V <sub>CC</sub> 25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | DCCP Data Clock Loop Filter charge pump.                                                                                                                                                 |