Order this document by MC145506/D

# Advance Information PCM Codec-Filter Mono-Circuit

The MC145506, MC145507, and MC145508 are per channel codec–filter PCM mono–circuits. These devices perform the voice digitization and reconstruction, as well as the band limiting and smoothing required for PCM systems. These devices have HCMOS compatible digital outputs and otherwise supplement the MC145500 – MC145505 series of PCM codec–filters. The MC145506, MC145507, and MC145508 are functionally similar to the MC145502, MC145503, and MC145505, respectively. They are designed to operate in both synchronous and asynchronous applications and contain an on–chip precision reference voltage. The MC145506 is offered in a 22–pin package and has the capability of selecting from three peak overload voltages (2.5 V, 3.15 V, and 3.78 V). The MC145507 and MC145508 offer versatility and low cost in 16–pin DIP and wide body SOIC packages. Most of the features of these devices can be made available in a lower pin count package tailored to a specific user's application. Contact the factory for further details.

These devices maintain compatibility with Motorola's family of MC3419/ MC33120 SLIC products.

The MC145500 family of PCM codec–filter mono–circuits utilize CMOS due to its reliable low–power performance and proven capability for complex analog/digital VLSI functions.

MC145506 (22-Pin Package, HCMOS Output Version of MC145502)

- Selectable Peak Overload Voltages (2.5 V, 3.15 V, 3.78 V)

- Push–Pull Analog Output with Gain Adjust

- 64 kHz to 4.1 MHz Transmit and/or Receive Data Clock Rate

- All the Features of the MC145507 Listed Below

MC145507 (16-Pin Package, HCMOS Output Version of MC145503)

- Transmit Bandpass and Receive Low-Pass Filters on Chip

- Pin Selectable Mu/A Law Companding with Corresponding Data Format

- On-Chip Precision Reference Voltage (3.15 V)

- Power Dissipation of 50 mW, Power Down of 0.1 mW at ±5 V

- Three Terminal Transmit Input Operational Amplifier

- Automatic Prescaler Accepts 128 kHz, 1.536 MHz, 1.544 MHz, 2.048 MHz, and 2.56 MHz for Internal Sequencing

- Separate Transmit and Receive Data Clocks

MC145508 (16–Pin Package, HCMOS Output Version of MC145505) Same as MC145507 Except:

- Common 64 kHz to 4.1 MHz Transmit/Receive Data Clock

- Separate CCI Pin with Automatic Prescaler Accepts 128 kHz, 1.536 MHz, 1.544 MHz, 2.048 MHz, and 2.56 MHz for Internal Sequencing

MC145506

MC145507

This document contains information on a new product. Specifications and information herein are subject to change without notice.

REV 0 2/00

© Motorola, Inc. 2000

For More Information On This Product, Go to: www.freescale.com

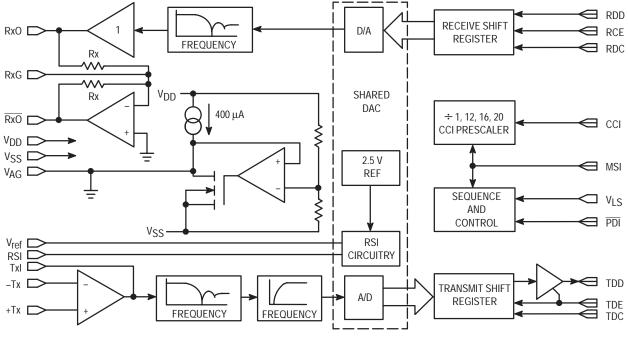

# MC145506/07/08 PCM CODEC-FILTER MONO-CIRCUIT BLOCK DIAGRAM

NOTES:  $\bigcirc$  Controlled by V<sub>LS</sub>.  $Rx \approx 100 \text{ k}\Omega$  (internal resistors).

## **PIN ASSIGNMENTS**

(Drawings Do Not Reflect Relative Size)

| MC145506P        |   |    |    |                   |  |  |  |  |

|------------------|---|----|----|-------------------|--|--|--|--|

| V <sub>ref</sub> | ۵ | 1• | 22 | ] rsi             |  |  |  |  |

| VAG              | ۵ | 2  | 21 | D v <sub>DD</sub> |  |  |  |  |

| RxO              | ۵ | 3  | 20 | RDD               |  |  |  |  |

| RxG              | ۵ | 4  | 19 | RCE               |  |  |  |  |

| RxO              | C | 5  | 18 | RDC               |  |  |  |  |

| +Tx              | ۵ | 6  | 17 | D TDC             |  |  |  |  |

| TxI              | ۵ | 7  | 16 | О ССІ             |  |  |  |  |

| -Tx              | ۵ | 8  | 15 | D TDD             |  |  |  |  |

| Mu/A             | ۵ | 9  | 14 | D TDE             |  |  |  |  |

| PDI              | C | 10 | 13 | D MSI             |  |  |  |  |

| V <sub>SS</sub>  | q | 11 | 12 | D V <sub>LS</sub> |  |  |  |  |

|                  |   |    |    |                   |  |  |  |  |

|                   | MC145507F | •                 |                   | MC145  |

|-------------------|-----------|-------------------|-------------------|--------|

| V <sub>AG</sub> [ | 1• 16     | ] v <sub>DD</sub> | v <sub>ag</sub> [ | 1•     |

| RxO [             | 2 15      | RDD               | RxO [             | 2      |

| +тх 🛛             | 3 14      | ] RCE             | +Tx [             | 3      |

| тхі 🛛             | 4 13      | ] rdc             | тхі 🛙             | 4      |

| –тх 🛛             | 5 12      | ] трс             | _тх 🛛             | 5      |

| Mu/A              | 6 11      | d dd C            | Mu/A 🛛            | 6      |

| PDI [             | 7 10      | ] tde             | PDI [             | 7      |

| v <sub>ss</sub> [ | 8 9       | ] v <sub>LS</sub> | v <sub>ss</sub> [ | 8      |

|                   |           |                   |                   |        |

| Г                 | MC145507D | w                 | r                 | MC1455 |

| v <sub>ag</sub> C | 1• 16     | v <sub>DD</sub>   | v <sub>AG</sub> [ | 1•     |

| RxO [             | 2 15      | ] RDD             | RxO [             | 2      |

| +Tx [             | 3 14      | RCE               | +Tx [             | 3      |

| txi C             | 4 13      | RDC               | txi [             | 4      |

| −tx C             | 5 12      | 🛛 тос             | -tx [             | 5      |

| Mu/A [            | 6 11      | D TDD             | Mu/A [            | 6      |

| PDI [             | 7 10      | D TDE             | PDI [             | 7      |

5508P 16 🛛 V<sub>DD</sub> 15 🛛 RDD 14 🛛 RCE 13 DC 12 CCI 11 🛛 TDD 10 D TDE 9 🛛 V<sub>LS</sub>

| MC145508DW        |    |    |                   |  |  |  |  |  |

|-------------------|----|----|-------------------|--|--|--|--|--|

| V <sub>AG</sub> [ | 1• | 16 | l v <sub>DD</sub> |  |  |  |  |  |

| RxO [             | 2  | 15 | RDD               |  |  |  |  |  |

| +Tx [             | 3  | 14 | RCE               |  |  |  |  |  |

| txi [             | 4  | 13 | D DC              |  |  |  |  |  |

| –тх 🛛             | 5  | 12 | Оссі              |  |  |  |  |  |

| Mu/A 🛛            | 6  | 11 | d tdd             |  |  |  |  |  |

| PDI [             | 7  | 10 | ] TDE             |  |  |  |  |  |

| v <sub>SS</sub> [ | 8  | 9  | V <sub>LS</sub>   |  |  |  |  |  |

V<sub>SS</sub> [ 8

9 🛛 V<sub>LS</sub>

## ABSOLUTE MAXIMUM RATINGS (Voltage Referenced to VSS)

| Rating                                            | Symbol            | Value                         | Unit |

|---------------------------------------------------|-------------------|-------------------------------|------|

| DC Supply Voltage                                 | $V_{DD} - V_{SS}$ | -0.5 to 13                    | V    |

| Voltage, Any Pin to V <sub>SS</sub>               | V                 | –0.5 to V <sub>DD</sub> + 0.5 | V    |

| DC Drain Per Pin (Excluding $V_{DD}$ , $V_{SS}$ ) | I                 | 10                            | mA   |

| Operating Temperature Range                       | TA                | -40 to 85                     | °C   |

| Storage Temperature Range                         | T <sub>stg</sub>  | -85 to 150                    | °C   |

This device contains circuitry to protect against damage due to high static voltages or electric fields; however, it is advised that normal precautions be taken to avoid application of any voltage higher than maximum rated voltages to this high–impedance circuit. For proper operation, it is recommended that V<sub>in</sub> and V<sub>out</sub> be constrained to the range V<sub>SS</sub>  $\leq$  (V<sub>in</sub> or V<sub>out</sub>)  $\leq$  V<sub>DD</sub>.

Unused inputs must always be tied to an appropriate logic voltage level (e.g.,  $V_{SS}$ ,  $V_{DD}$ ,  $V_{LS}$ , or  $V_{AG}$ ).

# **RECOMMENDED OPERATING CONDITIONS** (T<sub>A</sub> = $-40^{\circ}$ to $85^{\circ}$ C)

| Characteristic                                                                                     |                | Min         | Тур                     | Max          | Unit |

|----------------------------------------------------------------------------------------------------|----------------|-------------|-------------------------|--------------|------|

| DC Supply Voltage                                                                                  |                |             |                         |              | V    |

| Dual Supplies: $V_{DD} = -V_{SS} (V_{AG} = V_{LS} = 0 V)$                                          |                | 4.75        | 5.0                     | 6.3          |      |

| Single Supply: $V_{DD}$ to $V_{SS}$ (V <sub>AG</sub> is an Output, $V_{LS} = V_{DD}$ or $V_{SS}$ ) |                |             |                         |              |      |

| MC145506, MC145507, MC145508 Using Internal 3.15 V Reference                                       | 9              | 8.5         | —                       | 12.6         |      |

| MC145506 Using Internal 2.5 V Reference<br>MC145506 Using Internal 3.78 V Reference                |                | 7.0<br>9.5  | _                       | 12.6<br>12.6 |      |

| MC145506 Using External 1.5 V Reference, Referenced to $V_{AG}$                                    |                | 9.5<br>4.75 |                         | 12.6         |      |

| No 145500 Using External 1.5 V Relefence, Relefenced to VAG                                        |                | 4.75        |                         | 12.0         |      |

| Power Dissipation                                                                                  |                |             |                         |              | mW   |

| CMOS Logic Mode ( $V_{DD}$ to $V_{SS} = 10 \text{ V}, \text{ V}_{LS} = \text{V}_{DD}$ )            |                | —           | 40                      | 70           |      |

| HCMOS Logic Mode ( $V_{DD}$ = 5 V, $V_{SS}$ = –5 V, $V_{LS}$ = $V_{AG}$ = 0 V)                     |                | _           | 50                      | 90           |      |

| Power Down Dissipation                                                                             | _              | 0.1         | 1.0                     | mW           |      |

| Frame Rate Transmit and Receive                                                                    |                | 7.5         | 8.0                     | 8.5          | kHz  |

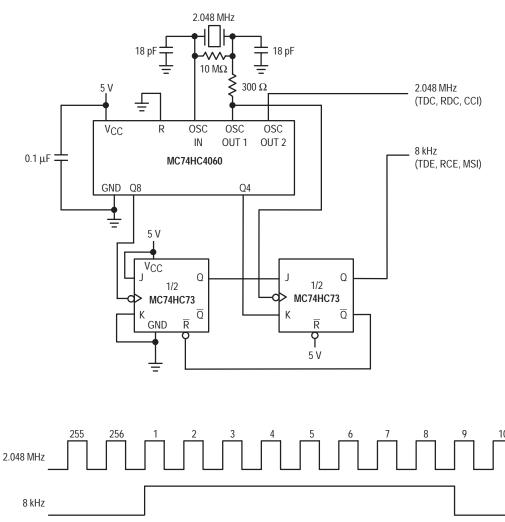

| CCI Clock Rate (TDC Clock Rate for MC145507)                                                       |                |             | 128                     | _            | kHz  |

| MC145506, MC145508                                                                                 |                | —           | 1536                    | _            |      |

| Must Use One of These Frequencies $\pm 2\%$ , Relative to MSI Frequence                            | y of 8 kHz     | —           | 1544                    | —            |      |

|                                                                                                    |                | —           | 2048                    | -            |      |

|                                                                                                    |                | —           | 2560                    | —            |      |

| Data Rate for MC145506, MC145508                                                                   |                | 64          | _                       | 4096         | kHz  |

| Full Scale Analog Input and Output Level                                                           |                |             |                         |              | Vp   |

| MC145507, MC145508                                                                                 |                | _           | 3.15                    | _            |      |

| MC145506 ( $V_{ref} = V_{SS}$ )                                                                    | $RSI = V_{DD}$ | —           | 3.78                    | _            |      |

|                                                                                                    | $RSI = V_{SS}$ | —           | 3.15                    | _            |      |

|                                                                                                    | $RSI = V_{AG}$ | —           | 2.5                     | -            |      |

| MC145506 Using an External Reference Voltage Applied at $V_{ref}$ Pin                              | $RSI = V_{DD}$ | —           | 1.51 x V <sub>ref</sub> | -            |      |

|                                                                                                    | RSI = VSS      | —           | 1.26 x V <sub>ref</sub> | -            |      |

|                                                                                                    | $RSI = V_{AG}$ | _           | V <sub>ref</sub>        | -            |      |

# **DIGITAL LEVELS** (V<sub>SS</sub> to V<sub>DD</sub> = 4.75 V to 12.6 V, $T_A = -40^{\circ}$ to 85°C)

| Characteristic                                                                                        | Symbol     | Min                     | Max                          | Unit |

|-------------------------------------------------------------------------------------------------------|------------|-------------------------|------------------------------|------|

| Input Voltage Levels (TDE, TDC, RCE, RDC, RDD, DC, MSI, CCI, PDI)                                     |            |                         |                              | V    |

| CMOS Mode ( $V_{LS} = V_{DD}$ , $V_{SS}$ is Digital Ground) "0"                                       | VIL        |                         | 0.3 x V <sub>DD</sub>        |      |

|                                                                                                       | VIH<br>VIL | 0.7 x V <sub>DD</sub>   | —<br>V <sub>LS</sub> + 0.8 V |      |

| HCMOS Mode ( $V_{LS} \le V_{DD} - 4.0 \text{ V}$ , $V_{LS}$ is Digital Ground) "0"<br>"1"             | VIL        | V <sub>LS</sub> + 2.0 V | VLS + 0.0 V                  |      |

| Output Current for TDD (Transmit Digital Data)                                                        |            |                         |                              | mA   |

| CMOS Mode ( $V_{LS} = V_{DD}$ , $V_{SS} = 0$ V and is Digital Ground)                                 |            |                         |                              |      |

| (V <sub>DD</sub> = 5 V, V <sub>out</sub> = 0.4 V)                                                     | IOL        | 1.6                     | —                            |      |

| $(V_{DD} = 10 \text{ V}, V_{out} = 0.5 \text{ V})$                                                    |            | 1.6                     | -                            |      |

| $(V_{DD} = 5 V, V_{out} = 4.5 V)$<br>$(V_{DD} = 10 V, V_{out} = 9.5 V)$                               | ЮН         | -1.6<br>-1.6            |                              |      |

| HCMOS Mode (VI $S \le V_{DD} - 4.75$ V, VI $S = 0$ V and is Digital Ground) (V <sub>DI</sub> = 0.4 V) | IOL        | 1.6                     | _                            |      |

| $(V_{OH} = V_{DD} - 0.5 V)$                                                                           | IOH        | -1.6                    | —                            |      |

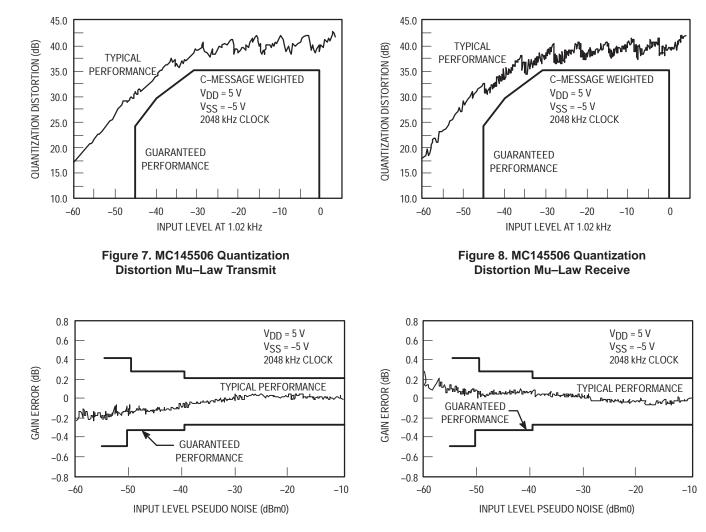

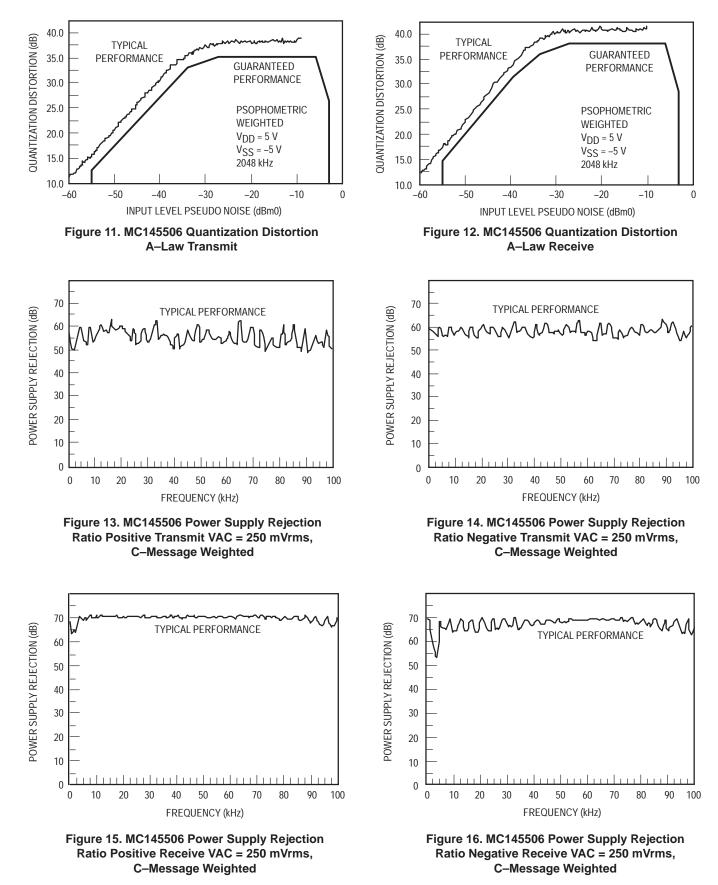

# ANALOG TRANSMISSION PERFORMANCE

(V<sub>DD</sub> = 5 V  $\pm$  5%, V<sub>SS</sub> = -5 V  $\pm$  5%, V<sub>LS</sub> = V<sub>AG</sub> = 0 V, V<sub>ref</sub> = RSI = V<sub>SS</sub> (Internal 3.15 V Reference),

0 dBm0 = 1.546 Vrms = 6 dBm @ 600  $\Omega$ , T<sub>A</sub> = -40° to 85°C, TDC = RDC = CCI, TDE = RCE = MSI, Unless Otherwise Noted)

| Characteristic                                                                                          |                                                                                                                              | End-t                              | o–End                         | A/D                                |                                | D/A                                |                                 |               |

|---------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|------------------------------------|-------------------------------|------------------------------------|--------------------------------|------------------------------------|---------------------------------|---------------|

|                                                                                                         |                                                                                                                              | Min                                | Max                           | Min                                | Max                            | Min                                | Max                             | Unit          |

| Absolute Gain (0 dBm0 @ 1.02 kHz, T <sub>A</sub> = 25°C, V <sub>DD</sub> = 5 V, V <sub>SS</sub> = -5 V) |                                                                                                                              |                                    | _                             | -0.30                              | 0.30                           | -0.30                              | 0.30                            | dB            |

| Absolute Gain Variation with Temperature 0° to 70°C                                                     |                                                                                                                              |                                    | _                             | —                                  | ±0.03                          | —                                  | ±0.03                           | dB            |

| Absolute Gain Variation with Temperature –40° to $85^{\circ}$ C                                         |                                                                                                                              | _                                  | _                             | -                                  | ±0.1                           | -                                  | ±0.1                            | dB            |

| Absolute Gain Variation with Power Supply ( $V_{DD} = 5 V$ ,                                            | V <sub>SS</sub> = -5 V, 5%)                                                                                                  |                                    | _                             | -                                  | ±0.02                          | _                                  | ±0.02                           | dB            |

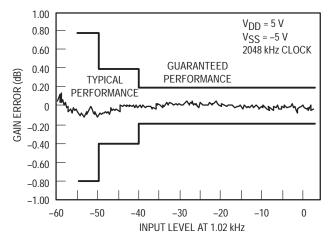

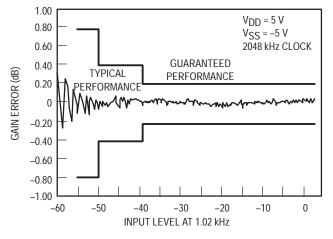

| Gain vs Level Tone (Relative to –10 dBm0, 1.02 kHz)                                                     | 3 to -40 dBm0<br>-40 to -50 dBm0<br>-50 to -55 dBm0                                                                          | -0.4<br>-0.8<br>-1.6               | 0.4<br>0.8<br>1.6             | -0.2<br>-0.4<br>-0.8               | 0.2<br>0.4<br>0.8              | -0.2<br>-0.4<br>-0.8               | 0.2<br>0.4<br>0.8               | dB            |

| Gain vs Level Pseudo Noise (A–Law Relative to –10 dB<br>CCITT G.714                                     | m0)<br>-10 to -40 dBm0<br>-40 to -50 dBm0<br>-50 to -55 dBm0                                                                 |                                    |                               | -0.25<br>-0.30<br>-0.45            | 0.25<br>0.30<br>0.45           | -0.25<br>-0.30<br>-0.45            | 0.25<br>0.30<br>0.45            | dB            |

| Total Distortion – 1.02 kHz Tone (C–Message)                                                            | 0 to –30 dBm0<br>–40 dBm0<br>–45 dBm0                                                                                        | 35<br>29<br>24                     |                               | 36<br>29<br>24                     |                                | 36<br>30<br>25                     |                                 | dBC           |

| Total Distortion With Pseudo Noise (A–Law)<br>CCITT G.714                                               | -3 dBm0<br>-6 to -27 dBm0<br>-34 dBm0<br>-40 dBm0<br>-55 dBm0                                                                | 27.5<br>35<br>33.1<br>28.2<br>13.2 | <br><br>                      | 28<br>35.5<br>33.5<br>28.5<br>13.5 | <br>                           | 28.5<br>36<br>34.2<br>30.0<br>15.0 | <br>                            | dB            |

|                                                                                                         | essage Weighted)<br>ometric Weighted)                                                                                        |                                    | 15<br>69                      |                                    | 15<br>69                       |                                    | 9<br>78                         | dBrnC<br>dBm0 |

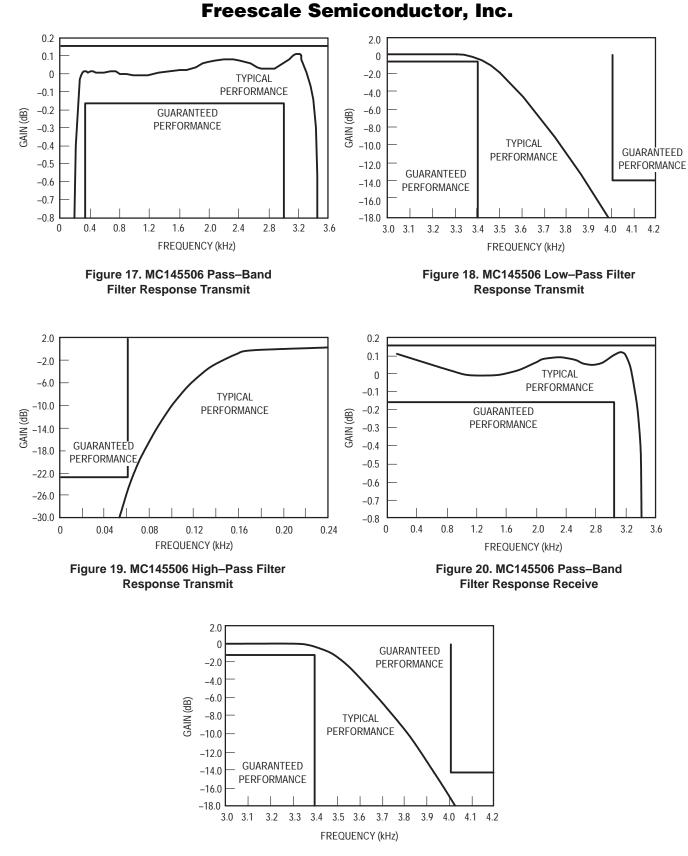

| Frequency Response (Relative to 1.02 kHz @ 0 dBm0)                                                      | 15 to 60 Hz<br>300 to 3000 Hz<br>3400 Hz<br>4000 Hz<br>≥4600 Hz                                                              | <br>                               | -23<br>0.3<br>0<br>-28<br>-60 | <br>_0.15<br><br>                  | -23<br>0.15<br>0<br>-14<br>-32 | <br>_0.15<br><br>                  | 0.15<br>0.15<br>0<br>-14<br>-30 | dB            |

| Inband Spurious (1.02 kHz @ 0 dBm0, Transmit and Rx                                                     | :O)<br>300 to 3000 Hz                                                                                                        |                                    | —                             | —                                  | -43                            | -                                  | -43                             | dBm0          |

| Out–of–Band Spurious at RxO (300 – 3400 Hz @ 0 dBr<br>8                                                 | n0 In)<br>4600 to 7600 Hz<br>7600 to 8400 Hz<br>400 to 100,000 Hz                                                            |                                    | -30<br>-40<br>-30             |                                    |                                |                                    | -30<br>-40<br>-30               | dB            |

| Idle Channel Noise Selective @ 8 kHz, Input = $V_{AG}$ , 30                                             | Hz Bandwidth                                                                                                                 | _                                  | -70                           | _                                  | _                              | _                                  | -70                             | dBm0          |

| Absolute Delay @ 1020 Hz (TDC = 2.048 MHz, TDE = 8                                                      | 3 kHz)                                                                                                                       |                                    |                               |                                    |                                |                                    |                                 | μs            |

| Group Delay Referenced to 1600 Hz (TDC = 2048 kHz,<br>TDE = 8 kHz)                                      | 500 to 600 Hz<br>600 to 800 Hz<br>800 to 1000 Hz<br>1000 to 1600 Hz<br>1600 to 2600 Hz<br>2600 to 2800 Hz<br>2800 to 3000 Hz |                                    |                               |                                    |                                |                                    |                                 | μs            |

| Crosstalk of 1020 Hz @ 0 dBm0 From A/D or D/A (Note                                                     | 2)                                                                                                                           |                                    | _                             | _                                  | -75                            | _                                  | -80                             | dB            |

| Intermodulation Distortion of Two Frequencies of Amplit<br>-21 dBm0 from the Range 300 to 3400 Hz       | udes –4 to                                                                                                                   |                                    | —                             | -                                  | -41                            | -                                  | -41                             | dB            |

NOTES:

1. Extrapolated from a 1020 Hz @ –50 dBm0 distortion measurement to correct for encoder enhancement.

2. Selectively measured while the A/D is stimulated with 2667 Hz @ –50 dBm0.

# ANALOG ELECTRICAL CHARACTERISTICS (V<sub>DD</sub> = $-V_{SS}$ = 5 V to 6 V ±5%, T<sub>A</sub> = $-40^{\circ}$ to 85°C)

| Characteristic                                                                                                                                                                |                        | Symbol           | Min                                            | Тур                                            | Max                                            | Unit   |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|------------------|------------------------------------------------|------------------------------------------------|------------------------------------------------|--------|

| Input Current +Tx,                                                                                                                                                            | , –Tx                  | l <sub>in</sub>  | -                                              | ±0.01                                          | ±0.2                                           | μΑ     |

| AC Input Impedance to V <sub>AG</sub> (1 kHz) +Tx,                                                                                                                            | , –Tx                  | Z <sub>in</sub>  | 5                                              | 10                                             | _                                              | MΩ     |

| Input Capacitance +Tx,                                                                                                                                                        | , –Tx                  |                  | _                                              | _                                              | 10                                             | pF     |

| Input Offset Voltage of TxI Op Amp                                                                                                                                            |                        |                  | -                                              | < ±30                                          | _                                              | mV     |

| Input Common Mode Voltage Range +Tx,                                                                                                                                          | , –Tx                  | VICR             | V <sub>SS</sub> + 1.0                          | _                                              | V <sub>DD</sub> – 2.0                          | V      |

| Input Common Mode Rejection Ratio +Tx,                                                                                                                                        | , –Tx                  | CMRR             | _                                              | 70                                             | _                                              | dB     |

| Txl Unity Gain Bandwidth $R_L \ge 10$                                                                                                                                         | 0 kΩ                   | BWp              | _                                              | 1000                                           | _                                              | kHz    |

| Txl Open Loop Gain $R_L \ge 10$                                                                                                                                               | 0 kΩ                   | AVOL             | _                                              | 75                                             | _                                              | dB     |

| Equivalent Input Noise (C-Message) Between +Tx and -Tx, at Txl                                                                                                                |                        |                  | -                                              | -20                                            |                                                | dBrnC0 |

| Output Load Capacitance for Txl Op Amp                                                                                                                                        |                        |                  | 0                                              | _                                              | 100                                            | pF     |

| Output Voltage Range Txl Op Amp, RxO or $\overline{RxO}$<br>RL = 10 k $\Omega$ to V<br>RL = 600 $\Omega$ to V                                                                 | V <sub>AG</sub><br>VAG | V <sub>out</sub> | V <sub>SS</sub> + 0.8<br>V <sub>SS</sub> + 1.5 | _                                              | V <sub>DD</sub> – 1.0<br>V <sub>DD</sub> – 1.5 | V      |

| $\label{eq:VSS} \mbox{Output Current Txl, RxO, } \overline{RxO} \qquad \qquad \mbox{V}_{\mbox{SS}} + 1.5 \ \mbox{V} \leq \mbox{V}_{\mbox{OUt}} \leq \mbox{V}_{\mbox{DD}} - 1$ | 1.5 V                  |                  | ±5.5                                           | —                                              | —                                              | mA     |

| Output Impedance RxO, RxO* 0 to 3.4                                                                                                                                           | kHz                    | Zout             | -                                              | 3                                              | _                                              | Ω      |

| Output Load Capacitance for RxO and RxO*                                                                                                                                      |                        |                  | 0                                              | —                                              | 200                                            | pF     |

| AO                                                                                                                                                                            | RxO<br>RxO*            |                  | _                                              |                                                | ±100<br>±150                                   | mV     |

| Internal Gainsetting Resistors for RxG to RxO and RxO                                                                                                                         |                        |                  | 62                                             | 100                                            | 225                                            | kΩ     |

| External Reference Voltage Applied to $V_{\mbox{ref}}$ (Referenced to $V_{\mbox{AG}})$                                                                                        |                        |                  | 0.5                                            | _                                              | V <sub>DD</sub> – 1.0                          | V      |

| V <sub>ref</sub> Input Current                                                                                                                                                |                        |                  | _                                              | —                                              | 20                                             | μA     |

| V <sub>AG</sub> Output Bias Voltage                                                                                                                                           |                        |                  | -                                              | 0.53 V <sub>DD</sub> +<br>0.47 V <sub>SS</sub> |                                                | V      |

|                                                                                                                                                                               | ource<br>Sink          | IVAG             | 0.4<br>10.0                                    | —                                              | 0.8                                            | mA     |

| Output Leakage Current During Power Down for the Txl Op Amp, $V_{\mbox{\rm A}}$ RxO, and $\mbox{\rm RxO}$                                                                     | <u>.</u> G,            |                  | -                                              | —                                              | ±30                                            | μΑ     |

|                                                                                                                                                                               | nsmit<br>ceive         |                  | 45<br>55                                       | 50<br>65                                       | —                                              | dBC    |

|                                                                                                                                                                               | nsmit<br>ceive         |                  | 50<br>50                                       | 55<br>60                                       |                                                | dBC    |

\* Assumes that RxG is not connected for gain modifications to  $\overline{RxO}$ .

# **MODE CONTROL LOGIC** (V<sub>SS</sub> to V<sub>DD</sub> = 4.75 V to 12.6 V, T<sub>A</sub> = $-40^{\circ}$ to $85^{\circ}$ C)

| Characteristic                                                                                                                    | Min                                              | Тур                                                               | Max | Unit                                                              |     |

|-----------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------|-------------------------------------------------------------------|-----|-------------------------------------------------------------------|-----|

| $V_{LS}$ Voltage for HCMOS Mode (HCMOS Logic Levels Reference)                                                                    | eferenced to V <sub>LS</sub> )                   | VSS                                                               | _   | V <sub>DD</sub> – 4.0                                             | V   |

| $V_{\mbox{LS}}$ Voltage for CMOS Mode (CMOS Logic Levels of $V_{\mbox{S}}$                                                        | S to V <sub>DD</sub> )                           | V <sub>DD</sub> – 0.5                                             | —   | V <sub>DD</sub>                                                   | V   |

| Mu/A Select Voltage                                                                                                               | Mu–Law Mode<br>Sign Magnitude Mode<br>A–Law Mode | V <sub>DD</sub> - 0.5<br>V <sub>AG</sub> - 0.5<br>V <sub>SS</sub> |     | V <sub>DD</sub><br>V <sub>AG</sub> + 0.5<br>V <sub>SS</sub> + 0.5 | V   |

| RSI Voltage for Reference Select Input (MC145506)                                                                                 | 3.78 V Mode<br>2.5 V Mode<br>3.15 V Mode         | V <sub>DD</sub> - 0.5<br>V <sub>AG</sub> - 0.5<br>V <sub>SS</sub> |     | V <sub>DD</sub><br>V <sub>AG</sub> + 0.5<br>V <sub>SS</sub> + 0.5 | V   |

| V <sub>ref</sub> Voltage for Internal or External Reference (MC145506 Only)<br>Internal Reference Mode<br>External Reference Mode |                                                  |                                                                   |     | V <sub>SS</sub> + 0.5<br>V <sub>DD</sub> – 1.0                    | V   |

| Analog Test Mode Selection Frequency, MS = CCI (MC145506 Only)<br>See Pin Description; Test Modes                                 |                                                  |                                                                   | 128 | —                                                                 | kHz |

# **SWITCHING CHARACTERISTICS** (V<sub>SS</sub> to V<sub>DD</sub> = 9.5 V to 12.6 V, $T_A = -40^{\circ}$ to 85°C, $C_L = 150$ pF, CMOS or HCMOS Mode)

| Characteris                                                                                                                                                   | tic                         | Symbol           | Min  | Тур                                 | Max        | Unit |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|------------------|------|-------------------------------------|------------|------|

| Output Rise Time<br>Output Fall Time                                                                                                                          | TDD                         | tTLH<br>tTHL     |      | 30<br>30                            | 80<br>80   | ns   |

| Input Rise Time TDE, TDE, TDE, TDE, TDE, TDE, TDE, TDE,                                                                                                       | TDC, RCE, RDC, DC, MSI, CCI | ttlh<br>tthl     |      | _                                   | 4 4        | μs   |

| Pulse Width TDE Low,                                                                                                                                          | TDC, RCE, RDC, DC, MSI, CCI | tw               | 100  | -                                   | -          | ns   |

| Data Clock Pulse Frequency                                                                                                                                    | TDC, RDC, DC                | fCL              | 64   | -                                   | 4096       | kHz  |

| CCI Clock Pulse Frequency (MSI = 8 kHz)<br>This Pin Will Accept One of These Discrete Clock Frequencies and<br>Will Compensate to Produce Internal Sequencing |                             |                  | <br> | 128<br>1536<br>1544<br>2048<br>2560 | <br>       | kHz  |

| Propagation Delay Time<br>TDE Rising to TDD Low Impedance                                                                                                     | HCMOS<br>CMOS               | 1 1 1            |      | 90<br>90                            | 180<br>150 | ns   |

| TDE Falling to TDD High Impedance                                                                                                                             | HCMOS<br>CMOS               | 1 1 4            | _    | _                                   | 55<br>40   |      |

| TDC Rising Edge to TDD Data, During                                                                                                                           | TDE High HCMOS<br>CMOS      | 1 10             | _    | 90<br>90                            | 180<br>150 |      |

| TDE Rising Edge to TDD Data, During                                                                                                                           | TDC High HCMOS<br>CMOS      | <sup>t</sup> P4  |      | 90<br>90                            | 180<br>150 |      |

| TDC Falling Edge to TDE Rising Edge Se                                                                                                                        | tup Time                    | tsu1             | 20   | -                                   | -          | ns   |

| TDE Rising Edge to TDC Falling Edge Se                                                                                                                        | tup Time                    | t <sub>su2</sub> | 100  | —                                   | _          | ns   |

| TDE Falling Edge to TDC Rising Edge to                                                                                                                        | Preserve the Next TDD Data  | t <sub>su8</sub> | 20   | —                                   | —          | ns   |

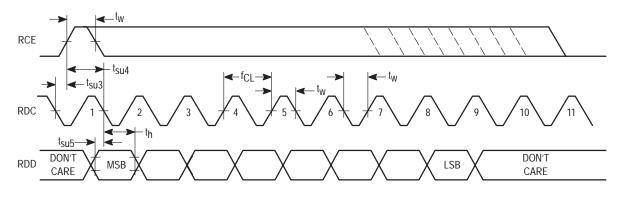

| RDC Falling Edge to RCE Rising Edge Se                                                                                                                        | etup Time                   | t <sub>su3</sub> | 20   | —                                   | —          | ns   |

| RCE Rising Edge to RDC Falling Edge Se                                                                                                                        | etup Time                   | t <sub>su4</sub> | 100  | —                                   | —          | ns   |

| RDD Valid to RDC Falling Edge Setup Tir                                                                                                                       | ne                          | t <sub>su5</sub> | 60   | —                                   | —          | ns   |

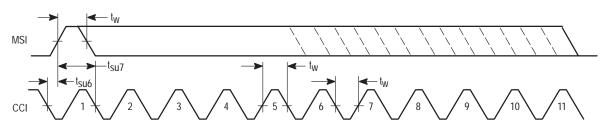

| CCI Falling Edge to MSI Rising Edge Set                                                                                                                       | up Time                     | t <sub>su6</sub> | 20   | —                                   | —          | ns   |

| MSI Rising Edge to CCI Falling Edge Set                                                                                                                       | up Time                     | tsu7             | 100  | —                                   | -          | ns   |

| RDD Hold Time from RDC Falling Edge                                                                                                                           |                             | th               | 100  | -                                   | -          | ns   |

| TDE, TDC, RCE, RDC, RDD, DC, MSI, C                                                                                                                           | CI Input Capacitance        |                  | —    | —                                   | 10         | pF   |

| TDE, TDC, RCE, RDC, RDD, DC, MSI, CCI Input Current                                                                                                           |                             |                  | —    | ±0.01                               | ±0.2       | μΑ   |

| TDD Capacitance During High Impedance                                                                                                                         | e (TDE Low)                 |                  | —    | 12                                  | 15         | pF   |

| TDD Input Current During High Impedance                                                                                                                       | e (TDE Low)                 |                  | _    | ±0.1                                | ±10.0      | μA   |

## **DEVICE DESCRIPTIONS**

A codec–filter is a device which is used for digitizing and reconstructing the human voice. These devices were developed primarily for the telephone network to facilitate voice switching and transmission. Once the voice is digitized, it may be switched by digital switching methods or transmitted long distance (T1, microwave, satellites, etc.) without degradation. The name codec is an acronym from "coder" for the A/D used to digitize voice, and "decoder" for the D/A used for reconstructing voice. A codec is a single device that does both the A/D and D/A conversions.

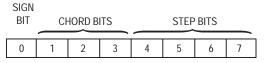

To digitize intelligible voice requires a signal to distortion of about 30 dB for a dynamic range of about 40 dB. This may be accomplished with a linear 13-bit A/D and D/A, but will far exceed the required signal to distortion at amplitudes greater than 40 dB below the peak amplitude. This excess performance is at the expense of data per sample. Two methods of data reduction are implemented by compressing the 13-bit linear scheme to companded 8-bit schemes. These companding schemes follow a segmented or "piecewise-linear" curve formatted as a sign bit, 3 chord bits, and 4 step bits. For a given chord, all 16 of the steps have the same voltage weighting. As the voltage of the analog input increases, the 4 step bits increment and carry to the 3 chord bits which increment. With the chord bits incremented, the step bits double their voltage weighting. This results in an effective resolution of 6 bits (sign + chord + 4 step bits) across a 42 dB dynamic range (7 chords above 0, by 6 dB per chord). There are two companding schemes used; Mu-255 Law specifically in North America, and A-Law specifically in Europe. These companding schemes are accepted world wide. The tables show the linear quantization levels to PCM words for the two companding schemes.

In a sampling environment, Nyquist theory says that to properly sample a continuous signal, it must be sampled at a frequency higher than twice the signal's highest frequency component. Voice contains spectral energy above 3 kHz, but its absence is not detrimental to intelligibility. To reduce the digital data rate, which is proportional to the sampling rate, a sample rate of 8 kHz was adopted, consistent with a bandwidth of 3 kHz. This sampling requires a low–pass filter to limit the high frequency energy above 3 kHz from distorting the inband signal. The telephone line is also subject to 50/60 Hz power line coupling which must be attenuated from the signal by a high–pass filter before the A/D converter.

The D/A process reconstructs a staircase version of the desired inband signal which has spectral images of the inband signal modulated about the sample frequency and its harmonics. These spectral images are called aliasing components which need to be attenuated to obtain the desired signal. The low-pass filter used to attenuate these aliasing components is typically called a reconstruction or smoothing filter.

The MC145500 series PCM codec–filters have the codec, both presampling and reconstruction filters, a precision voltage reference on chip, and require no external components. There are three distinct versions of the Motorola MC145500 series with HCMOS compatible outputs.

## MC145506

The MC145506 PCM codec-filter is the full-featured 22-pin device. It is intended for use in applications requiring

maximum flexibility. The MC145506 contains all the features of the MC145507 and MC145508. The MC145506 is intended for bit interleaved or byte interleaved applications with data clock frequencies which are nonstandard or time varying. One of the five standard frequencies (listed below) is applied to the CCI input, and the data clock inputs can be any frequency between 64 kHz and 4.096 MHz. The V<sub>ref</sub> pin allows for use of an external shared reference or selection of the internal reference. The RxG pin accommodates gain adjustments for the inverted analog output. All three pins of the input gainsetting operational amplifier are present which provide maximum flexibility for the analog interface.

## MC145507

The MC145507 PCM mono–circuit is intended for standard byte interleaved synchronous or asynchronous applications. TDC can be one of five discrete frequencies. These are 128 kHz (40% to 60% duty cycle), 1.536 MHz, 1.544 MHz, 2.048 MHz, or 2.56 MHz. (For other data clock frequencies, see MC145506 or MC145508.) The internal reference is set for 3.15 V peak full scale, and the full scale input level at Txl and output level at RxO is 6.3 Vp–p. This is the 3 dBm0 level of the PCM codec–filter. The +Tx and –Tx inputs provide maximum flexibility for analog interface. All other functions are described in the pin description.

## MC145508

The MC145508 PCM mono-circuit is intended for byte interleaved synchronous applications. The MC145508 has all the features of the MC145507 but internally connects TDC and RDC (see pin description) to the DC pin. One of the five standard frequencies (listed above) should be applied to CCI. The data clock input (DC) can be any frequency between 64 kHz and 4.069 MHz.

## **PIN DESCRIPTIONS**

# DIGITAL

## VLS

## Logic Level Select Input and HCMOS Digital Ground

V<sub>LS</sub> controls the logic levels and digital ground reference for all digital inputs and the digital output. These devices can operate with logic levels from full supply (V<sub>SS</sub> to V<sub>DD</sub>) or with TTL logic levels using V<sub>LS</sub> as digital ground. For V<sub>LS</sub> = V<sub>DD</sub>, all I/O is full supply (V<sub>SS</sub> to V<sub>DD</sub> swing) with CMOS switch points. For V<sub>SS</sub> < V<sub>LS</sub> < (V<sub>DD</sub> – 4 V), all inputs are TTL compatible with V<sub>LS</sub> being the digital ground while TDD outputs HCMOS levels from V<sub>LS</sub> to V<sub>DD</sub>. The pins controlled by V<sub>LS</sub> are inputs MSI, CCI, TDE, TDC, RCE, RDC, RDD, PDI, and output TDD.

# MSI

## **Master Synchronization Input**

MSI is used for determining the sample rate of the transmit side and as a time base for selecting the internal prescale divider for the convert clock input (CCI) pin. The MSI pin should be tied to an 8 kHz clock which may be a frame sync or system sync signal. MSI has no relation to transmit or receive data timing, except for determining the internal transmit strobe as described under the TDE pin description. MSI should be derived from the transmit timing in asynchronous applications. In many applications, MSI can be tied to TDE. (MSI is tied internally to TDE in the MC145507/08.)

## CCI

## **Convert Clock Input**

CCI is designed to accept five discrete clock frequencies. These are 128 kHz, 1.536 MHz, 1.544 MHz, 2.048 MHz, or 2.56 MHz. The frequency at this input is compared with MSI and prescale divided to produce the internal sequencing clock at 128 kHz (or 16 times the sampling rate). The duty cycle of CCI is dictated by the minimum pulse width except for 128 kHz, which is used directly for internal sequencing and must have a 40% to 60% duty cycle. In asynchronous applications, CCI should be derived from transmit timing. (CCI is tied internally to TDC in the MC145507.)

## TDC

## **Transmit Data Clock Input**

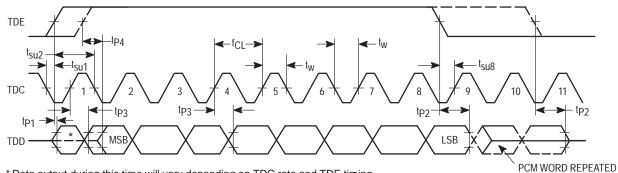

TDC can be any frequency from 64 kHz to 4.096 MHz, and is often tied to CCI if the data rate is equal to one of the five discrete frequencies. This clock is the shift clock for the transmit shift register and its rising edges produce successive data bits at TDD. TDE should be derived from this clock. (TDC and RDC are tied together internally in the MC145508 and are called DC.)

## TDE

## **Transmit Data Enable Input**

TDE serves three major functions. The first TDE rising edge following an MSI rising edge, generates the internal transmit strobe which initiates an A/D conversion. The internal transmit strobe also transfers a new PCM data word into the transmit shift register (sign bit first) ready to be output at TDD. The TDE pin is the high-impedance control for the transmit digital data (TDD) output. As long as this pin is high, the TDD output stays low impedance. This pin also enables the output shift register for clocking out the 8-bit serial PCM word. The logical AND of the TDE pin with the TDC pin, clocks out a new data bit at TDD. TDE should be held high for eight consecutive TDC cycles to clock out a complete PCM word for byte interleaved applications. The transmit shift register feeds back on itself to allow multiple reads of the transmit data. If the PCM word is clocked out once per frame in a byte interleaved system, the MSI pin function is transparent and may be connected to TDE.

The TDE pin may be cycled during a PCM word for bit interleaved applications. TDE controls both the high–impedance state of the TDD output and the internal shift clock. TDE must fall before TDC rises ( $t_{SU8}$ ) to ensure integrity of the next data bit. There must be at least two TDC falling edges between the last TDE rising edge of one frame and the first TDE rising edge of the next frame. MSI must be available separate from TDE for bit interleaved applications.

# TDD

## **Transmit Digital Data Output**

The output levels at this pin are controlled by the V<sub>LS</sub> pin. For V<sub>LS</sub> connected to V<sub>DD</sub>, the output levels are from V<sub>SS</sub> to V<sub>DD</sub>. For a voltage of V<sub>LS</sub> between V<sub>DD</sub>-4 V and V<sub>SS</sub>, the output levels are HCMOS compatible with V<sub>LS</sub> being the digital ground supply and V<sub>DD</sub> being the positive logic supply. The TDD pin is a three–state output controlled by the TDE pin. The timing of this pin is controlled by TDC and TDE. The data format (Mu–Law, A–Law, or sign magnitude) is controlled by the Mu/A pin.

## RDC

## **Receive Data Clock Input**

RDC can be any frequency from 64 kHz to 4.096 MHz. This pin is often tied to the TDC pin for applications that can use a common clock for both transmit and receive data transfers. The receive shift register is controlled by the receive clock enable (RCE) pin to clock data into the receive digital data (RDD) pin on falling RDC edges. These three signals can be asynchronous with all other digital pins. The RDC input is internally tied to the TDC input on the MC145508 and called DC.

# RCE

#### **Receive Clock Enable Input**

The rising edge of RCE should identify the sign bit of a receive PCM word on RDD. The next falling edge of RDC, after a rising RCE, loads the first bit of the PCM word into the receive register. The next seven falling edges enter the remainder of the PCM word. On the ninth rising edge, the receive PCM word is transferred to the receive buffer register and the A/D sequence is interrupted to commence the decode process. In asynchronous applications with an 8 kHz transmit sample rate, the receive sample rate should be between 7.5 kHz and 8.5 kHz. Two receive PCM words may be decoded and analog summed each transmit frame to allow on–chip conferencing. The two PCM words should be clocked in as two single PCM words, a minimum of 31.25 µs apart, with a receive data clock of 512 kHz or faster.

# RDD

## **Receive Digital Data Input**

RDD is the receive digital data input. The timing for this pin is controlled by RDC and RCE. The data format is determined by the Mu/A pin.

# Mu/A

## Mu/A Select

This pin selects the companding law and the data format at TDD and RDD.

- Mu/A = V<sub>DD</sub>; Mu–255 Companding D3 Data Format with Zero Code Suppress

- Mu/A = V<sub>AG</sub>; Mu–255 Companding with Sign Magnitude Data Format

- Mu/A = V<sub>SS</sub>; A–Law Companding with CCITT Data Format Bit Inversions

| Code         | Sign/<br>Magnitude |      | Mu–Law |      | A–Law<br>(CCITT) |      |

|--------------|--------------------|------|--------|------|------------------|------|

| + Full Scale | 1111               | 1111 | 1000   | 0000 | 1010             | 1010 |

| + Zero       | 1000               | 0000 | 1111   | 1111 | 1101             | 0101 |

| – Zero       | 0000               | 0000 | 0111   | 1111 | 0101             | 0101 |

| – Full Scale | 0111               | 1111 | 0000   | 0010 | 0010             | 1010 |

NOTE: Starting from sign magnitude, to change format: To Mu–Law —

MSB is unchanged (sign)

Invert remaining 7 bits

If code is 0000 0000, change to 0000 0010 (for zero code suppression)

To A–Law —

MSB is unchanged (sign) Invert odd numbered bits Ignore zero code suppression

# PDI

# **Power Down Input**

The power down input disables the bias circuitry and gates off all clock inputs. This puts the V<sub>AG</sub>, TxI, RxO, RxO, and TDD outputs into a high–impedance state. The power dissipation is reduced to 0.1 mW when  $\overline{PDI}$  is a low logic level. The circuit operates normally with  $\overline{PDI} = V_{DD}$  or with a logic high as defined by connection at V<sub>LS</sub>. TDD will not come out of high impedance for two MSI cycles after  $\overline{PDI}$  goes high.

# DC

# Data Clock Input

In the MC145508, TDC and RDC are internally connected to DCLK.

## ANALOG

# VAG

# Analog Ground Input/Output Pin

VAG is the analog ground power supply input/output. All analog signals into and out of the device use this as their ground reference. Each version of the MC145500 PCM codec-filter family can provide its own analog ground supply internally. The dc voltage of this internal supply is 6% positive of the midway between V<sub>DD</sub> and V<sub>SS</sub>. This supply can sink more than 8 mA but has a current source limited to 400 µA. The output of this supply is internally connected to the analog ground input of the part. The node where this supply and the analog ground are connected is brought out to the VAG pin. In symmetric dual supply systems (±5, ±6, etc.), VAG may be externally tied to the system analog ground supply. When RxO or RxO drive low-impedance loads tied to VAG, a pullup resistor to V and will be required to boost the source current capability if VAG is not tied to the supply ground. All analog signals for the part are referenced to VAG, including noise; therefore, decoupling capacitors (0.1 µF) should be used from VDD to VAG and VSS to VAG.

# Vref

# Positive Voltage Reference Input (MC145506 Only)

The V<sub>ref</sub> pin allows an external reference voltage to be used for the A/D and D/A conversions. If V<sub>ref</sub> is tied to V<sub>SS</sub>, the internal reference is selected. If V<sub>ref</sub> > V<sub>AG</sub>, then the external mode is selected and the voltage applied to V<sub>ref</sub> is used for generating the internal converter reference voltage. In either internal or external reference mode, the actual voltage used for conversion is multiplied by the ratio selected by the RSI pin. The RSI pin circuitry is explained under its pin description below. Both the internal and external references are inverted within the PCM codec–filter for negative input voltages such that only one reference is required.

**External Mode** — In the external reference mode (V<sub>ref</sub> > V<sub>AG</sub>), a 2.5 V reference like the MC1403 may be connected from V<sub>ref</sub> to V<sub>AG</sub>. A single external reference may be shared by tying together a number of V<sub>ref</sub> pins and V<sub>AG</sub> pins from different codec–filters. In special applications, the external reference voltage may be between 0.5 and 5 V. However, the

reference voltage gain selection circuitry associated with RSI must be considered to arrive at the desired codec-filter gain.

**Internal Mode** — In the internal reference mode ( $V_{ref} = V_{SS}$ ), an internal 2.5 V reference supplies the reference voltage for the RSI circuitry. The  $V_{ref}$  pin is functionally connected to  $V_{SS}$  for the MC145507 and MC145508 pinouts.

# RSI

# Reference Select Input (MC145506 Only)

The RSI input allows the selection of three different overload or full-scale A/D and D/A converter reference voltages independent of the internal or external reference mode. The RSI pin is a digital input that senses three different logic states: V<sub>SS</sub>, V<sub>AG</sub>, and V<sub>DD</sub>. For RSI = V<sub>AG</sub>, the reference voltage is used directly for the converters. The internal reference is 2.5 V. For RSI = VSS, the reference voltage is multiplied by the ratio of 1.26, which results in an internal converter reference of 3.15 V. For RSI =  $V_{DD}$ , the reference voltage is multiplied by 1.51, which results in an internal converter reference of 3.78 V. The device requires a minimum of 1.0 V of headroom between the internal converter reference to VDD. VSS has this same absolute valued minimum, also measured from the VAG pin. The various modes of operation are summarized in Table 2. The RSI pin is functionally connected to VSS for the MC145507 and MC145508 pinouts.

# RxO, RxO

# **Receive Analog Outputs**

These two complimentary outputs are generated from the output of the receive filter. They are equal in magnitude and out of phase. The maximum signal output of each is equal to the maximum peak–to–peak signal described with the reference. If a 3.15 V reference is used with RSI tied to VAG and a 3 dBm0 sine wave is decoded, the RxO output will be a 6.3 V peak–to–peak signal. RxO will also have an inverted signal output of 6.3 V peak–to–peak. External loads may be connected from RxO to RxO for a 6 dB push–pull signal gain or from either RxO or RxO to 9 dBm. With RSI tied to V<sub>DD</sub>, each output will drive 900  $\Omega$  to 9 dBm.

# RxG

## Receive Output Gain Adjust (MC145506 Only)

The purpose of the RxG pin is to allow external gain adjustment for the RxO pin. If RxG is left open, then the output signal at RxO will be inverted and output at RxO. Thus, the push-pull gain to a load from RxO to RxO is two times the output level at RxO. If external resistors are applied from RxO to RxG (RI) and from RxG to  $\overline{RxO}$  (RG), the gain of  $\overline{RxO}$  can be set differently from inverting unity. These resistors should be in the range of 10 k $\Omega$ . The RxO output level is unchanged by the resistors and the RxO gain is approximately equal to minus RG/RI. The actual gain is determined by taking into account the internal resistors which will be in parallel to these external resistors. The internal resistors have a large tolerance, but they match each other very closely. This matching tends to minimize the effects of their tolerance on external gain configurations. The circuit for RxG and RxO is shown in the Block Diagram.

# Txl

## **Transmit Analog Input**

Txl is the input to the transmit filter. It is also the output of the transmit gain amplifier. The Txl input has an internal gain

of 1.0, such that a 3 dBm0 signal at TxI corresponds to the peak converter reference voltage as described in the V<sub>ref</sub> and RSI pin descriptions. For a 3.15 V reference, the 3 dBm0 input should be 6.3 V peak–to–peak.

# +Tx / –Tx

#### Positive Tx Amplifier Input Negative Tx Amplifier Input

The Txl pin is the input to the transmit band–pass filter. If +Tx or -Tx is available, then there is an internal amplifier preceding the filter whose pins are +Tx, -Tx, and Txl. These pins allow access to the amplifier terminals to tailor the input gain with external resistors. The resistors should be in the range of 10 k $\Omega$ .

## POWER SUPPLIES

# VDD

#### Most Positive Power Supply

V<sub>DD</sub> is typically 5 V to 12 V.

# Vss

## Most Negative Power Supply

V<sub>SS</sub> is typically 10 V to 12 V negative of V<sub>DD</sub>.

For a  $\pm$ 5 V dual–supply system, the typical power supply configuration is V<sub>DD</sub> = 5 V, V<sub>SS</sub> = –5 V, V<sub>LS</sub> = 0 V (digital

ground accommodating TTL logic levels), and  $V_{AG} = 0 V$  being tied to system analog ground.

For single–supply applications, typical power supply configurations include:

$$V_{SS} = 0 V$$

V<sub>AG</sub> generates a mid supply voltage for referencing all analog signals.

$V_{LS}$  controls the logic levels. This pin should be connected to  $V_{DD}$  for CMOS logic levels from  $V_{SS}$  to  $V_{DD}$ . This pin should be connected to digital ground for true TTL logic input levels referenced to  $V_{LS}$ , with HCMOS output levels from  $V_{LS}$  to  $V_{DD}$ .

## **TESTING CONSIDERATIONS (MC145506 ONLY)**

An analog test mode is activated by connecting MSI and CCI to 128 kHz. In this mode, the input of the A/D (the output of the Tx filter) is available at the  $\overline{PDI}$  pin. This input is direct coupled to the A/D side of the codec. The A/D is a differential design. This results in the gain of this input being effectively attenuated by half. If monitored with a high–impedance buffer, the output of the Tx low–pass filter can also be measured at the  $\overline{PDI}$  pin. This test mode allows independent evaluation of the transmit low–pass filter and A/D side of the codec. The transmit and receive channels of these devices are tested with the codec–filter fully functional.

\* To define RDD when TDD is high Z.

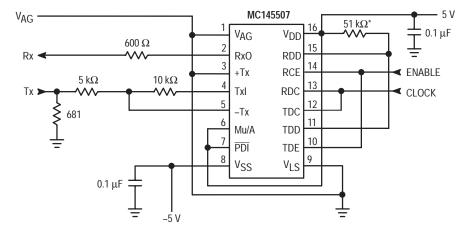

#### Figure 1. Test Circuit

| RSI*<br>Pin Level | V <sub>ref</sub> *<br>Pin Level    | Peak–to–Peak Overload Voltage<br>(TxI, RxO) |

|-------------------|------------------------------------|---------------------------------------------|

| V <sub>DD</sub>   | V <sub>SS</sub>                    | 7.56 Vp–p                                   |

| V <sub>DD</sub>   | V <sub>AG</sub> + V <sub>EXT</sub> | (3.02 x V <sub>EXT</sub> ) Vp–p             |

| V <sub>AG</sub>   | V <sub>SS</sub>                    | 5 Vp–p                                      |

| V <sub>AG</sub>   | V <sub>AG</sub> + V <sub>EXT</sub> | (2 x V <sub>EXT</sub> ) Vp–p                |

| V <sub>SS</sub>   | V <sub>SS</sub>                    | 6.3 Vp–p                                    |

| V <sub>SS</sub>   | V <sub>AG</sub> + V <sub>EXT</sub> | (2.52 x V <sub>EXT</sub> ) Vp–p             |

Table 1. MC145506 Options Available by Pin Selection

\* On MC145507/08, RSI and  $V_{ref}$  are tied internally to  $V_{SS}$ .

| Pin<br>Programmed<br>Logic<br>Level | Mu/A                                                                         | RSI<br>Peak<br>Overload<br>Voltage | VLS                                                                                              |

|-------------------------------------|------------------------------------------------------------------------------|------------------------------------|--------------------------------------------------------------------------------------------------|

| VDD                                 | Mu–Law Companding Curve and D3/D4 Digital<br>Formats with Zero Code Suppress | 3.78                               | CMOS<br>Logic Levels                                                                             |

| VAG                                 | Mu–Law Companding Curve and Sign Magnitude<br>Data Format                    | 2.50                               | TTL Input Levels, V <sub>AG</sub> Up;<br>HCMOS Output Levels, V <sub>AG</sub> to V <sub>DD</sub> |

| VSS                                 | A–Law Companding Curve and CCITT Digital<br>Format                           | 3.15                               | TTL Levels, V <sub>SS</sub> Up;<br>HCMOS Output Levels, V <sub>SS</sub> to V <sub>DD</sub>       |

Table 2. Summary of Operation Conditions User Programmed Through Pins  $V_{DD}$ ,  $V_{AG}$ , and  $V_{SS}$

\* Data output during this time will vary depending on TDC rate and TDE timing.

Figure 2. Transmit Timing Diagram

Figure 3. Receive Timing Diagram

Figure 4. MSI/CCI Timing Diagram

Figure 5. MC145506 Gain vs Level Mu-Law Transmit

Figure 6. MC145506 Gain vs Level Mu–Law Receive

Figure 9. MC145506 Gain vs Level A–Law Transmit F

Figure 10. MC145506 Gain vs Level A-Law Receive

Figure 21. MC145506 Low–Pass Filter Response Receive

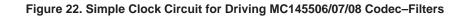

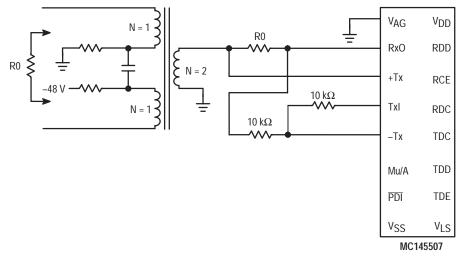

(a) Simplified Transformer Hybrid Using MC145507

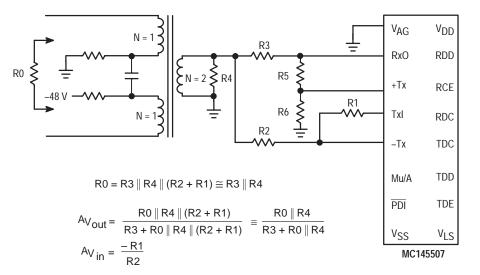

NOTE: Hybrid balance by R5 and R6 to equate the RxO signal gain at Txl through the inverting and non–inverting signal paths.

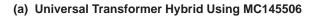

#### (b) Universal Transformer Hybrid Using MC145507

#### Figure 23. Hybrid Interfaces to the MC145507 PCM Codec-Filter Mono-Circuit

(b) Single-Ended Hybrid Using MC145506

Figure 24. Hybrid Interfaces to the MC145506 PCM Codec-Filter Mono-Circuit

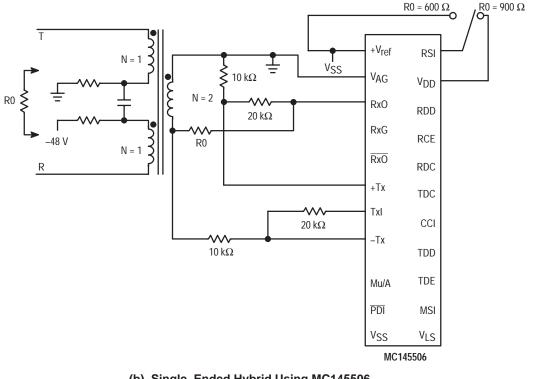

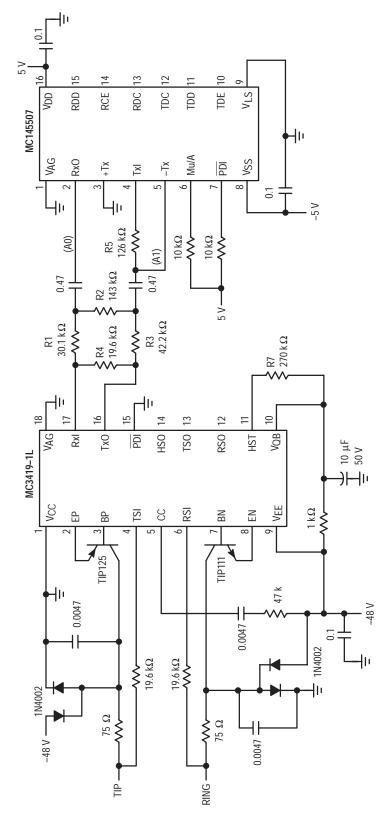

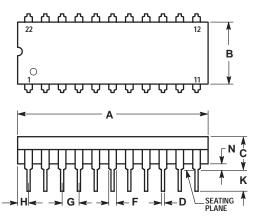

Figure 25. A Complete Single Party Channel Unit Using MC3419 SLIC and MC145507 PCM Mono–Circuit

|        |          |                         | Normalized<br>Encode    | Encode Digital Code |       |       |       |      | Normalized |      |      |        |

|--------|----------|-------------------------|-------------------------|---------------------|-------|-------|-------|------|------------|------|------|--------|

| Chord  | Number   | Step                    | Decision                | 1                   | 2     | 3     | 4     | 5    | 6          | 7    | 8    | Decode |

| Number | of Steps | Size                    | Levels                  | Sign                | Chord | Chord | Chord | Step | Step       | Step | Step | Levels |

|        |          |                         | - 8159 —                |                     |       |       |       |      |            |      |      |        |

|        |          |                         |                         | 1                   | 0     | 0     | 0     | 0    | 0          | 0    | 0    | 8031   |

| 8      | 16       | 256                     | 7903 —<br>:             |                     |       |       | :     |      |            |      |      | ÷      |

|        |          |                         | 4319 —<br>- 4063 —      | 1                   | 0     | 0     | 0     | 1    | 1          | 1    | 1    | 4191   |

| 7      | 16       | 128                     | - 4063 —<br>:<br>2143 — |                     |       |       | :     |      |            |      |      |        |

| 7      | 10       | 120                     | – 2015 –                | 1                   | 0     | 0     | 1     | 1    | 1          | 1    | 1    | 2079   |

| 6      | 6 16 64  | - 2013 -<br>:<br>1055 - |                         |                     |       | ÷     |       |      |            |      |      |        |

| 0      |          | 64 1055 —<br>991 —      | 1                       | 0                   | 1     | 0     | 1     | 1    | 1          | 1    | 1023 |        |

| 5      | 5 16 32  |                         | - 991 -<br>:<br>511 -   |                     | ÷     |       |       |      |            |      |      |        |

| 5      | 10       | 52                      | - 479 -                 | 1                   | 0     | 1     | 1     | 1    | 1          | 1    | 1    | 495    |

| 4      | 16       | 16                      | :<br>239 —              |                     |       |       |       |      |            |      |      |        |

| 4      | 10       | 10                      | - 223 -                 | 1                   | 1     | 0     | 0     | 1    | 1          | 1    | 1    | 231    |

| 3      | 16       | 8                       | - 223 —<br>:<br>103 —   |                     |       |       |       |      |            |      |      | :      |

| 5      | 10       | 0                       |                         | 1                   | 1     | 0     | 1     | 1    | 1          | 1    | 1    | 99     |

| 2      | 2 16 4   |                         | 95 —<br>:<br>4 35 —     |                     |       |       | :     |      |            |      |      | :      |

| 2      | 10       | 4                       | - 31 -                  | 1                   | 1     | 1     | 0     | 1    | 1          | 1    | 1    | 33     |

| 1      | 15       | 2                       | - 31 —<br>:<br>3 —      |                     |       |       | :     |      |            |      |      | :      |

| I      | 10       |                         | - 1 -                   | 1                   | 1     | 1     | 1     | 1    | 1          | 1    | 0    | 2      |

|        | 1        | 1                       | - 1 -<br>- 0 -          | 1                   | 1     | 1     | 1     | 1    | 1          | 1    | 1    | 0      |

| NOTES: |          |                         | 0                       |                     |       |       |       |      |            |      |      |        |

Table 3. Mu-Law Encode-Decode Characteristics

NOTES:

1. Characteristics are symmetrical about analog zero with sign bit = 0 for negative analog values.

2. Digital code includes inversion of all magnitude bits.

|        |          |      | Normalized<br>Encode    | Digital Code |       |       |       | Normalized |      |      |      |        |

|--------|----------|------|-------------------------|--------------|-------|-------|-------|------------|------|------|------|--------|

| Chord  | Number   | Step | Decision                | 1            | 2     | 3     | 4     | 5          | 6    | 7    | 8    | Decode |

| Number | of Steps | Size | Levels                  | Sign         | Chord | Chord | Chord | Step       | Step | Step | Step | Levels |

|        |          |      | - 4096 -                |              |       |       |       |            |      |      |      |        |

|        |          |      | 3968 —                  | 1            | 0     | 1     | 0     | 1          | 0    | 1    | 0    | 4032   |

| 7      | 16       | 128  | 3300<br>:<br>2176 —     |              |       |       |       |            |      |      |      | :      |

|        |          |      |                         | 1            | 0     | 1     | 0     | 0          | 1    | 0    | 1    | 2112   |

| 6      | 16       | 64   | - 2048 -<br>:<br>1088 - |              |       |       |       |            |      |      |      | :      |

| 0      | 10       | 04   | - 1024 -                | 1            | 0     | 1     | 1     | 0          | 1    | 0    | 1    | 1056   |

| 5      | 16       | 32   | - 1024 -<br>:<br>544 -  | :            |       |       |       |            |      | ÷    |      |        |

| 5      | 10       | 32   | - 512 -                 | 1            | 0     | 0     | 0     | 0          | 1    | 0    | 1    | 528    |

| 4      | 16       | 16   | - 512 -<br>:<br>272 -   |              |       |       |       | :          |      |      |      | :      |

| 4      | 10       | 10   | - 256 -                 | 1            | 0     | 0     | 1     | 0          | 1    | 0    | 1    | 264    |

| 3      | 16       | 8    | - 256 -<br>:<br>136 -   |              |       |       |       | :          |      |      |      | :      |

| 5      | 10       | 0    |                         | 1            | 1     | 1     | 0     | 0          | 1    | 0    | 1    | 132    |

| 2      |          |      | 4 68 -                  |              |       |       |       | :          |      |      |      | ÷      |

| 2 16 4 | 4        | 1    |                         | 1            | 1     | 1     | 0     | 1          | 0    | 1    | 66   |        |

| 1      |          |      |                         |              |       |       | :     |            |      |      | :    |        |

|        | 32       | 2    | 2 -                     | 1            | 1     | 0     | 1     | 0          | 1    | 0    | 1    | 1      |

|        |          |      | - 0 -                   |              |       |       |       |            |      |      |      |        |

Table 4. A-Law Encode-Decode Characteristics

NOTES:

1. Characteristics are symmetrical about analog zero with sign bit = 0 for negative analog values.

2. Digital code includes alternate bit inversion, as specified by CCITT.

# PACKAGE DIMENSIONS

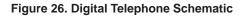

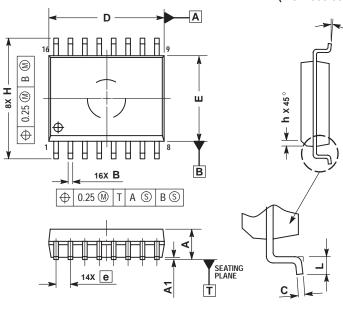

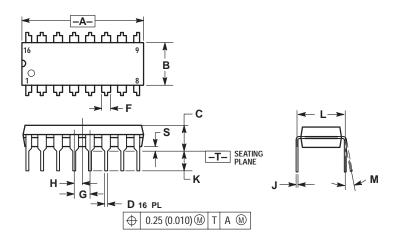

**DW SUFFIX** SOG PACKAGE CASE 751-03 (MC145507/08)

A

**P SUFFIX** PLASTIC DIP CASE 648-08 (MC145507/08)

NOTES:

- 1. DIMENSIONS ARE IN MILLIMETERS. 2. INTERPRET DIMENSIONS AND TOLERANCES

- PER ASME Y14.5M, 1994. DIMENSIONS D AND E DO NOT INLCUDE MOLD 3.

- PROTRUSION. MAXIMUM MOLD PROTRUSION 0.15 PER SIDE. 4.

- 5 DIMENSION B DOES NOT INCLUDE DAMBAR PROTRUSION. ALLOWABLE DAMBAR PROTRUSION. ALLOWADLE DAVIDAR PROTRUSION SHALL BE 0.13 TOTAL IN EXCESS OF THE B DIMENSION AT MAXIMUM MATERIAL CONDITION.

|     | MILLIMETERS |       |  |  |  |  |

|-----|-------------|-------|--|--|--|--|

| DIM | MIN         | MAX   |  |  |  |  |

| Α   | 2.35        | 2.65  |  |  |  |  |

| A1  | 0.10        | 0.25  |  |  |  |  |

| В   | 0.35        | 0.49  |  |  |  |  |

| С   | 0.23        | 0.32  |  |  |  |  |

| D   | 10.15       | 10.45 |  |  |  |  |

| Ε   | 7.40        | 7.60  |  |  |  |  |

| е   | 1.27        | BSC   |  |  |  |  |

| Н   | 10.05       | 10.55 |  |  |  |  |

| h   | 0.25        | 0.75  |  |  |  |  |

| L   | 0.50        | 0.90  |  |  |  |  |

| θ   | 0 °         | 7 °   |  |  |  |  |

|     |             |       |  |  |  |  |

NOTES:

DIMENSIONING AND TOLERANCING PER ANSI Y14.5M, 1982.

- Y 14.5M, 1982. CONTROLLING DIMENSION: INCH. DIMENSION L TO CENTER OF LEADS WHEN 2

- 3.

- FORMED PARALLEL. 4. DIMENSION B DOES NOT INCLUDE MOLD FLASH. 5. ROUNDED CORNERS OPTIONAL.

|     | INC   | HES   | MILLIM | ETERS |  |  |

|-----|-------|-------|--------|-------|--|--|

| DIM | MIN   | MAX   | MIN    | MAX   |  |  |

| Α   | 0.740 | 0.770 | 18.80  | 19.55 |  |  |

| В   | 0.250 | 0.270 | 6.35   | 6.85  |  |  |

| С   | 0.145 | 0.175 | 3.69   | 4.44  |  |  |