Rev. 2.0, 8/2006

# Switching Power Supply with Linear Regulators

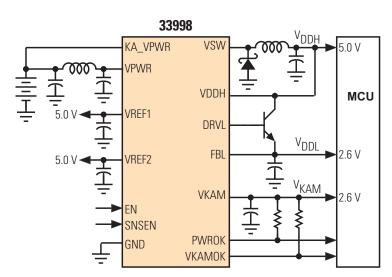

The 33998 is a medium-power, multi-output power supply integrated circuit that is capable of operating over a wide input voltage range, from 6.0 V up to 26.5 V with 40 V transient capability. It incorporates a sensorless current mode control step-down switching controller regulating directly to 5.0 V. The 2.6 V linear regulator uses an external pass transistor to reduce the 33998 power dissipation. The 33998 also provides a 2.6 V linear standby regulator and two 5.0 V sensor supply outputs protected by internal low-resistance LDMOS transistors.

There are two separate enable pins for the main and sensor supply outputs and standard supervisory functions such as resets with power-up reset delay.

The 33998 provides proper power supply sequencing for advanced microprocessor architectures such as the MPC5xx and 683xx microprocessor families.

#### **Features**

- Operating Voltage Range 6.0 V up to 26.5 V (40 V transient)

- Step-Down Switching Regulator Output V<sub>DDH</sub> = 5.0 V @ 1400 mA (total)

- Linear Regulator with External Pass Transistor V<sub>DDL</sub> = 2.6 V @ 400 mA

- Low-Power Standby Linear Regulator  $V_{KAM} = 2.6 V @ 10 mA$

- Two 5.0 V @ 200 mA (typical) Sensor Supplies V<sub>REF</sub> Protected Against Short-to-Battery and Short-to-Ground with Retry Capability

- Undervoltage Shutdown on the V<sub>DDL</sub>, V<sub>DDH</sub> Outputs with Retry Capability

- · Reset Signals

- · Power-Up Delay

- Enable Pins for Main Supplies (EN) and Sensor Supplies (SNSEN)

- Power Sequencing for Advanced Microprocessor Architectures

- Pb-Free Packaging Designated by Suffix Code EG

# 33998

#### **SWITCHING REGULATOR**

DW SUFFIX EG SUFFIX (PB-FREE) 98ASB42344B 24-PIN SOICW

| ORDERING INFORMATION |                                        |           |  |  |  |  |

|----------------------|----------------------------------------|-----------|--|--|--|--|

| Device               | Temperature<br>Range (T <sub>A</sub> ) | Package   |  |  |  |  |

| MC33998DW/R2         | -40°C to 125°C                         | 24 SOICW  |  |  |  |  |

| MCZ33998EG/R2        | -40 C to 125 C                         | 24 301000 |  |  |  |  |

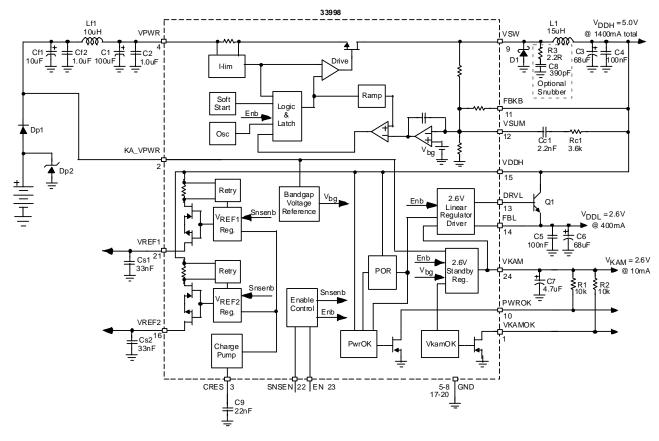

Figure 1. 33998 Simplified Application Diagram

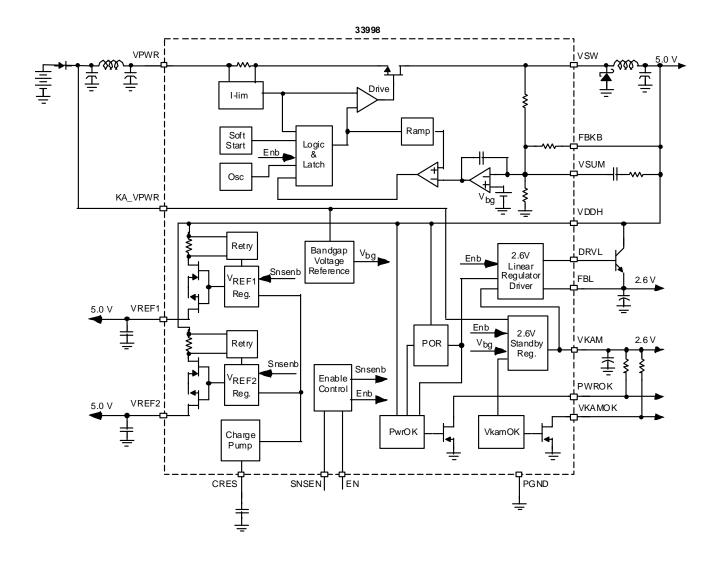

# INTERNAL BLOCK DIAGRAM

Figure 2. 33998 Simplified Internal Block Diagram

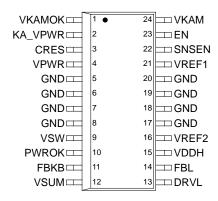

# **PIN CONNECTIONS**

Figure 3. 33998 Pin Connections

**Table 1. Pin Definitions**

| Pin Number | Pin<br>Name | Definition                                                                                                                                                                                                                                                          |

|------------|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1          | VKAMOK      | Keep-Alive Output Monitoring. This pin is an "open-drain" output that will be used with a discrete pull-up resistor to VKAM. When the supply voltage to the 33998 is disconnected or lost, the VKAMOK signal goes low.                                              |

| 2          | KA_VPWR     | Keep Alive Power Supply Pin. This supply pin is used in modules that have both direct battery connections and ignition switch activated connections.                                                                                                                |

| 3          | CRES        | Reservoir Capacitor. This pin is tied to an external "reservoir capacitor" for the internal charge pump.                                                                                                                                                            |

| 4          | VPWR        | Power Supply Pin. Main power input to the IC. This pin is directly connected to the switching regulator power MOSFET. In automotive applications this pin must be protected against reverse battery conditions by an external diode.                                |

| 5-8        | GND         | Ground of the integrated circuit.                                                                                                                                                                                                                                   |

| 9          | VSW         | Internal P-Channel Power MOSFET Drain. VSW is the "switching node" of the voltage buck converter. This pin is connected to the VPWR pin by an integrated p-channel MOSFET.                                                                                          |

| 10         | PWROK       | Power OK Reset Pin. This pin is an "open-drain" output that will be used with a discrete pull-up resistor to VKAM, VDDH, or VDDL. When either VDDH or VDDL output voltage goes out of the regulation limits this pin is pulled down.                                |

| 11         | FBKB        | Step-Down Switching Regulator Feedback Pin. The FBKB pin is the VDDH feedback signal for the switching regulator.                                                                                                                                                   |

| 12         | VSUM        | Error Amplifier "Summing Node". The VSUM pin is connected to the inverting input of the error amplifier. This node is also the "common" point of the integrated feedback resistor divider.                                                                          |

| 13         | DRVL        | Drive for VDDL (2.6 V) Regulator. The DRVL pin drives the base of an external NPN pass transistor for the VDDL linear post regulator. The collector of the VDDL pass transistor is connected to VDDH. An example of a suitable pass transistor is BCP68.            |

| 14         | FBL         | Feedback for VDDL (2.6 V) Regulator. The FBL pin is the voltage feedback sense signal from the VDDL (2.6 V) linear post regulator.                                                                                                                                  |

| 15         | VDDH        | VDDH is an input supply pin providing power for the buffered sensor supplies and the drive circuitry for the 2.6 V linear power regulator. The VDDH pin is supplied from the switching regulator output, capable of providing 5.0 V @ 1400 mA total output current. |

| 16         | VREF2       | Sensor Supply #2 Output. The VREF2 pin is sensor supply output #2.                                                                                                                                                                                                  |

| 17–20      | GND         | Ground of the integrated circuit.                                                                                                                                                                                                                                   |

| 21         | VREF1       | Sensor Supply #1 Output. The VREF1 pin is sensor supply output #1.                                                                                                                                                                                                  |

#### 33998

# Table 1. Pin Definitions (continued)

| Pin Number | Pin<br>Name | Definition                                                                                                                                                                          |

|------------|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 22         | SNSEN       | Sensor Supply Enable Input. The SNSEN pin is an input, which enables the VREF1 and VREF2 supplies. It allows the control module hardware/software to shut down the sensor supplies. |

| 23         | EN          | Enable Input. The EN pin is an input, which enables the main switching regulator and all other functions. When this pin is low, the power supply is in a low quiescent state.       |

| 24         | VKAM        | Keep-Alive (standby) 2.6 V Regulator Output. This is a 2.6 V low quiescent, low dropout regulator for Keep Alive memory.                                                            |

# **ELECTRICAL CHARACTERISTICS**

#### **MAXIMUM RATINGS**

## **Table 2. Maximum Ratings**

All voltages are with respect to ground unless otherwise noted.

| Rating                                                                  | Symbol              | Value       | Unit |

|-------------------------------------------------------------------------|---------------------|-------------|------|

| Main Supply Voltage                                                     | V <sub>PWR</sub>    | -0.3 to 45  | V    |

| Keep-Alive Supply Voltage                                               | KA_V <sub>PWR</sub> | -0.3 to 45  | V    |

| Switching Node                                                          | V <sub>SW</sub>     | -0.5 to 45  | V    |

| 5.0 V Input Power                                                       | $V_{DDH}$           | -0.3 to 6.0 | V    |

| Sensor Supply                                                           | V <sub>REF1</sub>   | -0.3 to 18  | V    |

|                                                                         | $V_{REF2}$          | -0.3 to 18  |      |

| Keep-Alive Supply Voltage                                               | $V_{KAM}$           | -0.3 to 6.0 | V    |

| Maximum Voltage at Logic I/O Pins                                       | EN                  | -0.3 to 6.0 | V    |

|                                                                         | SNSEN               | -0.3 to 6.0 |      |

|                                                                         | PWROK               | -0.3 to 6.0 |      |

|                                                                         | VKAMOK              | -0.3 to 6.0 |      |

| Charge Pump Reservoir Capacitor Voltage                                 | C <sub>RES</sub>    | -0.3 to 18  | V    |

| Error Amplifier Summing Node                                            | V <sub>SUM</sub>    | -0.3 to 6.0 | V    |

| Switching Regulator Output Feedback                                     | FBKB                | -0.3 to 6.0 | V    |

| VDDL Base Drive                                                         | DRVL                | -0.3 to 6.0 | V    |

| VDDL Feedback                                                           | FBL                 | -0.3 to 6.0 | V    |

| ESD Voltage                                                             |                     |             | V    |

| Human Body Model (all pins) (1)                                         | V <sub>ESD1</sub>   | ±500        |      |

| Machine Model (all pins) (1)                                            | V <sub>ESD2</sub>   | ±100        |      |

| Power Dissipation (T <sub>A</sub> = 25°C) <sup>(2)</sup>                | P <sub>D</sub>      | 800         | mW   |

| Thermal Resistance, Junction to Ambient <sup>(3)</sup> , <sup>(4)</sup> | $R_{	heta JA}$      | 60          | °C/W |

| Thermal Resistance, Junction to Board <sup>(5)</sup>                    | $R_{	heta JB}$      | 20          | °C/W |

| Operational Package Temperature [Ambient Temperature] (6)               | T <sub>A</sub>      | -40 to 125  | °C   |

#### Notes

- 1. ESD1 testing is performed in accordance with the Human Body Model ( $C_{ZAP}$ =100 pF,  $R_{ZAP}$ =1500  $\Omega$ ). ESD2 testing is performed in accordance with the Machine Model ( $C_{ZAP}$ =200 pF,  $R_{ZAP}$ =0  $\Omega$ )

- 2. Maximum power dissipation at indicated junction temperature.

- 3. Junction temperature is a function of on-chip power dissipation, package thermal resistance, mounting site (board) temperature, ambient temperature, air flow, power dissipation of other components on the board, and board thermal resistance.

- 4. Per SEMI G38-87 and JEDEC JESD51-2 with the single layer board horizontal.

- Thermal resistance between the die and the printed circuit board per JEDEC JESD51-8. Board temperature is measured on the top surface of the board near the package.

- 6. The limiting factor is junction temperature, taking into account the power dissipation, thermal resistance, and heat sinking.

# ELECTRICAL CHARACTERISTICS MAXIMUM RATINGS

# Table 2. Maximum Ratings (continued)

All voltages are with respect to ground unless otherwise noted.

| Rating                                                 | Symbol            | Value      | Unit |

|--------------------------------------------------------|-------------------|------------|------|

| Operational Junction Temperature                       | T <sub>J</sub>    | -40 to 150 | °C   |

| Storage Temperature                                    | T <sub>STG</sub>  | -55 to 150 | °C   |

| Peak Package Reflow Temperature During Reflow (7), (8) | T <sub>PPRT</sub> | Note 8     | °C   |

- 7. Pin soldering temperature limit is for 10 seconds maximum duration. Not designed for immersion soldering. Exceeding these limits may cause malfunction or permanent damage to the device.

- 8. Freescale's Package Reflow capability meets Pb-free requirements for JEDEC standard J-STD-020C. For Peak Package Reflow Temperature and Moisture Sensitivity Levels (MSL),

- Go to www.freescale.com, search by part number [e.g. remove prefixes/suffixes and enter the core ID to view all orderable parts. (i.e. MC33xxxD enter 33xxx), and review parametrics.

#### STATIC ELECTRICAL CHARACTERISTICS

#### **Table 3. Static Electrical Characteristics**

Characteristics noted under conditions  $9.0 \text{ V} \le \text{V}_{PWR} \le 16 \text{ V}$ ,  $-40^{\circ}\text{C} \le \text{T}_{J} = \text{T}_{A} \le 125^{\circ}\text{C}$ , using the typical application circuit (see Figure 8) unless otherwise noted. Typical values noted reflect the approximate parameter mean at  $\text{T}_{A} = 25^{\circ}\text{C}$  under nominal conditions unless otherwise noted.

| Characteristic                                                                    | Symbol                | Min | Тур  | Max  | Unit |

|-----------------------------------------------------------------------------------|-----------------------|-----|------|------|------|

| GENERAL                                                                           | 1                     |     | 1    |      |      |

| Supply Voltage Range                                                              |                       |     |      |      | V    |

| Normal Operating Voltage Range (9)                                                | V <sub>PWR(N)</sub>   | 6.0 | -    | 18   |      |

| Extended Operating Voltage Range (9)                                              | V <sub>PWR(E)</sub>   | 18  | -    | 26.5 |      |

| Maximum Transient Voltage - Load Dump (10)                                        | V <sub>PWR(LD)</sub>  | _   | _    | 40   | V    |

| VPWR Supply Current                                                               | I <sub>VPWR</sub>     |     |      |      | mA   |

| $EN = 5.0 \text{ V}, \text{ V}_{PWR} = 14 \text{ V}, \text{ No Loads}$            |                       | 25  | _    | 150  |      |

| VPWR Quiescent Supply Current                                                     | I <sub>QVPWR</sub>    |     |      |      | μА   |

| $EN = 0 V$ , $V_{PWR} = 12 V$                                                     |                       | 5.0 | _    | 15   |      |

| KA_VPWR Supply Current,                                                           | I <sub>KAVPWR</sub>   |     |      |      | mA   |

| $EN = 5.0 \text{ V}$ , $KA_V_{PWR} = 14 \text{ V}$ , No Load on $V_{KAM}$         |                       | 0.5 | _    | 3.0  |      |

| KA_VPWR Quiescent Supply Current                                                  | I <sub>QKAVPWR</sub>  |     |      |      | μА   |

| $EN = 0 V, KA_V_{PWR} = 12 V$                                                     |                       | 50  | _    | 350  |      |

| BUCK REGULATOR (VDDH)                                                             |                       |     | •    | 1    | 1    |

| Buck Converter Output Voltage                                                     | $V_{DDH}$             |     |      |      | V    |

| $I_{VDDH}$ = 200 mA to 1.4 A, $V_{PWR}$ = KA_ $V_{PWR}$ = 14 V                    |                       | 4.9 | -    | 5.1  |      |

| Buck Converter Output Voltage                                                     | V <sub>DDH</sub>      |     |      |      | V    |

| $I_{VDDH} = 1.4 A$ , $V_{PWR} = KA_V_{PWR} = 6.0 V$                               |                       | 4.9 | _    | 5.1  |      |

| VDDH Line Regulation                                                              | REGLN <sub>VDDH</sub> |     |      |      | mV   |

| $V_{PWR}$ = KA_ $V_{PWR}$ = 10 V to 14 V, $I_{VDDH}$ = 200 mA                     |                       | -20 | _    | 30   |      |

| VDDH Load Regulation                                                              |                       |     |      |      | mV   |

| $V_{PWR}$ = KA_ $V_{PWR}$ = 14 V, $I_{VDDH}$ = 200 mA to 1.4 A                    | REGLD <sub>VDDH</sub> | -20 | _    | 20   |      |

| $V_{PWR}$ = KA_ $V_{PWR}$ = 6.0 V, $I_{VDDH}$ = 200 mA to 1.4 A                   |                       | -20 | -    | 20   |      |

| VDDH Active Discharge Resistance                                                  | R <sub>HDISCH</sub>   |     |      |      | Ω    |

| $V_{PWR} = KA_V_{PWR} = 14 \text{ V}, EN = 0 \text{ V}, I_{VDDH} = 10 \text{ mA}$ |                       | 1.0 | _    | 15   |      |

| P-CHANNEL MOSFET                                                                  | 1                     |     |      |      |      |

| Drain-Source Breakdown Voltage—Not Tested (11)                                    | BV <sub>DSS</sub>     | 45  | _    | _    | V    |

| Drain-Source Current Limit—Not Tested (11)                                        | ISC <sub>SW1</sub>    | _   | -7.0 | _    | Α    |

#### Notes

- 9. VDDH is fully functional when the 33998 is operating at higher battery voltages, but these parameters are not tested. The test condition as are:

- a)  $V_{DDH}$  must be between 4.9 V and 5.1 V (200 mA to 1.4 A) for  $V_{PWR}$  = 14 V to 18 V.

- b)  $V_{DDH}$  must be between 4.8 V and 5.5 V (200 mA to 1.4 A) for  $V_{PWR}$  = 18 V to 26.5 V.

- 10. Part can survive, but no parameters are guaranteed.

- 11. Guaranteed by design but not production tested.

#### 33998

# **Table 3. Static Electrical Characteristics (continued)**

Characteristics noted under conditions  $9.0 \text{ V} \le \text{V}_{PWR} \le 16 \text{ V}$ ,  $-40^{\circ}\text{C} \le \text{T}_{J} = \text{T}_{A} \le 125^{\circ}\text{C}$ , using the typical application circuit (see <u>Figure 8</u>) unless otherwise noted. Typical values noted reflect the approximate parameter mean at  $\text{T}_{A} = 25^{\circ}\text{C}$  under nominal conditions unless otherwise noted.

| Characteristic                                                                                                 | Symbol                 | Min | Тур   | Max | Unit |

|----------------------------------------------------------------------------------------------------------------|------------------------|-----|-------|-----|------|

| LINEAR REGULATOR (VDDL)                                                                                        | <u>I</u>               |     | -     |     | 1    |

| VDDL Output Voltage                                                                                            | $V_{DDL}$              |     |       |     | V    |

| $V_{PWR} = KA_V_{PWR} = 14 \text{ V}, I_{VDDL} = 200 \text{ mA}$                                               |                        | 2.5 | 2.6   | 2.7 |      |

| VDDL Line Regulation                                                                                           | REGLN <sub>VDDL</sub>  |     |       |     | mV   |

| $V_{DDH}$ = 4.8 V to 5.2 V, $I_{VDDL}$ = 400 mA                                                                |                        | -30 | _     | 30  |      |

| VDDL Load Regulation                                                                                           | REGLD <sub>VDDL</sub>  |     |       |     | mV   |

| $V_{PWR} = KA_V_{PWR} = 14 \text{ V}, I_{VDDL} = 10 \text{ mA to } 400 \text{ mA}$                             |                        | -70 | _     | 70  |      |

| DRVL Output Current                                                                                            | I <sub>DRVL</sub>      |     |       |     | mA   |

| $V_{PWR} = KA_V_{PWR} = 14 \text{ V}, VDRVL = 1.0 \text{ V}$                                                   |                        | 5.0 | 11    | 25  |      |

| VDDL Active Discharge Resistance                                                                               | R <sub>LDISCH</sub>    |     |       |     | Ω    |

| $V_{PWR} = KA_V_{PWR} = 14 \text{ V}, EN = 0 \text{ V}, I_{FBL} = 10 \text{ mA}$                               |                        | 1.0 | _     | 10  |      |

| VDDH to VDDL Active Clamp Resistance                                                                           | R <sub>CLAMP</sub>     |     |       |     | Ω    |

| $V_{PWR} = KA_V_{PWR} = 14 \text{ V}, EN = 0 \text{ V}, I_{VDDH} = 50 \text{ mA}, V_{FBKB} = 0 \text{ V}$      |                        | 0.6 | _     | 10  |      |

| VDDL Output Capacitor Capacitance (12)                                                                         | C <sub>VDDL</sub>      | -   | 68    | _   | μF   |

| VDDL Output Capacitor ESR (12)                                                                                 | ESR <sub>VDDL</sub>    | -   | 0.125 | -   | Ω    |

| KEEP-ALIVE (STANDBY) REGULATOR (VKAM)                                                                          | <u>'</u>               |     | •     | •   |      |

| VKAM Output Voltage                                                                                            | $V_{KAM}$              |     |       |     | V    |

| $I_{VKAM} = 5.0 \text{ mA}$ , VPWR = KA_V <sub>PWR</sub> = 18 V, EN = 5.0 V                                    |                        | 2.5 | _     | 2.7 |      |

| VKAM Output Voltage, EN = 0 V (Standby Mode)                                                                   | $V_{KAM}$              |     |       |     | V    |

| $V_{PWR} = KA_V_{PWR} = 26 \text{ V}, I_{VKAM} = 0.5 \text{ mA}$                                               |                        | 2.5 | _     | 2.7 |      |

| $V_{PWR} = KA_V_{PWR} = 18 \text{ V}, I_{VKAM} = 5.0 \text{ mA}$                                               |                        | 2.5 | _     | 2.7 |      |

| $V_{PWR} = KA_V_{PWR} = 5.0 \text{ V}, I_{VKAM} = 10.0 \text{ mA}$                                             |                        | 2.5 | _     | 2.7 |      |

| $V_{PWR} = 0 \text{ V}, \text{ KA\_V}_{PWR} = 3.5 \text{ V}, I_{VKAM} = 5.0 \text{ mA}$                        |                        | 2.0 | _     | 2.7 |      |

| VKAM Line Regulation, EN = 0 V (Standby Mode)                                                                  | REGLN <sub>VKAM</sub>  |     |       |     | mV   |

| $V_{PWR}$ = KA_ $V_{PWR}$ = 5.0 V to 18 V, $I_{VKAM}$ = 2.0 mA                                                 |                        | -20 | _     | 20  |      |

| VKAM Load Regulation, EN = 0 V (Standby Mode)                                                                  | REGLDD <sub>VKAM</sub> |     |       |     | mV   |

| $V_{PWR} = KA_V_{PWR} = 14 \text{ V}, I_{VKAM} = 1.0 \text{ mA} \text{ to } 10 \text{ mA}$                     |                        | 0   | _     | 100 |      |

| Differential Voltage V <sub>KAM</sub> - V <sub>DDL</sub>                                                       | REG <sub>VKAM</sub>    |     |       |     | mV   |

| $EN = 5.0 \text{ V}, I_{VKAM} = 5.0 \text{ mA}, V_{PWR} = KA_{VPWR} = 14 \text{ V}, I_{VDDL} = 200 \text{ mA}$ |                        | -20 | _     | 60  |      |

| VKAM Output Capacitor Capacitance (12)                                                                         | C <sub>VKAM</sub>      | _   | 4.7   | _   | μF   |

| VKAM Output Capacitor ESR (12)                                                                                 | ESR <sub>VKAM</sub>    | _   | 1.4   | _   | Ω    |

#### Notes

12. Recommended value.

# **Table 3. Static Electrical Characteristics (continued)**

Characteristics noted under conditions  $9.0 \text{ V} \le \text{V}_{PWR} \le 16 \text{ V}$ ,  $-40^{\circ}\text{C} \le \text{T}_{J} = \text{T}_{A} \le 125^{\circ}\text{C}$ , using the typical application circuit (see <u>Figure 8</u>) unless otherwise noted. Typical values noted reflect the approximate parameter mean at  $\text{T}_{A} = 25^{\circ}\text{C}$  under nominal conditions unless otherwise noted.

| Characteristic                                                                                                                                          | Symbol                 | Min  | Тур | Max  | Unit |

|---------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|------|-----|------|------|

| SENSOR SUPPLIES (VREF1, VREF2)                                                                                                                          |                        |      |     |      |      |

| VREF On-Resistance, $T_A$ = -40°C<br>$I_{VREF}$ = 200 mA, $I_{VDDH}$ = 200 mA, $V_{PWR}$ = KA_ $V_{PWR}$ = 14 V, EN = 5.0 V                             | R <sub>DS(ON)</sub>    | _    | _   | 280  | mΩ   |

| VREF On-Resistance, $T_A$ = +25°C<br>I <sub>VREF</sub> = 200 mA, I <sub>VDDH</sub> = 200 mA, V <sub>PWR</sub> = KA_V <sub>PWR</sub> = 14 V, EN = 5.0 V  | R <sub>DS(ON)</sub>    | _    | -   | 350  | mΩ   |

| VREF On-Resistance, $T_A$ = +125°C<br>I <sub>VREF</sub> = 200 mA, I <sub>VDDH</sub> = 200 mA, V <sub>PWR</sub> = KA_V <sub>PWR</sub> = 14 V, EN = 5.0 V | R <sub>DS(ON)</sub>    | _    | _   | 455  | mΩ   |

| VREF Short-to-Battery Detect Current  V <sub>PWR</sub> = KA_V <sub>PWR</sub> = 14 V, EN = 5.0 V, SNSEN = 5.0 V                                          | I <sub>SC_BAT</sub>    | 500  | _   | 900  | mA   |

| VREF Short-to-Ground Detect Current  V <sub>PWR</sub> = KA_V <sub>PWR</sub> = 14 V, EN = 5.0 V, SNSEN = 5.0 V                                           | I <sub>SC_GND</sub>    | 500  | -   | 900  | mA   |

| Maximum Output Capacitance (Total) (13)                                                                                                                 | C <sub>VREF</sub>      | 33   | -   | 39   | nF   |

| SUPERVISORY CIRCUITS (VPWR)                                                                                                                             |                        |      |     |      |      |

| PWROK Undervoltage Threshold on $V_{DDL}$ , FBL Ramps Down $V_{PWR} = KA_V_{PWR} = 14 \text{ V}, I_{VDDH} = 200 \text{ mA}$                             | V <sub>FBL(THL)</sub>  | 2.1  | 2.4 | 2.5  | V    |

| PWROK Undervoltage Threshold on $V_{DDH}$<br>$V_{PWR} = KA_V_{PWR} = 14 \text{ V}, I_{VDDH} = 200 \text{ mA}$                                           | V <sub>DDH(THL)</sub>  | 4.5  | _   | 4.8  | V    |

| VDDH Overvoltage Threshold $V_{PWR} = KA_{V_{PWR}} = 10 \text{ V, I}_{VDDH} = 200 \text{ mA}$                                                           | V <sub>DDH(THH)</sub>  | 5.12 | -   | 5.7  | V    |

| PWROK Open Drain On-Resistance  V <sub>PWR</sub> = KA_V <sub>PWR</sub> = 14 V, EN = 5 V, I <sub>PwrOK</sub> = 5.0 mA                                    | R <sub>DS(ON)</sub>    | _    | _   | 200  | Ω    |

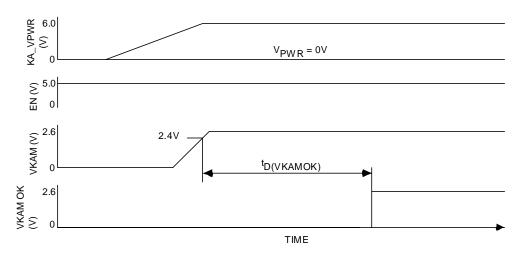

| VKAMOK Threshold, $V_{PWR} = KA_{VPWR} = 14 \text{ V}, I_{VDDH} = 200 \text{ mA}$                                                                       | V <sub>KAM(THL)</sub>  | 2.1  | 2.4 | 2.5  | V    |

| VKAMOK Threshold on $V_{PWR}$ , $V_{PWR}$ Ramps Up $KA_{VPWR} = 14 \text{ V}$ , $I_{VDDH} = 200 \text{ mA}$                                             | V <sub>PWROK(TH)</sub> | 4.0  | -   | 5.0  | V    |

| VKAMOK Open Drain On-Resistance $V_{PWR} = KA_{VPWR} = 14 \text{ V, EN} = 0 \text{ V, } I_{VKAMOK} = 10 \text{ mA}$                                     | R <sub>DS(ON)</sub>    | 50   | _   | 200  | Ω    |

| Enable Input Voltage Threshold (Pin EN)                                                                                                                 | V <sub>IH</sub>        | 1.0  | -   | 2.0  | V    |

| Enable Pull-Down Current (Pin EN), EN = 1.0 V V <sub>DDH</sub> to V <sub>IL(MIN)</sub>                                                                  | I <sub>PD</sub>        | 500  | -   | 1200 | nA   |

| Sensor Enable Input Voltage Threshold (Pin SNSEN)                                                                                                       | V <sub>IH</sub>        | 1.0  | -   | 2.0  | V    |

| Sensor Enable Pull-Down Current (Pin SNSEN)  SNSEN = 1.0 V V <sub>DDH</sub> to V <sub>IL(MIN)</sub>                                                     | I <sub>PD</sub>        | 500  | _   | 1200 | nA   |

#### Notes

13. Recommended value.

# ELECTRICAL CHARACTERISTICS STATIC ELECTRICAL CHARACTERISTICS

# Table 3. Static Electrical Characteristics (continued)

Characteristics noted under conditions  $9.0 \text{ V} \le \text{V}_{PWR} \le 16 \text{ V}$ ,  $-40^{\circ}\text{C} \le \text{T}_{J} = \text{T}_{A} \le 125^{\circ}\text{C}$ , using the typical application circuit (see <u>Figure 8</u>) unless otherwise noted. Typical values noted reflect the approximate parameter mean at  $\text{T}_{A} = 25^{\circ}\text{C}$  under nominal conditions unless otherwise noted.

| Characteristic                                                               | Symbol            | Min | Тур | Max | Unit |

|------------------------------------------------------------------------------|-------------------|-----|-----|-----|------|

| CHARGE PUMP (CRES)                                                           | •                 |     |     |     |      |

| Charge Pump Voltage                                                          | V <sub>CRES</sub> |     |     |     | V    |

| $V_{PWR}$ = KA_ $V_{PWR}$ = 14 V, $I_{VDDH}$ = 200 mA, $I_{CP}$ = 0 $\mu$ A  |                   | 12  | _   | 15  |      |

| $V_{PWR}$ = KA_ $V_{PWR}$ = 14 V, $I_{VDDH}$ = 200 mA, $I_{CP}$ = 10 $\mu$ A |                   | 12  | _   | 15  |      |

# **DYNAMIC ELECTRICAL CHARACTERISTICS**

## Table 4. DYNAMIC ELECTRICAL CHARACTERISTICS

Characteristics noted under conditions 9.0 V  $\leq$  V<sub>PWR</sub>  $\leq$  16 V, -40°C  $\leq$  T<sub>J</sub> = T<sub>A</sub>  $\leq$  125°C using the typical application circuit (see <u>Figure 8</u>) unless otherwise noted. Typical values noted reflect the approximate parameter mean at T<sub>A</sub> = 25°C under nominal conditions unless otherwise noted.

| Characteristic                                                                                                  | Symbol                 | Min | Тур | Max | Unit |

|-----------------------------------------------------------------------------------------------------------------|------------------------|-----|-----|-----|------|

| BUCK REGULATOR (VDDH)                                                                                           | •                      |     |     | •   |      |

| Switching Frequency (14)                                                                                        | f <sub>SW</sub>        | -   | 750 | _   | kHz  |

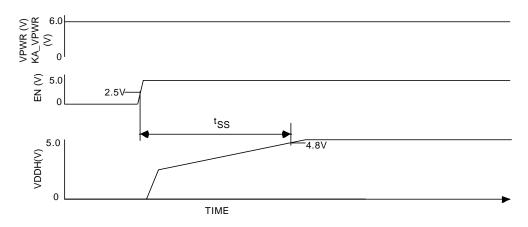

| Soft Start Duration (see Figure 2)                                                                              | t <sub>SS</sub>        |     |     |     | ms   |

| $V_{PWR} = KA_V_{PWR} = 6.0 V$                                                                                  |                        | 5.0 | _   | 15  |      |

| CHARGE PUMP (CRES)                                                                                              | •                      |     |     | •   |      |

| Charge Pump Current Ramp-Up Time                                                                                | t <sub>CRES</sub>      |     |     |     | ms   |

| $V_{PWR} = KA_{VPWR} = 14 \text{ V}, C_{RES} = 22 \text{ nF}, V_{CP} = 1.0 \text{ V} \text{ to } 11 \text{ V}$  |                        | 1.0 | _   | 20  |      |

| Charge Pump Ramp-Up Time                                                                                        | t <sub>CRES</sub>      |     |     |     | ms   |

| $V_{PWR} = KA_{VPWR} = 7.0 \text{ V}, C_{RES} = 22 \text{ nF}, V_{CP} = 7.0 \text{ V} \text{ to } 10 \text{ V}$ |                        | 1.0 | -   | 10  |      |

| SENSOR SUPPLIES (VREF1, VREF2)                                                                                  | •                      |     |     | •   |      |

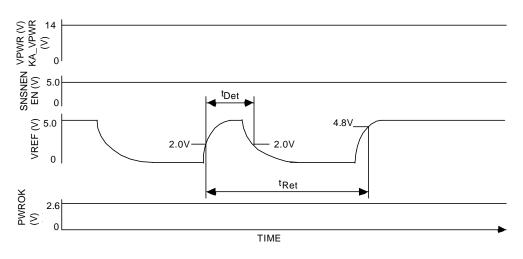

| VREF Overcurrent Detection Time (see Figure 3)                                                                  | t <sub>DET</sub>       |     |     |     | μS   |

| $V_{REF}$ Load $R_L = 5.0 \Omega$ to GND, $V_{DDH} = 5.1 \text{ V}$ , $V_{PWR} = KA_V_{PWR} = 10 \text{ V}$ ,   |                        | 0.5 |     |     |      |

| EN = 5.0 V, SNSEN = 5.0 V                                                                                       |                        | 0.5 | -   | 2.0 |      |

| VREF Retry Timer Delay (see Figure 3)                                                                           | t <sub>RET</sub>       |     |     |     | ms   |

| $V_{REF}$ Load $R_L = 5.0 \Omega$ to GND, $V_{DDH} = 5.1 \text{ V}$ , $V_{PWR} = KA_V_{PWR} = 10 \text{ V}$ ,   |                        | 5.0 |     | 00  |      |

| EN = 5.0 V, SNSEN = 5.0 V                                                                                       |                        | 5.0 | _   | 20  |      |

| SUPERVISORY CIRCUITS (VPWR)                                                                                     |                        |     |     |     |      |

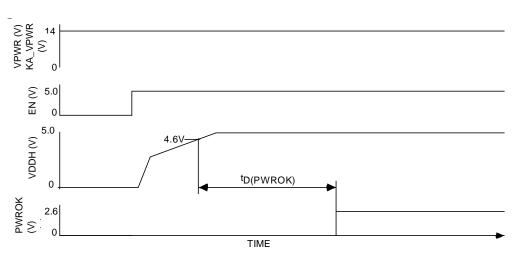

| PWROK Delay Time (Power-On Reset) (see Figure 4)                                                                | t <sub>D(PWROK)</sub>  | 5.0 | -   | 15  | ms   |

| VKAMOK Delay Time (see Figure 5)                                                                                | t <sub>D(VKAMOK)</sub> | 10  | -   | 30  | ms   |

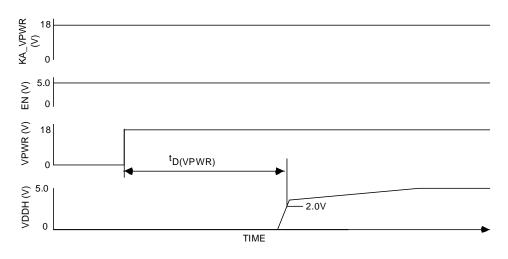

| VDDH Power-Up Delay Time (see <u>Figure 6</u> )                                                                 | t <sub>D(VPWR)</sub>   | 1.0 | -   | 10  | ms   |

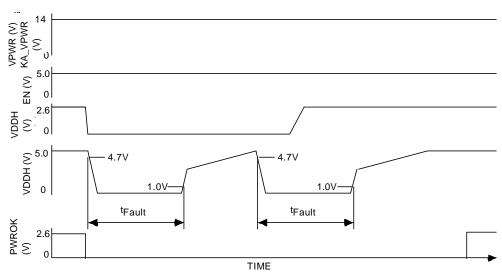

| Fault-Off Timer Delay Time (see Figure 7)                                                                       | t <sub>FAULT</sub>     | 1.0 | -   | 10  | ms   |

#### Notes

<sup>14.</sup> Guaranteed by design but not production tested.

# **TIMING DIAGRAMS**

Figure 4. Soft-Start Time

Figure 5. VREF Retry Timer

Figure 6. PWROK Delay Timer (Power-On Reset)

Figure 7. VKAMOK Delay Time

Figure 8. VDDH Power-Up Delay Time

Figure 9. Fault-Off Timer Delay Time

# **FUNCTIONAL DESCRIPTION**

#### INTRODUCTION

The 33998 multi-output power supply integrated circuit is capable of operating from 6.0 V up to 26.5 V with 40 V transient capability. It incorporates a step-down switching controller regulating directly to 5.0 V. The 2.6 V linear regulator uses an external pass transistor, thus reducing the

power dissipation of the integrated circuit. The 33998 also provides a 2.6 V linear standby regulator and two 5.0 V sensor supply outputs protected by internal low-resistance LDMOS transistors against short-to-battery and short-to-ground.

#### **FUNCTIONAL PIN DESCRIPTION**

#### **SWITCHING REGULATOR (VDDH)**

The switching regulator is a high-frequency (750 kHz), conventional buck converter with integrated high-side p-channel power MOSFET. Its output voltage is regulated to provide 5.0 V with ±2% accuracy and it is intended to directly power the digital and analog circuits of the Electronic Control Module (ECM). The switching regulator output is rated for 1400 mA total output current. This current can be used by the linear regulator VDDL and sensor supplies VREF1 and VREF2. The 33998 switching controller utilizes "Sensorless Current Mode Control" to achieve good line rejection and stabilize the feedback loop. A soft-start feature is incorporated into the 33998. When the device is enabled, the switching regulator output voltage VDDH ramps up to about half of full scale and then takes 16 steps up to the nominal regulation voltage level (5.0 V nominal).

#### 2.6 V LINEAR REGULATOR (VDDL)

The 2.6 V linear post-regulator is powered from the 5.0 V switching regulator output (VDDH). A discrete pass transistor is used to the power path for the VDDL regulator. This arrangement minimizes the power dissipation off the controller IC. The FBL pin is the feedback input of the regulator control loop and the DRVL pin the external NPN pass transistor base drive. Power up, power down, and fault management are coordinated with the 5.0 V switching regulator.

# **SENSOR SUPPLIES (VREF1) AND (VREF2)**

The sensor supplies are implemented using a protected switch to the main 5.0 V (switching regulator) output. The 33998 integrated circuit provides two low-resistance LDMOS power MOSFETs connected to the switching regulator output (VDDH). These switches have short-to-battery and short-to-ground protection integrated into the IC. When a severe fault conditions is detected, the affected sensor output is turned off and the sensor Retry Timer starts to time out. After the Retry Timer expires, the sensor supply tries to power up again. Sensor supplies VREF can be disabled by pulling the Sensor Enable SNSEN pin low (see Figure 7 for the VREF Retry Timer operation).

**Notes:** Severe fault conditions on the VREF1 and VREF2 outputs, like hard shorts to either ground or battery, may disrupt the operation of the main regulator VDDH. Shorts to

battery above 17 V are considered "double faults" and neither one of the VREF outputs is protected against such conditions.

Depending on the VDDH capacitor value and its ESR value, the severity of the short may disrupt the VDDH operation.

#### **KEEP-ALIVE REGULATOR, STANDBY (VKAM)**

The Keep-Alive Regulator VKAM (keep-alive memory) is intended to provide power for "key off" functions such as nonvolatile SRAM, "KeyOff" timers and controls, KeySwitch monitor circuits, and perhaps a CAN/SCP monitor and wake-up function. It may also power other low-current circuits required during a "KeyOff" condition. The regulated voltage is nominally 2.6 V. A severe fault condition on the VKAM output is signaled by pulling the VKAMOK signal low.

# KEEP-ALIVE OPERATION, STANDBY, POWER-DOWN MODE (VKAM)

When the EN pin is pulled low, the power supply is forced into a low-current standby mode. In order to reduce current drawn by the VPWR and KA\_VPWR pins, all power supply functions are disabled except for the VKAM and Enable (EN) pins. The latter pin is monitored for the "wake-up" signal. The switching transistor gate is actively disabled and the VDDL and VDDH pins are actively pulled low.

#### **POWER-UP DELAY TIMERS**

Two Power-Up Delay timers are integrated into the control section of the integrated circuit. One timer monitors the input voltage at the VPWR input pin (see Figure 3), and the other monitors the input voltage at the KA\_VPWR input pin. In both cases, sufficient supply voltage must be present long enough for the timers to "time out" before the switching regulator can be enabled.

#### **FAULT-OFF TIMER**

If the VDDL output voltage does not reach its valid range at the end of soft-start period, or if the VDDH or VDDL output voltage gets below its PWROK threshold level, the Fault-Off Timer shuts the switching regulator off until the timer "times out" and the switching regulator retries to power up again (see Figure 7 for Fault-Off Timer operation details).

# FUNCTIONAL DESCRIPTION FUNCTIONAL PIN DESCRIPTION

#### **POWER-ON RESET TIMER**

This timer starts to time out at the end of the soft-start period if the VDDH and VDDL outputs are in the valid regulation range. If the timer "times out", then the open-drain PWROK signal is released, indicating that "power is ON".

# SUPERVISORY CIRCUITS (PWROK) AND (VKAMOK)

The 33998 has two voltage monitoring open-drain outputs, the PWROK and the VKAMOK pins. PWROK is "active high". This output is pulled low when either of the regulator outputs

(VDDH or VDDL) are below their regulation windows. If both regulator outputs are above their respective lower thresholds, and the Power-On Reset Timer has expired, the output driver is turned off and this pin is at high-impedance state (see Figure 6).

The VKAMOK signal indicates a severe fault condition on the keep-alive regulator output VKAM. The VKAM output voltage is compared to the internal bandgap reference voltage. When the VKAM falls below the bandgap reference voltage level, the VKAMOK signal is pulled low.

# **TYPICAL APPLICATIONS**

**Note** The VDDH total output current is 1.4 A. This includes the current used by the linear regulator VDDL and buffered outputs VREF1 and VREF2.

Figure 10. 33998 Application Circuit Schematic Diagram

**Table 5. Recommended Components**

| Designator         | Value/Rating   | Description/Part No.                | Manufacturer (16)     |

|--------------------|----------------|-------------------------------------|-----------------------|

| Cf1                | 10 μF/50 V     | Aluminum Electrolytic/UUB1H100MNR   | Nichicon              |

| Cf2, C2            | 1.0 μF/50 V    | Ceramic X7R/C1812C105K5RACTR        | Kemet                 |

| C1                 | 100 μF/50 V    | Aluminum Electrolytic/UUH1V101MNR   | Nichicon              |

| C3 <sup>(15)</sup> | 68 μF/10 V     | Tantalum/T494D686M010AS             | Kemet                 |

| C6                 | 68 μF/10 V     | Tantalum/T494D686M010AS             | Kemet                 |

| C7                 | 4.7 μF/10 V    | Tantalum/T494A475M010AS             | Kemet                 |

| C4, C5             | 100 nF/16 V    | Ceramic X7R                         | Any Manufacturer      |

| C8 (Optional)      | 390 pF/50 V    | Ceramic X7R                         | Any Manufacturer      |

| C9                 | 22 nF/25 V     | Ceramic X7R                         | Any Manufacturer      |

| Cs1, Cs2           | 33 nF/25 V     | Ceramic X7R                         | Any Manufacturer      |

| Cc1                | 2.2 nF/16 V    | Ceramic X7R                         | Any Manufacturer      |

| R1, R2             | 10 kΩ          | Resistor 0805, 5%                   | Any Manufacturer      |

| R3 (Optional)      | 2.2 Ω          | Resistor 0805, 5%                   | Any Manufacturer      |

| Rc1                | 3.6 kΩ         | Resistor 0805, 5%                   | Any Manufacturer      |

| Lf1                | 10 μH          | CDRH127-100M                        | Sumida                |

|                    | or SLF10145-10 |                                     | TDK                   |

| L1                 | 15 µH          | CDRH127-150MC                       | Sumida                |

|                    |                | or SLF10145-150M2R2                 | TDK                   |

| Q1                 | 1.0 A/20 V     | Bipolar Transistor/BCP68T1          | ON Semiconductor      |

| D1                 | 2.0 A/50 V     | Schottky Diode/SS25                 | General Semiconductor |

| Dp1                | 3.0 A/200 V    | Diode/MURS320                       | ON Semiconductor      |

| Dp2                | 27 V           | Transient Voltage Suppressor/SM5A27 | General Semiconductor |

#### Notes

- 15. It is possible to use ceramic capacitors in the switcher output, e.g. C3 = 2 x 22  $\mu$ F/6.3 V X7R ceramic. In this case the compensation resistor has to be changed to Rc1 = 200  $\Omega$  to stabilize the switching regulator operation.

- 16. Freescale Semiconductor does not assume liability, endorse, or warrant components from external manufacturers that are referenced in circuit drawings or tables. While Freescale Semiconductor offers component recommendations in this configuration, it is the customer's responsibility to validate their application.

- 17. Freescale Semiconductor does not assume liability, endorse, or warrant components from external manufacturers that are referenced in circuit drawings or tables. While Freescale Semiconductor offers component recommendations in this configuration, it is the customer's responsibility to validate their application.

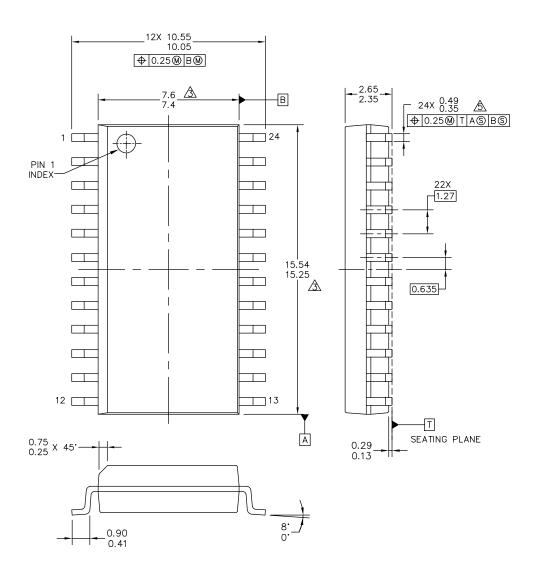

# **PACKAGING**

## **PACKAGE DIMENSIONS**

For the most current package revision, visit <u>www.freescale.com</u> and perform a keyword search using the "98A" listed below.

| © FREESCALE SEMICONDUCTOR, INC.  ALL RIGHTS RESERVED.  MECHANIC |  | L OUTLINE    | PRINT VERSION NO | T TO SCALE  |

|-----------------------------------------------------------------|--|--------------|------------------|-------------|

| TITLE: 24LD SOIC W/B, 1.27 PITCH<br>7.5 X 15.4<br>CASE-OUTLINE  |  | DOCUMENT NO  | ): 98ASB42344B   | REV: F      |

|                                                                 |  | CASE NUMBER  | : 751E-04        | 26 APR 2005 |

|                                                                 |  | STANDARD: JE | DEC MS-013 AD    |             |

DWB SUFFIX EG SUFFIX (PB-FREE) 24 PIN SOIC WIDE BODY PLASTIC PACKAGE 98ASB42344B ISSUE F

# **REVISION HISTORY**

| Revision | Date   | Description of Changes                                                                                                                                                                                                                                                                                                                                                                                                       |

|----------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2.0      | 8/2006 | <ul> <li>Implemented Revision History page</li> <li>Converted to Freescale format</li> <li>Update to the prevailing form and style</li> <li>Removed MC33998EG/R2, and replaced with MCZ33998EG/R2 in the Ordering Information block</li> <li>Removed Peak Package Reflow Temperature During Reflow (solder reflow) parameter from Maximum Ratings on page 5. Added note with instructions from www.freescale.com.</li> </ul> |

#### How to Reach Us:

#### **Home Page:**

www.freescale.com

#### E-mail:

support@freescale.com

#### **USA/Europe or Locations Not Listed:**

Freescale Semiconductor Technical Information Center, CH370 1300 N. Alma School Road Chandler, Arizona 85224 +1-800-521-6274 or +1-480-768-2130 support@freescale.com

# **Europe, Middle East, and Africa:** Freescale Halbleiter Deutschland GmbH

Freescale Halbleiter Deutschland GmbH Technical Information Center Schatzbogen 7 81829 Muenchen, Germany +44 1296 380 456 (English) +46 8 52200080 (English) +49 89 92103 559 (German) +33 1 69 35 48 48 (French) support@freescale.com

#### Japan

Freescale Semiconductor Japan Ltd. Headquarters ARCO Tower 15F 1-8-1, Shimo-Meguro, Meguro-ku, Tokyo 153-0064 Japan 0120 191014 or +81 3 5437 9125 support.japan@freescale.com

#### Asia/Pacific:

Freescale Semiconductor Hong Kong Ltd. Technical Information Center 2 Dai King Street

Tai Po Industrial Estate

Tai Po, N.T., Hong Kong

+800 2666 8080

support.asia@freescale.com

## For Literature Requests Only:

Freescale Semiconductor Literature Distribution Center P.O. Box 5405

Denver, Colorado 80217

1-800-441-2447 or 303-675-2140

Fax: 303-675-2150

LDCForFreescaleSemiconductor@hibbertgroup.com

RoHS-compliant and/or Pb-free versions of Freescale products have the functionality and electrical characteristics of their non-RoHS-compliant and/or non-Pb-free counterparts. For further information, see <a href="http://www.freescale.com">http://www.freescale.com</a> or contact your Freescale sales representative.

For information on Freescale's Environmental Products program, go to http://www.freescale.com/epp.

Information in this document is provided solely to enable system and software implementers to use Freescale Semiconductor products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits or integrated circuits based on the information in this document.

Freescale Semiconductor reserves the right to make changes without further notice to any products herein. Freescale Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Freescale Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters that may be provided in Freescale Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals", must be validated for each customer application by customer's technical experts. Freescale Semiconductor does not convey any license under its patent rights nor the rights of others. Freescale Semiconductor products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Freescale Semiconductor product could create a situation where personal injury or death may occur. Should Buyer purchase or use Freescale Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold Freescale Semiconductor and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Freescale Semiconductor was negligent regarding the design or manufacture of the part.

Freescale<sup>™</sup> and the Freescale logo are trademarks of Freescale Semiconductor, Inc. All other product or service names are the property of their respective owners.

© Freescale Semiconductor, Inc., 2007. All rights reserved.