# **Stepper Motor Driver**

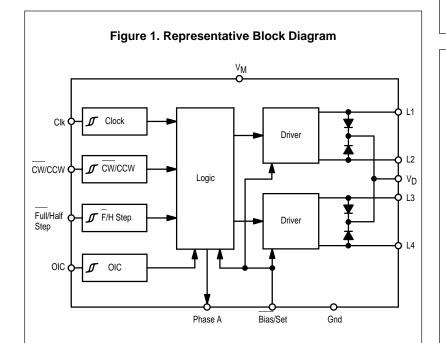

The MC3479 is designed to drive a two-phase stepper motor in the bipolar mode. The circuit consists of four input sections, a logic decoding/sequencing <u>section</u>, two driver-stages for the motor coils, and an output to indicate the Phase A drive state.

- Single Supply Operation: 7.2 to 16.5 V

- 350 mA/Coil Drive Capability

- Clamp Diodes Provided for Back-EMF Suppression

- Selectable CW/CCW and Full/Half Step Operation

- Selectable High/Low Output Impedance (Half Step Mode)

- TTL/CMOS Compatible Inputs

- Input Hysteresis: 400 mV Minimum

- Phase Logic Can Be Initialized to Phase A

- Phase A Output Drive State Indication (Open–Collector)

- Available in Standard DIP and Surface Mount

#### **ORDERING INFORMATION**

| Device  | Operating<br>Temperature Range | Package |

|---------|--------------------------------|---------|

| MC3479P | $T_A = 0^\circ$ to +70°C       | Plastic |

## STEPPER MOTOR DRIVER

SEMICONDUCTOR TECHNICAL DATA

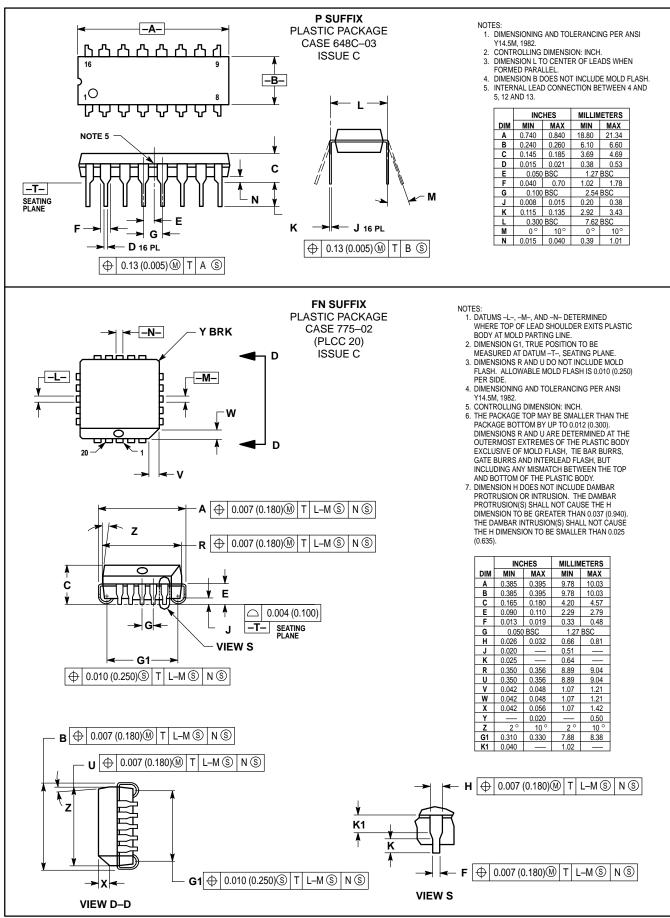

P SUFFIX PLASTIC PACKAGE CASE 648C

#### INPUT TRUTH TABLE

|                | Input Low    | Input High   |

|----------------|--------------|--------------|

| CW/CCW         | CW           | CCW          |

| Full/Half Step | Full Step    | Half Step    |

| OIC            | Hi Z         | Low Z        |

| Clk            | Positive Edg | ge Triggered |

© Motorola, Inc. 1996

### MAXIMUM RATINGS

| Rating                              | Symbol           | Value                | Unit |

|-------------------------------------|------------------|----------------------|------|

| Supply Voltage                      | VM               | + 18                 | Vdc  |

| Clamp Diode Cathode Voltage (Pin 1) | VD               | V <sub>M</sub> + 5.0 | Vdc  |

| Driver Output Voltage               | V <sub>OD</sub>  | V <sub>M</sub> + 6.0 | Vdc  |

| Drive Output Current/Coil           | lod              | ± 500                | mA   |

| Input Voltage (Logic Controls)      | V <sub>in</sub>  | – 0.5 to + 7.0       | Vdc  |

| Bias/Set Current                    | IBS              | - 10                 | mA   |

| Phase A Output Voltage              | VOA              | + 18                 | Vdc  |

| Phase A Sink Current                | IOA              | 20                   | mA   |

| Junction Temperature                | Тj               | + 150                | °C   |

| Storage Temperature Range           | T <sub>stg</sub> | – 65 to + 150        | °C   |

## **RECOMMENDED OPERATING CONDITIONS**

| Characteristic                            | Symbol | Min   | Max                  | Unit |

|-------------------------------------------|--------|-------|----------------------|------|

| Supply Voltage                            | VM     | + 7.2 | + 16.5               | Vdc  |

| Clamp Diode Cathode Voltage               | VD     | VM    | V <sub>M</sub> + 4.5 | Vdc  |

| Driver Output Current (Per Coil) (Note 1) | lod    | —     | 350                  | mA   |

| Input Voltage (Logic Controls)            | Vin    | 0     | + 5.5                | Vdc  |

| Bias/Set Current (Outputs Active)         | IBS    | - 300 | - 75                 | μA   |

| Phase A Output Voltage                    | VOA    | —     | VM                   | Vdc  |

| Phase A Sink Current                      | IOA    | 0     | 8.0                  | mA   |

| Operating Ambient Temperature             | TA     | 0     | + 70                 | °C   |

**NOTE:** 1. See section on Power Dissipation in Application Information.

DC ELECTRICAL CHARACTERISTICS (Specifications apply over the recommended supply voltage and temperature range, [Notes 2, 3] unless otherwise noted.)

| Characteristic                                                       | Pins  | Symbol | Min      | Тур | Max | Unit |

|----------------------------------------------------------------------|-------|--------|----------|-----|-----|------|

| INPUT LOGIC LEVELS                                                   |       |        |          |     |     |      |

| Threshold Voltage (Low-to-High)                                      | 7, 8, | VTLH   | —        | _   | 2.0 | Vdc  |

| Threshold Voltage (High-to-Low)                                      | 9, 10 | VTHL   | 0.8      | _   | —   | Vdc  |

| Hysteresis                                                           |       | VHYS   | 0.4      | _   | —   | Vdc  |

| Current: $(V_{I} = 0.4 V)$<br>$(V_{I} = 5.5 V)$<br>$(V_{I} = 2.7 V)$ |       | ΙIL    | -100<br> |     |     | μΑ   |

#### DRIVER OUTPUT LEVELS

| Output High Voltage                                                                                            | 2, 3,  | VOHD |                      |   |       | Vdc |

|----------------------------------------------------------------------------------------------------------------|--------|------|----------------------|---|-------|-----|

| $(I_{BS} = -300 \ \mu\text{A})$ : $(I_{OD} = -350 \ \text{mA})$                                                | 14, 15 |      | V <sub>M</sub> – 2.0 | — | —     |     |

| $(I_{OD} = -0.1 \text{ mA})$                                                                                   |        |      | V <sub>M</sub> – 1.2 | — | —     |     |

| Output Low Voltage ( $I_{BS} = -300 \ \mu\text{A}, I_{OD} = 350 \ \text{mA}$ )                                 |        | VOLD | _                    | — | 0.8   | Vdc |

| Differential Mode Output Voltage Difference (Note 4) $(I_{BS} = -300 \ \mu\text{A}, I_{OD} = 350 \ \text{mA})$ |        | DVOD | —                    | _ | 0.15  | Vdc |

| Common Mode Output Voltage Difference (Note 5)<br>( $I_{BS} = -300 \ \mu A$ , $I_{OD} = -0.1 \ mA$ )           |        | CVOD | —                    | — | 0.15  | Vdc |

| Output Leakage, Hi Z State                                                                                     |        |      |                      |   |       | μA  |

| $(0 \leq V_{OD} \leq V_{M}, I_{BS} = -5.0 \mu\text{A})$                                                        |        | IOZ1 | - 100                | — | + 100 |     |

| $(0 \le V_{OD} \le V_{M}, I_{BS} = -300 \mu\text{A}, F/H = 2.0 \text{V}, OIC = 0.8 \text{V})$                  |        | IOZ2 | - 100                | — | + 100 |     |

NOTES: 2. Algebraic convention rather than absolute values is used to designate limit values. 3. Current into a pin is designated as positive. Current out of a pin is designated as negative. 4. DV<sub>OD</sub> = |V<sub>OD1,2</sub> - V<sub>OD3,4</sub> | where: V<sub>OD1,2</sub> = (V<sub>OHD1</sub> - V<sub>OLD2</sub>) or (V<sub>OHD2</sub> - V<sub>OLD1</sub>), and V<sub>OD3,4</sub> = (V<sub>OHD3</sub> - V<sub>OLD4</sub>) or (V<sub>OHD4</sub> - V<sub>OLD3</sub>). 5. CV<sub>OD</sub> = |V<sub>OHD1</sub> - V<sub>OHD2</sub> | or |V<sub>OHD3</sub> - V<sub>OHD4</sub> |.

DC ELECTRICAL CHARACTERISTICS (Specifications apply over the recommended supply voltage and temperature range, [Notes 2, 3] unless otherwise noted.)

| Characteristic                                                                                                                                                                   | Pins               | Symbol                        | Min   | Тур | Max            | Unit |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|-------------------------------|-------|-----|----------------|------|

| CLAMP DIODES                                                                                                                                                                     |                    |                               |       |     |                |      |

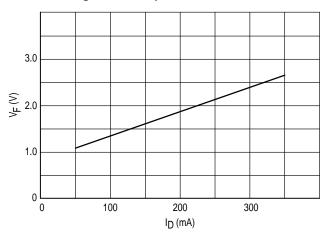

| Forward Voltage<br>(I <sub>D</sub> = 350 mA)                                                                                                                                     | 1, 2, 3,<br>14, 15 | VDF                           | _     | 2.5 | 3.0            | Vdc  |

| Leakage Current (Per Diode)<br>(Pin 1 = 21 V; Outputs = 0 V; I <sub>BS</sub> = 0 μA)                                                                                             |                    | IDR                           | —     | _   | 100            | μA   |

| PHASE A OUTPUT                                                                                                                                                                   |                    |                               |       |     | •              |      |

| Output Low Voltage<br>(I <sub>OA</sub> = 8.0 mA)                                                                                                                                 | 11                 | VOLA                          | _     | _   | 0.4            | Vdc  |

| Off State Leakage Current<br>(V <sub>OHA</sub> = 16.5 V)                                                                                                                         |                    | IOHA                          | _     | _   | 100            | μA   |

| POWER SUPPLY                                                                                                                                                                     |                    |                               |       |     |                |      |

| Power Supply Current<br>( $I_{OD} = 0 \ \mu A, I_{BS} = -300 \ \mu A$ )                                                                                                          | 16                 |                               |       |     |                | mA   |

| $(L1 = V_{OHD}, L2 = V_{OLD}, L3 = V_{OHD}, L4 = V_{OLD})$<br>$(L1 = V_{OHD}, L2 = V_{OLD}, L3 = Hi Z, L4 = Hi Z)$<br>$(L1 = V_{OHD}, L2 = V_{OLD}, L3 = V_{OHD}, L4 = V_{OHD})$ |                    | I <sub>MW</sub><br>IMZ<br>IMN |       |     | 70<br>40<br>75 |      |

| BIAS/SET CURRENT                                                                                                                                                                 |                    | 1                             | •     |     | •              |      |

| To Set Phase A                                                                                                                                                                   | 6                  | IBS                           | - 5.0 | _   | —              | μA   |

### PACKAGE THERMAL CHARACTERISTICS

| Characteristic                                        | Symbol           | Min | Тур | Max | Unit |

|-------------------------------------------------------|------------------|-----|-----|-----|------|

| Thermal Resistance, Junction-to-Ambient (No Heatsink) | R <sub>θJA</sub> | _   | 45  | _   | °C/W |

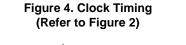

#### AC SWITCHING CHARACTERISTICS (T<sub>A</sub> = + 25°C, V<sub>M</sub> = 12 V) (See Figures 2, 3, 4)

| Characteristic                                | Pins        | Symbol            | Min | Тур | Max | Unit |

|-----------------------------------------------|-------------|-------------------|-----|-----|-----|------|

| Clock Frequency                               | 7           | fCK               | 0   | _   | 50  | kHz  |

| Clock Pulse Width (High)                      | 7           | РWCKH             | 10  | —   | —   | μs   |

| Clock Pulse Width (Low)                       | 7           | PWCKL             | 10  | —   | —   | μs   |

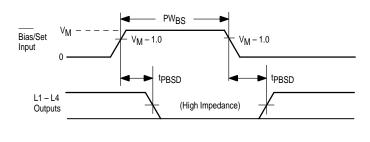

| Bias/Set Pulse Width                          | 6           | PWBS              | 10  | —   | —   | μs   |

| Setup Time (CW/CCW and F/HS)                  | 10–7<br>9–7 | t <sub>su</sub>   | 5.0 | _   | _   | μs   |

| Hold Time (CW/CCW and F/HS)                   | 10–7<br>9–7 | th                | 10  | _   | _   | μs   |

| Propagation Delay (Clk-to-Driver Output)      |             | <sup>t</sup> PCD  | —   | 8.0 | —   | μs   |

| Propagation Delay (Bias/Set-to-Driver Output) |             | <sup>t</sup> PBSD | —   | 1.0 | —   | μs   |

| Propagation Delay (Clk-to-Phase A Low)        | 7–11        | <sup>t</sup> PHLA | _   | 12  | —   | μs   |

| Propagation Delay (Clk-to-Phase A High)       | 7–11        | <sup>t</sup> PLHA | _   | 5.0 | —   | μs   |

NOTES: 2. Algebraic convention rather than absolute values is used to designate limit values. 3. Current into a pin is designated as positive. Current out of a pin is designated as negative.

#### Figure 2. AC Test Circuit

#### Figure 3. Bias/Set Timing (Refer to Figure 2)

Note:  $t_{f}$ ,  $t_{f}$  (10% to 90%) for input signals are  $\leq 25$  ns.

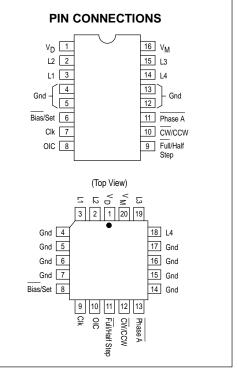

## PIN FUNCTION DESCRIPTION

| Pin N                         | о.              |                                |                  |                                                                                                                                                                                                                                                                                                                              |

|-------------------------------|-----------------|--------------------------------|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 20–Pin                        | 16–Pin          | Function                       | Symbol           | Description                                                                                                                                                                                                                                                                                                                  |

| 20                            | 16              | Power Supply                   | VM               | Power supply pin for both the logic circuit and the motor coil current.<br>Voltage range is + 7.2 to + 16.5 volts.                                                                                                                                                                                                           |

| 4, 5, 6, 7,<br>14, 15, 16, 17 | 4, 5,<br>12, 13 | Ground                         | Gnd              | Ground pins for the logic circuit and the motor coil current. The physical configuration of the pins aids in dissipating heat from within the IC package.                                                                                                                                                                    |

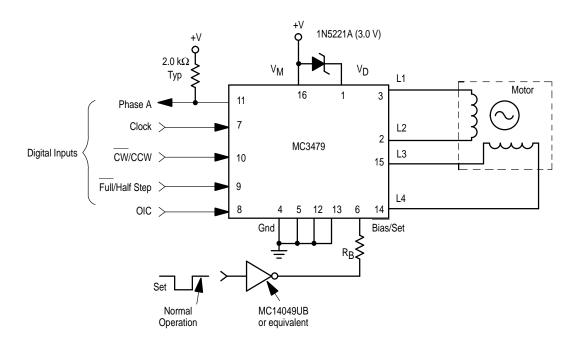

| 1                             | 1               | Clamp Diode<br>Voltage         | VD               | This pin is used to protect the outputs where large voltage spikes may occur as the motor coils are switched. Typically a diode is connected between this pin and Pin 16. See Figure 11.                                                                                                                                     |

| 2, 3,<br>18, 19               | 2, 3,<br>14, 15 | Driver Outputs                 | L1, L2<br>L3, L4 | High current outputs for the motor coils. L1 and L2 are connected to one coil, and L3 and L4 to the other coil.                                                                                                                                                                                                              |

| 8                             | 6               | Bias/Set                       | B/S              | This pin is typically 0.7 volts below V <sub>M</sub> . The current out of this pin (through a resistor to ground) determines the maximum output sink current. If the pin is opened ( $I_{BS} < 5.0 \ \mu$ A) the outputs as <u>sume a high</u> impedance condition, while the internal logic presets to a Phase A condition. |

| 9                             | 7               | Clock                          | Clk              | The positive edge of the clock input switches the outputs to the next position. This input has no effect if Pin 6 is open.                                                                                                                                                                                                   |

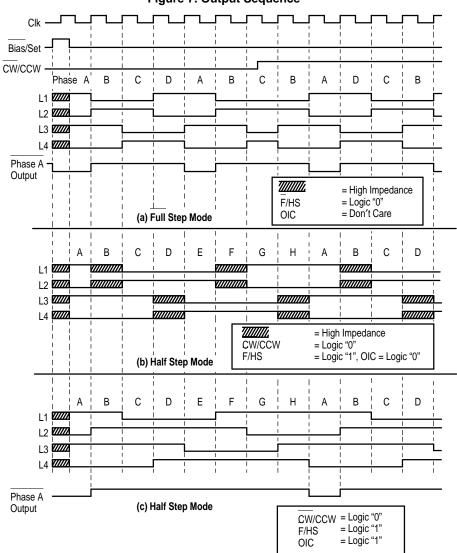

| 11                            | 9               | Full/Half Step                 | F/HS             | When low (Logic "0"), each clock input pulse will cause the motor to rotate one full step. When high, each clock pulse will cause the motor to rotate one-half step. See Figure 7 for sequence.                                                                                                                              |

| 12                            | 10              | Clockwise/<br>Counterclockwise | CW/CCW           | This input allows reversing the rotation of the motor. See Figure 7 for sequence.                                                                                                                                                                                                                                            |

| 10                            | 8               | Output Impedance<br>Control    | OIC              | This input is relevant only in the half step mode (Pin 9 > 2.0 V). When low (Logic "0"), the two driver outputs of the non–energized coil will be in a high impedance condition. When high the same driver outputs will be at a low impedance referenced to $V_M$ . See Figure 7.                                            |

| 13                            | 11              | Phase A                        | Ph A             | This open <u>–collecto</u> r output indicates (when low) that the driver outputs are in the Phase A condition (L1 = L3 = $V_{OHD}$ , L2 = L4 = $V_{OLD}$ ).                                                                                                                                                                  |

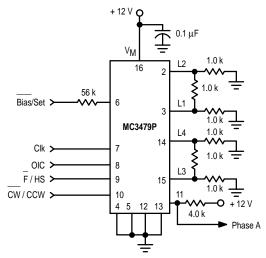

## **APPLICATION INFORMATION**

#### General

The MC3479 integrated circuit is designed to drive a stepper positioning motor in applications such as disk drives and robotics. The outputs can provide up to 350 mA to each of two coils of a two–phase motor. The outputs change state with each low–to–high transition of the clock input, with the new output state depending on the previous state, as well as the input conditions at the logic controls.

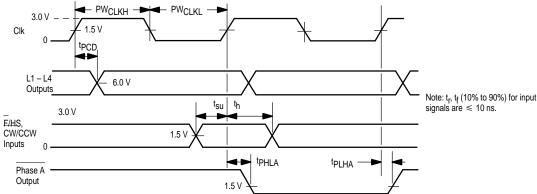

#### Outputs

The outputs (L1–L4) are high current outputs (see Figure 5), which when connected to a two–phase motor, provide two full–bridge configurations (L3 and L4 are not shown in Figure 5). The polarities applied to the motor coils depend on which transistor ( $Q_H$  or  $Q_L$ ) of each output is on, which in turn depends on the inputs and the decoding circuitry.

The maximum sink current available at the outputs is a function of the re<u>sistor</u> connected between Pin 6 and ground (see section on Bias/Set operation). Whenever the outputs are to be in a high impedance state, both transistors ( $Q_H$  and  $Q_L$  of Figure 5) of each output are off.

#### ٧D

This pin allows for provision of a current path for the motor coil current during switching, in order to suppress back–EMF voltage spikes. V<sub>D</sub> is normally connected to V<sub>M</sub> (Pin 16) through a diode (zener or regular), a resistor, or directly. The peaks instantaneous voltage at the outputs must not exceed V<sub>M</sub> by more than 6.0 V. The voltage drop across the internal clamping diodes must be included in this portion of the design (see Figure 6). Note the parasitic diodes (Figure 5) across each Q<sub>L</sub> of each output provide for a complete circuit path for the switched current.

**Figure 6. Clamp Diode Characteristics**

### Full/Half Step

When this input is at a Logic "0" (<0.8 V), the outputs change a full step with each <u>clock</u> cycle, with the sequence direction <u>depending</u> on the CW/CCW input. There are four steps (Phase A, B, C, D) for each complete cycle of the sequencing logic. Current flows through both motor coils during each step, as shown in Figure 7.

When taken to a Logic "1" (>2.0 V), the outputs change a half step with each clock cycle, with the sequence direction depending on the CW/CCW input. Eight steps (Phase A to H) result for each complete cycle of the sequencing logic. Phase A, C, E and G correspond (in polarity) to Phase A, B, C, and D, respectively, of the full step sequence. Phase B, D, F and H provide current to one motor coil, while de-energizing the other coil. The condition of the outputs of the de-energized coil depends on the OIC input, see Figure 7 timing diagram.

#### OIC

The output impedance control input determines the output impedance to the de-energized coil when operating in the half-step mode. When the outputs are in Phase B, D, F or H (Figure 7) and this input is at a Logic "0" (<0.8 V), the two

outputs to the de-energized coil are in a high impedance condition —  $Q_L$  and  $Q_H$  of both outputs (Figure 5) are off. When this input is at a Logic "1" (>2.0 V), a low impedance output is provided to the de-energized coil as both outputs have  $Q_H$  on ( $Q_L$  off). To complete the low impedance path requires connecting  $V_D$  to  $V_M$  as described elsewhere in this data sheet.

#### **Bias/Set**

This pin can be used for three functions: a) determining the maximum output sink current; b) setting the internal logic to a known state; and c) reducing power consumption.

a) The maximum output sink current is determined by the base drive current supplied to the lower transistors (QLs of Figure 5) of each output, which in turn, is a function of IBS. The appropriate value of IBS is determined by:

#### $I_{BS} = I_{OD} \times 0.86$

where  $I_{BS}$  is in microamps, and  $I_{OD}$  is the motor current/coil in milliamps.

Figure 7. Output Sequence

The value of  $\mathsf{R}_\mathsf{B}$  (between this pin and ground) is then determined by:

$$R_{B} = \frac{V_{M} - 0.7 V}{I_{BS}}$$

b) When this pin is opened (raised to V<sub>M</sub>) such that I<sub>BS</sub> is <5.0  $\mu$ A, the internal logic is set to the Phase A condition, and the four driver outputs are put into a high impedance state. The Phase A output (Pin 11) goes active (low), and input signals at the controls are ignored during this time. Upon re–establishing I<sub>BS</sub>. the driver outputs become active, and will be in the Phase A position (L1 = L3 = V<sub>OHD</sub>, L2 = L4 = V<sub>OLD</sub>). The circuit will then respond to the inputs at the controls.

The Set function (opening this pin) can be used as a power–up reset while supply voltages are settling. A CMOS logic gate (powered by  $V_M$ ) can be used to control this pin as shown in Figure 11.

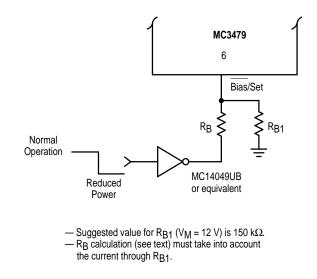

c) Whenever the motor is not being stepped, power dissipation in the IC and in the motor may be lowered by reducing IBS, so as to reduce the output (motor) current. Setting IBS to 75  $\mu$ A will reduce the motor current, but will not reset the internal logic as described above. See Figure 12 for a suggested circuit.

#### **Power Dissipation**

The power dissipated by the MC3479 must be such that the junction temperature (T<sub>J</sub>) does not exceed 150°C. The power dissipated can be expressed as:

$$\mathsf{P} = (\mathsf{V}_\mathsf{M} \times \mathsf{I}_\mathsf{M}) + (2 \times \mathsf{I}_\mathsf{OD}) [(\mathsf{V}_\mathsf{M} - \mathsf{V}_\mathsf{OHD}) + \mathsf{V}_\mathsf{OLD}]$$

where  $V_M =$ Supply voltage;

IM = Supply current other than IOD;

IOD = Output current to each motor coil;

VOHD = Driver output high voltage;

VOLD = Driver output low voltage.

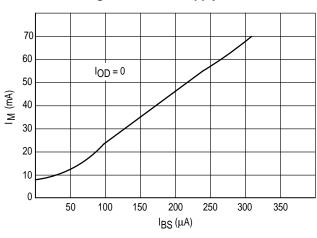

The power supply current  $(I_M)$  is obtained from Figure 8. After the power dissipation is calculated, the junction temperature can be calculated using:

$$T_J = (P \times R_{\theta JA}) + T_A$$

where  $R_{\theta JA}$  = Junction-to-ambient thermal resistance (52°C/W for the DIP, 72°C/W for the FN Package);  $T_A$  = Ambient Temperature.

Figure 8. Power Supply Current

For example, assume an application where  $V_M = 12$  V, the motor requires 200 mA/coil, operating at room temperature with no heatsink on the IC. I<sub>BS</sub> is calculated:

$$I_{BS} = 200 \times 0.86$$

$I_{BS} = 172 \,\mu A$

R<sub>B</sub> is calculated:

$$R_B = (12 - 0.7)$$

V/172 μA

$R_B = 65.7$  kΩ

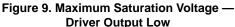

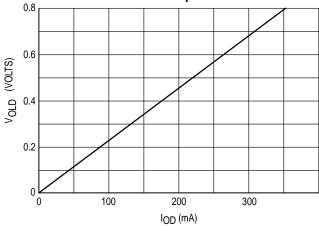

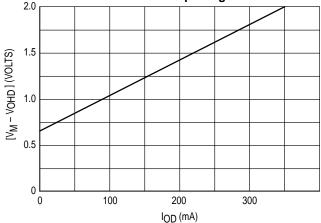

From Figure 8,  $I_M$  (max) is determined to be 40 mA. From Figure 9, VOLD is 0.46 volts, and from Figure 10, (VM-VOHD) is 1.4 volts.

$$P = (12 \times 0.040) + (2 \times 0.2) (1.4 + 0.46)$$

$$P = 1.22 W$$

$$T_J = (1.22 W \times 52^{\circ}C/W) + 25^{\circ}C$$

$$T_J = 88^{\circ}C$$

This temperature is well below the maximum limit. If the calculated T<sub>J</sub> had been higher than 150°C, a heatsink such as the Staver Co. V–7 Series, Aavid #5802, or Thermalloy #6012 could be used to reduce  $R_{\theta JA}$ . In extreme cases, forced air cooling should be considered.

The above calculation, and  $R_{\theta JA}$ , assumes that a ground plane is provided under the MC3479 (either or both sides of the PC board) to aid in the heat dissipation. Single nominal width traces leading from the four ground pins should be avoided as this will increase  $T_J$ , as well as provide potentially disruptive ground noise and  $I_R$  drops when switching the motor current.

#### Figure 10. Maximum Saturation Voltage — Driver Output High

## Figure 11. Typical Applications Circuit

Figure 12. Power Reduction

## MC3479 OUTLINE DIMENSIONS

Motorola reserves the right to make changes without further notice to any products herein. Motorola makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Motorola assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters which may be provided in Motorola data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. Motorola does not convey any license under its patent rights on the rights or other applications intended to support or sustain life, or for any other application in which the failure of the Motorola product could create a situation where personal injury or death may occur. Should Buyer purchase or use Motorola products for any such unintended or unauthorized application, Buyer shall indemnify and hold Motorola and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Motorola was negligent regarding the design or manufacture of the part. Motorola and **(Motorola**) are registered trademarks of Motorola, Inc. is an Equal Opportunity/Affirmative Action Employer.

#### How to reach us:

USA/EUROPE/Locations Not Listed: Motorola Literature Distribution; P.O. Box 20912; Phoenix, Arizona 85036. 1–800–441–2447 or 602–303–5454

MFAX: RMFAX0@email.sps.mot.com - TOUCHTONE 602-244-6609 INTERNET: http://Design-NET.com JAPAN: Nippon Motorola Ltd.; Tatsumi–SPD–JLDC, 6F Seibu–Butsuryu–Center, 3–14–2 Tatsumi Koto–Ku, Tokyo 135, Japan. 03–81–3521–8315

ASIA/PACIFIC: Motorola Semiconductors H.K. Ltd.; 8B Tai Ping Industrial Park, 51 Ting Kok Road, Tai Po, N.T., Hong Kong. 852–26629298