## S<sup>2</sup>ADC<sup>™</sup> - Simultaneous Sampling Analog to Digital Converter

- Patented Simultaneous Sampling of 2 channels (Patent # 5,638,072)

- 12 Bit Resolution

- Single +5Volt Supply

- Internal Reference, 1.25V

- Unipolar 0 to +2.5 Volt Input Range

- Fast, 7.75 µs Conversion Time Both Channels

- Fast Power Shutdown/Turn-On Mode

- 3-Wire Synchronous Serial High Speed Interface

- True Differential Measurements

- 2µA Shutdown Mode (10µW)

- Low Power CMOS 60mW typical

#### **DESCRIPTION**

The **SP8530** is a two channel simultaneous sampling, 12-Bit serial out data acquisition system. The device contains a high speed 12-Bit analog to digital converter, internal reference, and sample/hold circuitry for both channels. The **8530** is available in 16-pin PDIP and SOIC packages, specified over Commercial and Industrial temperature ranges.

<sup>™-</sup>S²ADC is a TRADEMARK OF SIPEX CORPORATION Patent Pending

### **ABSOLUTE MAXIMUM RATINGS**

| (TA=+25°C unless otherwise noted) |                   |

|-----------------------------------|-------------------|

| VDD to DGND                       | 0.3V to +7V       |

| VDA to AGND                       | 0.3V to +7V       |

| Vin to AGND                       | 0.3V to VDA +0.3V |

| Digital Input to VSS              | 0.3V to VDD+0.3V  |

| Digital Output to VSS             | 0.3V to VDD+0.3V  |

| Operating Temp. Range             |                   |

| Commercial (J,K Version)          | 0°C to 70°C       |

| Industrial (A,B Version)          | 40°C to +85°C     |

| Storage Temperature               | 65°C to 150°C     |

| Lead Temperature(Solder 10sec)    | +300°C            |

| Power Dissipation to +70°C        | 500mW             |

| Derate Above 70°C                 | 10mW/ °C          |

CAUTION:

ESD (ElectroStatic Discharge) sensitive device. Permanent damage may occur on unconnected devices subject to high energy electrostatic fields. Unused devices must be stored in conductive foam or shunts.

Personnel should be properly grounded prior to handling this device. The protective foam should be discharged to the destination socket before devices are removed.

## **SPECIFICATIONS**

Unless otherwise noted the following specifications apply for  $V_{DD} = 5V$  with limits applicable for  $T_A = 25^{\circ}C$ .

| PARAMETER                    | MIN. | TYP.         | MAX.          | UNIT  | CONDITIONS                   |

|------------------------------|------|--------------|---------------|-------|------------------------------|

| DC Accuracy                  |      |              |               |       |                              |

| Resolution                   |      | 12           |               | Bits  |                              |

| Integral Linearity           |      |              |               |       |                              |

| J, A                         |      | <u>+</u> 0.6 | <u>+</u> 1.0  | LSB   |                              |

| K ,B                         |      | <u>+</u> 0.4 | <u>+</u> 0.75 | LSB   |                              |

| Differential Linearity Error |      |              |               |       |                              |

| J, A                         |      | <u>+</u> 0.5 | ±1.0          | LSB   | No Missing Codes             |

| K ,B                         |      | <u>+</u> 0.5 | <u>+</u> 1.0  | LSB   | No Missing Codes             |

| Gain Error                   |      |              |               |       |                              |

| J, A                         |      | <u>+</u> 0.2 | <u>+</u> 1.0  | %FSR  | Externally Trimmable to Zero |

| K,B                          |      | <u>+</u> 0.1 | <u>+</u> 0.5  | %FSR  | Externally Trimmable to Zero |

| Offset Error                 |      |              |               |       |                              |

| J, A                         |      | <u>+</u> 4   | <u>+</u> 7    | LSB   | Externally Trimmable to Zero |

| K,B                          |      | <u>+</u> 3   | <u>+</u> 5    | LSB   | Externally Trimmable to Zero |

| Gain Match                   |      |              |               |       |                              |

| J, A                         |      | <u>+</u> 2   |               | LSB   |                              |

| K,B                          |      | <u>+</u> 2   |               | LSB   |                              |

| Offset Match                 |      |              |               |       |                              |

| J, A                         |      | <u>+</u> 1.0 |               | LSB   | Externally Trimmable to Zero |

| K,B                          |      | <u>+</u> 0.5 |               | LSB   | Externally Trimmable to Zero |

| Analog Input                 |      | 0 to 2.5     |               | Volts |                              |

| Conversion Speed             |      |              |               |       |                              |

| Sample Time                  | 400  |              |               | ns    |                              |

| Conversion Time              | 7.75 |              |               | μs    |                              |

| Complete Cycle               | 8.25 |              |               | ,     |                              |

| Simultaneous Convert         |      |              |               |       |                              |

| Rate:                        |      |              | 121           | KHz   | Simultaneous Pair            |

| Clock Speed                  |      |              | 4             | MHz   |                              |

| Data Rate:                   |      |              | 242           | KHz   | Total Data Conversion Rate   |

## **SPECIFICATIONS** (continued)

Unless otherwise noted the following specifications apply for  $V_{DD}$  = 5V with limits applicable for  $T_A$  = 25°C.

| PARAMETER                                 | MIN. | TYP.              | MAX.        | UNIT                          | CONDITIONS                              |

|-------------------------------------------|------|-------------------|-------------|-------------------------------|-----------------------------------------|

| Reference Output                          |      |                   |             | 51111                         |                                         |

| Ref. Out Temp. Coef.<br>J, A<br>K,B       |      | 1.25<br>15<br>10  |             | Volt.Nom.<br>ppm/°C<br>ppm/°C |                                         |

| · ·                                       |      |                   |             | ββιιί, σ                      |                                         |

| Ref.Out Error<br>Output Current           |      | <u>+2</u><br>1    | <u>+</u> 25 | mV<br>mA                      |                                         |

| Digital Inputs<br>Input Low Voltage , VIL |      |                   | 0.8         | Volt Max.                     | VDD=5V <u>+</u> 5%                      |

| Input High Voltage , VIH                  | 2.0  |                   |             | Volt Min.                     | VDD=5V <u>+</u> 5%                      |

| Input Current IIN                         |      | <u>±</u> 1        |             | μΑ                            |                                         |

| Input Capacitance                         |      | 3                 |             | pF Max.                       |                                         |

| Digital Outputs                           |      |                   |             |                               |                                         |

| Data Format                               | 1    | ı<br> 2-Bit Seria | al          |                               | See Timing diagram                      |

| Data Coding                               |      | Binary            |             |                               | See Timing Diagram                      |

| VOH                                       | 4.0  |                   |             | Volt. Min.                    | VDD=5V±5%, IOH=-0.4mA                   |

| VOL                                       |      |                   | 0.4         | Volt Max.                     | VDD=5V±5%, IOL=-1.6mA                   |

| AC Accuracy                               |      |                   |             |                               | fin=47KHz,VDD=5.0V<br>@ 25°C, SCLK=4MHz |

| Spurious Free Dynamic<br>Range (SFDR)     |      | 83                |             | dB                            |                                         |

| Total Harmonic Distortion (THD)           |      | -80               |             | dB                            |                                         |

| Signal to Noise &<br>Distortion (SINAD)   |      | 71                |             | dB                            |                                         |

| Signal to Noise (SNR)                     |      | 72                |             | dB                            |                                         |

| Sampling Dynamics                         |      |                   |             |                               |                                         |

| Acquisition Time to 0.01%                 |      | 200               |             | ns                            | For a <u>+</u> FS step change at input  |

| -3db Small Signal BW                      |      | 13                |             | MHz                           |                                         |

| Aperture Delay                            |      | 35                |             | ns                            |                                         |

| Aperture Jitter                           |      | 150               |             | ps RMS                        |                                         |

| Aperture Delay Matching                   |      | 400               |             | ps                            |                                         |

| Power Supplies<br>VDD                     | 4.75 |                   | 5.25        | Volts                         |                                         |

## **SPECIFICATIONS** (continued)

Unless otherwise noted the following specifications apply for  $V_{pp} = 5V$  with limits applicable for  $T_a = 25$ °C.

| PARAMETER                                            | MIN. | TYP.      | MAX.     | UNIT     | CONDITIONS                                    |

|------------------------------------------------------|------|-----------|----------|----------|-----------------------------------------------|

| Power Supplies Cont.                                 |      |           |          |          |                                               |

| Supply Current<br>Operating Mode                     |      | 11.5      | 17       | mA       | SD=0, VDD=+5.0V                               |

| Shutdown Mode                                        |      | 0.01      | 2        | μΑ       | SD=1                                          |

| Power Dissipation<br>Operating Mode<br>Shutdown Mode |      | 60<br>.05 | 85<br>10 | mW<br>μW | SD=0<br>SD=1                                  |

| Power Turn On                                        |      |           | 20       | μS       | Via Shutdown Control to 1 LSB settling error. |

| Temperature Range                                    |      |           |          |          |                                               |

| Commercial                                           | 0    | to        | +70      | °C       |                                               |

| Industrial                                           | -40  | to        | +85      | °C       |                                               |

| Storage                                              | -65  | to        | +150     | °C       |                                               |

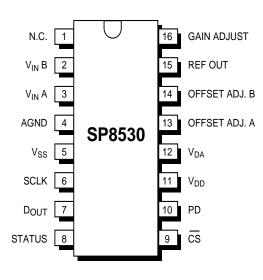

#### **PIN ASSIGNMENTS**

Pin 1-N.C.-No Connection

Pin 2-VIN B-Analog Input B

Pin 3-VIN A- Analog Input A

Pin 4-AGND-Analog Ground

Pin 5-VSS-Digital Ground

Pin 6-SCLK-Serial Clock Input

Pin 7-DOUT Digital Data Output

Pin 8-STATUS- High During Conversion

Pin 9-CS-Chip Select Bar Input High Deselects chip Low Selects chip

Pin 10-SD-Shutdown Input, logic low power up, logic high = powerdown

Pin 11-VDD Digital +5V supply

Pin 12-VDA Analog +5V supply

Pin 13-OffADJ-A External Offset Adjust A

Pin 14-OffADJ-B External Offset Adjust B

Pin 15-REFOUT-Voltage Reference Output

Pin 16-GAINADJ-External Gain Adjustment

#### **FEATURES**

The **SP8530** is a two channel simultaneous sampling, 12-Bit serial out data acquisition system. The device contains a high speed 12-bit analog to digital converter, internal reference, and sample and hold circuitry for both channels. The patented, simultaneous sampling feature of this monolithic integrated circuit, permits the user to measure and convert the analog information on each of two channels at the same

time, thus preserving the relevant temporal information of the applied signals, precisely. This unique feature permits the **SP8530** to ideally fit applications where the information content is carried on dual carriers, such as in-phase and quadrature phase systems. Further, S<sup>2</sup>ADC<sup>TM</sup> architecture permits the sampling of such signals without the necessity of demodulating or further conditioning of the carrier prior to conversion, potentially saving significant amounts of other support electronics. It is also suited to measure instantaneous transfer functions between input signals and their corresponding output signal.

Such measurements are commonly made in test equipment and PIN electronics as well as in many other systems where instantaneous cause and effect relationships are monitored.

The SP8530 permits the user to convert each channel and digitally subtract the result in external logic to produce a precise digital differential result.

The **SP8530** is fabricated in Sipex' Bipolar Enhanced CMOS Process that permits state-of-the-art design using bipolar devices in the analog/linear section and extremely low power CMOS in digital/logic section.

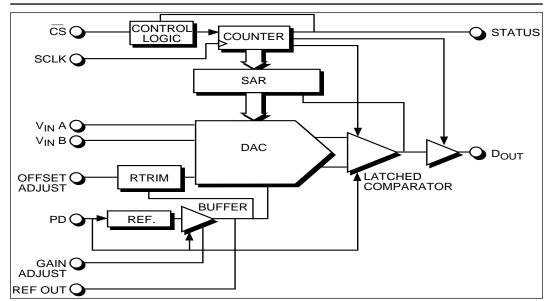

#### **CIRCUIT OPERATION**

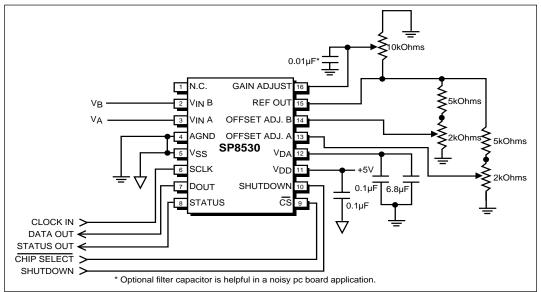

The operating circuit in Figure 1 shows a simple circuit required to operate the **SP8530**. The conversion is controlled by the user supplied signal Chip Select Bar  $(\overline{CS})$  which selects and deselects the device, and a system clock (SCLK).

A high level applied to  $\overline{CS}$  asynchronously clears the internal logic, puts the sample & hold (CDAC) into sample mode and places the DOUT (Data Output) pin in a high impedance state.

Conversion is initiated by falling edge on  $\overline{CS}$  in slave mode at which point the selected input voltages are held and a conversion is started. A delay of 90ns is required between the falling edge of  $\overline{CS}$  and the first rising of SCLK.

Figure 1. Operating Circuit

The device responds to the shut down signal asynchronously so that a conversion in progress will be interrupted and the resulting data will be erroneous. A  $20 \,\mu\text{Sec}$  delay is required between the falling edge of power down and initiation of a conversion.

#### **Data Format**

32 bits of data are sent for each conversion. The first 16 bits are the conversion A result, which is shipped with 4 leading "0"s, and then 12 bits of data, MSB first. The second 16 bits are the conversion B result, which are also shipped with 4 leading "0"s, and then 12 bits of data, MSB first. Data changes on the falling edge of SCLK and is stable on the rising edge of SCLK.

Continuous stand alone operation is obtained by holding  $\overline{CS}$  low. In this mode an oscillator is connected directly to SCLK pin. The SCLK signal along with the STATUS output Signal are used to synchronize the host system with the converter's data. In this mode there is a single dead SCLK cycle between the 32nd clock of one conversion and the first clock of the following conversion for the **SP8530**. A clock frequency of 4 MHz the **SP8530** provides a throughput rate of 121KHz.

In slave mode operation,  $\overline{CS}$  is brought high on each conversion so that all conversions are initiated by falling edge on  $\overline{CS}$ .

#### **Layout Considerations**

Because of the high resolution and linearity of the **SP8530** system design considerations such as ground path impedance and contact resistance become very important.

To avoid introducing distortion when driving the analog inputs of these devices, the source resistance must be very low, or constant with signal level. Note that in the operating circuit there is no connection made between VDA (Pin 12) and the system power supply. This is because the analog supply pin (VDA) is connected internally to the digital supply pin (VDD) through a ten ohm resistor.

This connection when combined with parallel combination of  $6.8\mu F$  tantalum and  $0.1\mu F$  ceramic capacitor between VDA and analog ground, will provide some immunity to noise which resides on the system supply. To maintain maximum system accuracy, the supply connected to the VDD pin should be well isolated from digital supplies and wide load variations.

To limit effects of digital switching elsewhere in a system, it often makes sense to run a separate +5V supply conductor from the supply regulator to any analog components requiring +5V including the **SP8530**. Noise on the power

#### **Layout Considerations (cont.)**

supply lines can degrade the converters performance, especially corrupting are noise and spikes from a switching power supply.

The ground pins (AGND and VSS) on the SP8530 are separated internally and should be connected to each other under the converter. Applying the technique of using separate analog and digital ground planes is usually the best way to preserve dynamic performance and reduce noise coupling into sensitive converter circuits. Where any compromise must be made the common return of the analog input signal should be referenced to the AGND pin of the converter. This prevents any voltage drops that might occur in the power supply's common return from appearing in series with the input signal.

Coupling between analog and digital lines should be minimized by careful layout. For instance, if analog and digital lines must cross they should do so at right angles. Parallel analog and digital lines should be separated from each other by a trace connected to common.

If external gain and offset potentiometers are used, the potentiometers and related resistors should be located as close to the **SP8530** as possible.

#### Minimizing "Glitches"

Coupling of external transients into an analog to digital converter can cause errors which are difficult to debug. In addition to the above discussions on layout considerations, bypassing and grounding, there are several other useful steps that can be taken to get the best analog performance from a system using the SP8530 converters. These potential system problem sources are particularly important to consider when developing a new system, and looking for causes of errors in breadboards.

First, care should be taken to avoid transients during critical times in the sampling and conversion process. Since the **SP8530** has a internal sample/hold function, the signal that puts the device into hold state ( $\overline{CS}$  going low) is critical, as it would be on any sample/hold amplifier. The  $\overline{CS}$  falling edge should have a 5 to 10 ns transition time, low jitter, and have minimal ringing, especially during the first 20ns after it falls.

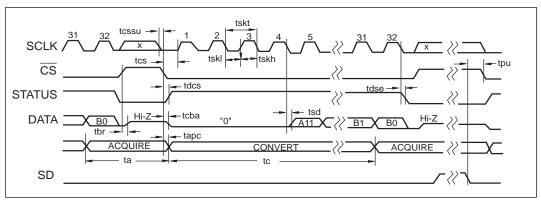

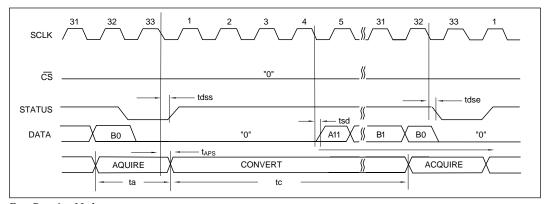

## **TIMING CHARACTERISTICS**

(Typical @ 25°C with V<sub>DD</sub> = +5V, unless otherwise noted)

| PARAMETER                                        | MIN. | TYP. | MAX | .UNIT | COND. |

|--------------------------------------------------|------|------|-----|-------|-------|

| Thoughput Time (tTP=tA+tC)                       | 8.25 | ·    |     | μs    |       |

| Acquisition Time (tA) (2 SCLK Periods)           | 400  | 500  |     | ns    |       |

| Conversion Time (tC) (31 SCLK Periods)           | 7.75 |      |     | μs    |       |

| SCLK Low Pulse Width (tSKL)                      | 110  | 125  |     | ns    |       |

| SCLK High Pulse Width (tSKH)                     | 110  | 125  |     | ns    |       |

| SCLK Period (tSKT)                               | 250  |      |     | ns    |       |

| Buss Access Time (tCBA)                          |      | 51   |     | ns    |       |

| Buss Relinquish Time (tBR)                       |      | 45   |     | ns    |       |

| Setup Time -SCLK Falling to CSN Falling (tCSSU)  | 0    |      |     | ns    |       |

| CSN Low Before SCLK Rises (tCS)                  | 90   |      |     | ns    |       |

| SCLK Falling to Data Valid (tSD)                 |      | 50   |     | ns    |       |

| CSN Falling to status Rising (tDCS)              |      | 69   |     | ns    |       |

| SCLK 33 Falling to Status Rising Free Run (tDSS) |      | 70   |     | ns    |       |

| SCLK32 Falling to Status Falling ( tDSE)         |      | 45   |     | ns    |       |

| Delay SD Low to initiate Conversion (tpu)        |      | 5    |     | μs    |       |

| Aperture Delay Slave-Mode (tAPC)                 |      | 30   |     | ns    |       |

| Aperture Delay Free-Running Mode (tAPS)          |      | 35   |     | ns    |       |

#### **TIMING DIAGRAMS**

Slave Mode

Free Running Mode

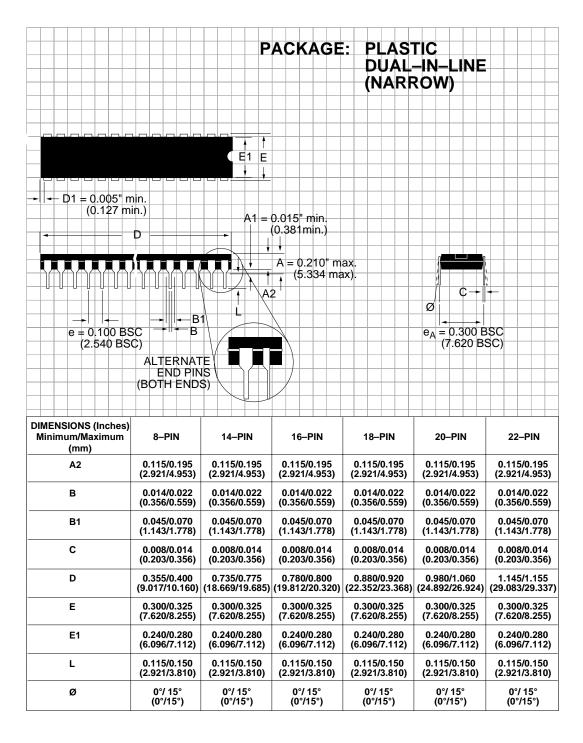

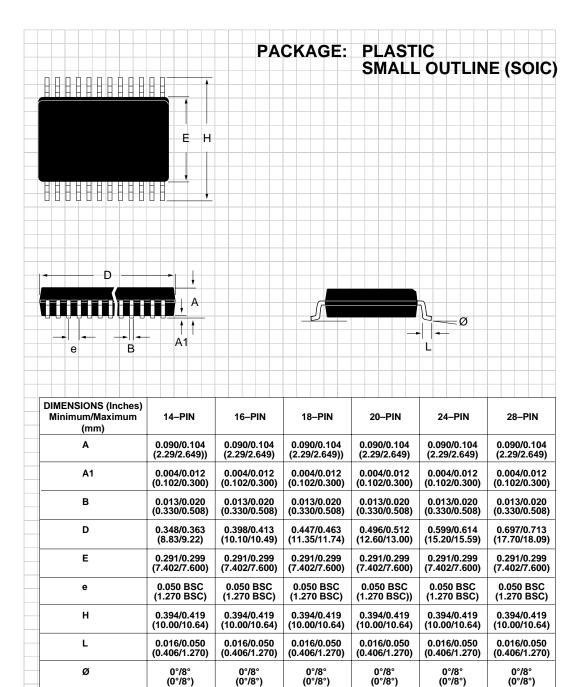

| ORDERING INFORMATION |                     |                   |                          |  |  |

|----------------------|---------------------|-------------------|--------------------------|--|--|

| Model segment        |                     |                   |                          |  |  |

| Model                | INL Linearity (LSB) | Temperature Range | Package Types            |  |  |

| SP8530JN             | ±1.0                | 0°C to +70°C      | 16-pin, 0.3" Plastic DIF |  |  |

| SP8530JS             | ±1.0                | 0°C to +70°C      | 16-pin, 0.3" SOIC        |  |  |

| SP8530KN             | ±0.75               | 0°C to +70°C      | 16-pin, 0.3" Plastic DIF |  |  |

| SP8530KS             | ±0.75               | 0°C to +70°C      | 16-pin, 0.3" SOIC        |  |  |

| SP8530AN             | ±1.0                | 40°C to +85°C     | 16-pin, 0.3" Plastic DIF |  |  |

| SP8530AS             | ±1.0                | 40°C to +85°C     | 16-pin, 0.3" SOIC        |  |  |

| SP8530BN             | ±0.75               | 40°C to +85°C     | 16-pin, 0.3" Plastic DIF |  |  |

| SP8530BS             | ±0.75               | 40°C to +85°C     | 16-pin, 0.3" SOIC        |  |  |

Please consult the factory for pricing and availability on a Tape-On-Reel option.

SIGNAL PROCESSING EXCELLENCE

#### Sipex Corporation

Headquarters and Sales Office 22 Linnell Circle Billerica, MA 01821 TEL: (978) 667-8700 FAX: (978) 670-9001 e-mail: sales@sipex.com

# **Sales Office**233 South Hillview Drive Milpitas, CA 95035 TEL: (408) 934-7500 FAX: (408) 935-7600

Sipex Corporation reserves the right to make changes to any products described herein. Sipex does not assume any liability arising out of the application or use of any product or circuit described hereing; neither does it convey any license under its patent rights nor the rights of others.