# ML2712 2.4GHz RF Transceiver

## **GENERAL DESCRIPTION**

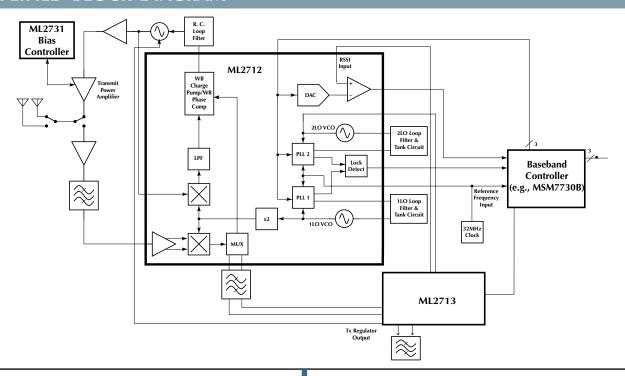

The ML2712 combined with the ML2713 form a FSK (Frequency Shift Keying) 2.4 GHz radio chipset. The ML2712 contains the RF and PLL circuits for a half duplex radio transceiver solution for IEEE802.11 and other wireless communication protocols using the 2.4 GHz ISM band.

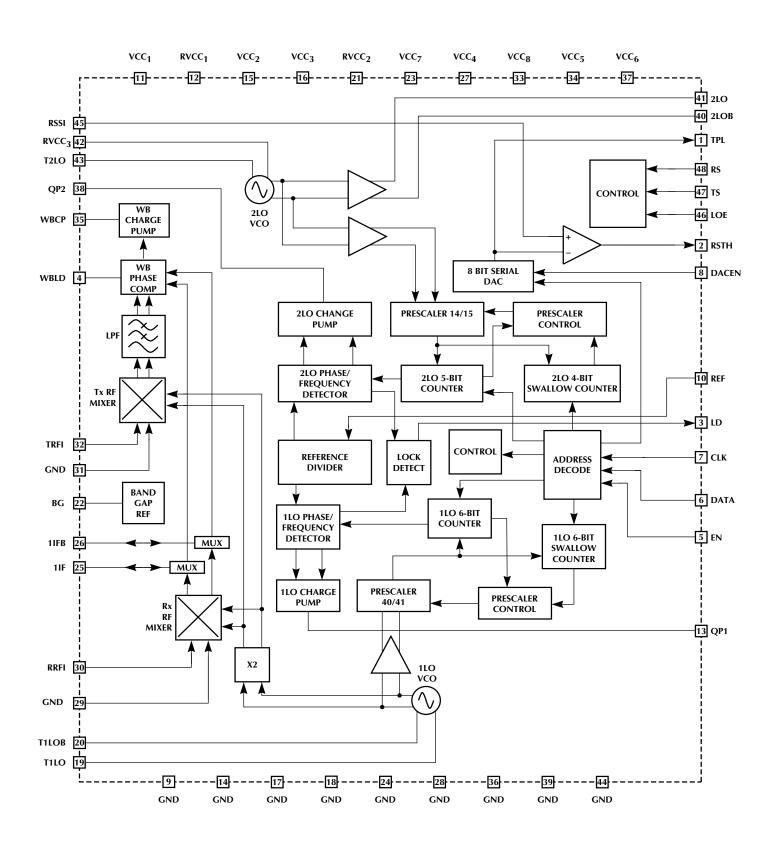

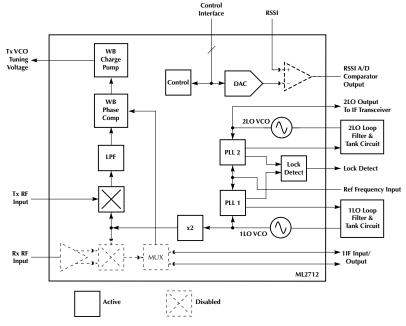

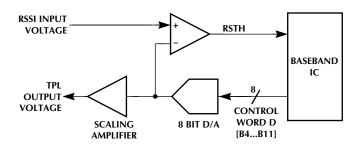

The ML2712 is controlled using a three-wire programming interface and three control lines. The transmit circuits feature an RF down converter for a transmit frequency translation loop and a Wideband Phase Detector for a directly modulated VCO transmitter. An RF down converter mixer is provided for receive. All frequency generation circuits are integrated for the RF conversion, the 1LO VCO and PLL plus a 2LO VCO and PLL for use in dual conversion radios. In addition the ML2712 contains an 8 bit D/A & Comparator that may be used together as a tracking A/D for Received Signal Strength Indication measurement (RSSI).

## FEATURES

- 2.4GHz RF Down Converter

- Programmable 2.2GHz and 236MHz Frequency Synthesizers

- External VCO tank circuits for flexibility

- Compatibility with the OKI MSM7730 and similar baseband controllers

- Transmit Wideband Phase Comparator for closed loop transmitter with >5MHz loop bandwidth

- PLLs Programmable via 3 wire interface

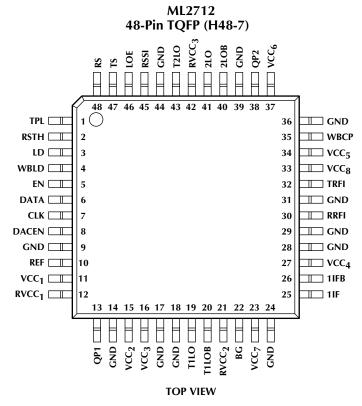

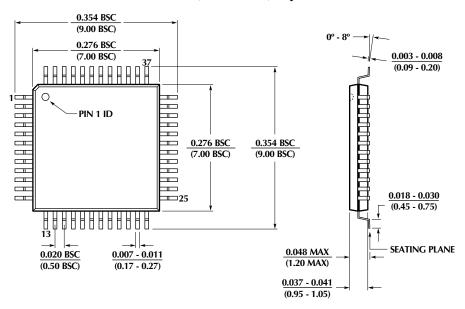

- 48 pin TQFP 7mm body

- 3.0V to 5.5V operation

### **APPLICATIONS**

- 2.4GHz Frequency Shift Key modulated radios

- PC Card & Flashcard Wireless Transceivers

- IEEE802.11FHSS Compatible 1 and 2Mbps Standard

## SIMPLIFIED BLOCK DIAGRAM

### TABLE OF CONTENTS

| General Description        |    |

|----------------------------|----|

| General Description        | 1  |

| Features                   | 1  |

| Applications               |    |

| Block Diagram              |    |

| Pin Descriptions           | 4  |

| Pin Configuration          | 4  |

| Functional Description     |    |

| Introduction               |    |

| Modes of Operation         | 88 |

| Transmit Mode              | 88 |

| Standby Mode               | 88 |

| Receive Mode               |    |

| Overview of PLLs           |    |

| Operating Mode Control     |    |

| Serial Control Bus         |    |

| Electrical Tables          |    |

| Electrical Characteristics |    |

| Absolute Maximum Ratings   | 18 |

| Operating Conditions       |    |

| Physical Dimensions        |    |

| Ordering Information       | 24 |

## **WARRANTY**

Micro Linear makes no representations or warranties with respect to the accuracy, utility, or completeness of the contents of this publication and reserves the right to make changes to specifications and product descriptions at any time without notice. No license, express or implied, by estoppel or otherwise, to any patents or other intellectual property rights is granted by this document. The circuits contained in this document are offered as possible applications only. Particular uses or applications may invalidate some of the specifications and/or product descriptions contained herein. The customer is urged to perform its own engineering review before deciding on a particular application. Micro Linear assumes no liability whatsoever, and disclaims any express or implied warranty, relating to sale and/or use of Micro Linear products including liability or warranties relating to merchantability, fitness for a particular purpose, or infringement of any intellectual property right. Micro Linear products are not designed for use in medical, life saving, or life sustaining applications.

© Micro Linear 2000. is a registered trademark of Micro Linear Corporation. All other trademarks are the property of their respective owners.

Products described herein may be covered by one or more of the following U.S. patents: 4,897,611; 4,964,026; 5,027,116; 5,281,862; 5,283,483; 5,418,502; 5,508,570; 5,510,727; 5,523,940; 5,546,017; 5,559,470; 5,565,761; 5,592,128; 5,594,376; 5,652,479; 5,661,427; 5,663,874; 5,672,959; 5,689,167; 5,714,897; 5,717,798; 5,742,151; 5,747,977; 5,754,012; 5,757,174; 5,767,653; 5,777,514; 5,793,168; 5,798,635; 5,804,950; 5,808,455; 5,811,999; 5,818,207; 5,818,669; 5,825,165; 5,825,223; 5,838,723; 5,844,378; 5,844,941. Japan: 2,598,946; 2,619,299; 2,704,176; 2,821,714. Other patents are pending.

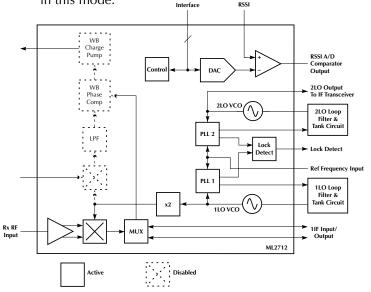

## **BLOCK DIAGRAM**

## PIN CONFIGURATION

| PIN      | DESCRIPTIO       | ONS      |                                                                                                                                                                        |

|----------|------------------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin #    | Signal Name      | I/O Type | Description                                                                                                                                                            |

| Power an | d Ground         |          |                                                                                                                                                                        |

| 11       | VCC <sub>1</sub> |          | Supply Voltage for CMOS Logic. A bypass capacitor connected with minimum trace lengths from VCC <sub>1</sub> to PCB ground is recommended                              |

| 9        | GND              |          | Ground for CMOS Logic                                                                                                                                                  |

| 15       | VCC <sub>2</sub> |          | Supply voltage for Digital/Analog Converter and Comparator. A bypass capacitor connected with minimum trace lengths from VCC <sub>2</sub> to PCB ground is recommended |

| 16       | VCC <sub>3</sub> |          | Supply Voltage for 1LO Prescaler and Phase Detector. A bypass capacitor connected with minimum trace lengths from VCC <sub>3</sub> to PCB ground is recommended        |

| 17       | GND              |          | Ground for 1LO Prescaler and Phase Detector                                                                                                                            |

| 27       | VCC <sub>4</sub> |          | Supply Voltage for RF Amplifier. A bypass capacitor connected with minimum trace lengths from $VCC_4$ to PCB ground is recommended                                     |

| 28       | GND              |          | Ground for RF Low Noise Amplifier                                                                                                                                      |

| 34       | VCC <sub>5</sub> |          | Supply Voltage for Wideband Transmit PLL Charge Pump. A bypass capacitor connected with minimum trace lengths from VCC <sub>5</sub> to PCB ground is recommended       |

| 36       | GND              |          | Ground for Wideband Transmit PLL Charge Pump. Minimizing the lead trace length from this GND to PCB ground to reduce inductance and resistance is recommended          |

| 37       | VCC <sub>6</sub> |          | Supply Voltage for 2LO Charge Pump. A bypass capacitor connected with minimum trace lengths from $VCC_6$ to PCB ground is recommended                                  |

| 39       | GND              |          | Ground for 2LO Charge Pump                                                                                                                                             |

| 23       | VCC <sub>7</sub> |          | Power Supply for 2LO Prescaler and Phase Detector. A bypass capacitor connected with minimum trace lengths from VCC <sub>7</sub> to PCB ground is recommended          |

| Pin #     | DESCRIPTI Signal Name | I/O Type   | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|-----------|-----------------------|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|           |                       | 1/О туре   | •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 24        | GND                   |            | Ground for 2LO Prescaler and Phase Detector                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 33        | VCC <sub>8</sub>      |            | Supply Voltage for Mixers, 1LO Frequency Doubler, and Transmit PLL. A bypass capacitor connected with minimum trace lengths from VCC <sub>8</sub> to PCB ground is recommended                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 29        | GND                   |            | Ground for Mixers, 1LO Frequency Doubler, and Transmit PLL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Regulated | l Power and Gro       | und        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 12        | RVCC <sub>1</sub>     |            | Regulated Bypass Output Supply Voltage for 1LO PLL Charge Pump. A bypass capacitor connected with minimum trace lengths from ${\rm RVCC_1}$ to PCB ground i recommended                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 14        | GND                   |            | Ground for 1LO PLL Charge Pump                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 21        | RVCC <sub>2</sub>     |            | Regulated Bypass Output Supply for 1LO Voltage Controlled Oscillator. A bypass capacitor connected with minimum trace lengths from RVCC <sub>2</sub> to PCB ground is recommended                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 18        | GND                   |            | Ground for 1LO Voltage Controlled Oscillator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 42        | RVCC <sub>3</sub>     |            | Regulated Bypass Output Supply for 2LO Voltage Controlled Oscillator. A bypass capacitor connected with minimum trace lengths from RVCC <sub>3</sub> to PCB ground is recommended                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 44        | GND                   |            | Ground for 2LO Voltage Controlled Oscillator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| ransmitt  | er Section            |            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 32        | TRFI                  | I          | Transmit RF Input signal. This signal, input to the Transmit Down Converter Mixer should be AC coupled and matched to the nominal $50\Omega$ input impedance                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 31        | GND                   |            | Transmit Signal Ground. Minimizing the lead trace length from this GND to PCB ground to reduce inductance and resistance is recommended                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 35        | WBCP                  | O (Analog) | Wideband PLL Charge Pump output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 10        | REF                   | I          | Reference frequency input to Phase Locked Loops. Requires square wave input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 3         | LD                    | O (CMOS)   | Lock Detect output. Low output indicates this pin is in open drain. Two Phase Locked Loops are frequency locked and requires $10k\Omega$ pull-up                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 4         | WBLD                  | O (CMOS)   | Wideband PLL Lock Detect open drain output and requires 10kΩ pull-up                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 41        | 2LO                   | O          | 2LO output. Together with 2LOB provides a balanced 2LO output port for input to Down Converter Mixer on ML2713. Requires 5KΩ external pull-up resistor to VCC3 if not connected to ML2713 In Standby Mode, 2LOB and 2LO provide a calibration tone used to calibrate the ML2713 IF Transceiver                                                                                                                                                                                                                                                                                                                                 |

| 40        | 2LOB                  | О          | 2LOI output. Together with 2LO provide a balanced 2LO output port for input to Down Converter Mixer on ML2713 Requires $5K\Omega$ external pull-up resistor to VCC1 if not connected to ML2713 In Standby Mode, 2LO and 2LOB provide a calibration tone used to calibrate the ML2713 IF Transceiver                                                                                                                                                                                                                                                                                                                            |

| 25        | 1IF                   | I/O        | IF Input/Output. In RECEIVE Mode, functions with 1IFB to present a balanced first IF output port with $340\Omega$ output impedance. Connection must be AC coupled. It is recommended that the signal trace connected to this pin be isolated from other signal or digital control lines to maintain receiver sensitivity In TRANSMIT Mode, functions with 1IFB to present a balanced first IF input port with $340\Omega$ input impedance. Connection must be AC coupled. It is recommended that the signal trace connected to this pin be isolated from othe signal or digital control lines to maintain receiver sensitivity |

|                | DESCRIPTI   |              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|----------------|-------------|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin #          | Signal Name | І/О Туре     | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 26             | 1IFB        | I/O          | IF Input/Output Inverted. In RECEIVE Mode, functions with 1IF to present a balanced first IF output port with $340\Omega$ output impedance. Connection must be AC coupled. It is recommended that the signal trace connected to this pin be isolated from other signal or digital control lines to maintain receiver sensitivity In TRANSMIT Mode, functions with 1IF to present a balanced first IF input port with $340\Omega$ input impedance. Connection must be AC coupled. It is recommended that the signal trace connected to this pin be isolated from other signal or digital control lines to maintain receiver sensitivity |

| Receiver       | Section     |              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 30             | RRFI        | I            | Receive RF Input signal. It is recommended that the nominal input impedance of $20\Omega$ on this pin be matched and be AC coupled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

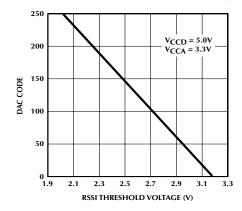

| 45             | RSSI        | I (Analog)   | Received Signal Strength Indicator input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

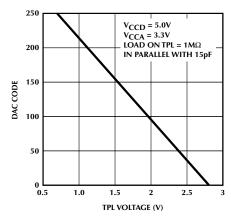

| 1              | TPL         | О            | Digital to Analog Converter high output voltage defined by contents of Control Register E                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 2              | RSTH        | O (CMOS)     | RSSI Threshold output. High output indicates RSSI input is greater than TPL. Digital to Analog Converter output voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 19             | T1LO        | (Tank Port)  | First Local Oscillator Tank circuit. T1LO and T1LOB provide a balanced pair for connection to an external parallel inductor/capacitor tank circuit that determines the frequency of oscillation                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 20             | T1LOB       | (Tank Port)  | Inverted First Local Oscillator Tank circuit. T1LOTB and T1LO provide a balanced pair for connection to an external parallel inductor/capacitor tank circuit that determines the frequency of oscillation                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 13             | QP1         | O            | Charge Pump output of 1LO Phase Locked Loop. Analog output switches between $VCC_2$ and ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 38             | QP2         | O (Analog)   | Charge Pump output of 2LO Phase Locked Loop charge pump output. Analog output switches between VCC <sub>6</sub> and ground as controlled by the phase detector in the 2LO PLL                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 43             | T2LO        | O (Analog)   | Second Local Oscillator Tank circuit. T2LO and GND (pin 44) provide an unbalanced pair for a connection to an external parallel inductor/capacitor tank circuit that determines the frequency of oscillation                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 22             | BG          | I/O (Analog) | Bandgap voltage output. Connection available for bypass capacitor recommended for noise decoupling from Bandgap voltage reference. Recommended capacitance value is 10nF connected to ground                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| <b>Mode Co</b> | ntrol       |              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 46             | LOE         | I (CMOS)     | Local Oscillator Enable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 47             | TS          | I (CMOS)     | Transmit Switch                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 48             | RS          | I (CMOS)     | Receive Switch                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Serial In      | terface     |              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 5              | EN          | I (CMOS)     | Enable serial data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 8              | DACEN       | I (CMOS)     | D/A Converter Enable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 6              | DATA        | I (CMOS)     | Serial Data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 7              | CLK         | I (CMOS)     | Clock input for serial data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

### **FUNCTIONAL DESCRIPTION**

### INTRODUCTION

The ML2712 2.4GHZ RF Transceiver contains all the RF circuitry, including the phase lock loop (PLL), and the active VCO circuits, for a half duplex transceiver. When combined with the ML2713 it enables the design of a high performance 2.4GHz half duplex radio with a fast switching time between transmit and receive modes. This is ideal for applications such as frequency hopping radio for the IEEE 802.11 FH standard.

The ML2712 Transceiver has four modes of operation; 1) Standby 2) Transmit 3) Receive and 4) Sleep. The operating modes of the ML2712 can be programmed through a parallel control interface or through a serial interface. Two serial control interfaces are utilized for programming the PLLs and on chip A/D.

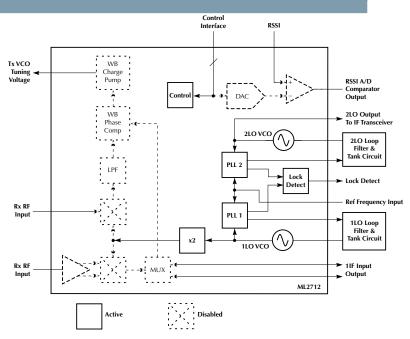

In STANDBY mode all the PLL and VCO circuits are enabled while all the transmitter and receiver circuits are disabled. The use of STANDBY mode is recommended when the PLLs are locking, after the PLL frequencies have been reprogrammed, or after the IC has been transferred out of SLEEP mode.

The transmit circuits include a 2.4GHz RF down converter for transmit frequency translation and a Wideband Phase Detector that implements a directly modulated VCO transmitter radio architecture. The receive section of the ML2712 includes a 2.4GHz RF mixer that down converts the received RF frequency to the first IF frequency; nominally 260MHz. All required frequency generation circuits are integrated on-chip for the RF conversion including the 1LO VCO and the PLL and 1LO frequency doubler. Additionally, a second VCO and PLL provide a 2LO output useable in IF circuits in a dual conversion radio. An 8 bit D/A & Comparator for an RSSI tracking A/D are also integrated on-chip.

The two local oscillator signals generated in the ML2712 are the 1LO with at a typical frequency in the region of 2.2GHz and the 2LO, with a typical frequency of 236MHz. Both signals are phase locked by the independently programmable PLLs to a common external reference frequency. External tank circuits are required for the 1LO and 2LO VCOs to determine the operating frequency ranges. The 1LO signal, generated by doubling the frequency of the 1LO VCO, is used by both the transmit and receive mixer circuits to down convert the 2.4GHz RF signals. The half-frequency 1LO VCO eases tank circuit design and minimizes the VCO pulling when the the radio switches between transmit and receive modes. The differential output from the 2LO VCO is provided for use in radio IF circuits such as the ML2713. A lock detect output indicates when the PLLs are

frequency locked. Programming of the PLL frequency is performed via a three wire serial interface.

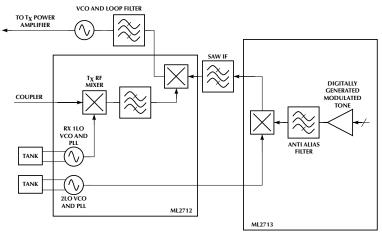

The ML2712 implements a directly modulated VCO transmitter architecture. The elements of this architecture include a Power Amplifier, a transmitter VCO, a transmitter reference generation circuit and a 1IF Wideband PLL which locks the Transmitter VCO to this transmit reference signal. The ML2712 does not integrate the PA but does provide the Wideband PLL and an RF down-convert mixer, enabling the transmit reference signal to be generated at a lower frequency. In TRANSMIT mode the 2.2GHz (nominal) 1LO signal is used to down-convert the 2.4GHz external transmit VCO RF signal. The down converted signal is then phase locked by the on chip wideband phase detector to an externally modulated signal (Transmit reference IF) and output to pins 1IFB and 1IF. The output of the Wideband phase detector controls the transmit VCO frequency (Tx VCO external to IC) via an external loop filter. For a typical application, e.g., IEEE802.11 the symbol rate is 1Msymbol/sec. The lock up time is less than 2µsec. enabling a radio designed with the ML2712 to switch between transmit and receive modes in less than 2µsec.

The ML2712 receiver circuits perform the RF down conversion. A typical receiver design would include the ML2712, an external LNA and RF filter, an IF filter and the ML2713 IF Transceiver. In RECEIVE mode, the ML2712 uses the 1LO signal to down convert the received 2.4 GHz band signal to a nominal 260 MHz IF. The received IF signal is output on 1IF and 1IFO pins. By multiplexing both the transmit and receive signals on one set of pins, only a single Surface Acoustic Wave (SAW) IF channel filter is required in the radio design. A SAW filter with a nominal Gaussian impulse response can be used to provide modulation filtering of the transmit reference IF signal. When in receive mode the A/D and Comparator provide the analog circuits for a tracking A/D converter, intended for RSSI digitization or clear channel assessment for "listen before talk" radios.

In SLEEP mode all circuits, except for the central interface and programming registers, are powered down to minimize power consumption.

### MODES OF OPERATION

### STANDBY MODE

In STANDBY mode all the PLL and VCO circuits are enabled while all the transmitter and receiver circuits are disabled. (see Figigure 1) The use of STANDBY mode is recommended when the PLLs are locking, after the PLL frequencies have been reprogrammed, or after the IC has been transferred out of SLEEP mode. The VCO and PLL circuits are enabled and reach a locked state in 150 usec indicated by an active Lock Detect (LD) signal. The frequency divide ratio settings defined by Control Word C and D (see Table 4) define the frequencies of the 1LO PLL and 2LO PLL.

### TRANSMIT MODE

The ML2712 uses a directly modulated VCO running at the transmitter frequency to generate the transmited signal. The VCO is then free of unwanted spurious signals and has the advantage of requiring no bandpass filtering for the transmitter signal prior to or after the Power Amplifier. The transmitter VCO is phase locked to the center frequency with the transmitter modulation applied. The modulated signal is applied directly to the VCO inside the loop bandwidth of a phase locked loop. To allow modulation rates in excess of 1Mbps requires a very wideband phase detector, capable of operating with loop bandwidths in excess of 5MHz. In this circuit the noise floor is set by the transmit VCO rather than by upconvert mixers. The circuits active in TRANSMIT Mode are shown in Figure 2.

#### **DIRECTLY MODULATED TRANSMIT VCO**

The transmitter is designed to enable a significant amount of power to be generated at the required frequency using a VCO, and is a technique for generating low noise, phase/frequency modulated transmitters without the need for bandpass filtering.

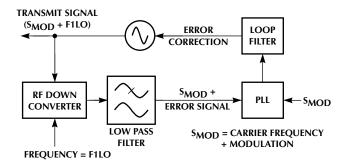

The ML2712 transmitter architecture is shown Figure 3. A tuning voltage applied to the transmit VCO, operating at the final transmission frequency, ensures the correct center frequency before modulation is applied. This closed loop system, uses a PLL with the Transmit VCO phase locked to a modulated reference signal ( $S_{\rm MOD}$ ). The modulated reference signal is generated at 260MHz. The signal from the Transmit VCO is down converted with the 1LO signal, then filtered through a bandpass filter. The output of the filter is fed to the very high-speed phase/ frequency detector Wideband PLL. This compares the down-converted transmit signal with the modulated reference signal  $S_{\rm MOD}$ .

Any frequency or phase error between  $S_{MOD}$  and the down-converted signal is corrected by changing the tuning voltage of the transmit VCO. The down-conversion with the F1LO translates the reference signal  $S_{MOD}$  to the final transmitter frequency.

Figure 1. Standby Mode Active Circuits

**Figure 2. Transmit Mode Active Circuits**

Figure 3. Directly Modulated VCO Transmitter

## MODES OF OPERATION (CONTINUED)

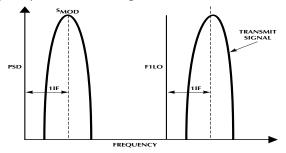

Any modulation on  $S_{MOD}$  is duplicated at the final frequency, provided is it inside the control loop bandwidth. The spectrum of  $S_{MOD}$  and the final output frequency are shown in Figure 4.

Figure 4. Simplified Spectrum of Directly Modulated VCO Transmitter

The PLL loop bandwidth is at least four times that of the modulation rate. Meeting the IEEE802.11 FHSS specification for 1Msymbol/sec requires a PLL control loop bandwidth greater than 4MHz. To achieve the Wideband PLL dynamics and the RF channel spacing requirements, the Transmit VCO is down converted with the 1LO signal (at Frequency F1LO). The RF channel spacing can be achieved by stepping the 1LO VCO. This allows the same VCOs and PLLs to be used in both Transmit and Receive Modes. For typical WLAN operation the receive frequency and transmit frequency are the same (between frequency hops). Therefore the 1LO (and 2LO) frequencies do not require re-tuning when switching from transmit to receive. As a result the transmit to receive turnround time is very rapid. It is determined by the power on, settling, and lock up times of the Wideband PLL. For 802.11 FH systems the requirement is less than 2µsec.

#### TRANSMITTER PLL

The transmitter wideband PLL is shown in Figure 5. An external VCO provides a nominal 2.45GHz signal which is coupled to the Transmit RF mixer using a directional coupler or similar external circuit. The transmiter RF mixer is used to down-convert the transmiter VCO signal using the frequency doubled 1LO VCO to

Figure 5. Wideband Phase Locked

produce a 260MHz (nominal) signal. This signal is fed via a low pass filter to the Wideband Phase Comparator where is it compared to the Transmit IF reference signal, supplied by the ML2713. The Wideband Phase Comparator output controls the transmit VCO via an external loop filter. The bandwidth of the Wideband Phase Comparator is high enough to enable a relatively low tolerance Transmit VCO to be used.

The Transmit RF input is a single ended design with a nominal 50 ohms input impedance. The Transmit RF downconverter and Wideband PLL are only enabled in TRANSMIT Mode.

The Wideband PLL is designed to ensure the Transmit VCO is within the pull-in range of the Wideband PLL (so it will lock when transmitting), to achieve required lock up time, and to set the loop bandwidth. The Wideband PLL loop bandwidth requirement is 4 times the symbol rate at a minimum. The ML2712 is capable of loop bandwidth greater than 5MHz. Since the bandwidth of the Wideband PLL can be >4MHz, the lock up time for 802.11 applications is typically less than 2µsec. The maximum frequency pull-in range for the transmit VCO is 500MHz to ensure that the down-converted signal passes through the low pass filter.

Design of the ML2712 enables the large pull-in frequency in the Wideband PLL. When TS (Pin 47)is asserted the Wideband charge pump output is first clamped to midrail. A PFD detector is then used to ensure frequency lock. Finally the output switches to an XOR detector for accurate phase tracking. After TS is asserted WBCP is clamped to a nominal voltage of mid rail of VQWB (the charge pump supply voltage) for 0.25µsec for 16MHz and 32MHz at the reference input, or 0.2µsec for 20MHz or 40MHz. This pulls the VCO to mid range.

When the clamp is disabled a phase frequency detector (PFD) pulls the VCO to frequency lock for 1 $\mu$ sec with 16 MHz and 32MHz reference input, or 0.8 $\mu$ sec with 20MHz or 40MHz reference input. This rapidly pulls the VCO to frequency lock.

If the Wideband bit (Control Word B b11) is set low, the PFD is then disabled and an XOR phase detector is used until the TS signal is de-asserted. A factor of four difference between the PFD and XOR charge pump currents keeps KD, the phase detector gain, constant. The PFD charge pump current is nominally 2mA and the XOR charge pump current is nominally 0.25mA.

A lock detect output from the Wideband PLL indicates Frequency Lock. An indication of the transmitter not locked is required by some regulatory authorities.

### MODES OF OPERATION (CONTINUED)

### RECEIVE MODE

The circuits active in RECEIVE Mode are shown in Figure 6. All the transmitter circuits are normally disabled in this mode.

**Figure 6. Receive Mode Active Circuits**

#### **RECEIVE RF DOWN-CONVERTER**

The Receive RF input amplifier converts the single ended RF input to a differential signal which is then fed to a mixer. The amplifier and mixer combination down-converts the received RF signal to the receiver 1LO IF (1IF), which is optimized for 260MHz. The output of the down-converter is differential with  $340\Omega$  of output impedance suitable for low loss matching to an external SAW IF filter. The 1IF output ports are bidirectional and are multiplexed with the transmit reference IF input.

#### PLL & VCO CIRCUITS

Two independently programmable PLL circuits control the 1LO and 2LO VCO frequencies. These are programmed via the Serial Control Bus (DATA, CLK, and ENABLE). Program words are clocked into divider or control circuits when ENABLE is asserted. The programming is operational whether the ML2712 is in SLEEP, STANDBY, RECEIVE or TRANSMIT Mode.

The reference signal, REF (Pin 10) typically from an external crystal oscillator, is fed to a programmable reference divider with programmable division ratios of 40, 32, 20 and 16. The reference divider output is fed to both the 2LO and the 1LO phase/frequency detectors.

The polarity of the charge pump output current pulse is programmable to give a positive or negative frequency/voltage control. The value of the current pulses is programmable via the Serial Control Bus. (See Table 7 and 10)

#### 1LO VCO

The 1LO VCO operates at approximately 1.1GHz, and is doubled to a final frequency of 2.2GHz. The 1GHZ VCO signal is connected to the 1LO PLL circuits. The VCO requires an external differential tank circuit design to reduce the effects of frequency pulling due to signal coupling. The tank circuit is tuned by the charge pump output QP1(Pin 13) using a passive external loop filter.

The active circuitry for the 1LO VCO is a differential cross-coupled pair providing a negative resistance across the tank circuit to maintain oscillation. The tank circuit must provide a DC path to RVCC<sub>2</sub> (Pin 21). The layout of this circuit must be kept symmetric to minimize interference or coupling from other circuits in the radio.

#### **2LO VCO**

The 2LO VCO requires an external tank circuit and loop filter. The 2LO VCO is phase locked to provide a fixed frequency, nominally 236MHz. The differential pair 2LO (Pin41) and 2LOB (Pin 40) providedrive to the ML2713. The 2LO differential outputs are from the collectors of a differential pair that require a pull-up to a nominal 2.3V, normally provided by the ML2713.

A calibration tone added to the 2LO output in STANDBY Mode is intended for aligning filters and discriminators in the IF circuits of the ML2713. The calibration tone is an 8MHz square wave with a 16MHz or 32MHz reference input, or a 10MHz square wave with af 20MHz or 40MHz reference input.

The 2LO VCO is a cross-coupled pair, with one base connected to RVCC<sub>3</sub> (Pin 42) (2LO supply voltage). The other base is connected to an external tank circuit through T2LO (Pin 43). This design presents a negative impedance across the tank circuit. Since a dominant oscillation, due to bond wire inductance and parasitic capacitance on the PCB, can lead to high frequency oscillation (of the order of 1GHz), the circuit must be carefully laid out. The 2LO tank circuit must provide a DC path from T2LO to RVCC<sub>3</sub> (Pin 42).

## MODES OF OPERATION (CONTINUED)

### **OVERVIEW OF PLLS**

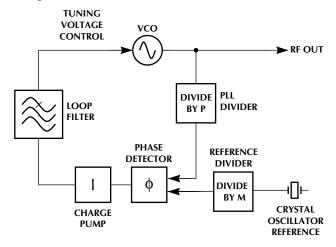

Control words programmed via the Serial Control Bus set the ML2712 PLL reference frequency divider, and the 2LO PLL and 1LO PLL signal dividers division ratios. For illustration a simple PLL is shown in Figure 7.

Figure 7. Simple PLL

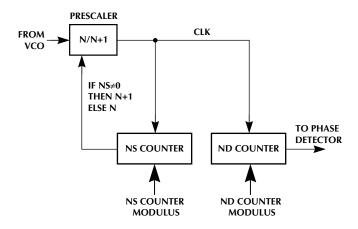

The simplified signal divide by P (Figure 7) uses a dual modulus (or swallow pulse) prescaler system.

Figure 8 shows a dual modulus signal divider. This type of PLL is able to divide by two integers, N and N+1. ND & NS, are clocked in parallel by pulses from the prescaler, which is initially set to N+1. The ND & NS registers are programmed via the Serial Control Bus. The signal divider ratio achieved by this system is given by the equation:

$R_{SD} = N \times ND + NS$ . ND must be greater than NS.

Figure 8. Dual Modulus Signal Divider

The output of the signal divider is compared with the 500 kHz comparison frequency from the reference divider in the phase detector. In the PLL (Fig. 8) the tuning voltage to the VCO is adjusted until phase locking occurs. At this point the VCO frequency in MHz will be given by the equation:

$$f = (N \times ND + NS) \times (f_R/M).$$

Note that since both PLL signal divider and reference divider are subject to an extra divide by two stage, they may be neglected in the equations. However, it is important to note that the comparison frequency in MHz in both the 1LO and the 2LO PLL is given by  $f_C = f_R/2M$ .

### DAC AND RSSI COMPARATOR

The DAC can be used to generate a voltage output to control the transmit power in an external power amplifier (PA). The DAC and Comparator can also be used to form an RSSI threshold circuit or an RSSI tracking A/D in conjunction with external baseband circuits. The DAC is programmed via the Serial Control Bus using either the DACEN or the EN control line. The DAC may be programmed at serial clock rates up to 16MHz.

#### **SLEEP MODE**

In SLEEP Mode only the control circuits are active. These circuits are static CMOS and consume minimal current when there is no interface activity.

## **CONTROL INTERFACES**

### **OPERATING MODE CONTROL**

A parallel control interface dynamically controls the four different Modes of operation. The control lines TS (Pin 47), RS (Pin 48) and LOE (Pin 46) enable the PLLs, VCOs, transmitter and receiver circuits. The relationship between this control interface, the Modes of operation and the functioning of the circuits are described in Table 1. The function of this control interface can be duplicated via the Serial Control Bus, and the circuits enabled in STANDBY, RECEIVE and TRANSMIT can be programmed via the Serial Control Bus.

| RS                    | TS                   | LOE  | Mode     | IC Status                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|-----------------------|----------------------|------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| High                  | High                 | High | SLEEP    | All radio circuits are off. Static CMOS control circuits are active, consuming minimal current but permitting the register settings to be changed via the baseband controller IC. Registers store power-up default or previously programmed values on serial control lines. The baseband IC may configure the radio, while the radio is neither transmitting nor receiving data, but the ML2712 will maintain the last programmed values. Note that in SLEEP Mode the operating Mode control may be overridden by the Serial Control Bus if parallel control interface is not required. |

| High                  | High                 | Low  | Standby  | Only the VCO and PLL circuits are enabled in this mode and will be locked within 150µsec. This will be flagged by an LD (lock detect) signal. The frequency divide ratio settings will cause the two PLLs to lock to the desired frequencies. In this mode the 2nd LO output signal can have a calibration signal added to the 2LO VCO signal. This calibration signal is used for discriminator alignment on the ML2713. The 8 bit DAC and associated comparator circuit are enabled.                                                                                                  |

| Low                   | Low High Low RECEIVE |      | RECEIVE  | The Receive RF down-converter, 1LO PLL & VCO, 2LO PLL & VCO, RSSI DAC, and RSSI comparator are all enabled, although for maximum flexibility any of these circuits could be disabled via the Serial Control Bus.                                                                                                                                                                                                                                                                                                                                                                        |

| High Low Low TRANSMIT |                      |      | TRANSMIT | The Transmit RF down-converter, Wideband PLL, 1LO PLL & VCO, 2LO PLL & VCO, and RSSI D/A are all enabled, although for maximum flexibility any of these circuits could be disabled via the Serial Control Bus                                                                                                                                                                                                                                                                                                                                                                           |

**Table 1. Operating Mode ControlStates**

### SERIAL CONTROL BUS

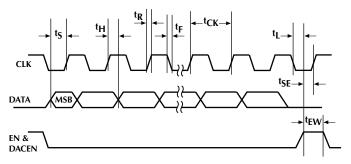

The ML2712 contains two 3-wire serial control interfaces. They have common clock and data, but separate latch enable controls (EN & DACEN). The EN signal programs the registers that determine the operation of the PLLs, VCOs and DAC, and determines which circuits are active in STANDBY, RECEIVE and TRANSMIT Modes. The DACEN signal is dedicated to DAC programming only. Serial bus control is active in all operating Modes. The serial control interface overrides the parallel mode control interface. See Table 2 and Figure 9.

All DATA bits are clocked into the ML2712 while EN or DACEN is low and loaded into the addressed latch on the low to high trailing edge of the EN or DACEN pulse. The serial bus control register only retains the last 16 bits of data that follow either the EN or DACEN pulse. The data latches are fully static CMOS and use minimal power when the Serial Control Bus is inactive.

All Serial Control Bus words are entered data MSB first. The word is made up of data and address fields. The data field is the leading 13 bits and the last 3 bits are the address field (see Table 3). The address field determines the destination register for the data field. There are 5 control registers (CONTROL WORDs A, B, C, D, and E) defined in Table 4. When data is latched by a DACEN pulse the address field is ignored and the data field is always used to program the 8-bit DAC. In Tables 3 and 4 the left-most bit isalways the MSB.

EN or DACEN are enabled to latch data into the DAC register as determined by the DCE control bit, b4 in Control Word B. When DCE is set to 0, the default power up state, the EN latch enable pulse is active and the DACEN pulse is disabled. In this state a rising edge on EN will write data to the 8-bit DAC when the address field is correct. Other control words may be written using different address fields as shown in Table 4. When DCE is set to 1 both DACEN and EN

pulses are active and either may be used to latch control words, although not simultaneously. In this mode DACEN will write data to the 8-bit DAC regardless of the address data. The EN pulse will continue to operate as described for DCE set to 0.

The ML2712 default power up condition is designed for normal operation. At power up the registers are programmed as in Table 4. The user may adjust the mode of operation for specific tasks by programming the control register settings immediately after power up, or at an appropriate time during operation. Note that address field 000 is reserved for test modes and should not be programmed in normal operation.

Figure 9. Control Bus Timing

|                 | Parameter           | Min | Тур | Max | Units |  |

|-----------------|---------------------|-----|-----|-----|-------|--|

| CLK             |                     |     |     |     |       |  |

| t <sub>R</sub>  | Rise time           |     |     | 15  | ns    |  |

| t <sub>F</sub>  | Fall time           |     |     | 15  | ns    |  |

| t <sub>CK</sub> | Period              | 50  |     |     | ns    |  |

| EN & DACEN      |                     |     |     |     |       |  |

| t <sub>EW</sub> | Pulse width         | 2   |     |     | ns    |  |

| $t_{_{L}}$      | Falling edge delay  | 15  |     |     | ns    |  |

| t <sub>se</sub> | Rising edge setup   | 15  |     |     | ns    |  |

| DATA            |                     |     |     |     |       |  |

| t <sub>s</sub>  | Data-to-Clock Setup | 15  |     |     | ns    |  |

| t <sub>H</sub>  | Data-to-Clock Hold  | 15  |     |     | ns    |  |

**Table 2. Three Wire Bus Interface Timing Characteristics**

| Field    |            | DATA                       |            |           |           |           |           |           |           |           |           | ADDRESS   |           |          |          |          |

|----------|------------|----------------------------|------------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|----------|----------|----------|

| bit      | 0          | 1 2 3 4 5 6 7 8 9 10 11 12 |            |           |           |           |           |           | 13        | 14        | 15        |           |           |          |          |          |

| Function | Data<br>12 | Data<br>11                 | Data<br>10 | Data<br>9 | Data<br>8 | Data<br>7 | Data<br>6 | Data<br>5 | Data<br>4 | Data<br>3 | Data<br>2 | Data<br>1 | Data<br>0 | Add<br>3 | Add<br>2 | Add<br>1 |

Table 3. Format of Serial Control Bus data

| Data             | b0  | b1  | b2     | b3     | b4      | b5    | b6                       | <b>b</b> 7 | b8       | b9             | b10      | b11 | b12 | b13 | b14     | b15 |

|------------------|-----|-----|--------|--------|---------|-------|--------------------------|------------|----------|----------------|----------|-----|-----|-----|---------|-----|

| Control Word A   | VC1 | VC2 | PLL1   | PLL2   | CP1     | CP2   | PP1                      | PP2        | LD1      | LD2            | PPW      | РВ  | х   |     |         |     |

| Power Up Default | 1   | 1   | 1      | 1      | 1       | 1     | 1                        | 1          | 1        | 1              | 1        | 1   | х   | 0   | 0       | 1   |

| Control Word B   | TX  | RX  | LBC    | DAC    | DCE     | СОМ   | CI1                      | CI2        | CI3      | CI4            | CAL      | WB  | х   |     |         |     |

| Power Up Default | 0   | 0   | 0      | 1      | 0       | 1     | 1                        | 1          | 1        | 1              | 1        | 1   | х   | 0   | 1       | 0   |

| Control Word C   |     | MSB | ILO NE | 1 Coun | ter LSB |       | MSB 1LO NS1 Swallow Cou  |            |          |                | ounter l | _SB | х   |     | Address | ,   |

| Power Up Default | 1   | 1   | 0      | 1      | 1       | 0     | 0                        | 1          | 0        | 1              | 0        | 0   | х   | 0   | 1       | 1   |

| Control Word D   | MSB | 2LO | ND2 Co | ounter |         | MSB 2 | 2LO NS2 Counter<br>B LSB |            |          | Reference Div. |          |     | Х   |     | Address |     |

| Power Up Default | 1   | 0   | 0      | 0      | 0       | 1     | 1                        | 0          | 0        | 0              | 0        | 1   | х   | 1   | 0       | 0   |

| Control Word E   | х   | х   | х      | х      | MSB     |       | 8                        | -bit DA    | C Voltag | ge             |          | LSB | х   | ·   | Address | ,   |

| Power Up Default | х   | х   | х      | х      | 0       | 0     | 0                        | 0          | 0        | 0              | 0        | 0   | x   | 1   | 0       | 1   |

Table 4. Control Word Settings on the Serial Control Bus

|     | Control Bit in CONTROL WORD A |      |      |     |     |         | ML2712 Circuits Enabled |              |            |                    |                    |  |

|-----|-------------------------------|------|------|-----|-----|---------|-------------------------|--------------|------------|--------------------|--------------------|--|

| VC1 | VC2                           | PLL1 | PLL2 | CP1 | CP2 | 1LO VCO | 2LO VCO                 | 1LO PLL      | 2LO PLL    | 1LO Charge<br>Pump | 2LO Charge<br>Pump |  |

| 0   | 0                             | 0    | 0    | 0   | 0   | ALL OFF |                         |              |            |                    |                    |  |

| 1   | х                             | х    | х    | х   | х   | ON      | х                       | х            | х          | х                  | х                  |  |

| Х   | 1                             | Х    | Х    | Х   | х   | х       | ON                      | х            | х          | х                  | х                  |  |

| Х   | Х                             | 1    | х    | х   | х   | х       | х                       | ON           | х          | х                  | х                  |  |

| Х   | х                             | х    | 1    | х   | х   | х       | х                       | х            | ON         | х                  | х                  |  |

| Х   | Х                             | Х    | Х    | 1   | х   | х       | х                       | х            | х          | ON                 | х                  |  |

| Х   | х                             | х    | х    | х   | 1   | х       | х                       | х            | х          | х                  | ON                 |  |

| 1   | 1                             | 1    | 1    | 1   | 1   |         | ALL ON                  | N (DEFAULT F | POWER UP C | CONDITION)         |                    |  |

Table 5. VCO, PLL and Charge Pump Power Control Modes

#### **CONTROL WORD A**

Control Word A enables the VCOs, PLL dividers, PLL charge pumps and voltage reference circuits; programs the polarity of PLL charge pumps; and programs the function of the Lock Detect (LD) output.

### Control Bits VC1, VC2, PLL1, PLL2, CP1, CP2

Two frequency synthesizers, 1LO and 2LO, each contain a VCO and a PLL. This dual conversion superheterodyne receiver uses the two local

oscillators to down convert the 2450 MHz ISM Band RF signal. (Table 5).

All these circuit components are enabled individually using CONTROL WORD A as defined in Table 4. For the PLLs to operate, all control bits must be set to 1.

#### **Control Bits LD1 & LD2**

The PLLs indicate their lock status using the Lock Detect output (LD Pin 3). Control bits LD1 & LD2 program the indication of frequency lock on 1LO, 2LO, or both 1LO and 2LO, as shown in Table 6.

| Contro | ol Mode  | LOS            | itatus   |               |                              |

|--------|----------|----------------|----------|---------------|------------------------------|

| LD1    | LD2      | 1LO            | 2LO      | LD Pin output | Mode of Operation            |

| 0      | 0        | Х              | Х        | 1             | Output disabled              |

| 0      | 1        | unlocked       | unlocked | 0             |                              |

| 0      | 1        | locked         | unlocked | 0             | 1LO lock indication          |

| 1      | unlocked | locked         | 0        | 1             | TEO TOCK ITICICATION         |

| locked | locked   |                |          |               |                              |

| 1      | 0        | unlocked       | unlocked | 0             |                              |

| 1      | 0        | locked         | unlocked | 0             | 21 O lock indication         |

| 1      | 0        | unlocked       | locked   | 1             | 210 lock indication          |

| 1      | 0        | locked         | locked   | 1             |                              |

| 1      | 1        | unlocked unloc |          | 0             |                              |

| 1      | 1        | locked         | unlocked | 0             | 2LO & 1LO lock<br>indication |

| 1      | 1        | unlocked       | locked   | 0             | muication                    |

| 1      | 1        | locked         | locked   | 1             |                              |

**Table 6. Lock Detect Mode**

#### Control Bits PP1, PP2 & PPW

In each PLL a charge pump or switched current source either sinks or sources a current pulse depending on the error signal at the phase detector. lif the divided VCO frequency at the phase detector is greater than the reference frequency, the charge pump will source a current pulse. The current pulse is fed to an external loop filter serving as an integrator or current reservoir. The result is the voltage across the loop filter and the tuning voltage to the VCO increasing or decreasing depending on the loop filter being referenced to ground or the power supply. The polarity of charge pumps within the PLL and transmit wideband PLL (WBPLL) may be programmed using CONTROL WORD A as shown in Table 7. The charge pump current settings in Table 10 assume that the external loop filter is reference to ground.

#### **Control Bit PB**

A band-gap voltage reference is used to control bias levels. Control Bit PB in CONTROL WORD A controls this internal voltage reference. For any circuits to operate, other than the control interfaces, this bit must equal 1.

#### **CONTROL WORD B**

Control Word B changes the control mode in which ML2712 operates. CONTROL WORD B may also be used to program charge pump current level and enable the DAC, Comparator & calibration circuits.

### Control Bits TX, RX & LBC

The Mode of operation can be controlled via the serial interface (which disables the parallel operating mode interface). This option reduces the pin count requirement for a baseband controller. Individual circuit blocks may all be toggled on or off using control words. Extra control mode bits, TX & RX in CONTROL WORD B, are provided to enable transmit and receive switching via the Serial Control Bus interface. These control bits are enabled by the LBC control bit as shown in Table 8. Individual circuit blocks may be controlled by the Serial Control Bus control interface during LBC = 1 mode. When LBC = 1 the control lines TS (pin 47) and RS (pin 48), are ignored and the Mode of operation is determined by the TX and RX bit in Control Word D.

| _  | ontrol Bit<br>TROL WO |     | Control Status                                             |

|----|-----------------------|-----|------------------------------------------------------------|

| TX | RX                    | LBC |                                                            |

| Х  | Х                     | 0   | Parallel Control Interface<br>(Default Power on condition) |

| 0  | 0                     | 1   | Serial control - Tx & Rx circuits off                      |

| 0  | 1                     | 1   | Serial control - Rx circuits on                            |

| 1  | 0                     | 1   | Serial control - Tx circuits on                            |

| 1  | 1                     | 1   | Serial control - Tx & Rx circuits off                      |

Table 8. Parallel Control Over-Ride Using LBC Bit

|     | Bit in CO<br>WORD |     | ML2712 Charge Pump Polarity                 |                                             |                                              |  |  |  |  |

|-----|-------------------|-----|---------------------------------------------|---------------------------------------------|----------------------------------------------|--|--|--|--|

| PP1 | PP2               | PPW | 1LO Charge pump polarity                    | 2LO Charge pump polarity                    | WBPLL Charge pump polarity                   |  |  |  |  |

| 1   | х                 | х   | Frequency signal > Frequency ref. Pump high | х                                           | х                                            |  |  |  |  |

| 0   | х                 | х   | Frequency signal > Frequency ref. Pump low  | x                                           | x                                            |  |  |  |  |

| х   | 1                 | х   | x                                           | Frequency signal > Frequency ref. Pump high | Х                                            |  |  |  |  |

| х   | 0                 | х   | х                                           | Frequency signal > Frequency ref. Pump low  | Х                                            |  |  |  |  |

| х   | х                 | 1   | х                                           | x                                           | Frequency signal > Frequency ref.  Pump high |  |  |  |  |

| х   | х                 | 0   | х                                           | x                                           | Frequency signal > Frequency ref.  Pump low  |  |  |  |  |

**Table 7. Charge Pump Polarity**

### Control Bits DAC, COM & DCE

The DAC and comparator may be used as a tracking ADC circuit. In normal operation these circuits are available in TRANSMIT, RECEIVE & STANDBY operating Modes. However, independent control of the comparator and DAC is available via control bits as shown in Table 9. There are two other modes available to program the DAC. When DCE in CONTROL WORD B is set to 0, EN is active and DACEN is disabled. With DCE at 1 both the DACEN and EN pins are active. DACEN and EN cannot be simultaneously low. With DCE at 1 a rising edge on DACEN will write data to the 8-bit DAC regardless of the address data.

| Control Bit in<br>CONTROL<br>WORD B |     | Circuits Enabled                             |

|-------------------------------------|-----|----------------------------------------------|

| DAC                                 | СОМ |                                              |

| 1                                   | 1   | DAC & Comparator on (Default power up state) |

| 0                                   | 1   | DAC off, Comparator on                       |

| 1                                   | 0   | DAC on, Comparator off                       |

| 0                                   | 0   | DAC & Comparator off                         |

Table 9. Control of ML2712 DAC & Comparator

#### Control Bits CI1, CI2, CI3, CI4

The PLLs each contain a charge pump. The magnitude of the current in these pumps may be controlled as defined in Table 10. The recommended values for best phase detector performance are [CI1,CI2]=[1,0] or [1,1] and [CI3,CI4] = [1,0] or [1,1].

#### **Control Bit CAL**