# Preliminary Information

# Clock Generator for PowerQUICC and PowerPC Microprocessors

The MPC9855 is a PLL based clock generator specifically designed for Freescale Microprocessor and Microcontroller applications including the PowerPC and PowerQUICC. This device generates a microprocessor input clock. The microprocessor clock is selectable in output frequency to any of the commonly used microprocessor input and bus frequencies. The device offers eight low skew clock outputs in two banks, each configurable to support different clock frequencies. The extended temperature range of the MPC9855 supports telecommunication and networking requirements.

## Features

- 8 LVCMOS outputs for processor and other circuitry

- Crystal oscillator or external reference input

- 25 or 33 MHz Input reference frequency

- Selectable output frequencies include = 200, 166, 133,125, 111, 100, 83, 66, 50, 33, or 16 MHz

- Buffered reference clock output (2 copies)

- · Low cycle-to-cycle and period jitter

- 100-lead PBGA package

- 100-lead Pb-free Package Available

- 3.3 V supply with 3.3 V or 2.5 V LVCMOS output supplies

- · Supports computing, networking, telecommunications applications

- Ambient temperature range –40°C to +85°C

- 100-lead PBGA package

- 100-lead Pb-free Package Available

## **Functional Description**

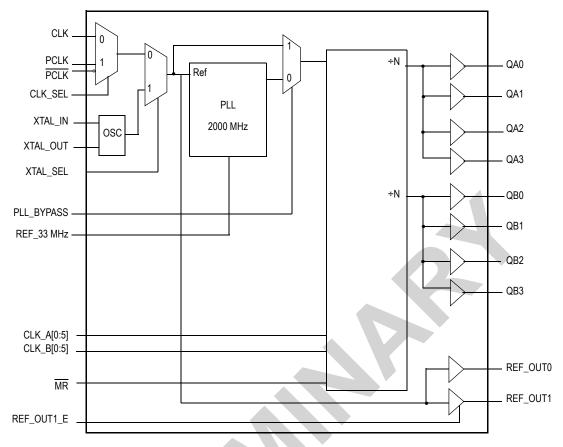

The MPC9855 uses either a 25 or 33 MHz reference frequency to generate 8 LVCMOS output clocks, of which, the frequency is selectable from 16 MHz to 200 MHz. The reference is applied to the input of a PLL and multiplied to 2 GHz. Output dividers, divide this frequency by 10, 12, 15, 16, 18, 20, 24, 30, 40, 60, or 120 to produce output frequencies of 200, 166, 133, 125, 111, 100, 83, 66, 50, 33, or 16 MHz. The single-ended LVCMOS outputs provide 8 low skew outputs for use in driving a microprocessor or microcontroller clock input as well as other system components. The input reference, either crystal or external input is also buffered to a separate dual outputs that my be used as the clock source for a Ethernet PHY if desired.

The reference clock may be provided by either an external clock input of 25 or 33 MHz. An internal oscillator requiring a 25 MHz crystal for frequency control may also be used. The external clock source my be applied to either of two clock inputs and selected via the CLK\_SEL control input. Both single ended LVCMOS and differential LVPECL inputs are available. The crystal oscillator or external clock input is selected via the input pin of XTAL\_SEL. Other than the crystal, no external components are required for crystal oscillator operation. The REF\_33 MHz configuration pin is used to select between a 33 and 25 MHz input frequency.

The MPC9855 is packaged in a 100 lead MAPBGA package to optimize both performance and board density.

| ORDERING INFORMATION |                                     |         |                 |  |  |  |  |  |  |

|----------------------|-------------------------------------|---------|-----------------|--|--|--|--|--|--|

| Device               | Device Temp. Range Case No. Package |         |                 |  |  |  |  |  |  |

| MPC9855              | –40°C to +85°C                      | 1462-01 | 100 lead MAPBGA |  |  |  |  |  |  |

Figure 1. MPC9855 Logic Diagram

Table 1. Pin Configurations

| Pin                                            | I/O    | Туре   | Function                                                                      | Supply            | Active/State |

|------------------------------------------------|--------|--------|-------------------------------------------------------------------------------|-------------------|--------------|

| CLK                                            | Input  | LVCMOS | PLL reference clock input (pull-down)                                         | V <sub>DD</sub>   | —            |

| PCLK, PCLK                                     | Input  | LVPECL | PLL reference clock input<br>(PCLK — pull-down, PCLK — pull-up and pull-down) | V <sub>DD</sub>   | -            |

| QA0, QA1,<br>QA2, QA3<br>QB0, QB1,<br>QB2, QB3 | Output | LVCMOS | Clock Outputs                                                                 | V <sub>DDOA</sub> | _            |

| REF_OUT0<br>REF_OUT1                           | Output | LVCMOS | Reference Output (25 MHz or 33 MHz)                                           | V <sub>DD</sub>   | —            |

| XTAL_IN                                        | Input  | LVCMOS | Crystal Oscillator Input Pin                                                  | V <sub>DD</sub>   | —            |

| XTAL_OUT                                       | Output | LVCMOS | Crystal Oscillator Output Pin                                                 | V <sub>DD</sub>   | —            |

| CLK_SEL                                        | Input  | LVCMOS | Select between CLK and PCLK input (pull-down)                                 | V <sub>DD</sub>   | High         |

| XTAL_SEL                                       | Input  | LVCMOS | Select between External Input and Crystal Oscillator Input (pull-down)        | V <sub>DD</sub>   | High         |

| REF_33 MHz                                     | Input  | LVCMOS | Selects 33MHz input (pull-down)                                               | V <sub>DD</sub>   | High         |

| REF_OUT1_E                                     | Input  | LVCMOS | Enables REF_OUT! output (pull-down)                                           | V <sub>DD</sub>   | High         |

| MR                                             | Input  | LVCMOS | Master Reset (pull-up)                                                        | V <sub>DD</sub>   | Low          |

| PLL_BYPASS                                     | Input  | LVCMOS | Select PLL or static test mode (pull-up)                                      | V <sub>DD</sub>   | High         |

| CLK_A[0:5] <sup>(1)</sup>                      | Input  | LVCMOS | Configures Bank A clock output frequency (pull-up)                            | V <sub>DD</sub>   | —            |

| CLK_ <b>B</b> [0:5] <sup>1</sup>               | Input  | LVCMOS | Configures Bank B clock output frequency (pull-up)                            | V <sub>DD</sub>   | —            |

| V <sub>DD</sub>                                | _      | —      | 3.3 V Supply                                                                  | —                 | —            |

| V <sub>DDA</sub>                               | —      | —      | Analog Supply                                                                 | —                 | —            |

| V <sub>DDOA</sub>                              | _      | -      | Output Supply — Bank A                                                        | —                 | —            |

| V <sub>DDOB</sub>                              | —      |        | Output Supply — Bank B                                                        | —                 | —            |

| GND                                            | —      | _      | Ground                                                                        | _                 | _            |

1. Power PC bit ordering (bit 0 = msb, bit 5 = lsb).

# Table 2. Function Table

| Control    | Default | 0                        | 1                        |

|------------|---------|--------------------------|--------------------------|

| CLK_SEL    | 0       | CLK                      | PCLK                     |

| XTAL_SEL   | 0       | CLKx                     | XTAL                     |

| PLL_BYPASS | 0       | Normal                   | Bypass                   |

| REF_OUT1_E | 0       | Disables REF_OUT1        | Enables REF_OUT1         |

| REF_33 MHz | 0       | Selects 25 MHz Reference | Selects 33 MHz Reference |

| MR         | 1       | Reset                    | Normal                   |

CLK\_A and CLK\_B control output frequencies. Refer to Table 3 for specific device configuration

| CLK_x[0:5] <sup>(1)</sup> | CLK_x[0]<br>(msb) | CLK_x[1] | CLK_x[2] | CLK_x[3] | CLK_x[4] | CLK_x[5]<br>(Isb) | N                | Frequency<br>(MHz) |

|---------------------------|-------------------|----------|----------|----------|----------|-------------------|------------------|--------------------|

| 111111                    | 1                 | 1        | 1        | 1        | 1        | 1                 | 126              | 15.87              |

| 111100                    | 1                 | 1        | 1        | 1        | 0        | 0                 | 120              | 16.67              |

| 101000                    | 1                 | 0        | 1        | 0        | 0        | 0                 | 80               | 25.00              |

| 011110                    | 0                 | 1        | 1        | 1        | 1        | 0                 | 60               | 33.33              |

| 010100                    | 0                 | 1        | 0        | 1        | 0        | 0                 | 40               | 50.00              |

| 001111                    | 0                 | 0        | 1        | 1        | 1        | 1                 | 30               | 66.67              |

| 001100                    | 0                 | 0        | 1        | 1        | 0        | 0                 | 24               | 83.33              |

| 001010                    | 0                 | 0        | 1        | 0        | 1        | 0                 | 20               | 100.00             |

| 001001                    | 0                 | 0        | 1        | 0        | 0        | 1                 | 18               | 111.11             |

| 001000                    | 0                 | 0        | 1        | 0        | 0        | 0                 | 16               | 125.00             |

| 000111                    | 0                 | 0        | 0        | 1        | 1        | 1                 | 15               | 133.33             |

| 000110                    | 0                 | 0        | 0        | 1        | 1        | 0                 | 12               | 166.67             |

| 000101                    | 0                 | 0        | 0        | 1        | 0        | 1                 | 10               | 200.00             |

| 000100                    | 0                 | 0        | 0        | 1        | 0        | 0                 | 8 <sup>(2)</sup> | 250                |

Table 3. Output Configurations (Banks A & B)

1. PowerPC bit ordering (bit 0 = msb, bit 5 = lsb)

2. Minimum value for N.

# **OPERATION INFORMATION**

## **Output Frequency Configuration**

The MPC9855 was designed to provide the commonly used frequencies in PowerQUICC, PowerPC and other microprocessor systems. Table 3 lists the configuration values that will generate those common frequencies. The MPC9855 can generate numerous other frequencies that may be useful in specific applications. The output frequency (fout) may be calculated by the following equation.

# f<sub>out</sub> = 2000 / N

where f<sub>out</sub> is in MHz and N = 2 \* CLK\_x[0:5]

This calculation is valid for all values of N from 8 to 126. Note that N = 15 is a modified case of the configuration inputs CLK x[0:5]. To achieve N = 15 CLK x[0:5] is configured to 00111 or 7.

## **Crystal Input Operation**

The MPC9855 features a fully integrated Pierce oscillator to minimize system implementation costs. Other than the addition of a crystal no external components are required The crystal selection should be 25 MHz, parallel resonant type with a load specification of  $C_1 = 10 \text{ pF}$ .

The crystal should be located as close to the MPC92469 XTAL IN and XTAL OUT pins as possible to avoid any board level parasitic.

# Power-Up and MR Operation

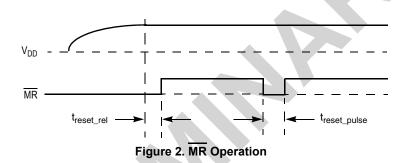

Figure 2 defines the release time and the minimum pulse length for  $\overline{MR}$  pin. The  $\overline{MR}$  release time is based upon the power supply being stable and within V<sub>DD</sub> specifications. See Table 10 for actual parameter values. The MPC9855 may be configured after release of reset and the outputs will be stable for use after lock indication is obtained.

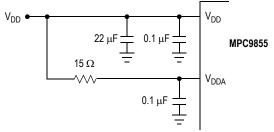

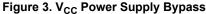

## **Power Supply Bypassing**

The MPC9855 is a mixed analog/digital product. The architecture of the XC9855 supports low noise signal operation at high frequencies. In order to maintain its superior signal quality, all V<sub>DD</sub> pins should be bypassed by high-frequency ceramic capacitors connected to GND. If the spectral frequencies of the internally generated switching noise on the supply pins cross the series resonant point of an individual bypass capacitor, its overall impedance begins to look inductive and thus increases with increasing frequency. The parallel capacitor combination shown ensures that a low impedance path to ground exists for frequencies well above the noise bandwidth.

## **Power Consumption**

The total power consumption of the MPC9855 may be calculated by the following formula:

$P = V_{DD} * (I_{DD} + I_{DDA} + I_{DDOC}) + (CPD * frequency * 4 * V_{DDOA}^{**2}) + (CPD * frequency * 4 * V_{DDOB}^{**2})$

where frequency is the programmed output frequency for bank A and bank B.

# Table 4. Absolute Maximum Ratings<sup>(1)</sup>

| Symbol            | Characteristics                           | Min  | Мах                   | Unit | Condition |

|-------------------|-------------------------------------------|------|-----------------------|------|-----------|

| V <sub>DD</sub>   | Supply Voltage (core)                     | -0.3 | 3.8                   | V    |           |

| V <sub>DDA</sub>  | Supply Voltage (Analog Supply Voltage)    | -0.3 | V <sub>DD</sub>       | V    |           |

| V <sub>DDOA</sub> | Supply Voltage (LVCMOS output for Bank A) | -0.3 | V <sub>DD</sub>       | V    |           |

| V <sub>DDOB</sub> | Supply Voltage (LVCMOS output for Bank B) | -0.3 | V <sub>DD</sub>       |      |           |

| V <sub>IN</sub>   | DC Input Voltage                          | -0.3 | V <sub>DD</sub> +0.3  | V    |           |

| V <sub>OUT</sub>  | DC Output Voltage <sup>(2)</sup>          | -0.3 | V <sub>DDx</sub> +0.3 | V    |           |

| I <sub>IN</sub>   | DC Input Current                          |      | ±20                   | mA   |           |

| I <sub>OUT</sub>  | DC Output Current                         |      | ±50                   | mA   |           |

| Τ <sub>S</sub>    | Storage Temperature                       | -65  | 125                   | °C   |           |

1. Absolute maximum continuous ratings are those maximum values beyond which damage to the device may occur. Exposure to these conditions or conditions beyond those indicated may adversely affect device reliability. Functional operation at absolute-maximum-rated conditions is not implied.

2.  $V_{DDx}$  references power supply pin associated with specific output pin.

## **Table 5. General Specifications**

| Symbol          | Characteristics                          | Min  | Тур                 | Max | Unit | Condition    |

|-----------------|------------------------------------------|------|---------------------|-----|------|--------------|

| V <sub>TT</sub> | Output Termination Voltage               |      | V <sub>DD</sub> ÷ 2 |     | V    |              |

| MM              | ESD Protection (Machine Model)           | 200  |                     |     | V    |              |

| HBM             | ESD Protection (Human Body Model)        | 2000 |                     |     | V    |              |

| CDM             | ESD Protection (Charged Device Model)    | 500  |                     |     | V    |              |

| LU              | Latch-Up Immunity                        | 200  |                     |     | mA   |              |

| C <sub>IN</sub> | Input Capacitance                        |      | 4                   |     | pF   | Inputs       |

| C <sub>PD</sub> | Power Dissipation Capacitance            |      | 6                   |     | pF   | Per Output   |

| $\theta_{JC}$   | Thermal Resistance (junction-to-ambient) | -    | 54.5                |     | °C/W | Air Flow = 0 |

| T <sub>A</sub>  | Ambient Temperature                      | -40  |                     | 85  | °C   |              |

# Table 6. DC Characteristics ( $T_A = -40^{\circ}C$ to $85^{\circ}C$ )

| Symbol                                                    | Characteristics                                                                                       | Min      | Тур | Мах | Unit | Condition                          |  |  |  |  |

|-----------------------------------------------------------|-------------------------------------------------------------------------------------------------------|----------|-----|-----|------|------------------------------------|--|--|--|--|

| Supply Cur                                                | Supply Current for $V_{DD}$ = 3.3 V ± 5%, $V_{DDOA}$ = 3.3 V ± 5%, = $V_{DDOB}$ = 3.3 V ± 5%          |          |     |     |      |                                    |  |  |  |  |

| I <sub>DD</sub> + I <sub>DDA</sub><br>+ I <sub>DDOC</sub> | Maximum Quiescent Supply Current (Core)                                                               |          | 160 |     | mA   | $V_{DD} + V_{DDA} + V_{DDOC}$ pins |  |  |  |  |

| I <sub>DDA</sub>                                          | Maximum Quiescent Supply Current (Analog Supply)                                                      |          | 15  |     | mA   | $V_{\text{DDIN}}$ pins             |  |  |  |  |

| Supply Cur                                                | rent for V <sub>DD</sub> = 3.3 V $\pm$ 5%, V <sub>DDOA</sub> = 2.5 V $\pm$ 5%, V <sub>DDOB</sub> = 2. | 5 V ± 5% |     |     |      |                                    |  |  |  |  |

| I <sub>DD</sub> + I <sub>DDA</sub><br>+ I <sub>DDOC</sub> | Maximum Quiescent Supply Current (Core)                                                               |          | 140 |     | mA   | $V_{DD} + V_{DDA} + V_{DDOC}$ pins |  |  |  |  |

| I <sub>DDA</sub>                                          | Maximum Quiescent Supply Current (Analog Supply)                                                      |          | 15  |     | mA   | $V_{\text{DDIN}}$ pins             |  |  |  |  |

| Symbol                                                                                                | Characteristics                                               | Min | Тур | Max                   | Unit | Condition |  |  |

|-------------------------------------------------------------------------------------------------------|---------------------------------------------------------------|-----|-----|-----------------------|------|-----------|--|--|

| Differential LVPECL clock inputs (CLK1, $\overline{\text{CLK1}}$ ) for V <sub>DD</sub> = 3.3 V ± 0.5% |                                                               |     |     |                       |      |           |  |  |

| V <sub>PP</sub>                                                                                       | Differential Voltage <sup>(2)</sup> (peak-to-peak) (LVPECL)   | 250 |     |                       | mV   |           |  |  |

| V <sub>CMR</sub>                                                                                      | Differential Input Crosspoint Voltage <sup>(3)</sup> (LVPECL) | 1.0 |     | V <sub>DD</sub> – 0.6 | V    |           |  |  |

1. AC characteristics are design targets and pending characterization.

V<sub>PP</sub> is the minimum differential input voltage swing required to maintain AC characteristics including t<sub>PD</sub> and device-to-device skew.

V<sub>CMR</sub> (AC) is the crosspoint of the differential input signal. Normal AC operation is obtained when the crosspoint is within the V<sub>CMR</sub> (AC) range and the input swing lies within the V<sub>PP</sub> (AC) specification. Violation of V<sub>CMR</sub> (AC) or V<sub>PP</sub> (AC) impacts the device propagation delay, device and part-to-part skew.

# Table 8. LVCMOS I/O DC Characteristics (T<sub>A</sub> = $-40^{\circ}$ C to $85^{\circ}$ C)

|                  |                                                                    | 1        | r       |                       |      |                           |

|------------------|--------------------------------------------------------------------|----------|---------|-----------------------|------|---------------------------|

| Symbol           | Characteristics                                                    | Min      | Тур     | Мах                   | Unit | Condition                 |

| LVCMOS f         | or $V_{DD}$ = 3.3 V ± 5%                                           |          |         |                       |      |                           |

| V <sub>IH</sub>  | Input High Voltage                                                 | 2.0      |         | V <sub>DD</sub> + 0.3 | V    | LVCMOS                    |

| V <sub>IL</sub>  | Input Low Voltage                                                  |          |         | 0.8                   | v    | LVCMOS                    |

| I <sub>IN</sub>  | Input Current <sup>(1)</sup>                                       |          |         | 200                   | μA   | $V_{IN} = V_{DDL}$ or GND |

| LVCMOS f         | or $V_{DD}$ = 3.3 V ± 5%, $V_{DDOA}$ = 3.3 V ± 5%, $V_{DDOB}$ = 3. | 3 V ± 5% |         |                       |      |                           |

| V <sub>OH</sub>  | Output High Voltage                                                | 2.4      |         |                       | V    | I <sub>OH</sub> = -12 mA  |

| V <sub>OL</sub>  | Output Low Voltage                                                 |          |         | 0.4                   | V    | I <sub>OL</sub> = 12 mA   |

| Z <sub>OUT</sub> | Output Impedance                                                   |          | 14 – 17 |                       | Ω    |                           |

| LVCMOS f         | or $V_{DD}$ = 3.3 V ± 5%, $V_{DDOA}$ = 2.5 V ± 5%, $V_{DDOB}$ = 2. | 5 V ± 5% |         |                       |      | •                         |

| V <sub>OH</sub>  | Output High Voltage                                                | 1.9      |         |                       | V    | I <sub>OH</sub> = -10 mA  |

| V <sub>OL</sub>  | Output Low Voltage                                                 |          |         | 0.4                   | V    | I <sub>OL</sub> = 10 mA   |

| Z <sub>OUT</sub> | Output Impedance                                                   |          | 18 – 22 |                       | Ω    |                           |

1. Inputs have pull-down resistors affecting the input current.

| Symbol                          | Characteristics                                                                                                                                                   | Min                  | Тур            | Max               | Unit                     | Condition                                              |

|---------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|----------------|-------------------|--------------------------|--------------------------------------------------------|

| Input and Outp                  | ut Timing Specification                                                                                                                                           |                      |                |                   |                          |                                                        |

| f <sub>ref</sub>                | Input Reference Frequency (25 MHz input)<br>Input Reference Frequency (33 MHz input)<br>XTAL Input<br>Input Reference Frequency in PLL Bypass Mode <sup>(3)</sup> |                      | 25<br>33<br>25 | 250               | MHz<br>MHz<br>MHz<br>MHz | PLL bypass                                             |

| f <sub>VCO</sub>                | VCO Frequency Range <sup>(4)</sup>                                                                                                                                |                      | 2000           |                   | MHz                      |                                                        |

| f <sub>MCX</sub>                | Output Frequency Bank A output<br>Bank B output<br>Bank C output                                                                                                  | 15.87<br>15.87<br>50 |                | 200<br>200<br>500 | MHz<br>MHz<br>MHz        | PLL locked                                             |

| f <sub>refPW</sub>              | Reference Input Pulse Width                                                                                                                                       | 2                    |                |                   | ns                       |                                                        |

| f <sub>refCcc</sub>             | Input Frequency Accuracy                                                                                                                                          |                      |                | 100               | ppm                      |                                                        |

| t <sub>r</sub> , t <sub>f</sub> | Output Rise/Fall Time                                                                                                                                             | 80                   |                | 500               | ns                       | 20% to 80%                                             |

| DC                              | Output Duty Cycle                                                                                                                                                 | 47.5<br>45           | 50<br>50       | 52.5<br>55        | %                        | 3.3 V operation<br>2.5 V operation                     |

| PLL Specificati                 | ions                                                                                                                                                              |                      |                |                   |                          | ·                                                      |

| BW                              | PLL Closed Loop Bandwidth <sup>(5)</sup>                                                                                                                          |                      |                | 1                 | MHz                      |                                                        |

| t <sub>LOCK</sub>               | Maximum PLL Lock Time                                                                                                                                             |                      |                | 10                | ms                       |                                                        |

| t <sub>reset_ref</sub>          | MR Hold Time on Power Up                                                                                                                                          | 10                   |                |                   | ns                       |                                                        |

| t <sub>reset_pulse</sub>        | MR Hold Time                                                                                                                                                      | 10                   |                |                   | ns                       |                                                        |

| Skew and Jitte                  | r Specifications                                                                                                                                                  |                      |                |                   |                          | ·                                                      |

| t <sub>sk(O)</sub>              | Output-to-Output Skew (within a bank)                                                                                                                             |                      | 50             |                   | ps                       |                                                        |

| t <sub>sk(O)</sub>              | Output-to-Output Skew (across banks A and B)                                                                                                                      |                      | 100            |                   | ps                       | V <sub>DDOA</sub> = 3.3 V<br>V <sub>DDOB</sub> = 3.3 V |

| t <sub>JIT(CC)</sub>            | Cycle-to-cycle jitter                                                                                                                                             |                      | 150<br>80      |                   | ps                       | Bank A and B<br>Back C                                 |

| $t_{\text{JIT}(\text{PER})}$    | Period Jitter                                                                                                                                                     |                      | 150<br>80      |                   | ps                       | Bank A and B<br>Back C                                 |

| t <sub>JIT(∅)</sub>             | I/O Phase Jitter RMS (1 σ)                                                                                                                                        |                      | 15<br>15       |                   | ps                       | Bank A and B<br>Back C                                 |

# Table 9. AC Characteristics ( $V_{DD}$ = 3.3 V ± 5%, $V_{DDOA}$ = 3.3 V ± 5%, $V_{DDOB}$ = 3.3 V ± 5%, $T_A$ = -40°C to +85°C)<sup>(1)</sup> (2)

1. AC characteristics are design targets and pending characterization.

2. AC characteristics apply for parallel output termination of 50  $\Omega$  to V\_TT.

3. In bypass mode, the MPC9855 divides the input reference clock.

4. The input reference frequency must match the VCO lock range divided by the total feedback divider ratio:

$f_{ref} = (f_{VCO} \div M) \cdot N.$ 5. -3 dB point of PLL transfer characteristics.

Figure 4. MPC9855 AC Test Reference (LVCMOS Outputs)

| 1                        | 2                 | 3               | 4               | 5               | 6               | 7                 | 8               | 9                 | 10                |  |

|--------------------------|-------------------|-----------------|-----------------|-----------------|-----------------|-------------------|-----------------|-------------------|-------------------|--|

| V <sub>DDOA</sub>        | V <sub>DDOA</sub> | CLKA[1]         | CLKA[3]         | CLKA[5]         | $V_{DD}$        | QA1               | QA2             | V <sub>DDOA</sub> | V <sub>DDOA</sub> |  |

| V <sub>DDOA</sub>        | V <sub>DDOA</sub> | CLKA[0]         | CLKA[2]         | CLKA[4]         | QA0             | V <sub>DDOA</sub> | QA3             | V <sub>DDOA</sub> | V <sub>DDOA</sub> |  |

| RSVD                     | RSVD              | V <sub>DD</sub>   | V <sub>DD</sub> | V <sub>DD</sub>   | REF_OUT[          |  |

| V <sub>DDA</sub>         | V <sub>DDA</sub>  | V <sub>DD</sub> | GND             | GND             | GND             | GND               | V <sub>DD</sub> | RSVD              | REF_OUT[          |  |

| XTAL_SEL                 | CLK               | V <sub>DD</sub> | GND             | GND             | GND             | GND               | V <sub>DD</sub> | V <sub>DD</sub>   | GND               |  |

| PCLK                     | PCLK              | V <sub>DD</sub> | GND             | GND             | GND             | GND               | V <sub>DD</sub> | RSVD              | RSVD              |  |

| CLK_SEL                  | REF_33MHz         | V <sub>DD</sub> | GND             | GND             | GND             | GND               | V <sub>DD</sub> | PLL_BYPASS        | MR                |  |

| XTAL_IN                  | XTAL_OUT          | V <sub>DD</sub>   | V <sub>DD</sub> | RSVD              | REF_OUT1          |  |

| V <sub>DDOB</sub>        | V <sub>DDOB</sub> | CLKB[0]         | CLKB[2]         | CLKB[4]         | QB0             | V <sub>DDOB</sub> | QB3             | V <sub>DDOB</sub> | V <sub>DDOB</sub> |  |

| V <sub>DDOB</sub>        | V <sub>DDOB</sub> | CLKB[1]         | CLKB[3]         | CLKB[5]         | V <sub>DD</sub> | QB1               | QB2             | V <sub>DDOB</sub> | V <sub>DDOB</sub> |  |

| ble 11. MPC9855 Pin List |                   |                 |                 |                 |                 |                   |                 |                   |                   |  |

# Table 10. MPC9855 Pin Diagram (Top View)

# Table 11. MPC9855 Pin List

| Signal            | 100 Pin<br>MAPBGA | Signal           | 100 Pin<br>MAPBGA | Signal          | 100 Pin<br>MAPBGA | Signal          | 100 Pin<br>MAPBGA | Signal            | 100 Pin<br>MAPBGA |

|-------------------|-------------------|------------------|-------------------|-----------------|-------------------|-----------------|-------------------|-------------------|-------------------|

| V <sub>DDOA</sub> | A1                | RSVD             | C1                | XTAL_SEL        | E1                | CLK_SEL         | G1                | V <sub>DDOB</sub> | J1                |

| V <sub>DDOA</sub> | A2                | RSVD             | C2                | CLK             | E2                | REF_33MHz       | G2                | V <sub>DDOB</sub> | J2                |

| CLKA[1]           | A3                | V <sub>DD</sub>  | C3                | V <sub>DD</sub> | E3                | V <sub>DD</sub> | G3                | CLKB[0]           | J3                |

| CLKA[3]           | A4                | V <sub>DD</sub>  | C4                | GND             | E4                | GND             | G4                | CLKB[2]           | J4                |

| CLKA[5]           | A5                | V <sub>DD</sub>  | C5                | GND             | E5                | GND             | G5                | CLKB[4]           | J5                |

| $V_{DD}$          | A6                | V <sub>DD</sub>  | C6                | GND             | E6                | GND             | G6                | QB0               | J6                |

| QA1               | A7                | V <sub>DD</sub>  | C7                | GND             | E7                | GND             | G7                | V <sub>DDOB</sub> | J7                |

| QA2               | A8                | V <sub>DD</sub>  | C8                | V <sub>DD</sub> | E8                | V <sub>DD</sub> | G8                | QB3               | J8                |

| V <sub>DDOA</sub> | A9                | V <sub>DD</sub>  | C9                | V <sub>DD</sub> | E9                | PLL_BYPASS      | G9                | V <sub>DDOB</sub> | J9                |

| V <sub>DDOA</sub> | A10               | REF_OUT[0]       | C10               | GND             | E10               | MR              | G10               | V <sub>DDOB</sub> | J10               |

| V <sub>DDOA</sub> | B1                | V <sub>DDA</sub> | D1                | PCLK            | F1                | XTAL_IN         | H1                | V <sub>DDOB</sub> | K1                |

| V <sub>DDOA</sub> | B2                | V <sub>DDA</sub> | D2                | PCLK            | F2                | XTAL_OUT        | H2                | V <sub>DDOB</sub> | K2                |

| CLKA[0]           | B3                | V <sub>DD</sub>  | D3                | V <sub>DD</sub> | F3                | V <sub>DD</sub> | H3                | CLKB[1]           | K3                |

| CLKA[2]           | B4                | GND              | D4                | GND             | F4                | V <sub>DD</sub> | H4                | CLKB[3]           | K4                |

| CLKA[4]           | B5                | GND              | D5                | GND             | F5                | V <sub>DD</sub> | H5                | CLKB[5]           | K5                |

| QA0               | B6                | GND              | D6                | GND             | F6                | V <sub>DD</sub> | H6                | V <sub>DD</sub>   | K6                |

| V <sub>DDOA</sub> | B7                | GND              | D7                | GND             | F7                | V <sub>DD</sub> | H7                | QB1               | K7                |

| QA3               | B8                | V <sub>DD</sub>  | D8                | V <sub>DD</sub> | F8                | V <sub>DD</sub> | H8                | QB2               | K8                |

| V <sub>DDOA</sub> | B9                | RSVD             | D9                | RSVD            | F9                | RSVD            | H9                | V <sub>DDOB</sub> | K9                |

| V <sub>DDOA</sub> | B10               | REF_OUT[1]       | D10               | RSVD            | F10               | REF_OUT1E       | H10               | V <sub>DDOB</sub> | K10               |

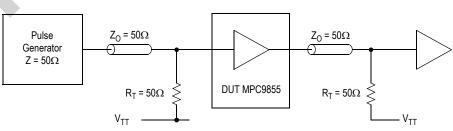

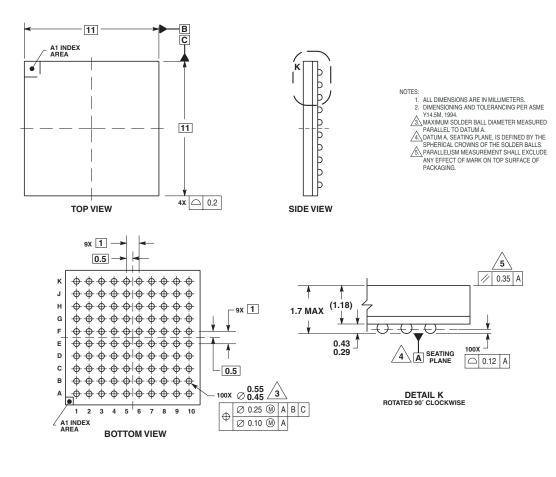

# PACKAGE DIMENSIONS

VA SUFFIX VM SUFFIX (Pb-FREE) 100 MAPBGA PACKAGE CASE 1462-01 ISSUE O

**MPC9855**

# NOTES

## How to Reach Us:

Home Page: www.freescale.com

E-mail: support@freescale.com

### **USA/Europe or Locations Not Listed:**

Freescale Semiconductor Technical Information Center, CH370 1300 N. Alma School Road Chandler, Arizona 85224 +1-800-521-6274 or +1-480-768-2130 support@freescale.com

## Europe, Middle East, and Africa:

Freescale Halbleiter Deutschland GmbH Technical Information Center Schatzbogen 7 81829 Muenchen, Germany +44 1296 380 456 (English) +46 8 52200080 (English) +49 89 92103 559 (German) +33 1 69 35 48 48 (French) support@freescale.com

#### Japan:

Freescale Semiconductor Japan Ltd. Headquarters ARCO Tower 15F 1-8-1, Shimo-Meguro, Meguro-ku, Tokyo 153-0064 Japan 0120 191014 or +81 3 5437 9125 support.japan@freescale.com

#### Asia/Pacific:

Freescale Semiconductor Hong Kong Ltd. Technical Information Center 2 Dai King Street Tai Po Industrial Estate Tai Po, N.T., Hong Kong +800 2666 8080 support.asia@freescale.com

#### For Literature Requests Only:

Freescale Semiconductor Literature Distribution Center P.O. Box 5405 Denver, Colorado 80217 1-800-441-2447 or 303-675-2140 Fax: 303-675-2150 LDCForFreescaleSemiconductor@hibbertgroup.com Information in this document is provided solely to enable system and software implementers to use Freescale Semiconductor products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits or integrated circuits based on the information in this document.

Freescale Semiconductor reserves the right to make changes without further notice to any products herein. Freescale Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Freescale Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters that may be provided in Freescale Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals", must be validated for each customer application by customer's technical experts. Freescale Semiconductor does not convey any license under its patent rights nor the rights of others. Freescale Semiconductor products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Freescale Semiconductor product could create a situation where personal injury or death may occur. Should Buyer purchase or use Freescale Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold Freescale Semiconductor and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Freescale Semiconductor was negligent regarding the design or manufacture of the part.

Freescale<sup>™</sup> and the Freescale logo are trademarks of Freescale Semiconductor, Inc. All other product or service names are the property of their respective owners. © Freescale Semiconductor, Inc. 2005. All rights reserved.