# MR27V3266D

2M x16 / 1M x32 Synchronous OTP ROM

## DESCRIPTION

The MR27V3266D is a 32Mbit One Time Programmable Synchronous Read Only Memory whose configuration can be electrically switched between 2,097,152 x16bit(word mode) and 1,048,576 x32bit(double word mode) by the state of the /WORD pin. The MR27V3266D supports high speed synchronous read operations using a single 3.3V power supply.

## FEATURES ON READ

- 3.3V power supply

- LVTTL compatible with multiplexed address

- Dual, electrically switchable configurations

2M x16(word mode) / 1M x32(double word mode)

- All inputs are sampled at the rising edge of the system clock

- High speed read operation

- 66MHz : CAS Latency=5 tRCDmin=2 Burst Length (4, 8) Data scramble (sequential, interleave) 50MHz : CAS Latency=4, 5 tRCDmin=1 Burst Length (4, 8) Data scramble (sequential, interleave)

- DQM for data out masking

- No Precharge operation is required. No Refresh operation is required.

- No power on sequence is required.

Mode register is automatically initialized to the default state after power on.

"Row Active" command to read data is applicable as the first command just after power on.

- Single Bank operation

- Package : TSOP II 86-P-400-0.50-K

# FEATURES ON PROGRAMMING

- 9.75V programming Power supply

- Programming algorithm is compatible with conventional asynchronous 32M OTP.

- MR27V3266D can be programmed with conventional EPROM programmers.

- Synchronous Burst read or Static Programming Operation are selected by the state of STO pin. High STO level enables full static programming. (Program, Program Verify, asynchronous Read)

- Low STO level enables synchronous burst read.

- Exclusive 86pin socket adapters are available from OKI to support programming requirements.

- The socket adapter is used on a 48DIP socket on the programmer.

- The socket adapter is designed with the STO pin connected to Vcc in order to program MR27V3266D as conventional 32M OTP.

- EPROM programmer must have the proper algorithm for 32M OTP.

- \*Device damage can occur if improper algorithm is used.

- High speed programming

- $10\mu s$  programming pulse per word allows high speed programming.

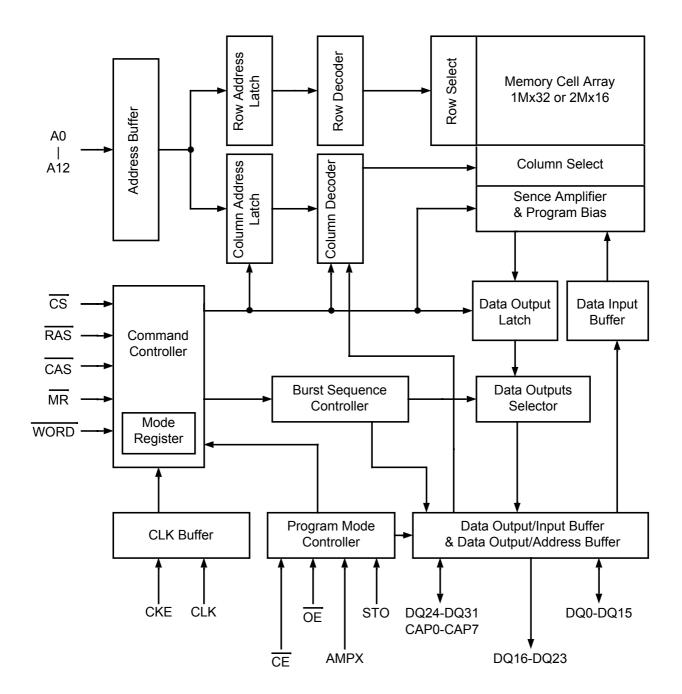

#### FUNCTION BLOCK DIAGRAM

PIN CONFIGURATION

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | TOP VIEW         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Programming in                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Static Opera     | tion (STO is high)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Synchronous                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Read (STO        | is Vss or open)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | ]                                                                                                                                                                                                                                                                                                                                               |

| Vcc<br>DQ0<br>VccQ<br>DC<br>DQ1<br>VssQ<br>DC<br>DQ2<br>VccQ<br>DC<br>DQ3<br>VssQ<br>DC<br>DC<br>Vcc<br>DC<br>Vcc<br>DC<br>Vcc<br>NC<br>/CAS<br>/RAS<br>DC<br>/WORD<br>A12<br>A11<br>A10<br>A0<br>A1<br>A2<br>NC<br>Vcc<br>DC<br>Vcc<br>DC<br>DC<br>Vcc<br>DC<br>DC<br>Vcc<br>DC<br>DC<br>Vcc<br>DC<br>DC<br>Vcc<br>DC<br>Vcc<br>DC<br>DC<br>Vcc<br>DC<br>Vcc<br>DC<br>DC<br>Vcc<br>DC<br>Vcc<br>DC<br>Vcc<br>DC<br>Vcc<br>DC<br>Vcc<br>DC<br>Vcc<br>DC<br>Vcc<br>DC<br>Vcc<br>DC<br>Vcc<br>DC<br>Vcc<br>DC<br>Vcc<br>DC<br>Vcc<br>DC<br>Vcc<br>DC<br>Vcc<br>DC<br>Vcc<br>DC<br>Vcc<br>DC<br>Vcc<br>DC<br>Vcc<br>DC<br>Vcc<br>DC<br>Vcc<br>DC<br>Vcc<br>DC<br>Vcc<br>DC<br>Vcc<br>DC<br>Vcc<br>DC<br>Vcc<br>DC<br>Vcc<br>DC<br>Vcc<br>DC<br>Vcc<br>DC<br>Vcc<br>DC<br>Vcc<br>DC<br>Vcc<br>DC<br>Vcc<br>DC<br>Vcc<br>DC<br>Vcc<br>Vcc<br>DC<br>Vcc<br>Vcc<br>DC<br>Vcc<br>Vcc<br>DC<br>Vcc<br>DC<br>Vcc<br>DC<br>Vcc<br>DC<br>Vcc<br>DC<br>Vcc<br>Vcc<br>DC<br>Vcc<br>Vcc<br>DC<br>Vcc<br>Vcc<br>Vcc<br>Vcc<br>Vcc<br>Vcc<br>Vcc<br>Vcc<br>Vcc<br>Vc | Vcc     1       DQ0     2       VccQ     3       DQ16     4       DQ1     5       VssQ     6       DQ17     7       DQ2     8       VccQ     9       DQ18     10       DQ3     11       VssQ     12       DQ19     13       /MR     14       Vcc     15       DQM     16       NC     17       /CAS     19       /CS     20       /WORD     21       A10     24       A0     25       A1     26       A2     27       NC     30       DQ4     31       VssQ     33       DQ5     34       VccQ     33       DQ21     36       DQ23     39       DQ7     40       VccQ     41       DQ23     42       Vcc     43 | 86PIN<br>TSOP II | 86     Vss       85     DQ31       84     VssQ       83     DQ15       82     DQ30       81     VccQ       80     DQ14       79     DQ29       78     VssQ       77     DQ13       76     DQ28       75     VccQ       74     DQ12       73     NC       72     Vss       71     DC       70     DC       69     DC       68     CLK       67     CKE       66     A9       65     A8       64     A7       63     DC       58     Vss       57     DC       56     DQ27       55     VccQ       54     DQ10       50     DQ26       52     VssQ       51     DQ26       52     VssQ       51     DQ26       52     VssQ       41     VssQ    < | VSS<br>CAP0<br>VSSQ<br>DQ15<br>CAP1<br>VCCQ<br>DQ14<br>CAP2<br>VSSQ<br>DQ13<br>CAP3<br>VCCQ<br>DQ12<br>NC<br>VSS<br>VPP<br>/CE<br>/OE<br>DC<br>DC<br>DC<br>DC<br>DC<br>DC<br>A9<br>A8<br>A7<br>A6<br>A5<br>A4<br>A3<br>AMPX<br>VSS<br>STO<br>CAP4<br>VCCQ<br>DQ11<br>CAP5<br>VSSQ<br>DQ10<br>CAP5<br>VSSQ<br>DQ10<br>CAP7<br>VSSQ<br>DQ8<br>VSS |

DC(Don't Care) : Logical input level is ignored, however the pin is connected to input buffer of OTP

# PIN FUNCTION FOR SYNCHRONOUS READ OPERATION (STO pin is low level or open)

| PIN NAME | FUNCTION                          | DESCRIPTION                                                                                                                                                                                                                |

|----------|-----------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| STO      | Static Operation                  | Must be low for synchronous operation. Internal resistance<br>(around 10k ohms) pulls the input level down to Vss when<br>this pin is open. High level STO enables programming<br>operation compatible with standard OTPs. |

| CLK      | System Clock                      | All inputs are sampled at the rising edge.                                                                                                                                                                                 |

| /CS      | Chip Select                       | Enables command sampling by the CLK signal with a low level on the /CS input.                                                                                                                                              |

| CKE      | Clock Enable                      | Masks internal system clock to freeze the CLK operation of<br>subsequent CLK cycle. CKE must be enabled for command<br>sampling cycles. CLK is disabled for two types of operations.<br>1)Clock Suspend<br>2)Power down.   |

| A0-A12   | Address                           | Row and column addresses are multiplexed on the same pins.<br>Row address:RA0-RA12<br>Column address:CA0-CA6(x32) / CA0-CA7(x16)                                                                                           |

| /RAS     | Row Address Strobe                | Functionality depends on the combination.                                                                                                                                                                                  |

| /CAS     | Column Address Strobe             | See the function table.                                                                                                                                                                                                    |

| /MR      | Mode Register Set                 |                                                                                                                                                                                                                            |

| DQ0-DQ31 | Data Output                       | Data outputs are valid at the rising edge of CLK for read cycles. Except for read cycles DQn is high-Z state.                                                                                                              |

| DQM      | Data Output Masking               | Data outputs are masked after two cycles from when high level DQM is applied.                                                                                                                                              |

| /WORD    | x32/x16 Organization<br>Selection | The /WORD pin defines the organization of each read command to be x16 (word mode) or x32 (double word mode).<br>High=x32<br>Low=x16                                                                                        |

| Vcc      | Power Supply                      | 3.3V Power supply                                                                                                                                                                                                          |

| Vss      | Ground                            |                                                                                                                                                                                                                            |

| VccQ     | Data Output Power Supply          | 3.3V Power supply to DQ0-DQ31                                                                                                                                                                                              |

| VssQ     | Data Output Ground                |                                                                                                                                                                                                                            |

| NC       | No Connection                     |                                                                                                                                                                                                                            |

| DC       | Don't Care                        | Logical input level is ignored.                                                                                                                                                                                            |

# PIN FUNCTION FOR PROGRAMMING OPERATION (STO pin is high level)

| PIN NAME  | FUNCTION                       | DESCRIPTION                                                                                                                                                                                                                                                                 |

|-----------|--------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| STO       | Static Operation               | Must be set high for programming operation. Internal resistance (around 10k ohms) pulls the input level down to Vss for open state condition to be low level for synchronous read operation.                                                                                |

| AMPX      | Address Multiplex              | When AMPX is low, the addresses are not multiplexed and all<br>address bits must be supplied to A0-A12(Row Address) and<br>CAP0-CAP7(Column Address) simultaneously.<br>This pin should be set low on programming operation.                                                |

| A0-A12    | Address                        | When AMPX is low, A0-A12 is row address input.                                                                                                                                                                                                                              |

| /RAS      | Row address strobe             | When AMPX is low, input is not used.                                                                                                                                                                                                                                        |

| /CAS      | Column address strobe          | When AMPX is low, input is not used.                                                                                                                                                                                                                                        |

| DQ0-DQ15  | Data Input/Output              | Input of data for programming and output for program verify and read data.                                                                                                                                                                                                  |

| /WORD     | x32/x16 organization Selection | The /WORD pin defines the organization to be x16(word<br>mode) or x32(double word mode).<br>High= x32<br>Low = x16<br>Must be set low for programming operation.                                                                                                            |

| CAP0-CAP7 | Address Input                  | When /WORD is low, High-Z state on CAP0-CAP7 is held to be input pins.<br>When AMPX is low, CAP0 - CAP7 is column address input.                                                                                                                                            |

| /OE       | Output Enable                  | Control signal input for programming.<br>/OE of conventional OTP.                                                                                                                                                                                                           |

| /CE       | Chip Enable                    | Control signal input for programming.<br>Function for programming is associated with conventional<br>OTP.                                                                                                                                                                   |

| Vcc/Vss   | Power Supply/Ground            | Power and ground for the input buffers and the core logic.                                                                                                                                                                                                                  |

| VccQ/VssQ | Data Output Power/Ground       | Power and ground for output.                                                                                                                                                                                                                                                |

| Vpp       | Program Power Supply           | High voltage program power is supplied through VPP pin.<br>When VPP is higher than a predetermined voltage level<br>between Vcc+0.5V and Vcc+2V, pin function alters to high<br>VPP mode. To keep stable static read operation VPP pin must<br>be kept lower than Vcc+0.5V. |

The functionality of loose device programming must be studied with the specification of socket adapter that will be supplied by OKI. MR27V3266D on the socket adapter is the same programming functionality as conventional OTP.

## FUNCTION TABLE FOR SYNCHRONOUS READ

| COMMAND NAME              | FUNCTION                                   | CKEn-1 | CKEn | /CS | /RAS | /CAS | /MR | DQM | Add. | /WORD | STO | Notes |

|---------------------------|--------------------------------------------|--------|------|-----|------|------|-----|-----|------|-------|-----|-------|

| Mode Register Set         | Mode Register Set                          | Н      | Х    | L   | L    | L    | L   | Х   | Code | Х     | L   | 1     |

| Row Active                | Row Address Latch                          | Н      | Х    | L   | L    | Н    | Н   | Х   | RA   | Х     | L   | 2     |

| Read Word<br>(x16)        | Column Address Latch<br>Trigger Burst Read | н      | Х    | L   | Н    | L    | н   | x   | CA   | L     | L   | 3     |

| Read Double Word<br>(x32) | Column Address Latch<br>Trigger Burst Read | н      | Х    | L   | Н    | L    | н   | x   | CA   | н     | L   | 3     |

| Burst Stop                | Burst Stop                                 | Н      | Х    | L   | Н    | Н    | L   | Х   | Х    | Х     | L   | 4     |

| Precharge                 | Burst Stop                                 | Н      | Х    | L   | L    | Н    | L   | Х   | Х    | Х     | L   | 4     |

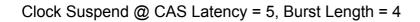

| Clock Suspend             | Entry                                      | Н      | L    | Х   | Х    | Х    | Х   | Х   | Х    | Х     | L   | 5     |

| (on Read)                 | Exit                                       | L      | Н    | Х   | Х    | Х    | Х   | Х   | Х    | Х     | L   | 5     |

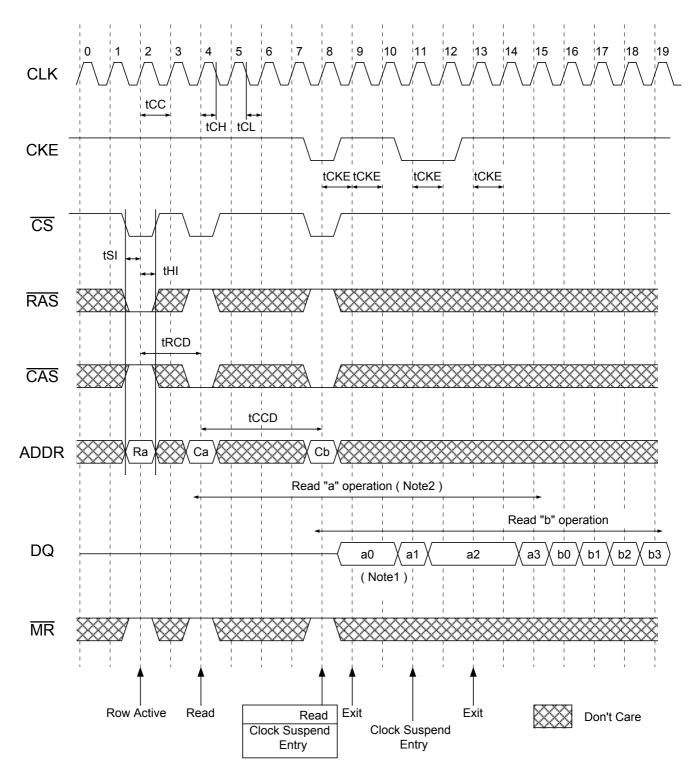

| Power Down<br>(on Active  | Entry                                      | Н      | L    | Н   | Х    | Х    | Х   | X   | Х    | Х     | L   | 6     |

| Standby)                  | Exit                                       | L      | Н    | Х   | Х    | Х    | Х   | X   | Х    | Х     | L   | 6     |

| Read Output               | Output Enable                              | Н      | X    | Х   | Х    | Х    | Х   | L   | Х    | Х     | L   |       |

| Mask Output               | High-Z Output                              | Н      | X    | Х   | Х    | Х    | Х   | Н   | X    | Х     | L   |       |

| No Operation              | Write on SDRAM                             | Н      | X    | L   | Н    | L    | L   | Х   | Х    | Х     | L   |       |

|                           | Self Refresh on SDRAM                      | Н      | L    | L   | L    | L    | Н   | X   | X    | Х     | L   |       |

|                           | Illegal on SDRAM                           | Н      | Н    | L   | L    | L    | Н   | Х   | Х    | Х     | L   |       |

|                           |                                            | Н      | X    | Н   | Х    | Х    | Х   | X   | X    | Х     | L   |       |

|                           |                                            | Н      | X    | L   | Н    | Н    | Н   | X   | X    | Х     | L   |       |

(H=Logical high, L=Logical low, X=Don't Care, L of STO includes pin open due to internal pull down resistor) (CKEn expresses the logical level at the simultaneous cycle with a command.)

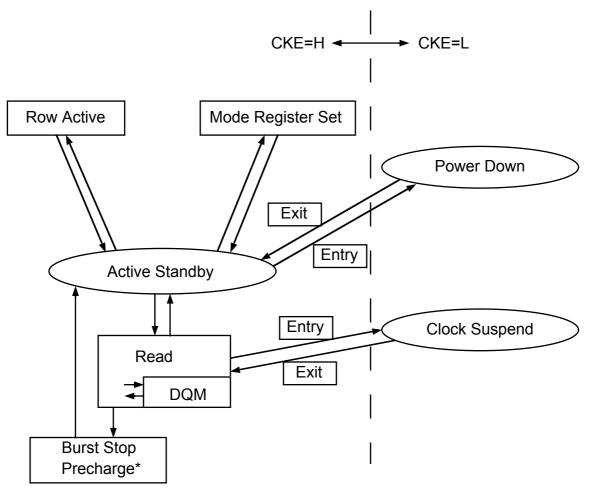

Refer to "Mode register Field Table" for Address Codes, and Mode Transition Chart for operational state. After power on any command can be sampled at any cycle in Active Standby state. After "Mode register Set" command is sampled, no new command can be accepted for 3 CLK cycles. The /CS input must be kept high for the 3 CLK cycles to prevent unexpected sampling of a command.

- 2. The "Row Active" command is effective till new "Row Active" command is implemented.

- The /WORD input is sampled simultaneously with "Read" command to select data width. A Double Word Burst(x32) or a Word Burst(x16) is selected by the /WORD input for each "Read" command. On condition of constant voltage level on /Word pin, organization is fixed to either x16 or x32. "Read" command ends it's implementation by itself at the finishing cycle of the burst read.

- 4. Since OTP technology uses static sense amplifiers, the "Precharge" command is not required however, due to customer request for the similarity of logical input code with SDRAM command, the name of "Precharge" is adopted. Function of "Precharge" command and "Burst Stop" command is only to stop the burst read cycles delayed by CAS Latency.

- 5. Sampled low level CKE disables CLK buffer to suspend internal clock signals at the next rising edge of CLK. Sampled high level CKE enables internal clock at the next rising edge of CLK. Low level CKE sampled in the period from the simultaneous cycle with a "Read" command till the end of the burst read cycle is distinguished with internal command controller from the low level CKE sampled in Active Standby state not to stop data sensing and burst read operation those consume power.

- Low level CKE sampled in Active Standby state cuts power dissipation to be in Power Down state. High level CKE sampled in Power Down state enables internal CKE to be in Active Standby state with preserved row address.

# MODE REGISTER FIELD TABLE

| Address  |    | A5 |    | A4          | A3 |    | A2         |    | A1 |         | A0       |  |

|----------|----|----|----|-------------|----|----|------------|----|----|---------|----------|--|

| Function |    |    |    | CAS Latency |    |    | ırst Type  |    | E  | Burst I | Length   |  |

|          | 1  |    |    |             |    | 1  |            |    |    |         |          |  |

|          | A5 | A4 | A3 | Length      |    | A2 | Туре       | A1 | A0 |         | Length   |  |

|          | 0  | 0  | 0  | Reserve     | d  | 0  | Sequential | 0  | 0  |         | Reserved |  |

|          | 0  | 0  | 1  | Reserve     | d  | 1  | Interleave | 0  | 1  | 4       |          |  |

|          | 0  | 1  | 0  | Reserve     | d  |    |            | 1  | 0  |         | 8        |  |

|          | 0  | 1  | 1  | 4           |    | ]  |            | 1  | 1  |         | Reserved |  |

|          | 1  | 0  | 0  | 5           |    |    |            |    | •  | •       |          |  |

|          | 1  | 0  | 1  | Reserved    |    |    |            |    |    |         |          |  |

|          | 1  | 1  | 0  | Reserved    |    | 1  |            |    |    |         |          |  |

|          | 1  | 1  | 1  | Reserve     | 1  |    |            |    |    |         |          |  |

#### Note

A7 and A8 must be low during Mode Register Set cycle.

During power on, mode register is initialized to the default state when Vcc reaches a specific voltage. The default state of Mode Register is below. (less than 3.0V)

CAS Latency=5

Burst Type=Sequential Burst length=4

#### BURST SEQUENCE (BURST LENGTH = 4)

| Initial a | ddress |   | Cogu  | ontial |   |            | Intorl |   |   |  |  |

|-----------|--------|---|-------|--------|---|------------|--------|---|---|--|--|

| A1        | A0     |   | Seque | enuar  | - | Interleave |        |   |   |  |  |

| 0         | 0      | 0 | 1     | 2      | 3 | 0          | 1      | 2 | 3 |  |  |

| 0         | 1      | 1 | 2     | 3      | 0 | 1          | 0      | 3 | 2 |  |  |

| 1         | 0      | 2 | 3     | 0      | 1 | 2          | 3      | 0 | 1 |  |  |

| 1         | 1      | 3 | 0     | 1      | 2 | 3          | 2      | 1 | 0 |  |  |

# BURST SEQUENCE (BURST LENGTH = 8)

| Ini | tial addr | ess |   |            |   | Sogu | ontial |   |   |   |   |            |   | Intor | 001/0 |   |   |   |  |

|-----|-----------|-----|---|------------|---|------|--------|---|---|---|---|------------|---|-------|-------|---|---|---|--|

| A2  | A1        | A0  |   | Sequential |   |      |        |   |   |   |   | Interleave |   |       |       |   |   |   |  |

| 0   | 0         | 0   | 0 | 1          | 2 | 3    | 4      | 5 | 6 | 7 | 0 | 1          | 2 | 3     | 4     | 5 | 6 | 7 |  |

| 0   | 0         | 1   | 1 | 2          | 3 | 4    | 5      | 6 | 7 | 0 | 1 | 0          | 3 | 2     | 5     | 4 | 7 | 6 |  |

| 0   | 1         | 0   | 2 | 3          | 4 | 5    | 6      | 7 | 0 | 1 | 2 | 3          | 0 | 1     | 6     | 7 | 4 | 5 |  |

| 0   | 1         | 1   | 3 | 4          | 5 | 6    | 7      | 0 | 1 | 2 | 3 | 2          | 1 | 0     | 7     | 6 | 5 | 4 |  |

| 1   | 0         | 0   | 4 | 5          | 6 | 7    | 0      | 1 | 2 | 3 | 4 | 5          | 6 | 7     | 0     | 1 | 2 | 3 |  |

| 1   | 0         | 1   | 5 | 6          | 7 | 0    | 1      | 2 | 3 | 4 | 5 | 4          | 7 | 6     | 1     | 0 | 3 | 2 |  |

| 1   | 1         | 0   | 6 | 7          | 0 | 1    | 2      | 3 | 4 | 5 | 6 | 7          | 4 | 5     | 2     | 3 | 0 | 1 |  |

| 1   | 1         | 1   | 7 | 0          | 1 | 2    | 3      | 4 | 5 | 6 | 7 | 6          | 5 | 4     | 3     | 2 | 1 | 0 |  |

# 32M Synchronous OTP

#### ADDRESSING MAP

#### (1) /WORD = "H" : x32 Organization

| Pin Name       | A0  | A1  | A2  | A3  | A4  | A5  | A6  | A7  | A8  | A9  | A10  | A11  | A12  |

|----------------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|------|------|------|

| Row Address    | RA0 | RA1 | RA2 | RA3 | RA4 | RA5 | RA6 | RA7 | RA8 | RA9 | RA10 | RA11 | RA12 |

| Column Address | CA0 | CA1 | CA2 | CA3 | CA4 | CA5 | CA6 | Х   | Х   | х   | Х    | Х    | Х    |

#### (2) /WORD = "L" : x16 Organization

| Pin Name       | A0  | A1  | A2  | A3  | A4  | A5  | A6  | A7  | A8  | A9  | A10  | A11  | A12  |

|----------------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|------|------|------|

| Row Address    | RA0 | RA1 | RA2 | RA3 | RA4 | RA5 | RA6 | RA7 | RA8 | RA9 | RA10 | RA11 | RA12 |

| Column Address | CA0 | CA1 | CA2 | CA3 | CA4 | CA5 | CA6 | CA7 | Х   | Х   | Х    | Х    | Х    |

#### (3) Programming

(X = Don't Care)

(X = Don't Care)

| Address displayed on programmer : x16         | Ad0   | Ad1          | Ad2          | Ad3          | Ad4  | Ad5  | Ad6  | Ad7  | Ad8 | Ad9 | Ad10 | Ad11 | Ad12 |

|-----------------------------------------------|-------|--------------|--------------|--------------|------|------|------|------|-----|-----|------|------|------|

| Device Address : x16<br>STO = "H", AMPX = "L" | CAP0  | CAP1         | CAP2         | CAP3         | CAP4 | CAP5 | CAP6 | CAP7 | A0  | A1  | A2   | A3   | A4   |

|                                               |       |              |              |              |      |      |      |      |     |     |      |      |      |

| Address ( STO = "L" )<br>/WORD = "L" : x16    | CA0   | Note2<br>CA1 | Note3<br>CA2 | CA3          | CA4  | CA5  | CA6  | CA7  | RA0 | RA1 | RA2  | RA3  | RA4  |

| Address ( STO = "L" )<br>/WORD = "H" : x32    | Note1 | CA0          | Note4<br>CA1 | Note5<br>CA2 | CA3  | CA4  | CA5  | CA6  | RA0 | RA1 | RA2  | RA3  | RA4  |

| Address displayed on programmer : x16         | Ad13  | Ad14         | Ad15         | Ad16         | Ad17 | Ad18 | Ad19 | Ad20 |     |     |      |      |      |

| Device Address : x16<br>STO = "H", AMPX = "L" | A5    | A6           | A7           | A8           | A9   | A10  | A11  | A12  |     |     |      |      |      |

|                                               |       |              |              |              |      |      |      |      |     |     |      |      |      |

| Address ( STO = "L" )<br>/WORD = "L" : x16    | RA5   | RA6          | RA7          | RA8          | RA9  | RA10 | RA11 | RA12 |     |     |      |      |      |

| Address ( STO = "L" )<br>/WORD = "H" : x32    | RA5   | RA6          | RA7          | RA8          | RA9  | RA10 | RA11 | RA12 |     |     |      |      |      |

User of MR27V3266D is recommended to study the relation between "Address displayed on programmer" and "Address(STO="L")" ignoring "Device Address:x16, STO="H"".

Order of data on Synchronous Read operation(STO="L") is checked on this table.

"Device Address:x16, STO="H"" will be utilized to design socket adapter on programmer or to check boards designed to mount blank OTP and program OTP on board.

OKI will supply socket adapter to program MR27V3266D as conventional x16 standard OTP. The users and the venders of programmer who use the socket adapter can ignore "Device Address:x16, STO="H"".

#### Note

A0 in programmer distinguishes upper word(x16) or lower word(x16) of Double word(x32). On word(x16) organization the address of device corresponds to the address of programmer. On double word(x32) organization the address numeral code of device is half of that in programmer, and output on DQ0-DQ15 is lower word(A0="0") and output on DQ16-DQ31 is upper word(A0="1").

- 2. CA1 is MSB of burst read on condition of /WORD="L" and BL=4

- 3. CA2 is MSB of burst read on condition of /WORD="L" and BL=8

- 4. CA1 is MSB of burst read on condition of /WORD="H" and BL=4

- 5. CA2 is MSB of burst read on condition of /WORD="H" and BL=8

# READ OPERATIONS

#### CLOCK ( CLK )

The clock input enables MR27V3266D to sample all the inputs, control internal circuitry, and turn on output drivers. All timings are referred to the rising edge of the clock. All inputs with high level CKE and low level /CS should be valid at the rising edge of CLK for proper functionality.

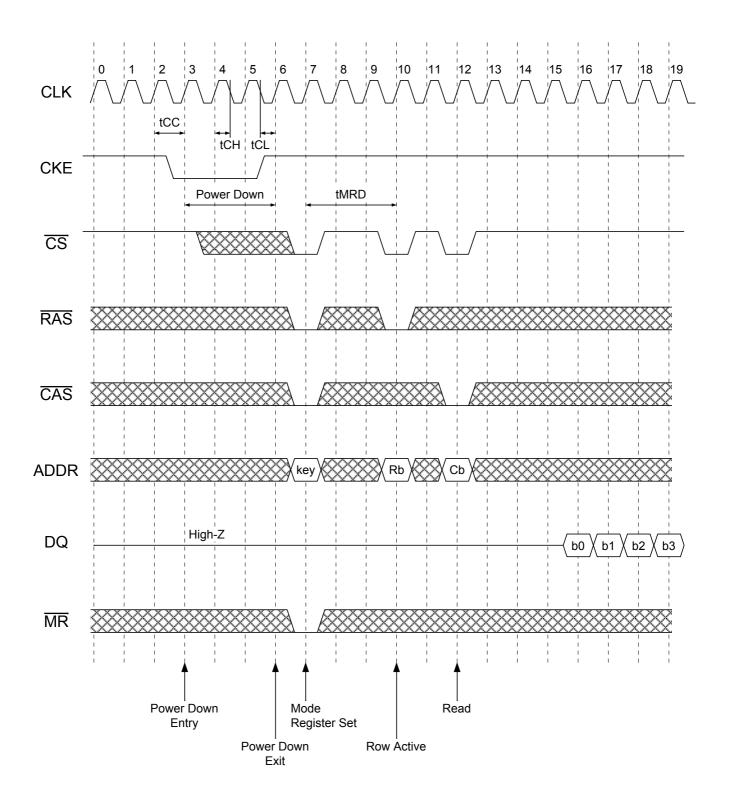

# CLOCK ENABLE ( CKE )

The clock enable(CKE) turns on or switches off the admission of the clock input into the internal clock signal lines. All internal circuits are controlled by the internal clock signal to implement every command. High level CKE sampled at CKEn-1 clock cycle enables the admission of the rising edge of clock input into internal clock line at CKEn cycle. Low level CKE sampled at CKEn-1 cycle suspends the rising edge of CLK at CKEn cycle. The suspension of internal clock signal in all state ignores new input except CKE, and holds internal state and output state. Low level CKE in Active Standby state, defined as Power Down state, cuts power dissipation. In Power Down state the contents of mode register and Row Address are preserved. After recovering high level CKE to exit from Power Down state, MR27V3266D is in Active Standby state. Low level CKE just after the sampling of "Read" command till the completion of burst read, defined as Clock Suspend, makes read operation go on with power dissipation. Any command operation does not interrupted by arbitrary low level CKE. Sampling command with low level CKE preceded with high level CKE is illegal.

#### POWER ON

Apply power and start clock considering following issues.

- During power on Mode Register is initialized into default state. (default state: CAS latency=5, Burst Type=Sequential, Burst length=4)

- After power on MR27V3266D is in Active Standby state and ready for "Mode Register set" command or "Row Active" command. MR27V3266D requires neither command nor waiting time as power on sequence after starting CLK input in order to start "Row Active" command to read data.

- It is recommended in order to utilize default state of Mode Register that /MR and CKE inputs are maintained to be pulled up during power on till the implementation of the first "Row Active" command. After above power on "Row Active" command and "Read" command can be started immediately on default Mode Register state.

- 4. It is recommended that DQM input is maintained to be pulled up to prevent unexpected operation of output buffers.

#### ORGANIZATION CONTROL

Organization of data output(DQ0-DQ31) depends on the logical level on /WORD at the input timing of every "Read" command. High level sampling of /WORD derives double word mode(x32) output and low level sampling of /WORD derives word mode(x16) output. Constant /WORD level input brings consistent organization.

#### MODE REGISTER

Mode register stores the operating mode of MR27V3266D. Operating modes are consisted with CAS latency, Burst Type, and Burst Length. Registration of RAS latency is not required, because RAS to CAS delay(tRCD) is requested independently of system clock. When the contents of Mode register are required to be changed for the next operation, "Mode Register Set" command can be sampled at any cycle in Active Standby state. After "Mode Register Set" command is sampled, /CS must be fixed to logical high level to prevent sampling of new command input during succeeding three clock cycles.

Refer to Mode Register Field Table for the relation between Operation modes and input pin assignment.

## READ OPERATIONS

#### CAS LATENCY

After sampling "Read" command MR27V3266D starts actual data read operation with sense amplifiers, and transmits the data from sense amplifiers to data out buffers to start burst read. This flow of sequential functionality takes time as clock cycles defined as CAS latency(CL). CAS latency is set in Mode Register as either four cycles or five cycles. In this sequence(from sampling "Read" command to start of driving data bus) sense amplifiers consume maximum current flow. The detailed sequence is below.

- 1. Fix column address of memory matrix driver. Row address is already fixed with "Row Active" command. (at 1st cycle)

- 2. Read data of selected memory cells with sense amplifiers.

- 3. Deliver data detected with sense amplifiers to the register for data output latch.

- 4. Couple selectively the section of the register storing each (double)word to output buffers.

- 5. Turn off sense amplifiers to save power. (at CL-1 cycle)

- 6. Enable output buffers to drive data bus. (at CL-1 cycle)

- 7. Data output on data bus can be sampled at the rising edge of system clock at CL cycle.

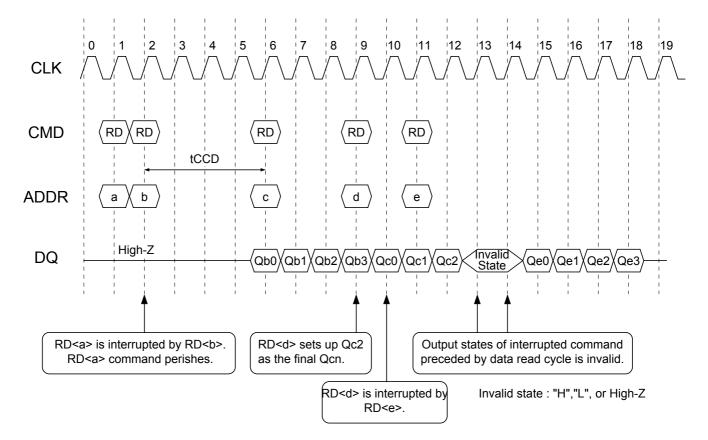

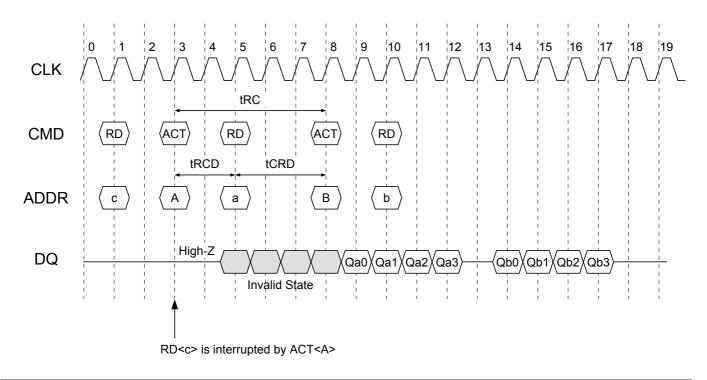

New "Row Active" command or new "Read" command can be sampled to perform gapless burst read at CL-1 clock cycle of the last "Read" command. New command preceding CL-1 cycle interrupts sense amplifiers to read the data at the selected memory cells of the last "Read" command. Interrupted "Read" command perishes or outputs invalid data before the starting of the data burst of new "Read" command. Refer to the timing chart of "Burst Read/Interrupt I" and "Burst Read/Interrupt II".

#### BURST READ

Data outputs are consecutive during the cycle number defined as Burst Length(BL). The latest burst read is completed unless any interruption such as "Precharge" command stops the sequential data output. Burst Length is set in Mode Register as either four or eight. After sampling of "Read" command the first output can be read at the cycle delayed by CAS latency. Burst Type is also stored in Mode register as either sequential or interleave. The output buffers go into high impedance state after burst read sequence is finished, unless a new "Read" command has been sampled to perform gapless read or preemptive read. Burst read can be interrupted by "Burst Stop" command or "Precharge" command at the cycle delayed by CAS latency from the command. On condition that reading data with sense amplifiers of preceding "Read" command is not interrupted by new "Read" command or "Row active" command, burst read of preceding "Read" command is continued regularly until the burst data sequence of the new "Read" command starts. The new(latest) burst data sequence always starts regularly.

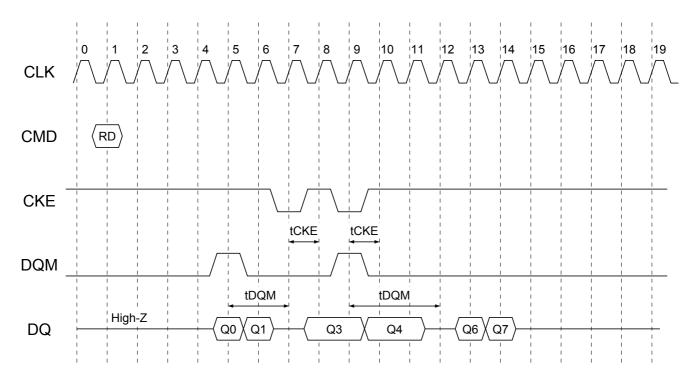

#### DQM

Input level on DQM is sampled at rising edge of system clock to mask data at two cycles later. Output of masked data is high-Z state.

# READ OPERATIONS

# MODE TRANSITION CHART

\*All operation of "Precharge" command is to stop burst read.

#### Note

# ABSOLUTE MAXIMUM RATINGS

| Parameter                          | Symbol        | Min  | Max       | Unit     |

|------------------------------------|---------------|------|-----------|----------|

| Voltage on Vcc Relative to Vss     | Vcc,VccQ      | -0.5 | 5         | V        |

| Voltage on Any pin Relative to Vss | VIN, VOUT, DC | -0.5 | Vcc + 0.5 | V        |

| Voltage on VPP Relative to Vss     | Vpp           | -0.5 | 10        | V        |

| Operating Temperature              | Та            | 0    | 70        | degree C |

| Storage Temperature                | Tstg          | -55  | 125       | degree C |

| Short Circuit Current              | los           | -    | 50        | mA       |

| Power Dissipation                  | PD            | -    | 1         | W        |

# RECOMMENDED OPERATING CONDITIONS for SYNCHRONOUS READ

| Parameter               | Symbol   | Min  | Тур | Max       | Unit     |

|-------------------------|----------|------|-----|-----------|----------|

| Power Supply Voltage    | Vcc,VccQ | 3.0  | 3.3 | 3.6       | V        |

| Voltage Level on DC pin | -        | -0.5 | -   | Vcc + 0.3 | V        |

| Input High Voltage      | Viн      | 2.0  | -   | 5         | V        |

| Input Low Voltage       | VIL      | -0.3 | -   | 0.8       | V        |

| Operating Temperature   | Та       | 0    | -   | 70        | degree C |

#### CAPACITANCE

| Parameter          | Symbol | Min | Max | Unit |

|--------------------|--------|-----|-----|------|

| Input Capacitance  | CIN    | -   | 5   | pF   |

| Output Capacitance | Соит   | -   | 7   | pF   |

# DC CHARACTERISTICS FOR SYNCHRONOUS READ

| Parameter                  | Symbol | Min  | Max       | Unit | Test condition        |                                           |  |

|----------------------------|--------|------|-----------|------|-----------------------|-------------------------------------------|--|

| Power Down Current         | ICCS1  | -    | 1         | mA   | CKE = 0.8V            | 100 15                                    |  |

|                            | ICCS2  | -    | 100       | μA   | CKE = 0V              | tCC = 15ns                                |  |

| Active Standby Current     | ICC1   | -    | 100       | mA   | CKE = 2.0V            | /CS = Vcc<br>tCC = 15ns                   |  |

| Gapless Burst Read Current | ICC2   | -    | 150       | mA   | CKE = Vcc             | tCC = 15ns,<br>DQM = H, CL = 4,<br>BL = 4 |  |

| Input Leak Current         | lı∟    | -10  | 10        | μA   | 0V > VIN > VCC + 0.3V |                                           |  |

| Output Leak Current        | IOL    | -10  | 10        | μA   | 0V > VIN > V0         | эс                                        |  |

| Input High Voltage         | Viн    | 2.0  | 5         | V    |                       |                                           |  |

| Input Low Voltage          | VIL    | -0.3 | 0.8       | V    | Note1                 |                                           |  |

| Voltage Level on DC pin    |        | -0.5 | Vcc + 0.3 | V    |                       |                                           |  |

| Output High Voltage Level  | Vон    | 2.4  | -         | V    | Іон = -2mA            |                                           |  |

| Output Low Voltage Level   | Vol    | -    | 0.4       | V    | IOL = 2mA             |                                           |  |

(Voltage levels are referred to Vss)

#### Note

VIL min can be -1.5V for the pulse width shorter than 10ns. Pulse width is measured at 50% of pulse peak level.

# AC CHARACTERISTICS FOR SYNCHRONOUS READ (1/2)

| Parameter                                            |        |        |      | Min         | Max | Unit  | Notes |

|------------------------------------------------------|--------|--------|------|-------------|-----|-------|-------|

| CLK Cycle time                                       | tCC    | 15     | -    | ns          |     |       |       |

| Data to Valid Output Delay                           | tAC    | -      | 9    | ns          |     |       |       |

| Data Output Hold Time                                |        |        | tOH  | 3           | _   | ns    |       |

| CLK High Pulse Width                                 |        |        | tCH  | 4           | -   | ns    |       |

| CLK Low Pulse Width                                  |        |        | tCL  | 4           | _   | ns    |       |

| Input Setup Time                                     |        |        | tSI  | 3           | -   | ns    |       |

| Input Hold Time                                      |        |        | tHI  | 1.5         | _   | ns    |       |

| CLK to Output in Low-Z                               |        |        | tOLZ | 0           | -   | ns    |       |

| CLK to Output in High-Z                              |        |        | tOHZ | -           | 10  | ns    |       |

| Input Level Transition Time                          |        |        | tT   | 0.1         | 10  | ns    |       |

| "Row Active" to "Read" Delay Time                    |        |        | tRCD | 1CLK        | -   | Cycle | 2     |

|                                                      |        |        |      | 2CLK        | -   | Cycle |       |

| "Read" to "Row Active" delay                         |        | CL = 4 | tCRD | 3CLK        | -   | Cycle | 1,2   |

| (Words of preceding "Read"                           | BL = 4 | CL = 5 | tCRD | 4CLK        | -   | Cycle | 1     |

| command can be read)<br>< Random Access >            |        | CL = 4 | tCRD | 3CLK        | _   | Cycle | 1,2   |

|                                                      | BL = 8 | CL = 5 | tCRD | 4CLK        | _   | Cycle | 1     |

| "Read" to "Read" delay                               | BL = 4 | CL = 4 | tCCD | 3CLK        | -   | Cycle | 1,2   |

| (Words of preceding "Read"                           |        | CL = 5 | tCCD | 4CLK        | -   | Cycle | 1     |

| command can be read)<br>< Sequential Access >        |        | CL = 4 | tCCD | 3CLK        | -   | Cycle | 1,2   |

|                                                      | BL = 8 | CL = 5 | tCCD | 4CLK        | -   | Cycle | 1     |

| "Row Active" Cycle Time                              | BL = 4 | CL = 4 | tRC  | 3CLK + tRCD | -   | Cycle | 1,2   |

| ( Words of preceding "Read"<br>command can be read ) | DL = 4 | CL = 5 | tRC  | 4CLK + tRCD | -   | Cycle | 1     |

| < Random Access >                                    | BL = 8 | CL = 4 | tRC  | 3CLK + tRCD | -   | Cycle | 1,2   |

|                                                      | DL = 0 | CL = 5 | tRC  | 4CLK + tRCD | -   | Cycle | 1     |

| "Read" to "Read" delay                               |        | CL = 4 | tCCD | 4CLK        | -   | Cycle | 2     |

| ( Gapless burst read )                               | BL = 4 | CL = 5 | tCCD | 4CLK        | _   | Cycle | 1     |

| < Sequential Access >                                | BL = 8 | CL = 4 | tCCD | 8CLK        | -   | Cycle | 2     |

|                                                      | tCCD   | 8CLK   | -    | Cycle       |     |       |       |

| "Read" to "Burst Stop" Delay                         |        |        |      | 1CLK        | -   | Cycle |       |

| "Read" to "Precharge" Delay                          |        | 1CLK   | -    | Cycle       |     |       |       |

| Power Down Exit Setup Time                           |        |        | tPDE | tSI + 1CLK  | -   | Cycle |       |

Note

Shortage of clock cycles interrupt the data sensing of preceding "Read" command. The shortage of cycle time for preceding command is detected by internal command controller to cease the preceding command operation. The latest "Row Active" or "Read" command is completed.

When legal tCCD is shorter than BL, burst read is terminated with another burst read.

2. Up to 50MHz

# AC CHARACTERISTICS FOR SYNCHRONOUS READ (2/2)

| Parameter                                   | Symbol | Value | Unit  | Notes |

|---------------------------------------------|--------|-------|-------|-------|

| Clock Disable time from CKE                 | tCKE   | 1CLK  | Cycle |       |

| Clock Enable time from CKE                  | tCKE   | 1CLK  | Cycle |       |

| Output High impedance from DQM              | tDQM   | 2CLK  | Cycle |       |

| Recovery from DQM                           | tDQM   | 2CLK  | Cycle |       |

| Output High impedance from "Burst Stop"     | tBOH   | CL    | Cycle |       |

| Output High impedance from "Precharge"      | tPOH   | CL    | Cycle |       |

| "Row Active" input from "Mode Register Set" | tMRD   | 3     | Cycle |       |

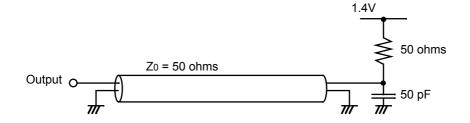

# AC TEST CONDITIONS

| Parameter                                      | Values                  | Notes |

|------------------------------------------------|-------------------------|-------|

| Input Signal Levels                            | VIH / VIL = 2.4V / 0.4V |       |

| Timing Reference Level of Input/Output Signals | 1.4V                    |       |

| Transition Time of Input Signals               | tr / tf = 1ns / 1ns     | 1     |

| Output Load                                    | LVTTL                   | 2     |

#### Note1

Transition time of input signals is measured between 0.8V and 2.0V . If tr or tf is longer than 1ns, "Timing Reference Level of Input/Output Signals" is changed to VIL or VIH / 0.8V or 2.0V respectively.

#### Note2

Output Load

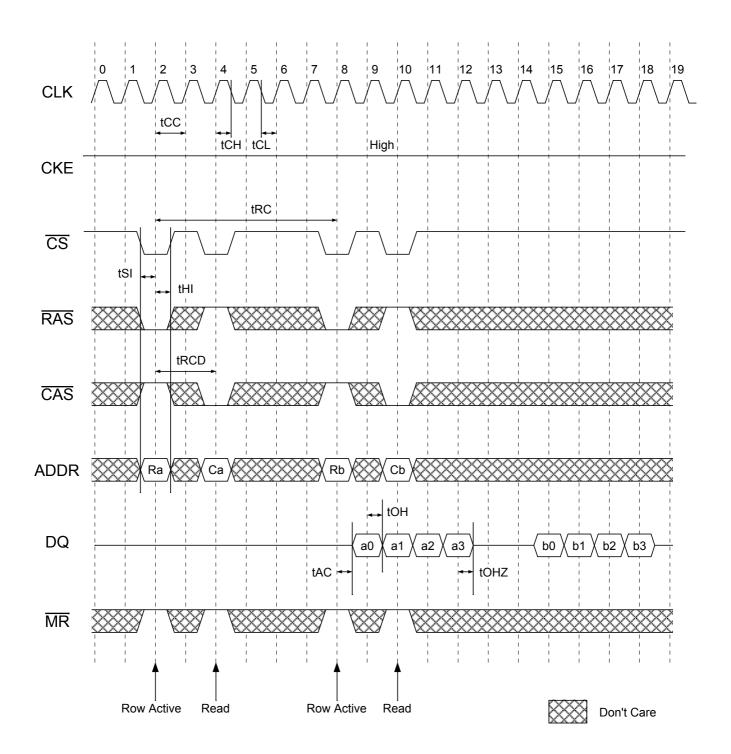

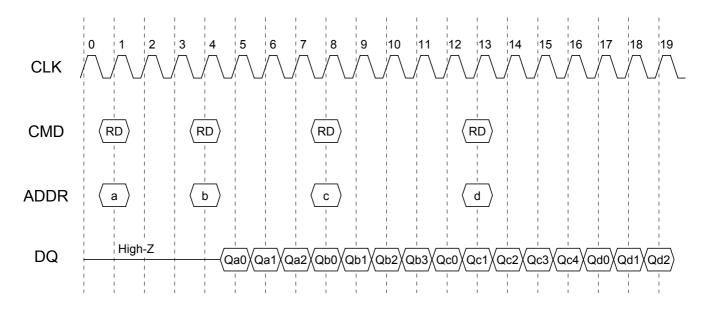

Read Cycle I : Random Access @ CAS Latency = 5, Burst Length = 4

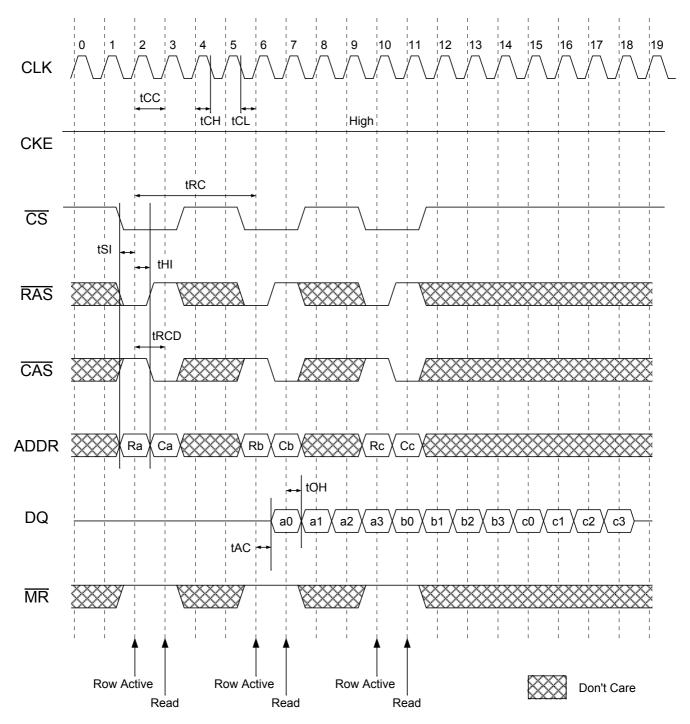

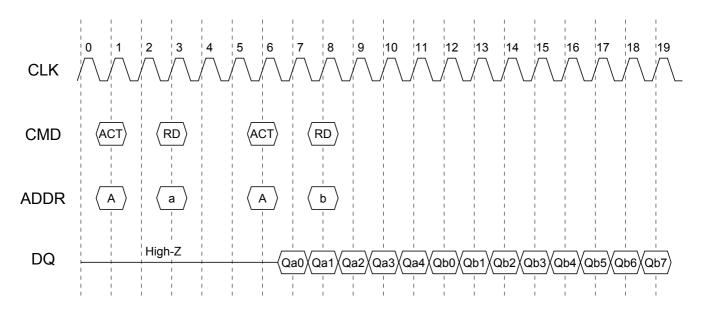

Read Cycle II : Random Access with Gapless Burst @ CAS Latency = 4, Burst Length = 4 (Up to 50MHz)

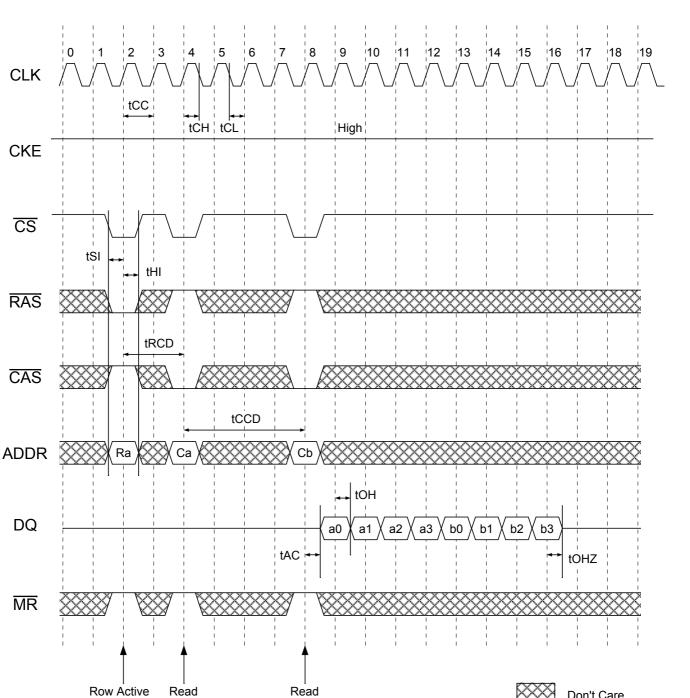

Read Cycle III : Consecutive Column Read @ CAS Latency = 5, Burst Length = 4

Don't Care

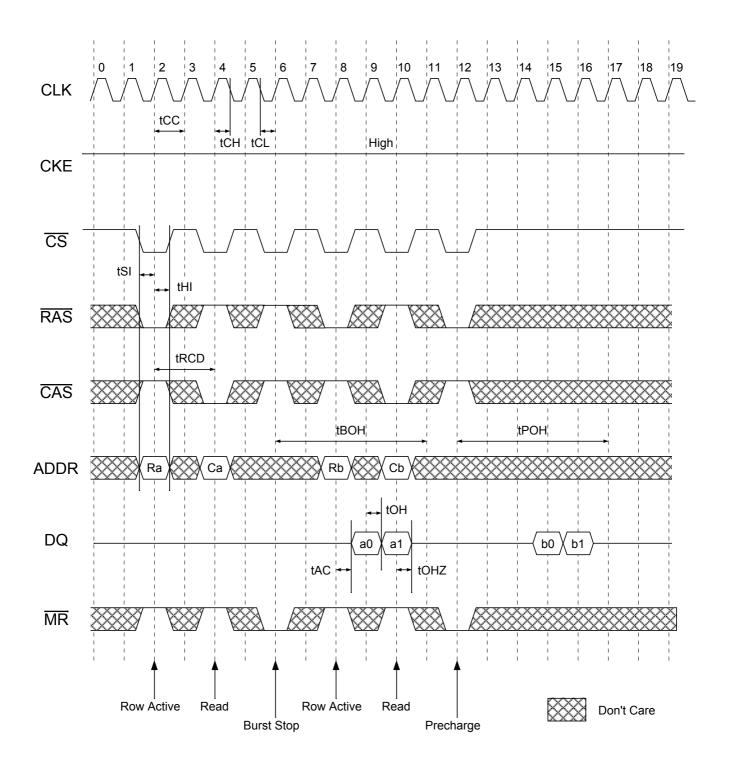

"Burst Stop" command & "Precharge" command @ CAS Latency = 5

Note

- 1. At cycle number 9, 12, 13, rising edge of internal clock is omitted because of low level CKE at cycle 8, 11,12.

- 2. Clock suspend is defined with the low level CKE sampled in the period of Read operation.

Minimum current consumption is expected in Power Down state. Low level CKE sampled only in Active Standby state is defined as Power Down "Entry" command and it cuts current consumption into minimum level. After Power Down "Exit" the contents of Mode Register and row address is preserved. During Power Down state no command can be sampled. Mode Register Set @ CAS Latency = 4, Burst Length = 4

DQM Operation @ CAS Latency = 4, Burst Length = 8

Burst Read / Interrupt I @ CAS Latency = 4, Burst Length = 4

Burst Read / Interrupt II @ CAS Latency = 4, Burst Length = 4

Preemptive Burst Read I @ CAS Latency = 4, Burst Length = 8

Preemptive Burst Read II @ CAS Latency = 4, Burst Length = 8

#### RECOMMENDED OPERATING CONDITIONS AND DC CHARACTERISTICS FOR PROGRAMMING ( STO is High Level )

| Parameter                          | Symbol | Min  | Тур  | Max       | Unit     | Condition                              | Note |

|------------------------------------|--------|------|------|-----------|----------|----------------------------------------|------|

|                                    | VPP1   | 9.5  | 9.75 | 10        | V        | Program Mode                           | 1    |

| VPP Supply Voltage                 | VPP2   | -0.3 | Vcc  | Vcc + 0.5 | V        | Read Mode                              | 2    |

|                                    | Vcc1   | 3.9  | 4.0  | 4.1       | V        | Program Mode                           | 1    |

| Vcc Supply Voltage                 | Vcc2   | 2.9  | 3.0  | 3.1       | V        | Read Mode                              | 2    |

|                                    | Vcc3   | 2.9  | -    | 3.4       | V        | Optional Read Mode                     | 2    |

|                                    | IPP1   | -    | -    | 50        | mA       | VPP = 10V, VCC = 4.1V                  |      |

| VPP Current                        | IPP2   | -    | -    | 100       | μA       | VPP = VCC = 4.1V                       |      |

|                                    | ICCP1  | -    | -    | 150       | mA       | VPP = 10V, VCC = 4.1V                  |      |

| Vcc Current                        | ICCP2  | -    | -    | 150       | mA       | VPP = VCC = 4.1V                       |      |

|                                    | Іссрз  | -    | -    | 10        | mA       | VPP = VCC = 4.1V,<br>tC = 1µS, /CE = H |      |

| Input Leak Current                 | lı∟    | -10  | -    | 10        | μA       |                                        |      |

| Output Leak Current                | IOL    | -10  | -    | 10        | μA       |                                        |      |

| Output High Voltage Level          | Vон    | 2.4  | -    | -         | V        | Іон = -400μА                           |      |

| Output Low Voltage Level           | Vol    | -    | -    | 0.45      | V        | IoL = 2.1mA                            |      |

| Input High Voltage                 | Vih    | 2.9  | -    | Vcc + 0.5 | V        | Vcc = 4.1V                             |      |

| Input Low Voltage                  | VIL    | -0.3 | -    | 0.45      | V        | Vcc = 2.9V                             |      |

| Voltage Level on DC pin            |        | -0.3 | -    | Vcc + 0.5 | V        |                                        |      |

| /OE Input Distinctive High Voltage | Ин     | 7.75 | 8    | 8.25      | V        |                                        | 1    |

| Operating Temperature              | Ta     | 20   | 25   | 30        | degree C |                                        |      |

(Voltage levels are referred to Vss)

Notes

1. Program represents the modes below.

Program, Program Verify, Program Inhibit

2. Read represents the modes below. Read, Output Disable, Standby

# FUNCTION TABLE FOR PROGRAMMING

|        | Function        | Vcc  | Vpp   | /CE | /OE | WORD | DQ0-<br>DQ15 | CAP0-<br>CAP7 | Add.     | /RAS<br>/CAS | AMPX | STO | Note |

|--------|-----------------|------|-------|-----|-----|------|--------------|---------------|----------|--------------|------|-----|------|

|        | Program         | 4.0V | 9.75V | L   | Н   | L    | Din          | A0 - A7       | A8 - A20 | Х            | L    | Н   | S    |

|        | Program Inhibit | 4.0V | 9.75V | Н   | Н   | L    | HZ           | A0 - A7       | A8 - A20 | Х            | L    | Н   |      |

|        | Program Verify  | 4.0V | 9.75V | L   | L   | L    | Dout         | A0 - A7       | A8 - A20 | Х            | L    | Н   |      |

| Static | Read            | 3.0V | 3.0V  | L   | L   | L    | Dout         | A0 - A7       | A8 - A20 | Х            | L    | Н   |      |

| Full S | Output Disable  | 3.0V | 3.0V  | L   | Н   | L    | HZ           | A0 - A7       | A8 - A20 | Х            | L    | Н   |      |

|        | Standby         | 3.0V | 3.0V  | Н   | Х   | L    | HZ           | A0 - A7       | A8 - A20 | Х            | L    | Н   |      |

|        | Contact Check   | 4.0V | 4.0V  | L   | 8V  | L    | AAAA         | AA            | 16AA     | Х            | Х    | Н   | 1    |

|        | Contact Check   | 4.0V | 4.0V  | L   | 8V  | L    | 5555         | 55            | 0955     | Х            | Х    | Н   | 1    |

|        |                 | -    |       |     | -   |      |              |               |          |              |      |     |      |

|        |                 |      |       |     |     |      |              |               |          |              |      |     |      |

|        |                 |      |       |     |     |      |              |               |          |              |      |     |      |

|        |                 |      |       |     |     |      |              |               |          |              |      |     |      |

|        |                 |      |       |     |     |      |              |               |          |              |      |     |      |

|        |                 |      |       |     |     |      |              |               |          |              |      |     |      |

|        |                 |      |       |     |     |      |              |               |          |              |      |     |      |

|        |                 |      |       |     |     |      |              |               |          |              |      |     |      |

(H = Logical High, L = Logical Low, X = Don't Care in the range of logical level)

#### Note

Dual procedures to check complementary output codes on the indicated complementary address inputs assure every address, DQ, and /OE pin connection. When address input code is incorrect, output code is "FFFF".

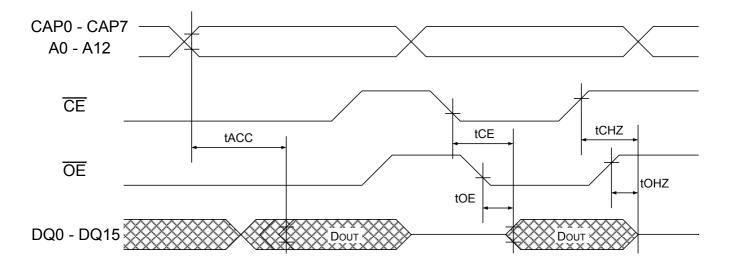

#### **PROGRAMMING OPERATION**

#### STO

Synchronous read is far different from anyone of conventional nonvolatile memories. STO input level switches operation mode either synchronous read or conventional EPROM/OTP type programming. The word "Programming" contains actual programming(inject electrons into floating gates of memory cells), program verify(verify data on actual programming bias), and read on programmer. High level STO assures full compatible programming operation with conventional EPROM/OTP. Low level STO assures high speed synchronous read. "Full static programming" is recommended for loose devices.

#### PROGRAM

MR27V3266D is programmed with 10 microsecond pulse width on 4.0V Vcc and 9.75V VPP. OKI recommends consecutive programming, because of the similarity of device sorting process. Almost all words can be programmed sufficiently with one pulse. Programmers are recommended to be equipped with large current capacity of VPP and Vcc supplying source and responsive capacitance(around  $0.1\mu$ F) on each socket to stabilize VPP and Vcc voltage level, since switching speed of transistors produced with advanced wafer process technology is very fast and high voltage immunity of those is decreasing. Excessive overshooting of VPP voltage may destroy device permanently. Excessive overshooting of Vcc voltage may cause misprogramming or disturbance. Excessive undershooting of VPP or Vcc level may cause insufficient electron injection into floating gate. Additional programming increases programming time.

#### PROGRAM INHIBIT

When VPP is 9.75V, address must be changed only in "Program Inhibit" mode.

#### PROGRAM VERIFY

This operation mode is utilized to check that each word is programmed sufficiently. It is recommended to take time more than some seconds between actual programming and "Program Verify" ("Read") for each word, because just after the actual programming(injection of electron into floating gate) of each word, pretended excessive electrons are attached around floating gate to show false sufficiency of programming. Programing flow is selected to separate "Program" and "Program Verify" to take enough time.

#### CONTACT CHECK

When programmed OTP lot contains failed devices by the rate of more than 0.1%, some of or almost all failed devices are caused by misconnection with the sockets on the programmer. The possibility of misconnection is increased with surface mount devices such as SOP or TSOP.

OKI will supply socket adapters exclusively applicable to MR27V3266D, but connections of all pins can not be assured with these socket adapters.

Following contact check sequence before actual programming is recommended.

- 1. Supply Vcc with 4.0V power source.

- 2. Bias logical low level on /CE.

- 3. Supply 8V on /OE to enable contact check mode.

- Apply two address codes and check each output respectively. If irregular address code is applied, then output is FFFF.

<Connection of Address, Dout, Vcc, /OE, and STO pins are checked>

- 5. /CE must be checked with a method suitable for the programmer.

- 6. VPP can be checked with current flow(more than 100  $\mu$ A) in Program Inhibit mode.

- 7. AMPX and /WORD pins is open in the socket adapter, since these pins are pulled down to Vss when STO is high.

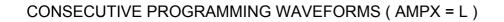

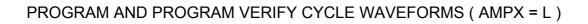

# AC CHARACTERISTICS FOR PROGRAMMING (STO is High Level)

| Parameter           | Symbol | Min | Тур | Max | Unit | Condition               | Notes |

|---------------------|--------|-----|-----|-----|------|-------------------------|-------|

| VPP Setup Time      | tVS    | 2   | -   | -   | μs   | VPP = 9.75V, VCC = 4.0V |       |

| Address Setup Time  | tAS    | 100 | -   | -   | ns   | VPP = 9.75V, VCC = 4.0V |       |

| Data Setup Time     | tDS    | 100 | -   | -   | ns   | VPP = 9.75V, VCC = 4.0V |       |

| Address Hold Time   | tAH    | 2   | -   | -   | μs   | VPP = 9.75V, VCC = 4.0V |       |

| Data Hold Time      | tDH    | 100 | -   | -   | ns   | VPP = 9.75V, VCC = 4.0V |       |

| Program Pulse Width | tPW    | 9   | 10  | 11  | μs   | VPP = 9.75V, VCC = 4.0V |       |

| /OE Setup Time      | tOES   | 2   | -   | -   | μs   | VPP = 9.75V, VCC = 4.0V |       |

| Data Valid from /OE | tOE    | -   | -   | 100 | ns   | VPP = 9.75V, VCC = 4.0V |       |

|                     |        |     |     |     |      |                         |       |

|                     |        |     |     |     |      |                         |       |

|                     |        |     |     |     |      |                         |       |

|                     |        |     |     |     |      |                         |       |

|                     |        |     |     |     |      |                         |       |

|                     |        |     |     |     |      |                         |       |

|                     |        |     |     |     |      |                         |       |

|                     |        |     |     |     |      |                         |       |

|                     |        |     |     |     |      |                         |       |

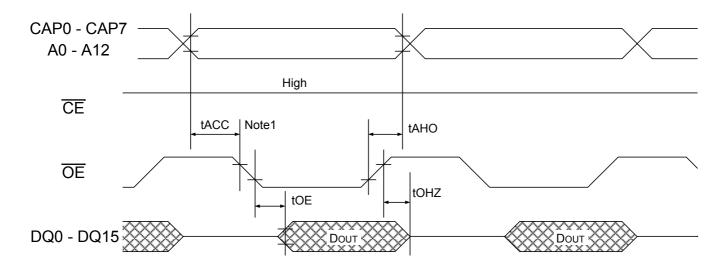

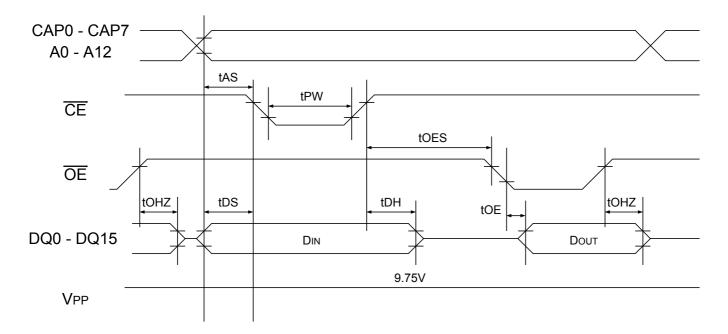

# AC CHARACTERISTICS FOR VERIFY AND READ (STO is High Level)

| Parameter                      | Symbol | Min | Тур | Max | Unit | Condition              | Notes |

|--------------------------------|--------|-----|-----|-----|------|------------------------|-------|

| Address Access Time            | tACC   | -   | -   | 80  | ns   | VPP = VCC = 2.9 - 4.1V |       |

| /RAS Access Time               | tACC   | -   | -   | 80  | ns   | VPP = VCC = 2.9 - 4.1V |       |

| /CAS Access Time               | tACC   | -   | -   | 80  | ns   | VPP = VCC = 2.9 - 4.1V |       |

| /CE Access Time                | tCE    | -   | -   | 80  | ns   | VPP = VCC = 2.9 - 4.1V |       |

| /OE Access Time                | tOE    | -   | -   | 30  | ns   | VPP = VCC = 2.9 - 4.1V |       |

| /CE High to Output Float Delay | tCHZ   | -   | -   | 25  | ns   | VPP = VCC = 2.9 - 4.1V |       |

| /OE High to Output Float Delay | tOHZ   | -   | -   | 20  | ns   | VPP = VCC = 2.9 - 4.1V |       |

| Address Hold from /OE high     | tAHO   | 0   | -   | -   | ns   | VPP = VCC = 2.9 - 4.1V |       |

|                                |        |     |     |     |      |                        |       |

|                                |        |     |     |     |      |                        |       |

|                                |        |     |     |     |      |                        |       |

|                                |        |     |     |     |      |                        |       |

|                                |        |     |     |     |      |                        |       |

|                                |        |     |     |     |      |                        |       |

|                                |        |     |     |     |      |                        |       |

|                                |        |     |     |     |      |                        |       |

# CONSECUTIVE PROGRAM VERIFY CYCLE (VPP = 9.75V, AMPX = L)

Note

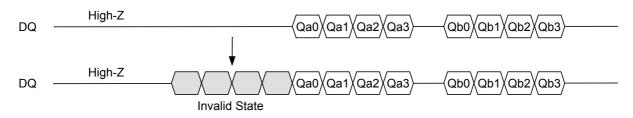

1. Falling edge of /OE must be preceded with data stabilizing time of more than tACC max., because output of invalid state can cause unstable system operation.

Output buffer of MR27V3266D is designed to drive 100pF load in 5ns.

# READ CYCLE ( AMPX = L )

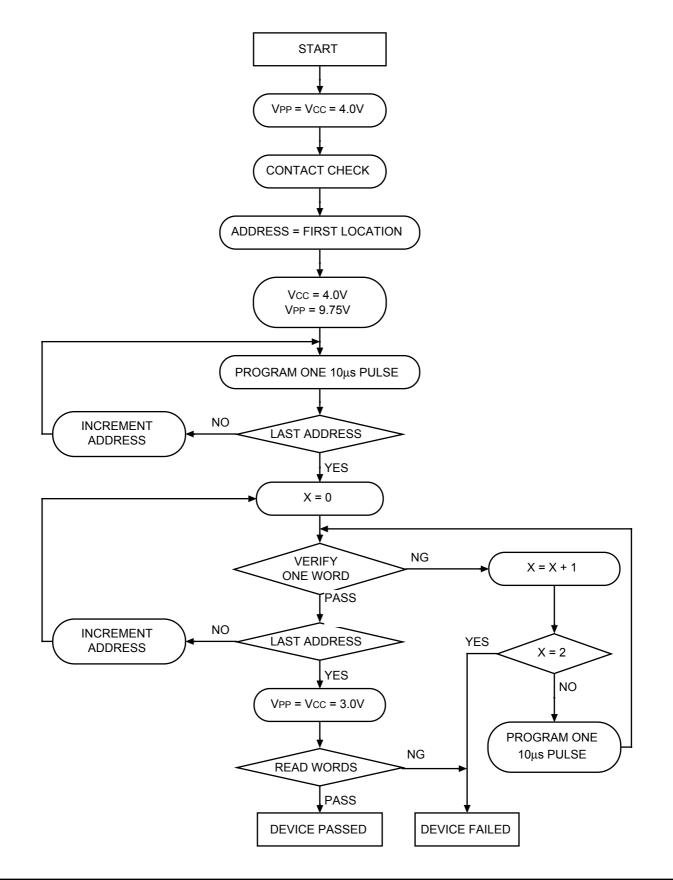

# PROGRAMMING FLOW CHART

#### **REVISION HISTORY**

Revision 2.0 — Revision 2.1

1. Page 13

Active Standby Current (ICC1) was revised from 50mA to 100mA.

2. Page 14

Regarding Note 1, it was revised from " .... internal command controller to cease the preceding command operation to keep output buffer high-Z state instead of the null output " to " .... internal command controller to cease the preceding command operation " ( underlined portion was eliminated. ).

3. Page 24

Regarding the timing diagram of " Burst Read / Interrupt II , DQ timing diagram was revised as bellow :

#### Revision 2.1 — Revision 2.2

1. Page 14

tRCD (" Row Active " to " Read " Delay Time ) was revised from 1CLK to 2CLK.

2. Page 17

Contents of this page ( timing diagram of " Random Access with Gapless Burst ") was eliminated.

#### Revision 2.2 — Revision 2.3

1. Page 5, 8

All descriptions of the case in " AMPX is high " were eliminated.

2. Page 27

All function table of "Address Multiplexed " and relational notes (2,3 and 4) were eliminated.

- 3. Page 29 , 30

- All timing parameters regarding "Address Multiplexed " and relational notes (1 and 2) were eliminated.

- 4. Page 31, 32, 33, 34 All timing waveforms regarding "Address Multiplexed " were eliminated.

#### Revision 2.3 — Revision 2.4

1. Page 14

tAC (Data to Valid Output Delay) was revised from 10ns to 9ns. tOH (Data Output Hold Time) was revised from 4ns to 3ns. tSI (Input Setup Time) was revised from 4ns to 3ns. tHI (Input Hold Time) was revised from 2ns to 1.5ns. tRCD (" Row Active " to " Read " Delay Time) =1 CLK was added in case of up to 50MHz. 2. Page 17

Contents of this page (timing diagram of "Random Access with Gapless Burst") was republished in case of up to 50MHz.