# The MRFIC Line 900 MHz GaAs Integrated Power Amplifier

This integrated circuit is intended for GSM class IV handsets. The device is specified for 2.8 watts output power and 48% minimum power added efficiency under GSM signal conditions at 4.8 Volt supply voltage. To achieve this superior performance, Motorola's planar GaAs MESFET process is employed. The device is packaged in the PFP–16 Power Flat Package which gives excellent thermal performance through a solderable backside contact.

- Usable Frequency Range 800 to 1000 MHz

- Typical Output Power:

36.0 dBm @ 5.8 Volts 35.0 dBm @ 4.8 Volts

- 31.5 dBm @ 3.6 Volts

- 48% Minimum Power Added Efficiency

- Low Parasitic, High Thermal Dissipation Package

- Order MRFIC0913R2 for Tape and Reel Option. R2 Suffix = 1,500 Units per 16 mm, 13 inch Reel.

- Device Marking = M0913

# MRFIC0913

900 MHz GSM CELLULAR INTEGRATED POWER AMPLIFIER GaAs MONOLITHIC INTEGRATED CIRCUIT

#### ABSOLUTE MAXIMUM RATINGS (T<sub>A</sub> = 25°C unless otherwise noted)

| Rating                               | Symbol                            | Value       | Unit |

|--------------------------------------|-----------------------------------|-------------|------|

| Supply Voltage                       | V <sub>D1</sub> , V <sub>D2</sub> | 9           | Vdc  |

| RF Input Power                       | Pin                               | 15          | dBm  |

| Gate Voltage                         | V <sub>SS</sub>                   | -6          | Vdc  |

| Ambient Operating Temperature        | T <sub>A</sub>                    | -40 to +85  | °C   |

| Storage Temperature                  | T <sub>stg</sub>                  | -65 to +150 | °C   |

| Thermal Resistance, Junction to Case | R <sub>0JC</sub>                  | 10          | °C/W |

### **RECOMMENDED OPERATING RANGES**

| Parameter          |                                   | Value       | Unit |

|--------------------|-----------------------------------|-------------|------|

| Supply Voltage     | V <sub>D1</sub> , V <sub>D2</sub> | 2.7 to 7.5  | Vdc  |

| Gate Voltage       | V <sub>SS</sub>                   | −5 to −3    | Vdc  |

| RF Frequency Range | <sup>f</sup> RF                   | 800 to 1000 | MHz  |

| RF Input Power     | P <sub>RF</sub>                   | 6 to 13     | dBm  |

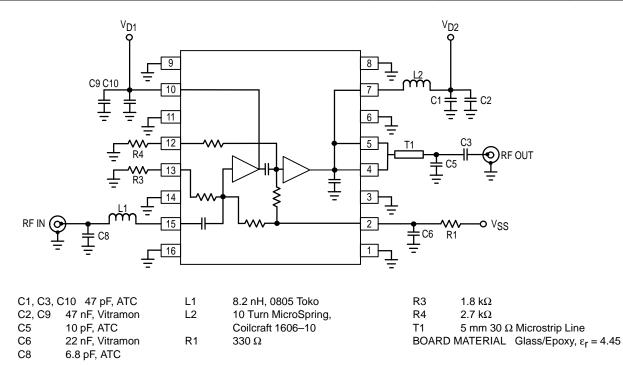

**ELECTRICAL CHARACTERISTICS** ( $V_{D1}$ ,  $V_{D2}$  = 4.8 V,  $V_{SS}$  = -4 V,  $P_{in}$  = 10 dBm, Peak Measurement at 12.5% Duty Cycle, 4.6 ms Period,  $T_A$  = 25°C unless otherwise noted. Measured in Reference Circuit Shown in Figure 1.)

| Characteristic                                                                                                                                                                                                                                                                                                                                                                           |                                                                          | Тур  | Max        | Unit |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|------|------------|------|

| Frequency Range                                                                                                                                                                                                                                                                                                                                                                          | 880                                                                      | —    | 915        | MHz  |

| Output Power                                                                                                                                                                                                                                                                                                                                                                             | 34.5                                                                     | 35   | —          | dBm  |

| Power Added Efficiency                                                                                                                                                                                                                                                                                                                                                                   | 48                                                                       | —    | —          | %    |

| Input VSWR                                                                                                                                                                                                                                                                                                                                                                               | _                                                                        | 2:1  | —          | VSWR |

| Harmonic Output<br>2nd<br>3rd                                                                                                                                                                                                                                                                                                                                                            | _                                                                        |      | -30<br>-35 | dBc  |

| Output Power at Low voltage ( $V_{D1}$ , $V_{D2}$ = 4.0 V)                                                                                                                                                                                                                                                                                                                               | 33.3                                                                     | 33.5 | —          | dBm  |

| Output Power, Isolation (V <sub>D1</sub> , V <sub>D2</sub> = 0 V)                                                                                                                                                                                                                                                                                                                        | _                                                                        | -20  | -15        | dBm  |

| Noise Power in 100 kHz, 925 to 960 MHz                                                                                                                                                                                                                                                                                                                                                   | -                                                                        | —    | -90        | dBm  |

| $ \begin{array}{l} \text{Stability} - \text{Spurious Output (P}_{\text{in}} = 10 \text{ to } 13 \text{ dBm}, \text{P}_{\text{out}} = 5 \text{ to } 35 \text{ dBm}, \text{Load} \\ \text{VSWR} = 6:1 \text{ at any Phase Angle, Source VSWR} = 3:1, \text{ at any Phase Angle,} \\ \text{V}_{\text{D1}}, \text{V}_{\text{D2}} \text{ adjusted for Specified P}_{\text{out}} \end{array} $ | _                                                                        | _    | -60        | dBc  |

| Load Mismatch stress (P <sub>in</sub> = 10 to 13 dBm, P <sub>out</sub> = 5 to 35 dBm, Load VSWR = 10:1 at any Phase Angle, V <sub>D1</sub> , V <sub>D2</sub> Adjusted for Specified P <sub>out</sub> )                                                                                                                                                                                   | No Degradation in Output Power after Returning to<br>Standard Conditions |      |            |      |

| 3 dB V <sub>DD</sub> Bandwidth (V <sub>D1</sub> , V <sub>D2</sub> = 0 to 6 V)                                                                                                                                                                                                                                                                                                            | 1                                                                        | _    | —          | MHz  |

| Negative Supply Current                                                                                                                                                                                                                                                                                                                                                                  | -                                                                        | _    | 1.25       | mA   |

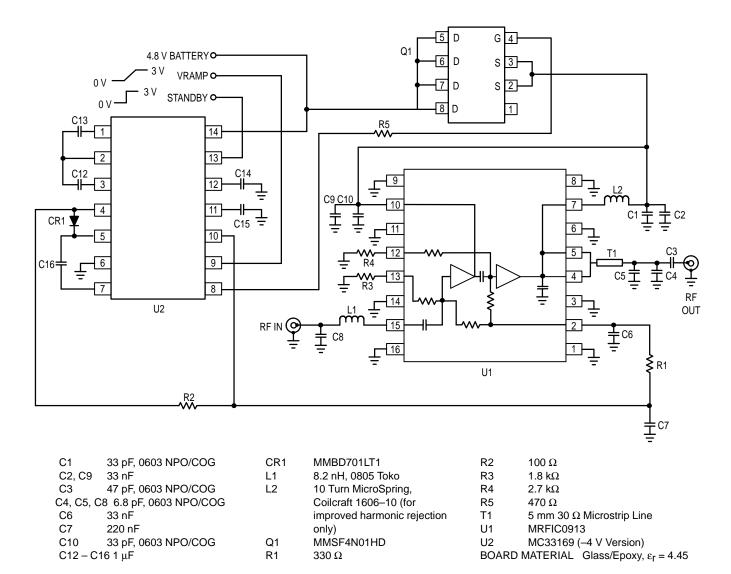

Note: Use of a Schottky diode such as MMBD701LT1 for CR1 is mandatory below 3.6 V. A general purpose silicon diode can be used above 3.6 V.

Figure 2. GSM Application Circuit Configuration with Drain Switch and MC33169 GaAs Power Amplifier Support IC

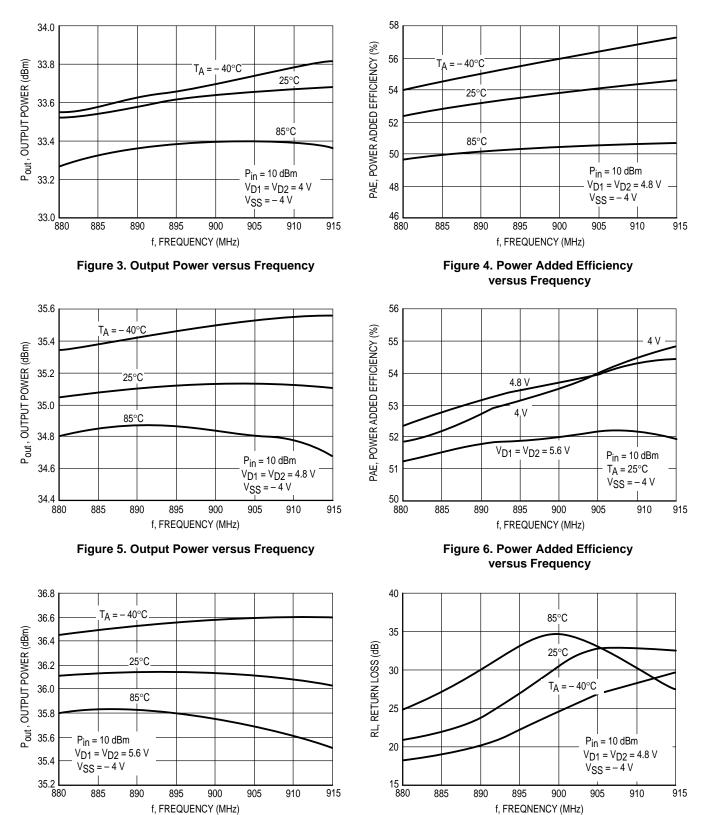

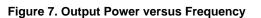

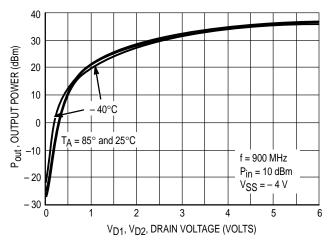

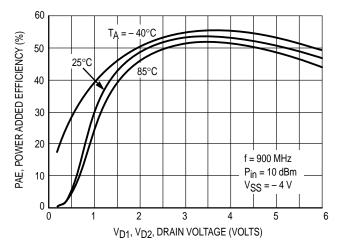

### **TYPICAL CHARACTERISTICS**

## **TYPICAL CHARACTERISTICS**

Figure 9. Output Power versus Drain Voltage

Figure 10. Power Added Efficiency versus Drain Voltage

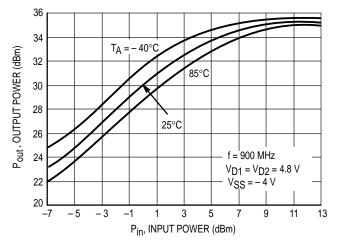

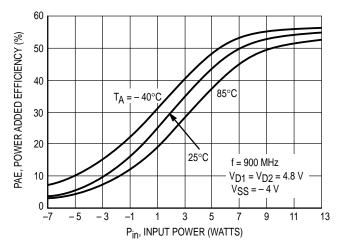

Figure 11. Output Power versus Input Power

Figure 12. Power Added Efficiency versus Input Power

| f     | Z <sub>in</sub><br>Ohms |        | Z <sub>OL</sub> *<br>Ohms |      |

|-------|-------------------------|--------|---------------------------|------|

| (MHz) | R                       | jХ     | R                         | jХ   |

| 880   | 13.65                   | -44.05 | 3.15                      | 5.06 |

| 885   | 13.64                   | -44.74 | 3.13                      | 4.97 |

| 890   | 13.65                   | -45.44 | 3.10                      | 4.89 |

| 895   | 13.64                   | -46.14 | 3.08                      | 4.80 |

| 900   | 13.64                   | -46.84 | 3.06                      | 4.71 |

| 905   | 13.65                   | -47.55 | 3.04                      | 4.63 |

| 910   | 13.66                   | -48.27 | 3.02                      | 4.54 |

| 915   | 13.66                   | -49.00 | 3.00                      | 4.45 |

Table 1. Device Impedances Derived from Circuit Characterization

#### **Design Philosophy**

The MRFIC0913 is a two-stage Integrated Power Amplifier designed for use in cellular phones, especially for those used in GSM Class IV, 4.8 V operation. With matching circuit modifications, it is also applicable for use in GSM Class IV 6 V and Class V 3.6 V equipment. Due to the fact that the input, output and some of the interstage matching is accomplished off chip, the device can be tuned to operate anywhere within the 800 to 1000 MHz frequency range. Typical performance at different battery voltages is:

- 36.0 dBm @ 5.8 V

- 35.0 dBm @ 4.8 V

- 31.5 dBm @ 3.6 V

This capability makes the MRFIC0913 suitable for portable cellular applications such as:

- 6 and 4.8 V GSM Class IV

- 3.6 V GSM Class V

- 3.6 V, 1.2 W Analog Cellular

#### **RF Circuit Considerations**

The MRFIC0913 can be tuned by changing the values and/ or positions of the appropriate external components. Refer to Figure 2, a typical GSM Class IV applications circuit.

The input match is a shunt–C, series–L, low–pass structure and can be retuned as desired with the only limitation being the on–chip 12 pF blocking capacitor. For saturated applications such as GSM and analog cellular, the input match should be optimized at the rated RF input power.

Interstage matching can be optimized by changing the value and/or position of the decoupling capacitor on the V<sub>D1</sub> supply line. Moving the capacitor closer to the device or reducing the value increases the frequency of resonance with the inductance of the device's wirebonds and leadframe pin.

Output matching is accomplished with a one-stage lowpass network as a compromise between bandwidth and harmonic rejection. Implementation is through chip capacitors mounted along a 30 or  $50\Omega$  microstrip transmission line. Values and positions are chosen to present a 3 $\Omega$  loadline to the device while conjugating the device output parasitics. The network must also properly terminate the second and third harmonics to optimize efficiency and reduce harmonic output. When low-Q commercial chip capacitors are used for the shunt capacitors, loss can be reduced by mounting two capacitors in parallel, as shown in Figure 2, to achieve the total value needed.

Loss in circuit traces must also be considered. The output transmission line and the bias supply lines should be at least 0.6 mm in width to accommodate the peak circulating currents which can be as high as 2 amperes. The bias supply line which supplies the output should include an RF choke of at least 8 nH, surface mount solenoid inductors or equivalent length of microstrip lines. Discrete inductors will usually give better efficiency and conserve board space.

The DC blocking capacitor required at the output of the device is best mounted at the  $50\Omega$  impedance point in the circuit where the RF current is at a minimum and the capacitor loss will have less effect.

#### **Biasing Considerations**

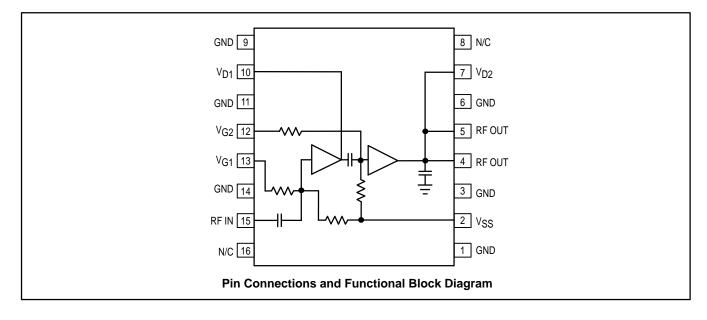

Gate bias is supplied to each stage separately through resistive division of the VSS voltage. The top of each divider is brought out through pins 12 and 13 (VG2 and VG1 respectively) allowing

gate biasing through use of external resistors or positive voltages. This allows setting the quiescent current of each stage separately.

For applications where the amplifier is operated close to saturation, such as GSM and analog cellular, the gate bias can be set with resistors. Variations in process and temperature will not affect amplifier performance significantly in these applications. The values shown in the Figure 1 will set quiescent currents of 80 to 160 mA for the first stage and 400 to 800 mA for the second stage.

For linear modes of operation which are required for PDC, DAMPS and CDMA, the quiescent current must be more carefully controlled. For these applications, the V<sub>G</sub> pins can be referenced to some tunable voltage which is set at the time of radio manufacturing. Less than 1.25 mA is required in the divider network so a DAC can be used as the voltage source. Typical settings for 6 V linear operation are 100 mA ±5% for the first stage, and 500 mA ±5% for the second stage.

#### Power Control Using the MC33169

The MC33169 is a dedicated GaAs power amplifier support IC which provides the -4 V required for V<sub>SS</sub>, an N–MOS drain switch interface and driver and power supply sequencing. The MC33169 can be used for power control in applications where the amplifier is operated in saturation since the output power in non–linear operation is proportional to V<sub>D</sub><sup>2</sup>. This provides a very linear and repeatable power control transfer function. This technique can be used open–loop to achieve 20–25 dB dynamic range over process and temperature variation. With careful design and selection of calibration points, this technique can be used for GSM phase II control where 29 dB dynamic range is required, eliminating the need for the complexity and cost of closed–loop control.

The transmit waveform ramping function required for systems such as GSM can be implemented with a simple Sallen and Key filter on the MC33169 control loop. The amplifier is then ramped on as the V<sub>RAMP</sub> pin is taken from 0 V to 3 V. To implement the different power steps required for GSM, the V<sub>RAMP</sub> pin is ramped between 0 V and the appropriate voltage between 0 V and 3 V for the desired output power.

For closed–loop configurations using the MC33169, MMSF4N01HD N–MOS switch and the MRFIC0913 provide a typical 1 MHz 3 dB loop bandwidth. The STANDBY pin must be enabled (3 V) at least 300  $\mu$ s before the V<sub>RAMP</sub> pin goes high and disabled (0 V) at least 20  $\mu$ s before the V<sub>RAMP</sub> pin goes low. This STANDBY function allows for the enabling of the MC33169 one burst before the active burst thus reducing power consumption.

#### Conclusion

The MRFIC0913 offers the flexibility in matching circuitry and gate biasing required for portable cellular applications. Together with the MC33169 support IC, the device offers an efficient system solution for TDMA applications such as GSM where saturated amplifier operation is used.

#### **Evaluation Boards**

Evaluation boards are available for RF Monolithic Integrated Circuits by adding a "TF" suffix to the device type. For a complete list of currently available boards and ones in development for newly introduced product, please contact your local Motorola Distributor or Sales Office.

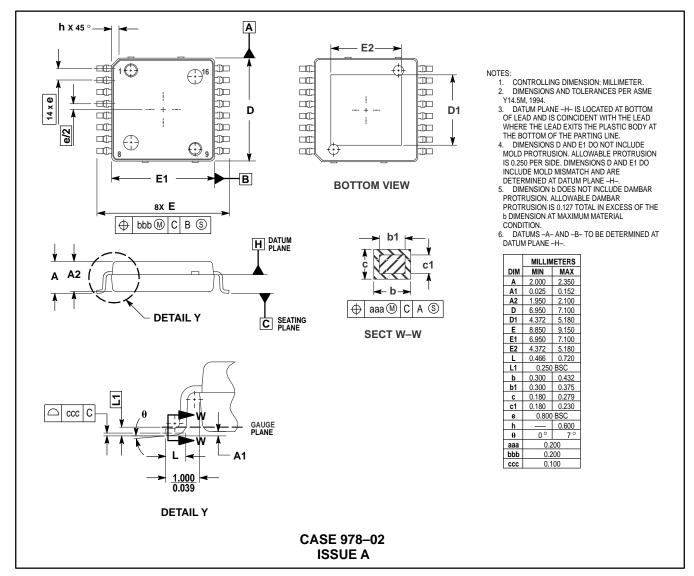

### PACKAGE DIMENSIONS

Motorola reserves the right to make changes without further notice to any products herein. Motorola makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Motorola assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters which may be provided in Motorola data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. Motorola does not convey any license under its patent rights nor the rights of others. Motorola products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Motorola product could create a situation where personal injury or death may occur. Should Buyer purchase or use Motorola products for any such unintended or unauthorized application, Buyer shall indemnify and hold Motorola and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Motorola was negligent regarding the design or manufacture of the part. Motorola and **(a)** are registered trademarks of Motorola, Inc. is an Equal Opportunity/Affirmative Action Employee.

#### How to reach us:

USA/EUROPE/Locations Not Listed: Motorola Literature Distribution; P.O. Box 5405, Denver, Colorado 80217. 303–675–2140 or 1–800–441–2447

$\Diamond$

JAPAN: Nippon Motorola Ltd.; Tatsumi–SPD–JLDC, 6F Seibu–Butsuryu–Center, 3–14–2 Tatsumi Koto–Ku, Tokyo 135, Japan. 81–3–3521–8315

Mfax is a trademark of Motorola, Inc.

Mfax™: RMFAX0@email.sps.mot.com – TOUCHTONE 602–244–6609 INTERNET: http://Design–NET.com ASIA/PACIFIC: Motorola Semiconductors H.K. Ltd.; 8B Tai Ping Industrial Park, 51 Ting Kok Road, Tai Po, N.T., Hong Kong. 852–26629298