**OKI** Semiconductor

# MSM6222B-xx

# DOT MATRIX LCD CONTROLLER WITH 16-DOT COMMON DRIVER AND 40-DOT SEGMENT DRIVER

## **GENERAL DESCRIPTION**

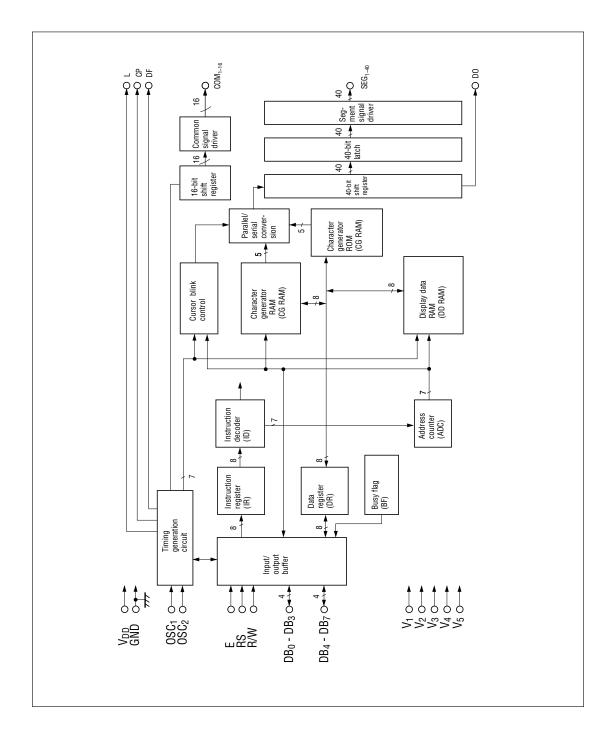

The MSM6222B-xx is a dot matrix LCD controller which is fabricated in low power CMOS silicon gate technology. Character display on the dot matrix character type LCD can be controlled in combination with a 4-bit/8-bit microcontroller. This LSI consists of 16-dot COMMON driver, 40-dot SEGMENT driver, display data RAM, character generator RAM, character generator ROM and control circuit.

The MSM6222B-xx is the equivalent of Hitachi's HD44780. There is, however, a slight difference between the two devices as described in the table on the last page.

The MSM6222B-xx has the character generator ROM that can be programmed by custom mask. MSM6222B-01 is a standard version having 160 characters with lowercase (5 x 7 dots), and 32 characters with uppercase (5 x 10 dots) in this ROM.

# FEATURES

- Easy interface with an 8-bit or 4-bit microcontroller.

- Dot matrix LCD controller/driver for lowercase (5 x 7 dots) or uppercase (5 x 10 dots).

- Automatic power ON reset.

- COMMON signal drivers (16) and SEGMENT signal drivers (40).

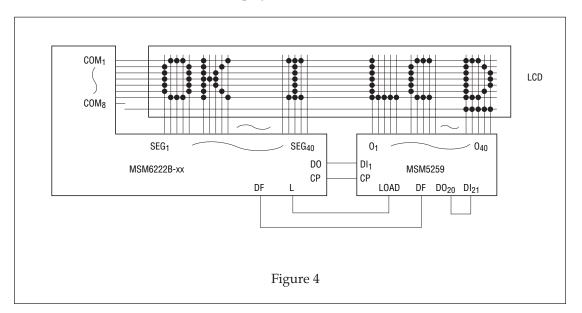

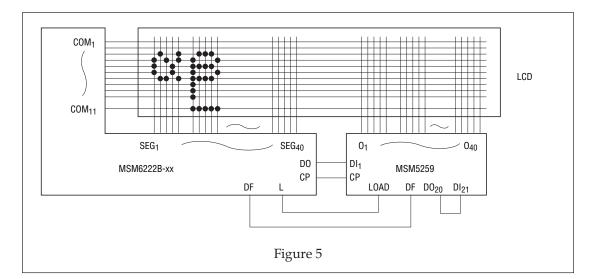

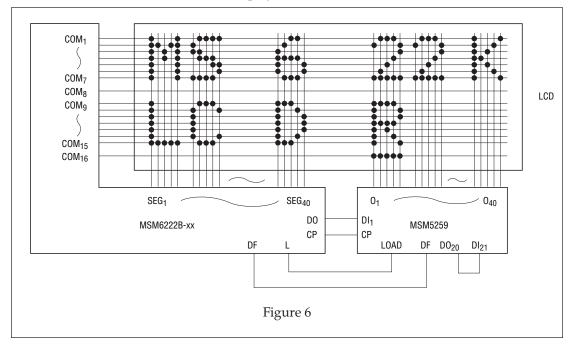

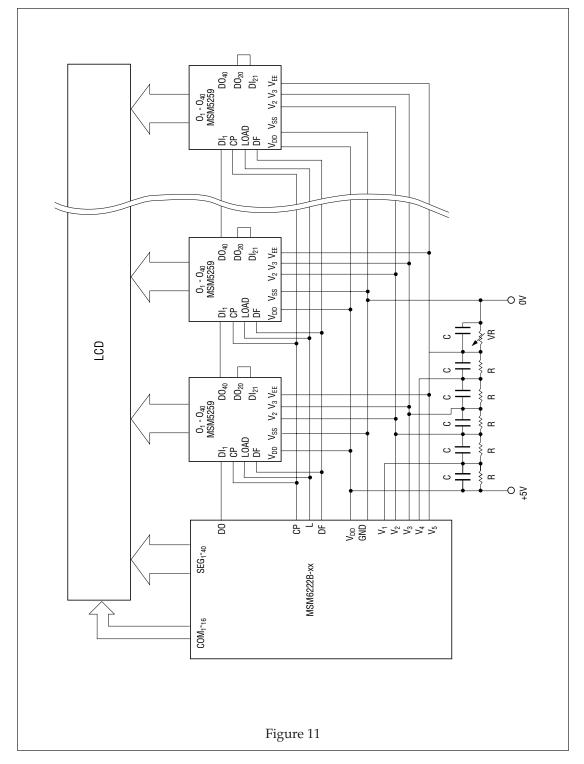

- Can control up to 80 characters when used in combination with MSM5259.

- Character generator ROM for 160 characters with lowercase (5 x 7 dots) and 32 characters with uppercase (5 x 10 dots).

- Character patterns are programmable by character generator RAM. (Lowercase: 5 x 8 dots, 8 kinds, uppercase: 5 x 11 dots, 4 kinds).

- Oscillation circuit for external resistor or ceralock.

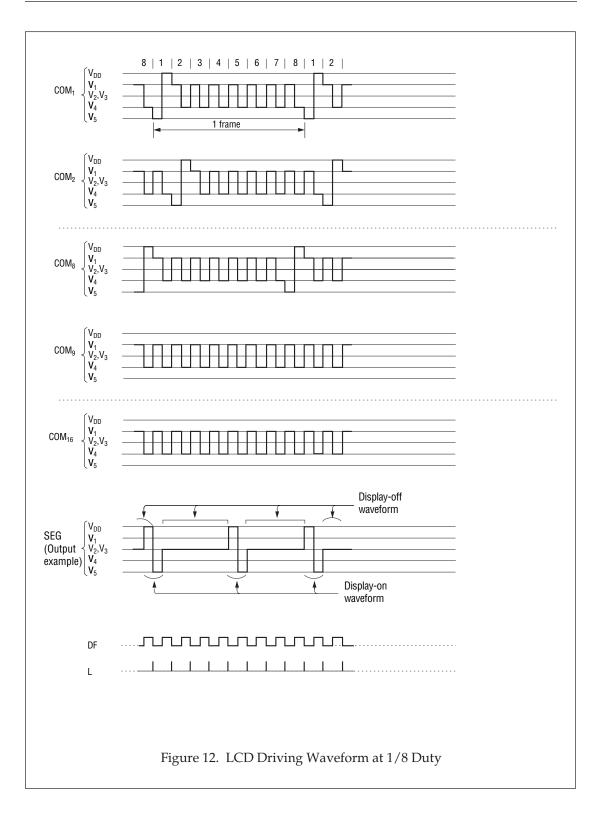

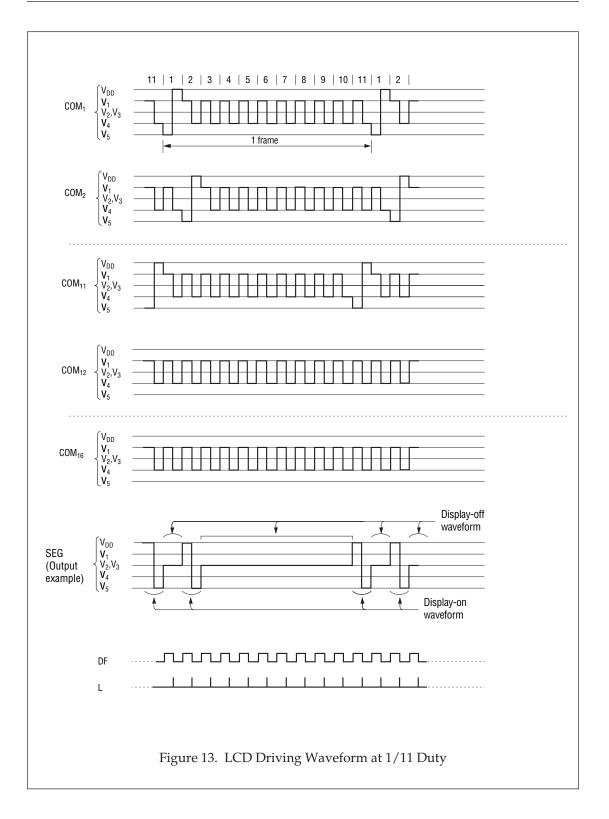

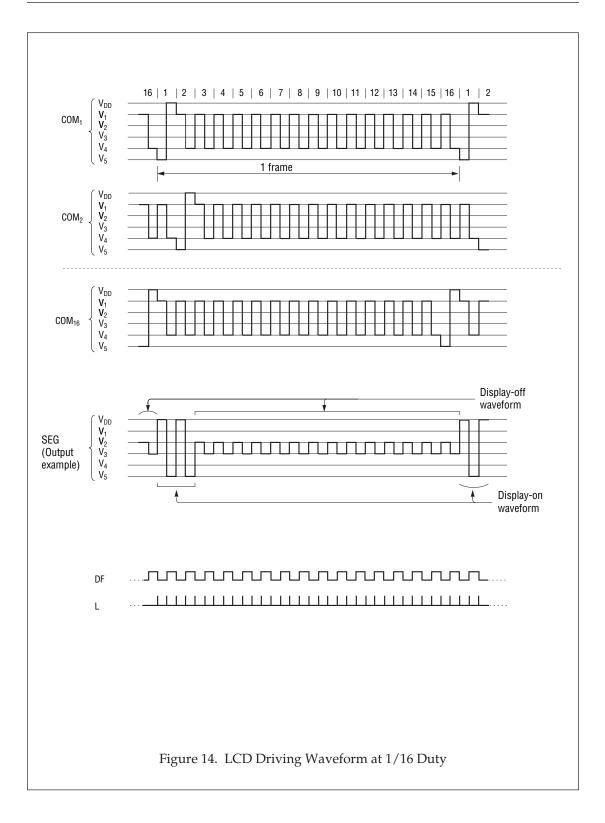

- 1/8 duty (1 line; 5 x 7 dots + cursor), 1/11 duty (1 line; 5 x 10 dots + cursor), or 1/16 duty (2 lines; 5 x 7 dots + cursor), selectable.

- Clear display even at 1/5 bias, 3.0V LCD driving voltage.

- Package options:

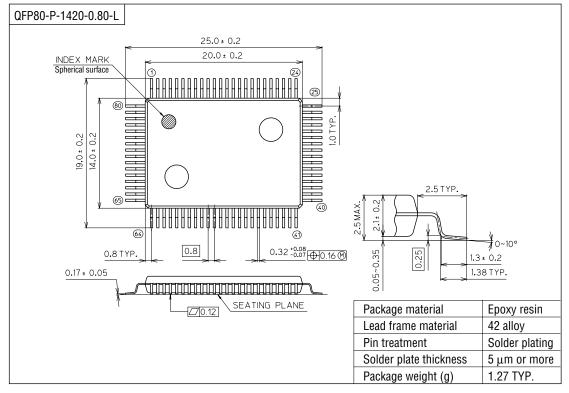

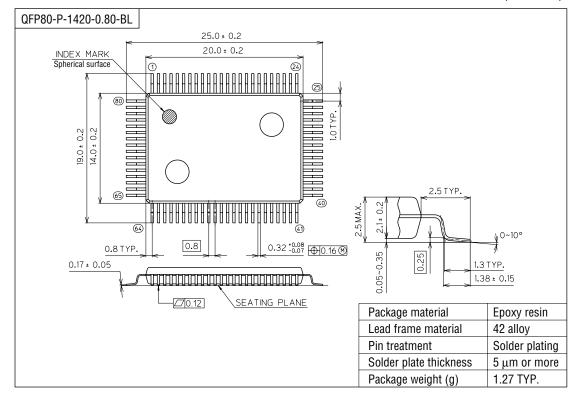

80-pin plastic QFP (QFP80-P-1420-0.80-L) (Product name: MSM6222B-xxGS-L) 80-pin plastic QFP (QFP80-P-1420-0.80-BL) (Product name: MSM6222B-xxGS-BL)

xx indicates code number.

# **BLOCK DIAGRAM**

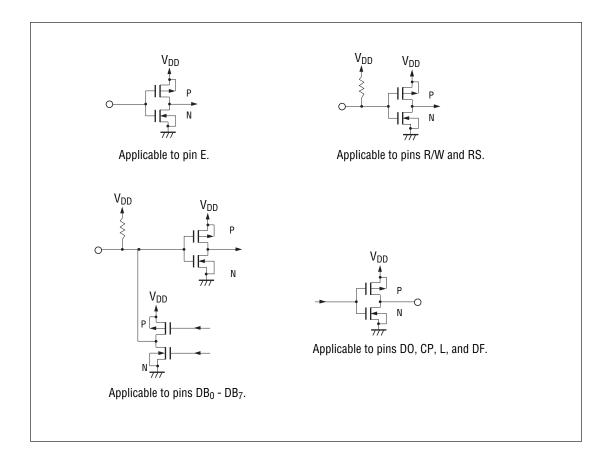

# INPUT AND OUTPUT CONFIGURATION

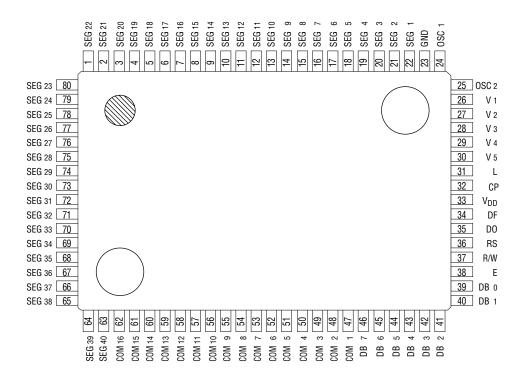

## PIN CONFIGURATION

**80-Pin Plastic QFP**

Note: The figure for Type L shows the configuration viewed from the reverse side of the package. Pay attention to the difference in pin arrangement.

# **PIN DESCRIPTIONS**

| Symbol                                                                             | Description                                                                                                      |

|------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|

| R/W                                                                                | Read/write selection input pin.<br>"H" : Read, and "L" : Write                                                   |

| RS                                                                                 | Register selection input pin.<br>"H" : Data register, and "L" : Instruction register                             |

| E                                                                                  | Input pin for data input/output between CPU and MSM6222B-xx and for instruction register activation.             |

| DB <sub>0</sub> - DB <sub>7</sub>                                                  | Input/output pins for data send/receive between CPU and MSM6222B-xx.                                             |

| OSC <sub>1</sub> , OSC <sub>2</sub>                                                | Clock oscillating pins required for internal operation upon receipt of the LCD drive signal and CPU instruction. |

| COM <sub>1</sub> - COM <sub>16</sub>                                               | LCD COMMON signal output pins.                                                                                   |

| SEG1 - SEG40                                                                       | LCD SEGMENT signal output pins.                                                                                  |

| DO                                                                                 | Output pin to be connected to MSM5259 to expand the number of characters to be displayed.                        |

| СР                                                                                 | Clock output pin used when DO pin data output shifts inside of MSM5259.                                          |

| L                                                                                  | Clock output pin for the serially transferred data to be latched to MSM5259.                                     |

| DF                                                                                 | The alternating current signal (Display Frequency) output pin.                                                   |

| V <sub>DD</sub>                                                                    | Power supply pin.                                                                                                |

| GND                                                                                | Ground pin.                                                                                                      |

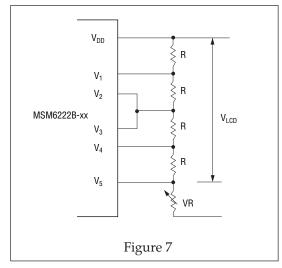

| V <sub>1</sub> , V <sub>2</sub> , V <sub>3</sub> , V <sub>4</sub> , V <sub>5</sub> | Bias voltage input pins to drive the LCD.                                                                        |

| ABSOLUTE MAXIMUM | RATINGS | 6 |

|------------------|---------|---|

|                  |         |   |

| Parameter           | Symbol                                           | Condition | Rating                        | Unit | Applicable pin                                   |

|---------------------|--------------------------------------------------|-----------|-------------------------------|------|--------------------------------------------------|

| Supply Voltage      | V <sub>DD</sub>                                  | Ta = 25°C | -0.3 to + 7.0                 | V    | V <sub>DD</sub> , GND                            |

| LCD Driving Voltage | V <sub>1</sub> , V <sub>2</sub> , V <sub>3</sub> | Ta = 25°C | V <sub>DD</sub> – 9.0 to      | V    | V <sub>1</sub> , V <sub>2</sub> , V <sub>3</sub> |

| LCD Driving Voltage | V4, V5                                           | 1a = 200  | V <sub>DD</sub> + 0.3         | v    | V4, V5                                           |

|                     |                                                  |           |                               |      | R/W, RS, E,                                      |

| Input Voltage       | VI                                               | Ta = 25°C | -0.3 to V <sub>DD</sub> + 0.3 | V    | DB <sub>0</sub> - DB <sub>7</sub>                |

|                     |                                                  |           |                               |      | OSC1                                             |

| Power Dissipation   | PD                                               |           | 500                           | mW   |                                                  |

| Storage Temperature | T <sub>STG</sub>                                 |           | -55 to + 150                  | °C   |                                                  |

## **RECOMMENDED OPERATING CONDITIONS**

| Parameter             | Symbol              | Condition                                               | Range       | Unit | Applicable pin                   |

|-----------------------|---------------------|---------------------------------------------------------|-------------|------|----------------------------------|

| Supply Voltage        | V <sub>DD</sub>     | _                                                       | 4.5 to 5.5  | V    | V <sub>DD</sub> , GND            |

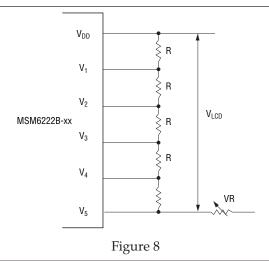

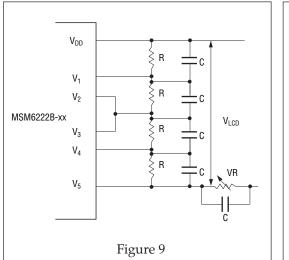

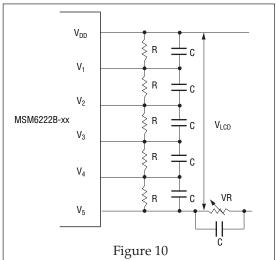

| LCD Driving Voltage   | V <sub>LCD</sub> *1 | $1/4$ bias, $V_{DD} - V_5^{*2}$                         | 3.0 to 8.0  | V    | V V                              |

| LCD Driving Voltage   | VLCD .              | 1/5 bias, V <sub>DD</sub> –V <sub>5</sub> <sup>*3</sup> | 3.0 to 8.0  | V    | V <sub>DD</sub> , V <sub>5</sub> |

| Operating Temperature | T <sub>op</sub>     |                                                         | -20 to + 75 | °C   | —                                |

\*1 Voltage between  $V_{DD}$  and  $V_{5.}$

- \*2 Voltages applicable to  $V_1$ ,  $V_2$ ,  $V_3$  and  $V_4$  are as follows.  $V_1 = V_{DD} - 1/4 (V_{DD} - V_5)$   $V_2 = V_3 = V_{DD} - 1/2 (V_{DD} - V_5)$   $V_4 = V_{DD} - 3/4 (V_{DD} - V_5)$ \*3 Voltages applicable to  $V_1$ ,  $V_2$ ,  $V_3$  and  $V_4$  are as follows.

- $V_1 = V_{DD} 1/5 (V_{DD} V_5)$  $V_2 = V_{DD} 2/5 (V_{DD} V_5)$

- $V_3 = V_{DD} 3/5 (V_{DD} V_5)$  $V_4 = V_{DD} - 4/5 (V_{DD} - V_5)$

|                       |                  |                                    |                    | (V   | <sub>DD</sub> = 4.5 to | o 5.5V, <sup>−</sup> | Га = –20 to +75°С)                   |

|-----------------------|------------------|------------------------------------|--------------------|------|------------------------|----------------------|--------------------------------------|

| Parameter             | Symbol           | Condition                          | Min.               | Тур. | Max.                   | Unit                 | Applicable pin                       |

| "H" Input Voltage     | V <sub>IH1</sub> | —                                  | 2.2                |      | V <sub>DD</sub>        | V                    | R/W, RS, E,                          |

| "L" Input Voltage     | V <sub>IL1</sub> | —                                  | -0.3               |      | 0.6                    | V                    | DB <sub>0</sub> - DB <sub>7</sub>    |

| "H" Input Voltage     | V <sub>IH2</sub> | —                                  | $V_{DD} - 1.0$     |      | V <sub>DD</sub>        | V                    | OSC1                                 |

| "L" Input Voltage     | V <sub>IL2</sub> | —                                  | -0.3               |      | 1.0                    | V                    | 0301                                 |

| "H" Output Voltage    | V <sub>0H1</sub> | I <sub>0</sub> = -0.205mA          | 2.4                |      |                        | V                    |                                      |

| "L" Output Voltage    | V <sub>0L1</sub> | l <sub>0</sub> = 1.2mA             | _                  |      | 0.4                    | V                    | DB <sub>0</sub> - DB <sub>7</sub>    |

| "H" Output Voltage    | V <sub>0H2</sub> | $I_0 = -40 \mu A$                  | 0.9V <sub>DD</sub> |      |                        | V                    | D0, CP, L,                           |

| "L" Output Voltage    | V <sub>0L2</sub> | $I_0 = 40 \mu A$                   | —                  |      | $0.1V_{DD}$            | V                    | DC, OSC <sub>2</sub>                 |

| COM Voltage Drop      | V <sub>C</sub>   | l <sub>0</sub> = ±50μA *1          | —                  | —    | 2.9                    | V                    | COM <sub>1</sub> - COM <sub>16</sub> |

| SEG Voltage Drop      | Vs               | l <sub>0</sub> = ±50μA *1          |                    |      | 3.8                    | V                    | SEG <sub>1</sub> - SEG <sub>40</sub> |

| Innut Lookogo Current | 1                | $V_I = V_{SS}$                     | —                  | —    | -1                     | μA                   | E                                    |

| Input Leakage Current | Ι <sub>Ι</sub>   | $V_I = V_{DD}$                     | _                  |      | 1                      | μA                   | E                                    |

|                       |                  | V <sub>DD</sub> = 5.0V             | -50                | 105  | 250                    | ۸                    |                                      |

| Input Current         |                  | $V_I = V_{SS}$                     | -50                | -125 | -250                   | μA                   |                                      |

|                       | I <sub>IL2</sub> | $V_I = V_{DD}$ , excluding current |                    |      | 2                      |                      | R/W, RS                              |

|                       |                  | flowing over pullup resistor       |                    |      |                        | μA                   | DB <sub>0</sub> - DB <sub>7</sub>    |

|                       |                  | and output drive MOS               |                    |      |                        |                      |                                      |

## ELECTRICAL CHARACTERISTICS DC Characteristics

\*1 Applicable to the voltage drop (V<sub>C</sub>) occurring in pins V<sub>DD</sub>, V<sub>1</sub>, V<sub>4</sub>, and V<sub>5</sub> to each COMMON pin (COM1 to COM16) when 50  $\mu$ A flows in or out of all COM and SEG pins. Also applicable to voltage drop (V<sub>S</sub>) occurring in pins V<sub>DD</sub>, V<sub>2</sub>, V<sub>3</sub>, and V<sub>5</sub> to each SEG pin (SEG1 to SEG40). When output level is at V<sub>DD</sub>, V<sub>1</sub> or V<sub>2</sub> level, 50  $\mu$ A flows out, while 50  $\mu$ A flows in when the output level is at V<sub>3</sub>, V<sub>4</sub> or V<sub>5</sub> level.

This occurs when +5V is input to  $V_{DD}$ ,  $V_1$ , and  $V_2$ , and when -3V is input to  $V_3$ ,  $V_4$ , and  $V_5$ .

|                    |                   |                                                                                                                                                                                               |          |      |      | (V <sub>DD</sub> = 4.5 to 5.5V, Ta = −20 to +75°C |      |                                                     |  |

|--------------------|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|------|------|---------------------------------------------------|------|-----------------------------------------------------|--|

| Parameter          | Symbol            | Conditio                                                                                                                                                                                      | n        | Min. | Тур. | Max.                                              | Unit | Applicable pin                                      |  |

| Supply Current (1) | I <sub>DD1</sub>  | $V_{DD}$ = 5.0V,<br>resistor oscillatio<br>external clock in<br>OSC <sub>1</sub> .<br>f <sub>OSC</sub> = 270kHz.<br>E is in "L" level.<br>Other inputs are<br>Output pins are<br>all no load. | put via  |      | 0.35 | 0.6                                               | mA   | V <sub>DD</sub>                                     |  |

| Supply Current (2) | I <sub>DD2</sub>  | $V_{DD} = 5.0V,$ ceramic oscillation,<br>$f_{OSC} = 250kHz.$ E is in "L" level.<br>Other pins are open.<br>Output pins are<br>all no load. *2                                                 |          | _    | 0.55 | 0.8                                               | mA   | V <sub>DD</sub>                                     |  |

| LCD Driving Bias   | V <sub>LCD1</sub> | VI VI *7                                                                                                                                                                                      | 1/5 bias | 3.0  | _    | 8.0                                               | v    | V <sub>DD</sub> , V <sub>1</sub> , V <sub>2</sub> , |  |

| Input Voltage      | V <sub>LCD2</sub> | V <sub>DD</sub> –V <sub>5</sub> *7                                                                                                                                                            | 1/4 bias | 3.0  | _    | 8.0                                               | V    | V <sub>3</sub> , V <sub>4</sub> , V <sub>5</sub>    |  |

\*2 Applicable to the current that flows in pin V<sub>DD</sub> when power is input as follows:  $V_{DD} = 5V$ , GND = 0V,  $V_1 = 3.4V$ ,  $V_2 = 1.8V$ ,  $V_3 = 0.2V$ ,  $V_4 = -1.4V$ , and  $V_5 = -3V$ .

## **AC Characteristics**

$(V_{DD} = 4.5 \text{ to } 5.5 \text{V}, \text{ Ta} = -20 \text{ to } +75^{\circ}\text{C})$

|                                  |                   |                               |    |      |      |      | , , , |                  |

|----------------------------------|-------------------|-------------------------------|----|------|------|------|-------|------------------|

| Parameter                        | Symbol            | Condition                     |    | Min. | Тур. | Max. | Unit  | Applicable pin   |

| R <sub>f</sub> Clock Oscillation | f <sub>OSC1</sub> | $R_f = 91k\Omega \pm 2\%$     |    | 175  | 250  | 350  | kHz   | OSC <sub>1</sub> |

| Frequency                        | 10501             |                               | *3 | 175  | 200  | 000  | KI IZ | OSC <sub>2</sub> |

| Clock Input                      | <b>f</b>          | OSC <sub>2</sub> is open.     |    | 125  | 250  | 350  | kHz   | 080.             |

| Frequency                        | f <sub>IN</sub>   | Input from OSC1               |    | 120  | 200  | 300  | КПД   | OSC1             |

| Input Clock Duty                 | f <sub>DUTY</sub> |                               | *4 | 45   | 50   | 55   | %     | OSC1             |

|                                  |                   |                               |    |      |      |      |       |                  |

| Input Clock Rise                 | t <sub>r</sub>    |                               | *5 | _    | _    | 0.2  | μs    | OSC1             |

| Time                             |                   |                               | •  |      |      |      |       |                  |

| Input Clock Fall                 | t <sub>f</sub>    |                               | *5 |      |      | 0.2  | μs    | OSC1             |

| Time                             | ч                 |                               | 5  |      |      | 0.2  | μο    | 0001             |

|                                  |                   | $R_f = 510k\Omega$ ,          |    |      |      |      |       |                  |

| Ceramic Filter                   |                   | $C_1 = C_2 = 200 \text{ pF},$ |    |      |      |      |       | OSC1             |

| Oscillation                      | f <sub>OSC</sub>  | $R_d = 30k\Omega$ , and       |    | 245  | 250  | 255  | kHz   | 0301<br>0SC2     |

| Frequency                        |                   | Ceralock CSB250A.             |    |      |      |      |       | 0302             |

|                                  |                   |                               | *6 |      |      |      |       |                  |

\*3 OSC<sub>1</sub> Rf  $R_f = 91 k \Omega \pm 2\%$ OSC<sub>2</sub> Minimum wiring is required between OSC1 and Rf and between OSC2 and Rf. \*4 Applied to pulse input via OSC<sub>1</sub>. t<sub>HW</sub> t<sub>LW</sub>  $0.5V_{DD}$ 0.5V<sub>DD</sub>  $0.5V_{DD}$ f<sub>IN</sub> waveform  $f_{DUTY} = t_{HW} / (t_{HW} + t_{LW}) \times 100(\%)$ \*5 Applied to pulse input via OSC<sub>1</sub>. V<sub>DD</sub>-1.0V 1.0V<sub>DD</sub> f<sub>IN</sub> waveform 1.0V  $1.0V_{DD}$ è tr Ťf C1 \*6 OSC<sub>1</sub> Ceralock R<sub>f</sub> OSC<sub>2</sub>  $\mathsf{R}_\mathsf{d}$ C2 7 Ceralock : CSB250A (mfd. by MURATA MFG.Co.)  $R_f$ : 510k $\Omega$  ±5%  $R_d$ : 30k $\Omega$  ±5% C1: 200pF ±10% C2: 200pF ±10% Please contact us when using this circuit.

\*7 Input the voltage listed in the table below to  $V_1$  -  $V_5$ :

| N (LCD lines)<br>Pin | 1-line mode                        | 2-line mode                        |

|----------------------|------------------------------------|------------------------------------|

| V <sub>1</sub>       | $V_{DD} - \frac{V_{LCD}}{4}$       | $V_{DD} - \frac{V_{LCD}}{5}$       |

| V2                   | $V_{DD} - \frac{V_{LCD}}{2}$       | $V_{DD} - \frac{2V_{LCD}}{5}$      |

| V <sub>3</sub>       | $V_{DD} - \frac{V_{LCD}}{2}$       | $V_{DD} - \frac{3V_{LCD}}{5}$      |

| V4                   | $V_{DD} - \frac{3V_{LCD}}{4}$      | $V_{DD} - \frac{4V_{LCD}}{5}$      |

| V <sub>5</sub>       | V <sub>DD</sub> – V <sub>LCD</sub> | V <sub>DD</sub> – V <sub>LCD</sub> |

$V_{LCD}$  is an LCD driving voltage. (For "N" (number of LCD lines), refer to the initial set of the instruction code.)

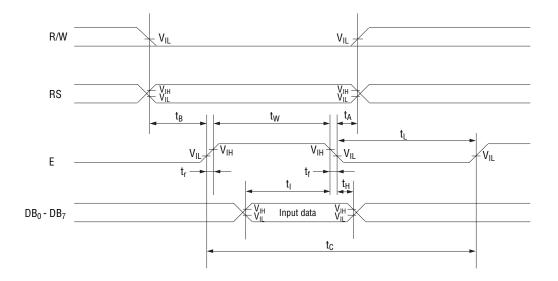

# **Switching Characteristics**

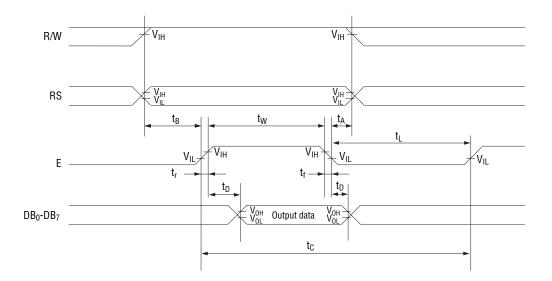

• Timing for input from the CPU

| Timing for input none the Cr O           |                | $(V_{DD} = 4.5 \text{ to } 5.5 \text{V}, \text{ Ta} = -20 \text{ to } +75^\circ$ |      |      |      |  |

|------------------------------------------|----------------|----------------------------------------------------------------------------------|------|------|------|--|

| Parameter                                | Symbol         | Min.                                                                             | Тур. | Max. | Unit |  |

| R/W and RS set-up time                   | t <sub>B</sub> | 140                                                                              | —    | —    | ns   |  |

| E "H" pulse width                        | tw             | 280                                                                              | _    |      | ns   |  |

| R/W and RS holding time                  | t <sub>A</sub> | 10                                                                               | —    |      | ns   |  |

| E rise time                              | t <sub>r</sub> |                                                                                  | —    | 25   | ns   |  |

| E fall time                              | t <sub>f</sub> |                                                                                  | —    | 25   | ns   |  |

| E "L" pulse width                        | tL             | 280                                                                              | —    |      | ns   |  |

| E cycle time                             | t <sub>C</sub> | 667                                                                              | —    |      | ns   |  |

| $DB_0$ to $DB_7$ input data set-up time  | tı             | 180                                                                              | _    | _    | ns   |  |

| $DB_0$ to $DB_7$ input data holding time | t <sub>H</sub> | 10                                                                               | _    |      | ns   |  |

# • Timing for output to the CPU

|                                           |                | (    | V <sub>DD</sub> = 4.5 to | 5.5V, Ta = - | -20 to +75°C) |

|-------------------------------------------|----------------|------|--------------------------|--------------|---------------|

| Parameter                                 | Symbol         | Min. | Тур.                     | Max.         | Unit          |

| R/W and RS set-up time                    | t <sub>B</sub> | 140  | —                        |              | ns            |

| E "H" pulse width                         | tw             | 280  | —                        |              | ns            |

| R/W and RS holding time                   | t <sub>A</sub> | 10   | —                        |              | ns            |

| E rise time                               | tr             | _    | —                        | 25           | ns            |

| E fall time                               | t <sub>f</sub> | _    | —                        | 25           | ns            |

| E "L" pulse width                         | tL             | 280  | —                        | —            | ns            |

| E cycle time                              | t <sub>C</sub> | 667  | —                        | _            | ns            |

| $DB_0$ to $DB_7$ data output delay time   | t <sub>D</sub> | _    |                          | 220          | ns            |

| $DB_0$ to $DB_7$ data output holding time | to             | 20   | _                        |              | ns            |

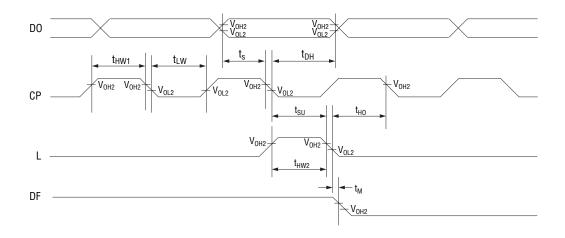

## • Timing for output to MSM5259

## $(V_{DD} = 4.5 \text{ to } 5.5 \text{V}, \text{ Ta} = -20 \text{ to } +75^{\circ}\text{C})$

|                  | ```                                                                                                                                | 100 110 10                                                                                                                                                                                                                             | ,                                                                                                                                                                                                                                                                    | ,                                                                                                                                                                                                                                                                            |

|------------------|------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Symbol           | Min.                                                                                                                               | Тур.                                                                                                                                                                                                                                   | Max.                                                                                                                                                                                                                                                                 | Unit                                                                                                                                                                                                                                                                         |

| t <sub>HW1</sub> | 800                                                                                                                                | —                                                                                                                                                                                                                                      | —                                                                                                                                                                                                                                                                    | ns                                                                                                                                                                                                                                                                           |

| t <sub>LW</sub>  | 800                                                                                                                                | _                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                      | ns                                                                                                                                                                                                                                                                           |

| ts               | 300                                                                                                                                | —                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                      | ns                                                                                                                                                                                                                                                                           |

| t <sub>DH</sub>  | 300                                                                                                                                | —                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                      | ns                                                                                                                                                                                                                                                                           |

| t <sub>SU</sub>  | 500                                                                                                                                | _                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                      | ns                                                                                                                                                                                                                                                                           |

| t <sub>HO</sub>  | 100                                                                                                                                | _                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                      | ns                                                                                                                                                                                                                                                                           |

| t <sub>HW2</sub> | 800                                                                                                                                | _                                                                                                                                                                                                                                      | —                                                                                                                                                                                                                                                                    | ns                                                                                                                                                                                                                                                                           |

| t <sub>M</sub>   | -1000                                                                                                                              | _                                                                                                                                                                                                                                      | 1000                                                                                                                                                                                                                                                                 | ns                                                                                                                                                                                                                                                                           |

|                  | t <sub>HW1</sub><br>t <sub>LW</sub><br>t <sub>S</sub><br>t <sub>DH</sub><br>t <sub>SU</sub><br>t <sub>HO</sub><br>t <sub>HW2</sub> | Symbol         Min.           t <sub>HW1</sub> 800           t <sub>LW</sub> 800           t <sub>S</sub> 300           t <sub>DH</sub> 300           t <sub>SU</sub> 500           t <sub>H0</sub> 100           t <sub>HW2</sub> 800 | $\begin{tabular}{ c c c c c c } \hline Symbol & Min. & Typ. \\ \hline t_{HW1} & 800 & \\ \hline t_{LW} & 800 & \\ \hline t_{S} & 300 & \\ \hline t_{DH} & 300 & \\ \hline t_{SU} & 500 & \\ \hline t_{HO} & 100 & \\ \hline t_{HW2} & 800 & \\ \hline \end{tabular}$ | Symbol         Min.         Typ.         Max.           t <sub>HW1</sub> 800             t <sub>LW</sub> 800             t <sub>S</sub> 300             t <sub>DH</sub> 300             t <sub>SU</sub> 500             t <sub>H0</sub> 100             t <sub>HW2</sub> 800 |

## FUNCTIONAL DESCRIPTION

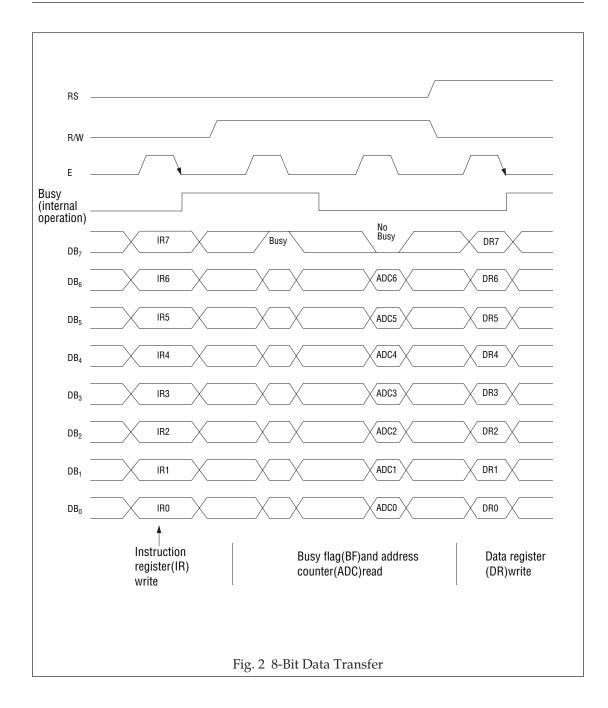

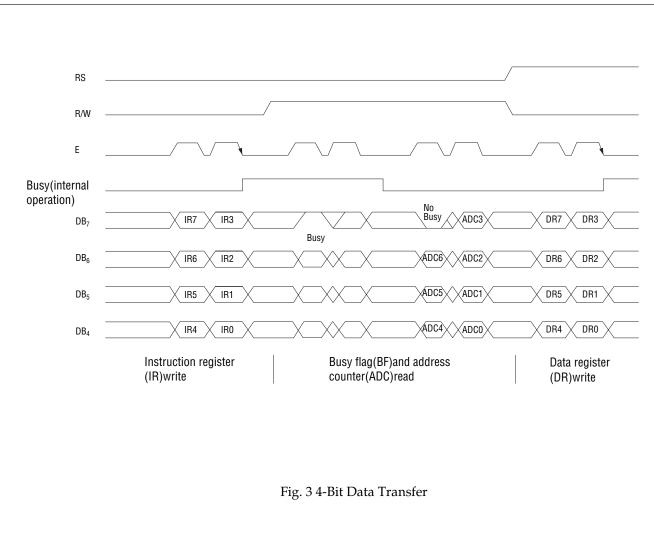

#### Instruction Register (IR) and Data Register (DR)

These two registers are selected by the REGISTER SELECTOR (RS) pin.

The DR is selected when the "H" level is input to the RS pin and IR is selected when the "L" level is input.

The IR is used to store the address of the display data RAM (DD RAM) or character generator RAM (CG RAM) and instruction code.

The IR can be written, but not be read by the microcomputer (CPU).

The DR is used to write and read the data to and from the DD RAM or CG RAM.

The data written to DR by the CPU is automatically written to the DD RAM or CG RAM as an internal operation.

When an address code is written to IR, the data (of the specified address) is automatically transferred from the DD RAM or CG RAM to the DR. Next, when the CPU reads the DR, it is possible to verify DD RAM or CG RAM data from the DR data.

After the writing of DR by the CPU, the next adress in the DD RAM or CG RAM is selected to be ready for the next CPU writing.

Likewise, after the reading out of DR by the CPU, DD RAM or CG RAM data is read out by the DR to be ready for the next CPU reading.

Write/read to and from both registers is carried out by the READ/WRITE (R/W) pin.

| R/W | RS | Function                                         |

|-----|----|--------------------------------------------------|

| L   | L  | IR write                                         |

| Н   | L  | Read of busy flag (BF) and address counter (ADC) |

| L   | Н  | DR write                                         |

| Н   | Н  | DR read                                          |

#### Table 1 RS and R/W pins functions

#### Busy Flag (BF)

When the busy flag is at "H", it indicates that the MSM6222B-xx is engaged in internal operation.

When the busy flag is at "H", any new instruction is ignored.

When R/W = "H" and RS = "L", the busy flag is output from  $DB_7$ .

New instruction should be input when busy flag is "L" level.

When the busy flag is at "H", the output code of the address counter (ADC) is undefined.

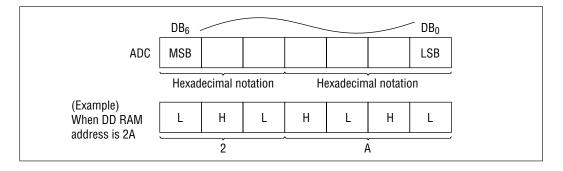

#### Address Counter (ADC)

The address counter (ADC) allocates the address for the DD RAM and CG RAM write/read and also for the cursor display.

When the instruction code for a DD RAM address or CG RAM address setting is input to IR, after deciding whether it is DD RAM or CG RAM, the address code is transferred from IR to ADC. After writing (reading) the display data to (from) the DD RAM or CG RAM, the ADC is incremented (decremented) by 1 internally.

The data of the ADC is output to  $DB_0 - DB_6$  on the conditions that R/W = "H", RS = "L", and BF = "L".

#### **Timing Generator Circuit**

This circuit is used to generate timing signals to activate internal operations upon receipt of CPU instruction and also from such internal circuits as the DD RAM, CG RAM, and CG ROM.

It is designed so that the internal operation caused by accessing from the CPU will not interfere with the internal operation caused by LCD driving. Consequently, when data is written from the CPU to DD RAM, flickering does not occur in a display area other than the display area where the data is written.

In addition, this circuit generates the transfer signal to MSM5259 for display character expansion.

#### Display Data RAM (DD RAM)

This RAM is used to store display data of 8-bit character codes (see Table 2).

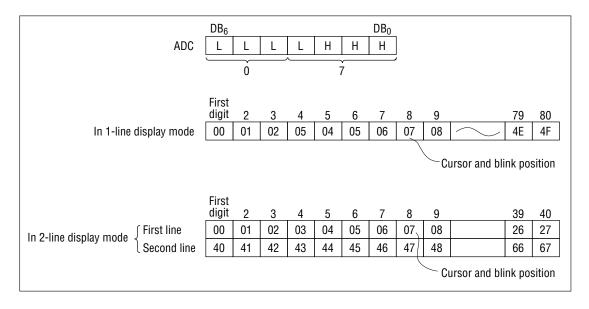

DD RAM address corresponds to the display position of the LCD. The correspondence between the two is described in the following.

DD RAM address (set to ADC) is expressed in hexadecimal notation as shown below:

(1) Correspondence between address and display position in the 1-line display mode

• When the MSM6222B-xx alone is used, up to 8 characters can be displayed from the first to eighth digit.

| First<br>digit | 2  | 3  | 4  | 5  | 6  | 7  | 8  |

|----------------|----|----|----|----|----|----|----|

| 00             | 01 | 02 | 03 | 04 | 05 | 06 | 07 |

When the display is shifted by instruction, the correspondence between the LCD display position and the DD RAM address changes as shown below:

| (Display             | First<br>digit | 2  | 3  | 4  | 5  | 6  | 7  | 8  |

|----------------------|----------------|----|----|----|----|----|----|----|

| shifted<br>to right) | 4F             | 00 | 01 | 02 | 03 | 04 | 05 | 06 |

| to right)            |                |    |    |    |    |    |    |    |

| (Display             | First<br>digit | 2  | 3  | 4  | 5  | 6  | 7  | 8  |

| shifted              | 01             | 02 | 03 | 04 | 05 | 06 | 07 | 08 |

| to left)             | ·              |    |    |    |    |    |    |    |

• When the MSM6222B-xx is used with one MSM5259, up to 16 characters can be displayed from the first to sixteenth digit as shown below:

| First<br>digit<br>00 | 2  | 3   | 4     | 5<br>04 | 6<br>05 | 7<br>06 | 8  | 9<br>08 | 10<br>09 | 11<br>0A | 12<br>0B | 13<br>0C | 14<br>0D | 15<br>0E | 16<br>0F |

|----------------------|----|-----|-------|---------|---------|---------|----|---------|----------|----------|----------|----------|----------|----------|----------|

| 00                   | 01 | MSM | 6222E |         |         | 00      | 07 |         | 03       | _        |          | 9 disp   | _        | UL       |          |

When the display is shifted by instruction, the correspondence between the LCD display and the DD RAM address changes as shown below:

| (Display shifted to right) | First<br>digit<br>4F | 2  | 3<br>01 | 4    | 5<br>03 | 6<br>04 | 7  | 8  | 9<br>07 | 10<br>08 | 11<br>09 | 12<br>0A | 13<br>0B | 14<br>0C | 15<br>0D | 16<br>0E |

|----------------------------|----------------------|----|---------|------|---------|---------|----|----|---------|----------|----------|----------|----------|----------|----------|----------|

| (Display shinted to right) |                      | 00 | 01      | 02   | - 00    | -04     | 00 | 00 | 07      |          |          |          |          |          | 00       |          |

|                            |                      | N  | ISM6    | 222E | 3-xx (  | displa  | ау |    | ~       |          | MSN      | A525     | 9 dis    | play     |          |          |

| (Display shifted to left)  | 01                   | 02 | 03      | 04   | 05      | 06      | 07 | 08 | 09      | 0A       | 0B       | 0C       | 0D       | 0E       | 0F       | 10       |

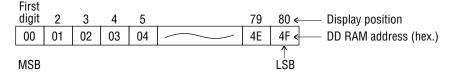

• Since the MSM6222B-xx has a DD RAM capacity of up to 80 characters, up to 9 MSM5259 devices can be connected to MSM6222B-xx so that 80 characters can be displayed.

First

| digit | 2  | 3   | 4    | 5    | 6    | 7   | 8  | 9  | 10 | 11  | 12  | 13  | 14    | 15 | 16 | 17 | 18 |         | 73       | 74 | 75  | 76  | 77  | 78    | 79 | 80 |

|-------|----|-----|------|------|------|-----|----|----|----|-----|-----|-----|-------|----|----|----|----|---------|----------|----|-----|-----|-----|-------|----|----|

| 00    | 01 | 02  | 03   | 04   | 05   | 06  | 07 | 08 | 09 | 0A  | 0B  | 0C  | 0D    | 0E | 0F | 10 | 11 | $\sim$  | 42       | 49 | 4A  | 4B  | 4C  | 4D    | 4E | 4F |

|       | MS | SM6 | 2228 | 3-xx | disp | lay |    | •  | M  | SM5 | 259 | (1) | displ | ay |    |    |    | 259 (2) | <b>`</b> | M  | SM5 | 259 | (9) | displ | ay |    |

- (8) display

(2) Correspondence between address and display position in the 2-line display mode

|             | First<br>digit | 2  | 3  | 4  | 5  | 39 40 - Display position      |

|-------------|----------------|----|----|----|----|-------------------------------|

| First line  | 00             | 01 | 02 | 03 | 04 | 26 27 < DD RAM address (hex.) |

| Second line | 40             | 41 | 42 | 43 | 44 | 66 67 <                       |

- (Note) The last address of the first line is not consecutive to the head address of the second line.

- When MSM6222B-xx alone is used, up to 16 characters (8 characters x 2 lines) can be displayed from the first to eighth digit.

|             | First<br>digit | 2  | 3  | 4  | 5  | 6  | 7  | 8  |

|-------------|----------------|----|----|----|----|----|----|----|

| First line  | 00             | 01 | 02 | 03 | 04 | 05 | 06 | 07 |

| Second line | 40             | 41 | 42 | 43 | 44 | 45 | 46 | 47 |

When the display is shifted by instruction, the correspondence between the LCD display position and the DD RAM address changes as shown below:

|                            |             | First<br>digit | 2  | 3  | 4  | 5  | 6  | 7  | 8  |

|----------------------------|-------------|----------------|----|----|----|----|----|----|----|

| (Diaplay abifted to right) | First line  | 27             | 00 | 01 | 02 | 03 | 04 | 05 | 06 |

| (Display shifted to right) | Second line | 67             | 40 | 41 | 42 | 43 | 44 | 45 | 46 |

|                            |             | First<br>digit | 2  | 3  | 4  | 5  | 6  | 7  | 8  |

| (Display shifted to left)  | First line  | 01             | 02 | 03 | 04 | 05 | 06 | 07 | 08 |

| (Display Silited to left)  | Second line | 41             | 42 | 43 | 44 | 45 | 46 | 47 | 48 |

• When the MSM6222B-xx is used with one MSM5259, up to 32 characters (16 characters x 2 lines) can be displayed from the first to the sixteenth digit.

|             | First<br>digit | 2  | 3  | 4  | 5  | 6  | 7  | 8  | 9  | 10 | 11 | 12 | 13 | 14 | 15 | 16 |

|-------------|----------------|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|

| First line  | 00             | 01 | 02 | 03 | 04 | 05 | 06 | 07 | 08 | 09 | 0A | 0B | 0C | 0D | 0E | 0F |

| Second line | 40             | 41 | 42 | 43 | 44 | 45 | 46 | 47 | 48 | 49 | 4A | 4B | 4C | 4D | 4E | 4F |

|             |                |    |    |    |    |    |    |    | •  |    |    |    |    |    |    | ,  |

MSM6222B-xx display

MSM5259 display

When the display is shifted by instruction, the correspondence between the LCD display position and the DD RAM address changes as shown below:

| (Display shift | ed to r        | ight) |     |       |         |        |       |         |        |       |    |       |        |       |       |    |

|----------------|----------------|-------|-----|-------|---------|--------|-------|---------|--------|-------|----|-------|--------|-------|-------|----|

|                | First<br>digit | 2     | 3   | 4     | 5       | 6      | 7     | 8       | 9      | 10    | 11 | 12    | 13     | 14    | 15    | 16 |

| First line     | 27             | 00    | 01  | 02    | 03      | 04     | 05    | 06      | 07     | 08    | 09 | 0A    | 0B     | 0C    | 0D    | 0E |

| Second line    | 67             | 40    | 41  | 42    | 43      | 44     | 45    | 46      | 47     | 48    | 49 | 4A    | 4B     | 4C    | 4D    | 4E |

|                |                |       | MSM | 62228 | 3-xx di | isplay | -     |         | •      |       | MS | SM525 | 9 disp | olay  |       |    |

| (Display shift | ed to le       | eft)  |     |       |         |        |       |         |        |       |    |       |        |       |       |    |

|                | First<br>digit | 2     | 3   | 4     | 5       | 6      | 7     | 8       | 9      | 10    | 11 | 12    | 13     | 14    | 15    | 16 |

| First line     | 01             | 02    | 03  | 04    | 05      | 06     | 07    | 08      | 09     | 0A    | 0B | 0C    | 0D     | 0E    | 0F    | 10 |

| Second line    | 41             | 42    | 43  | 44    | 45      | 46     | 47    | 48      | 49     | 4A    | 4B | 4C    | 4D     | 4E    | 4F    | 50 |

|                |                |       | MSM | 62228 | 3-xx di | isplay |       |         |        |       | MS | SM525 | 9 disp | olay  |       |    |

| • Since<br>MSM | 5259 0         |       |     |       |         |        |       |         |        |       |    |       |        |       |       |    |

| Fir            |                | o a   | 5 6 | 7 0   | 0 -     | 10 11  | 10 10 | - 1 - 1 | 5 16 - | 17 10 |    | າງ າ  | 1 25   | 0C 07 | 20 20 | 10 |

| Second line | Ľ    |     | 42<br>M62 |   |   |   |   |   | 48 |    |    | 4B<br>259 |    |    |    |    | N  | ISM | 5259<br>display |    |    | 62<br>M5: |    | ·  |    | 66<br>olay | 67 |

|-------------|------|-----|-----------|---|---|---|---|---|----|----|----|-----------|----|----|----|----|----|-----|-----------------|----|----|-----------|----|----|----|------------|----|

| First line  |      |     | 02        |   |   |   |   |   |    |    |    |           |    |    |    |    |    |     |                 |    |    |           |    |    |    | 26         |    |

|             | digi | t 2 | 3         | 4 | 5 | 6 | 7 | 8 | 9  | 10 | 11 | 12        | 13 | 14 | 15 | 16 | 17 | 18  |                 | 33 | 34 | 35        | 36 | 37 | 38 | 39         | 40 |

## **Character Generator ROM (CG ROM)**

The CG ROM is used to generate 5 x 7 dots (160 kinds) or 5 x 10 dots (32 kinds) character patterns from an 8-bit DD RAM character code signal.

The correspondence between 8-bit character codes and character patterns is shown in Table 2.

When the 8-bit character code of the CG ROM is written to the DD RAM, the character pattern of the CG ROM corresponding to the code is displayed on the LCD display position corresponding to the DD RAM address.

Upper MSB Lower 4 bits 0000 0010 0011 0100 0101 0110 0111 1010 1011 1100 1101 1110 1111 4 bits CG RAM (1) 0000 ٠. 7 Ξ 0 @ a Ρ P 夕 Ξ Р 3 р \_\_\_\_ 1 α LSB ŀ ļ Ĥ --2 3 3 (2) Q -34 ア チ L 1 А ä 0001 а q Ь 0 12 q إدعار B 2 ïi ľ e f F R ß " h (3) 2 В L."". Г ッ × × R β Θ 0010 b イ r الأيا ŦF ŝ. E 5 Ŧ Ŧ (4) # С S テ Ð 3 ウ 27 С S ε 0011 1 j  $\infty$ ╒╧╋╵ t D Ţ 47 c 52 (5) \$ D Т т ヤ Ω 4 I d þ. 0100 t F μ ٠. ` 7 . . " E. -ŀ Ļ\_ -1 e 25 (6) % 5 Е オ ナ ユ I\_. ł 0101 U е u ٠ .... σ ü ŀ 8 J. 7 = T ----5 (7) & F \_ ٧ U ヲ ታ \_ 6 V Ξ Σ 0110 ρ 2 g \_ ╪ 37 ] , IJ W ラ TE 0111 (8) 7 e. G g W Ы 77 + ヌ 7 g π 23 --4--4-H , **1--**2 IJ Ć h  $\overline{\mathsf{X}}$  $\sqrt{-}$ ,Г <u>کر</u> (1) 8 Н Х × 4 ク ネ IJ 1000 h Х ( イ i ļ 'T 1 ) 9 -- ! (2) Υ ケ ļ 9 ╘═╏ ル -1 ) у ノ 1001 ゥ y :+: 'n Ţ j. -(3) \* Ζ 1 75 千 J  $\mathcal{N}$  $\nu$ • i 1010 Ζ --т £ tt 23 1 К 'FĘ **7** サ Х 万 (4) ----Κ k E 1011 + オ Ē ~ ] **:** -<u>|-</u> j33 (5) ¥ シ フ ワ 円 1100 < ヤ **†**7 ¢ 2 , . او } M 7 ż (9) m ス ン £ 1101 \_ \_ Μ m -1  $\sim$ ÷ -----= Г 121 Ē ..... 17 > -÷ n **.**... 3 ホ \$ (7) Ν ٨ Ξ セ 1110 n >  $\rightarrow$ . 13 ÷ ----٩.  $\bigcirc$ ο (8) Ż ? d, 0 **-** "1 ソ マ ö 1111 0 ッ

Table 2 Relationship Between Character Codes and Characters (Character Patterns) of MSM6222B -01

18/45

## **Character Generator RAM (CG RAM)**

The CG RAM is used to display user's original character patterns other than character patterns in the CG ROM.

The CG RAM has a capacity (64 bytes = 512 bits) of writing 8 kinds of characters for  $5 \times 7$  dots and 4 kinds of characters for  $5 \times 10$  dots.

When displaying character patterns stored in the CG RAM, write 8-bit character codes (00 to 07 or 08 to 0F; hex.) on the left side as shown in Table 2. Then it is possible to output the character pattern to the LCD display position corresponding to the DD RAM address. The following explains how to write and read character patterns to and from the CG RAM.

(1) When the character pattern is  $5 \times 7$  dots (see Table 3-1).

• A method of writing character pattern to the CG RAM by CPU: Three bits of CG RAM addresses 0-2 correspond to the line position of the character pattern.

First, set increment or decrement by the CPU, and then input the CG RAM address. After this, write character patterns to the CG RAM through  $DB_0 - DB_7$  line by line.  $DB_0$  to  $DB_7$  correspond to CG RAM data 0-7 in Table 3-1.

It is displayed when "H" is set as input data and is not displayed when "L" is set as input data.

Since the ADC is automatically incremented or decremented by 1 after the writing of data to the CG RAM, it is not necessary to set the CG RAM address again.

The line, in which the CG RAM addresses 0-2 are all "H" ("7" in hexadecimal notation), is the cursor position. It is ORed with the cursor at the cursor position and displayed to LCD.

For this reason, it is necessary to set all input data that become cursor positions to "L". Although CG RAM data 0-4 bits are output to the LCD as display data, CG RAM data bits 5-7 are not output. The latter can be written and read to and from the RAM, it is therefore allowed to be used as data RAM.

• A method of displaying the CG RAM character pattern to the LCD:

The CG RAM is selected when upper 4 bits of the character codes are all "L". As character code bit 3 is invalid, the display of "0" in Table 3-1, is selected by character code "00" (hex.) or "08" (hex.).

When the 8-bit character code of the CG RAM is written to the DD RAM, the character pattern of the CG RAM is displayed on the LCD display position corresponding to the DD RAM address. (DD RAM data, bits 0-2 correspond to CG RAM address, bits 3-5.)

(2) When character pattern is  $5 \times 10$  dots (see Table 3-2).

• A method of writing character pattern into the CG RAM by the CPU:

Four bits of CG RAM address, bits 0-3, correspond to the line position of the character pattern.

First, set increment or decrement with the CPU, and then input the address of the CG RAM.

After this, write the character pattern code into the CG RAM, line by line from  $DB_0$ - $DB_7$ .

$DB_0$  to  $DB_7$  correspond to CG RAM data, bits 0-7, in Table 3-2.

It is displayed when "H" is set as input data, while it is not displayed when "L" is set as input data.

As the ADC is automatically incremented or decremented by 1 after the writing of data to the CG RAM, it is not necessary to set the CG RAM address again.

The line, the CGRAM addresses 0-3 of which are "A" in hexadecimal notation, is the cursor position. The CGRAM data is 0Red with the cursor at the cursor position and displayed to LCD. For this reason, it is necessary to set all input data that become cursor positions to "L".

When the CG RAM data, bits 0-4, and CG RAM addresses, bits 0-3, are "0" to "A", they are displayed on the LCD as the display data. When the CG RAM data, bits of 5-7, and CG RAM, bit data is 0-4 and CG RAM address data is "B" to "F", it is not output to the LCD.

But in this case, CG RAM can be used as RAM and it can be written into/read out. So, it can be used as the data RAM.

• A method of displaying the CG RAM character pattern to the LCD:

The CG RAM is selected when 4-upper order bits of the character code are all "L". As character code bits 0 and 3 are invalid, the display of " $\mu$ " is selected by character codes "00", "01", "08", and "09" (hex.) as in Table 3-2.

When the CG RAM character code is written to the DD RAM, the CG RAM character pattern is displayed on the LCD display position corresponding to the DD RAM address.

(DD RAM data bits 1 and 2 correspond to CG RAM address bits 4 and 5.)

Table 3-1Relationship between CG RAM data (character pattern), CG RAM address and<br/>DD RAM data when the character pattern is 5 x 7 dots.<br/>The example below indicates "OKI".

| CG RAM address                                                               | CG RAM data<br>(character pattern)                                                                                                                                                                                                  | DD RAM data<br>(character code) |

|------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|

| 5 4 3 2 1 0                                                                  | 7 6 5 4 3 2 1 0                                                                                                                                                                                                                     | 7 6 5 4 3 2 1 0                 |

| MSB LSB                                                                      | MSB LSB                                                                                                                                                                                                                             | MSB LSB                         |

| L L L L L L                                                                  | X X X L H H H L<br>H L L L H<br>H L L L H<br>L L L H<br>L L L H<br>H L L L L H                                                           | LLLXLL                          |

| L L H L L L                                                                  | X X X H L L H<br>H L L H L<br>H L L L L<br>H L L L L<br>H L L L                                                                             | ГГГХГГН                         |

|                                                                              | $\langle \rangle$                                                                                                                                                                                                                   |                                 |

| H H H L L L<br>L H<br>H H H H<br>H L H H<br>H L H<br>H L H<br>H H H<br>H H H | X X L H H H L<br>L L H L L<br>+ L L L H L L<br>+ L L L L L H L L<br>+ L L L L L L L L L L L L L L L L L L L | L L L X Н Н Н                   |

X : Don't Care

Table 3-2Relationship between CG RAM data (character pattern), CG RAM address and<br/>DD RAM data when the character pattern is 5 x 10 dots. The examples below<br/>indicate  $\mu$ , g and  $\mho$ .

| CG RAM address                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | CG RAM data<br>(character pattern)                                                                                                                                            | DD RAM data<br>(character code) |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|

| 5 4 3 2 1 0<br>MSB LSB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 7 6 5 4 3 2 1 0<br>MSB LSB                                                                                                                                                    | 7 6 5 4 3 2 1 0<br>MSB LSB      |

| L L L L L L<br>L L H<br>L L H<br>L L H<br>L L H<br>L H L<br>L H L<br>L H L<br>L H H<br>L H H<br>L H H<br>L H H<br>L H H<br>L H<br>H L L<br>H L H<br>H L H                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                         | ιιιιχιιχ                        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                               |                                 |

| L H L L L L<br>L L H<br>L L H H<br>L L H H<br>L H L H<br>L H L H<br>L H H L<br>L H H H<br>L H H                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | X X X L L L L L L<br>L L L L L<br>H H H H<br>H L L L H<br>H H H H<br>L L H<br>L H H H<br>L L L H<br>L H H<br>L L L L<br>H | гггхгнх                         |

| H L H H<br>H H L L<br>H H L H<br>H H L H<br>H H H H<br>H H H H                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                         |                                 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                               |                                 |

| L L L L<br>L L H<br>L L H L<br>L L H L<br>L H L<br>L H L<br>L H L<br>L H H<br>L H L<br>H L H<br>H L L<br>H L H<br>H L H<br>H L H<br>H L H<br>H H L<br>H H H<br>H H H H | X X X L L L L L<br>L L L L L<br>H H L L L H<br>H L L L H<br>H L L L H<br>H L L L H<br>H L L L H<br>L H L L H<br>L H L L H<br>L L L L<br>L L L L<br>L L L L<br>X X X X X<br>(  | <br>L L L L X Н Н X             |

X : Don't Care

## **Cursor/Blink Control Circuit**

This is a circuit that generates the LCD cursor and blink.

This circuit is under the control of the CPU program.

The display of the cursor and blink on the LCD is made at a position corresponding to the DD RAM address that is set in the ADC.

The figure below shows an example of the cursor/blink position when the value of ADC is set to "07" (hex.).

(Note) The cursor and blink are displayed even when the CG RAM address is set in the ADC. For this reason, it is necessary to inhibit the cursor and blink display while the CG RAM address is set in the ADC.

# LCD Display Circuit (COM<sub>1</sub> to COM<sub>16</sub>, SEG<sub>1</sub> to SEG<sub>40</sub>, L, CP, DO, and DF)

As the MSM6222B-xx provides the COM signal outputs (16 outputs) and the SEG signal outputs (40 outputs), it can display 8 characters (1-line display) or 16 characters (2-line display) as a unit.

$SEG_1$  to  $SEG_{40}$  are used to display 8-digit display on the LCD. To expand the display, an MSM5259 is used.

The MSM5259, 40-dot segment driver, is used for expansion of the SEG signal output.

Interface with the MSM5259 is made through data output pin (DO), clock output pin (CP), latch output pin (L), and display frequency pin (DF). The character pattern data is serially transferred to MSM5259 through DO and CP. When the data of 72 characters 360-bit (= 5-bit/ch. x 72 ch. = 1-line display) or 32 characters 160-bit (5-bit/ch. x 32 ch. = 2-line display) is output, the latch pulse is also output through pin L. By this latch pulse, the data transferred serially to MSM5259 is latched to be used as display data. The display frequency signal (DF) required when LCD is displayed is also output from DF pin synchronously with this latch pulse.

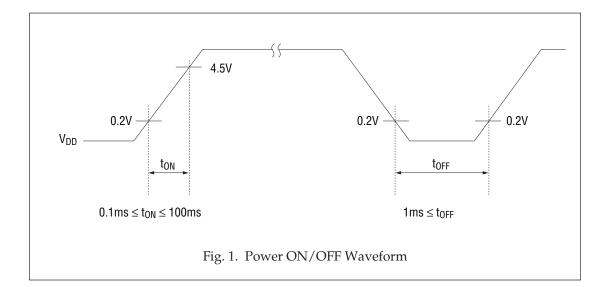

## **Built-in Reset Circuit**

The MSM6222B-xx is automatically initialized when the power is turned on. During initialization, the busy flag (BF) holds "H" and does not accept instructions (other than the busy flag read).

The busy flag holds "H" for 15 ms after V<sub>DD</sub> reaches 4.5V or more.

During initialization, the MSM6222B-xx executes the follwing instructions:

- Display clear

- Data length of interface with CPU: 8 bits (8B/4B = "H")

- LCD: 1-line display (N = "L")

- Character font:  $5 \times 7 \text{ dots} (F = "L")$

- ADC: Increment (I/D = "H")

- No display shift (SH = "L")

- Display: Off (DI = "L")

- Cursor: Off (C = "L")

- No blink (B = "L")

It is required to satisfy the following power supply conditions.

## Data Bus Connected with CPU

The data bus connected with CPU is available either once for 8 bits or twice for 4 bits. This allows the MSM6222B-xx to be interfaced with either an 8-bit or 4-bit CPU.

- When the interface data length is 8 bits Data buses DB<sub>0</sub> to DB<sub>7</sub> (8 buses) are all used and data input/output is carried out in one step.

- (2) When the interface data length is 4 bits The 8-bit data input/output is carried out in two steps by using only high-order 4 bits of data buses DB<sub>4</sub> to DB<sub>7</sub> (4 buses) The first time data input/output is made for 4-high order bits (DB<sub>4</sub> to DB<sub>7</sub> when the interfaces data length is 8 bits) and the second time data input/output is made for loworder 4 bits (DB<sub>0</sub> to DB<sub>3</sub> when the interface data length is 8 bits). Even when the data input/output can be completely made through high-order 4 bits, be sure to make another input/output of low-order 4 bits. (Example: Busy flag Read). Since the data input/output is carried out in two steps but as one execution, no normal data transfer is executed from the next input/output if accessed only once.

MSM6222B-xx

## Instruction Code

The instruction code is defined as the signal through which the MSM6222B-xx is accessed by the CPU.

The MSM6222B-xx begins operation upon receipt of the instruction code input.

As the internal processing operation of MSM6222B-xx starts in a timing that does not affect the LCD display, the busy status continues for longer than the CPU cycle time.

Under the busy status (when the busy flag is set to "H"), the MSM6222B-xx does not execute any instructions other than the busy flag read.

Therefore, the CPU has to verify that the busy flag is set to "L" prior to the input of the instruction code.

(1) Display clear:

|                  | R/W | RS | $DB_7$ | $DB_6$ | $DB_5$ | $DB_4$ | $DB_3$ | $DB_2$ | $DB_1$ | DB <sub>0</sub> |

|------------------|-----|----|--------|--------|--------|--------|--------|--------|--------|-----------------|

| Instruction code | L   | L  | L      | L      | L      | L      | L      | L      | L      | Н               |

When this instruction is executed, the LCD display is cleared.

I/D in the entry mode setting is set to "H" (increment). SH does not change.

When the cursor and blink are in display, the blinking position moves to the left end of the LCD (the left end of the first line in the 2-line display mode).

(Note) All DD RAM data goes to "20" (hex.), while the address counter (ADC) goes to "00" (hex.). The execution time is 1.64 ms (max.), when the OSC oscillation frequency is 250 kHz.

#### (2) Cursor home

|                  |      |        | $DB_7$ | . · · | · · |   |   |   |   | <u> </u> |

|------------------|------|--------|--------|-------|-----|---|---|---|---|----------|

| Instruction code | L    | L      | L      | L     | L   | L | L | L | Н | X        |

|                  | X: D | on't C | are    |       |     |   |   |   |   |          |

When this instruction is executed, the blinking position moves to the left end of the LCD (to the left end of the first line in the 2-line display mode) as the cursor and blink are being displayed.

When the display is in shift, the display returns to its original position before shifting.

(Note) The address counter (ADC) goes to "00" (hex.). The execution time is 1.64 ms (max.), when the OSC oscillation frequency is 250 kHz.

#### (3) Entry mode setting

|                  | R/W | RS | $DB_7$ | $DB_6$ | $DB_5$ | $DB_4$ | $DB_3$ | $DB_2$ | $DB_1$ | $DB_0$ |

|------------------|-----|----|--------|--------|--------|--------|--------|--------|--------|--------|

| Instruction code | L   | L  | L      | L      | L      | L      | L      | Н      | I/D    | SH     |

- When the I/D is set, the 8-bit character code is written or read to and from the DD RAM, the cursor and blink shift to the right by 1 character position (I/D = "H"; increment) or to the left by 1 character position (I/D = "L"; decrement). The address counter is incremented (I/D = "H") or decremented (I/D = "L") by 1 at this time. Even after the character pattern code is written or read to and from the CG RAM, the address counter (ADC) is incremented (I/D = "H") or decremented (I/D = "L") by 1.

- ② When SH = "H" is set, the character code is written to the DD RAM. Then the cursor and blink stop and the entire display shifts to the left (I/D = "H") or to the right (I/ D = "L") by 1 character position.

When the character is read from the DD RAM during SH = "H", or when the character pattern data is written or read to or from the CG RAM during SH = "H", the entire display does not shift, but normal write/read is performed (the entire display does not shift, but the cursor and blink shift to the right (I/D = "H") or to the left (I/D = "L") by 1 character position.

When SH = "L" is set, the display does not shift, but normal write/read is performed. The execution time when the OSC oscillation frequency is 250 kHz is 40  $\mu$ s.

(4) Display mode setting

|                  | R/W | RS | $DB_7$ | $DB_6$ | $DB_5$ | $DB_4$ | $DB_3$ | $DB_2$ | $DB_1$ | DB <sub>0</sub> |

|------------------|-----|----|--------|--------|--------|--------|--------|--------|--------|-----------------|

| Instruction code | L   | L  | L      | L      | L      | L      | Н      | DI     | С      | В               |

The DI bit controls whether the character pattern is displayed or not displayed. When DI is "H", this bit makes the LCD display the character pattern. When DI is "L", the LCD character pattern is not displayed. The cursor and blink are also cancelled at this time.

(Note) Unlike the display clear, the character code is not rewritten at all.

- ② The cursor is not displayed when C = "L" and is displayed when DI = "H" and C = "H".

- (3) The blink is cancelled when B = "L" and is executed when DI = "H" and B = "H". In the blink mode, all dots (including the cursor), displaying character pattern, and cursor are displayed alternately at 409.6 ms (in 5 x 7 dots character font) or 563.2 ms (in 5 x 10 dots character font) when the OSC oscillation frequency is 250 kHz. The execution time when the OSC oscillation frequency is 250 kHz is 40  $\mu$ s.

(5) Cursor and display shift

|                  | R/W | RS     | $DB_7$ | $DB_6$ | $DB_5$ | $DB_4$ | $DB_3$ | $DB_2$ | $DB_1$ | DB <sub>0</sub> |

|------------------|-----|--------|--------|--------|--------|--------|--------|--------|--------|-----------------|

| Instruction code | L   | L      | L      | L      | L      | Н      | D/C    | R/L    | Х      | Х               |

|                  | X:D | on't C | are    |        |        |        |        |        |        |                 |

When D/C = "L" and R/L = "L", the cursor and blink positions are shifted to the left by 1 character position (ADC is decremented by 1).

When D/C = L and R/L = "H", the cursor and blink positions are shifted to the right by 1 character position (ADC is incremented by 1).