### **MSM7557**

Single Chip MSK Modem with Compandor for Cordless Telephone

**OKI** Semiconductor

#### **GENERAL DESCRIPTION**

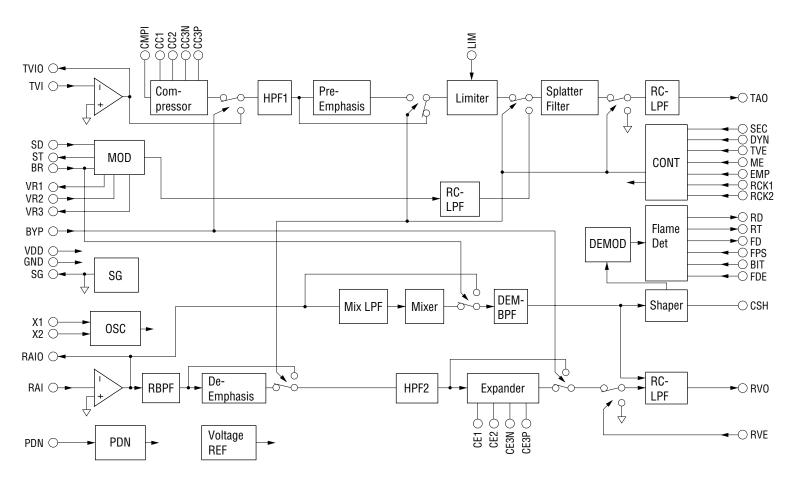

The MSM7557 is a single chip MSK modem with base band voice processor for cordless telephone. The MSM7557 voice transmit block consists of high pass filter, compressor, pre-emphasis, limiter and splatter filter.

Voice receive block consists of Band pass filter, De-emphasis and Expander.

#### FEATURES

- Available to transmit modem signal and also transmit base band voice signal through wireless transmission path (0.3 kHz to 3.4 kHz)

- Built-in compandor circuit

- Upper limit of voice band (3306 Hz/3400 Hz/3500 Hz) is selectable

- Modem bit rate (2400/1200 bps) is selectable

- Transmit function and receive function operate separately

- Emphasis mode selectable

- Built-in bit synchronous detector and frame synchronous detector

- Built-in limiter level generator and external limit voltage input

- Dynamic range selectable

- Built-in crystal oscillator circuit

- Wide range power supply voltage (2.7V ~ 5.5V)

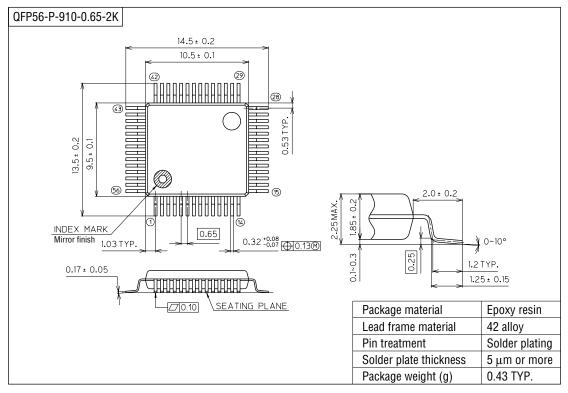

- Package : 56-pin plastic QFP (QFP56-P-910-0.65-2K) (Product name : MSM7557GS-2K)

## **MSM7557**

# **BLOCK DIAGRAM**

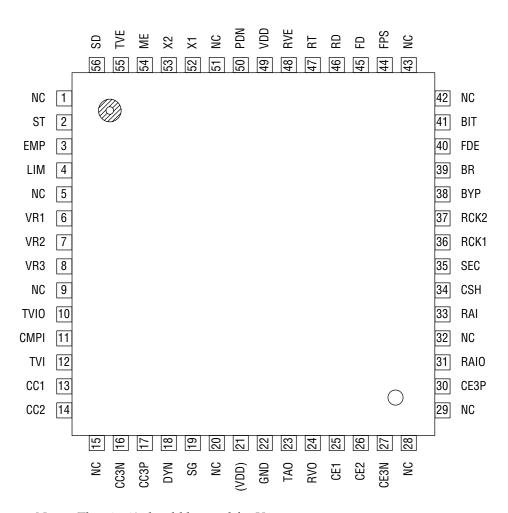

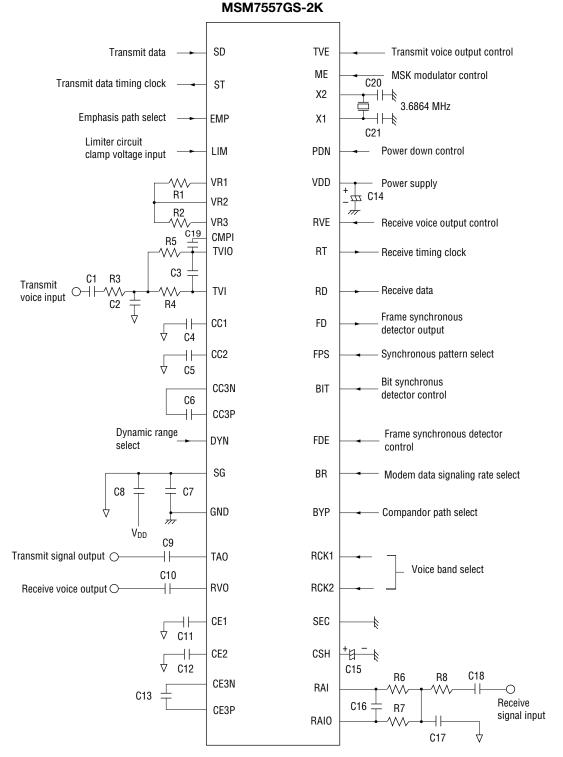

#### **PIN CONFIGURATION (TOP VIEW)**

Notes: The pin 49 should be used for V<sub>DD</sub>.

The pin 21 should be connected to  $V_{DD}$  or opened. NC : No connect pin

#### **PIN DESCRIPTION**

| Name |                                                                                                                                                             | Description                                                                                                                                                                                                                                                      | n                                                                                                                            |  |  |  |  |  |  |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

|      | Transmit                                                                                                                                                    | data input.                                                                                                                                                                                                                                                      |                                                                                                                              |  |  |  |  |  |  |

|      | The data on SD pin are took into MSK modulator and the data are available on the positive edge of ST                                                        |                                                                                                                                                                                                                                                                  |                                                                                                                              |  |  |  |  |  |  |

| SD   | Moc<br>inpu<br>In order to s                                                                                                                                | ME<br>SD input<br>ST<br>Modulator<br>input data<br>In order to synchronize a receive modem, more than 18bits bit-synchronous signal should be                                                                                                                    |                                                                                                                              |  |  |  |  |  |  |

|      | transmitted before data transmission. If S/N ratio of the receive signal is always good, more than 11bits bit-synchronous signal synchronizes the receiver. |                                                                                                                                                                                                                                                                  |                                                                                                                              |  |  |  |  |  |  |

|      | -                                                                                                                                                           | ta timing clock output.                                                                                                                                                                                                                                          |                                                                                                                              |  |  |  |  |  |  |

| ST   |                                                                                                                                                             | I "0" is put on ME pin, ST is fixed to digital "1" I                                                                                                                                                                                                             | level.                                                                                                                       |  |  |  |  |  |  |

|      | Emphasis path selection.                                                                                                                                    |                                                                                                                                                                                                                                                                  |                                                                                                                              |  |  |  |  |  |  |

|      | EMP                                                                                                                                                         | Transmit side                                                                                                                                                                                                                                                    | Receive side                                                                                                                 |  |  |  |  |  |  |

|      |                                                                                                                                                             | Pre-emphasis circuit is bypassed to the                                                                                                                                                                                                                          | De-emphasis circuit is bypassed to the                                                                                       |  |  |  |  |  |  |

|      | 0                                                                                                                                                           |                                                                                                                                                                                                                                                                  | path                                                                                                                         |  |  |  |  |  |  |

| EMP  | 0                                                                                                                                                           | path                                                                                                                                                                                                                                                             | path                                                                                                                         |  |  |  |  |  |  |

| EMP  |                                                                                                                                                             | path<br>Pre-emphasis circuit is connected to the                                                                                                                                                                                                                 | path<br>De-emphasis circuit is connected to the                                                                              |  |  |  |  |  |  |

| EMP  | 0                                                                                                                                                           | •                                                                                                                                                                                                                                                                | •                                                                                                                            |  |  |  |  |  |  |

| LIM  | 1<br>Deviation lir<br>Voice signal<br>this pin.<br>Input imped<br>When this p                                                                               | Pre-emphasis circuit is connected to the                                                                                                                                                                                                                         | De-emphasis circuit is connected to the path                                                                                 |  |  |  |  |  |  |

|      | 1<br>Deviation lir<br>Voice signal<br>this pin.<br>Input imped<br>When this p                                                                               | Pre-emphasis circuit is connected to the<br>path<br>niter control.<br>maximum Rf modulation level is controlled by<br>ance of this pin is about 200 kΩ.<br>in is left open, internal reference voltage is use                                                    | De-emphasis circuit is connected to the path                                                                                 |  |  |  |  |  |  |

|      | 1<br>Deviation lir<br>Voice signal<br>this pin.<br>Input imped<br>When this p<br>Internal clar                                                              | Pre-emphasis circuit is connected to the<br>path<br>niter control.<br>maximum Rf modulation level is controlled by<br>ance of this pin is about 200 kΩ.<br>in is left open, internal reference voltage is use<br>np level is as follows.                         | De-emphasis circuit is connected to the<br>path<br>y connecting external reference voltage to<br>ed as the clamp level.      |  |  |  |  |  |  |

|      | 1<br>Deviation lin<br>Voice signal<br>this pin.<br>Input imped<br>When this p<br>Internal clar<br><b>DYN</b>                                                | Pre-emphasis circuit is connected to the<br>path<br>niter control.<br>maximum Rf modulation level is controlled by<br>ance of this pin is about 200 kΩ.<br>in is left open, internal reference voltage is use<br>np level is as follows.<br>Internal clamp level | De-emphasis circuit is connected to the path y connecting external reference voltage to ed as the clamp level. Limiter level |  |  |  |  |  |  |

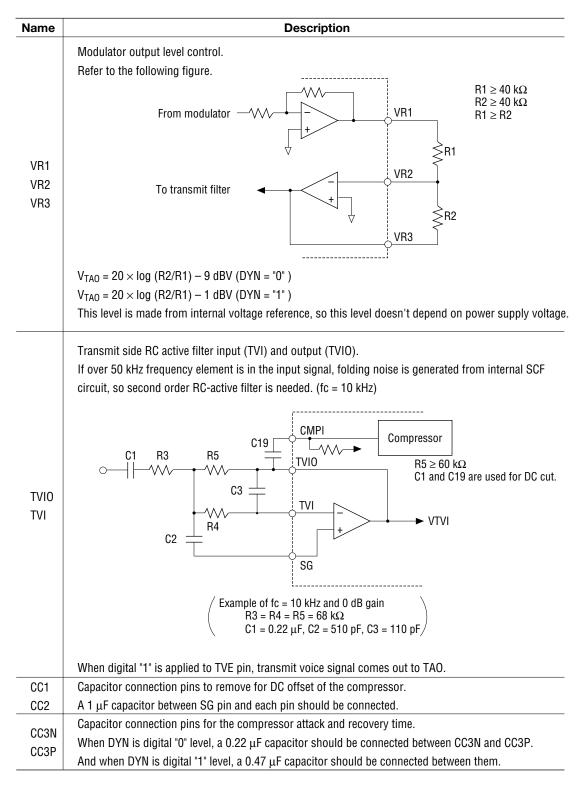

| Name |                                                                                                                                                                                                                 | Description                                                                                        |                   |                                  |                                     |  |  |  |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|-------------------|----------------------------------|-------------------------------------|--|--|--|

|      | Compresso                                                                                                                                                                                                       | r circuit input                                                                                    |                   |                                  |                                     |  |  |  |

| CMPI | Α 0.47 μF c                                                                                                                                                                                                     | apacitor shou                                                                                      | ld be connected b | between CMPI and TVIO            |                                     |  |  |  |

|      | Dynamic ra                                                                                                                                                                                                      | Dynamic range control input.                                                                       |                   |                                  |                                     |  |  |  |

|      | For an application of which $V_{DD}$ is always higher than 4.5 V (Base station), by setting DYN = "1",                                                                                                          |                                                                                                    |                   |                                  |                                     |  |  |  |

|      | modem transmit carrier level, typical input signal level, limiter clamp level and compandor                                                                                                                     |                                                                                                    |                   |                                  |                                     |  |  |  |

| DYN  | standard input level are up about 8dB to improve S/N ratio.                                                                                                                                                     |                                                                                                    |                   |                                  |                                     |  |  |  |

|      | For an application of which $V_{DD}$ is lower than 4.5 V (Hand-set) DYN shall be digital "0".                                                                                                                   |                                                                                                    |                   |                                  |                                     |  |  |  |

|      |                                                                                                                                                                                                                 |                                                                                                    | with the RF part, | one solution is to put di        | gital "0" on DYN pin for both Base  |  |  |  |

|      | station and                                                                                                                                                                                                     |                                                                                                    |                   |                                  |                                     |  |  |  |

| 00   |                                                                                                                                                                                                                 |                                                                                                    |                   | age is half of V <sub>DD</sub> . | aviaa parformanaa it in paanaany to |  |  |  |

| SG   | To make this voltage source impedance lower and to ensure the device performance, it is neces<br>put a bypass capacitor of more than $1\mu$ F between SG and V <sub>DD</sub> in close physical proximity to the |                                                                                                    |                   |                                  |                                     |  |  |  |

| GND  | Ground pin,                                                                                                                                                                                                     | -                                                                                                  |                   |                                  |                                     |  |  |  |

|      |                                                                                                                                                                                                                 |                                                                                                    | itnut             |                                  |                                     |  |  |  |

|      | Transmit analog signal output.<br>According to control data on ME and TVE, TAO is set as follows.                                                                                                               |                                                                                                    |                   |                                  |                                     |  |  |  |

|      | , looorunig t                                                                                                                                                                                                   | ME                                                                                                 | TVE               | 1                                | AO                                  |  |  |  |

| TAO  |                                                                                                                                                                                                                 | 0                                                                                                  | 0                 | No signal output (pot            |                                     |  |  |  |

|      |                                                                                                                                                                                                                 | 0                                                                                                  | 1                 | Voice signal output              |                                     |  |  |  |

|      |                                                                                                                                                                                                                 | 1                                                                                                  | X                 | MSK modulator output             | ıt                                  |  |  |  |

|      |                                                                                                                                                                                                                 |                                                                                                    |                   |                                  | X : Don't care                      |  |  |  |

|      |                                                                                                                                                                                                                 |                                                                                                    |                   |                                  |                                     |  |  |  |

|      | Receive voice signal output.<br>RVO pin state is defined by RVE control.                                                                                                                                        |                                                                                                    |                   |                                  |                                     |  |  |  |

|      | RVU pili sta                                                                                                                                                                                                    |                                                                                                    | JY RVE CONTOI.    |                                  |                                     |  |  |  |

| RV0  |                                                                                                                                                                                                                 | RVE                                                                                                |                   | RVO                              |                                     |  |  |  |

|      |                                                                                                                                                                                                                 | 0                                                                                                  | Output disable    | (potential = SG)                 |                                     |  |  |  |

|      |                                                                                                                                                                                                                 | 1                                                                                                  | Output enable     |                                  |                                     |  |  |  |

|      |                                                                                                                                                                                                                 |                                                                                                    |                   |                                  |                                     |  |  |  |

| CE1  | Capacitor c                                                                                                                                                                                                     | onnection pin                                                                                      | s to remove DC o  | ffset of the expander.           |                                     |  |  |  |

| CE2  |                                                                                                                                                                                                                 |                                                                                                    |                   | pin should be connecte           |                                     |  |  |  |

| CE3N | -                                                                                                                                                                                                               | Capacitor connection pins for the expander attack time and recovery time.                          |                   |                                  |                                     |  |  |  |

| CE3P |                                                                                                                                                                                                                 | When DYN is digital "0" level, a 0.22 $\mu$ F capacitor should be connected between CE3N and CE3P. |                   |                                  |                                     |  |  |  |

|      | And when DYN is digital "1" level, a 0.47 µF capacitor should be connected between them.<br>Receive side amplifier input (RAI) and output (RAIO).                                                               |                                                                                                    |                   |                                  |                                     |  |  |  |

| RAIO |                                                                                                                                                                                                                 |                                                                                                    | . , .             |                                  |                                     |  |  |  |

| RAI  | Second order RC-active filter is needed like TVIO and TVI.<br>Refer to TVIO and TVI pin description.                                                                                                            |                                                                                                    |                   |                                  |                                     |  |  |  |

|      |                                                                                                                                                                                                                 |                                                                                                    |                   | fset of the modem shape          | er circuit.                         |  |  |  |

| CSH  | -                                                                                                                                                                                                               |                                                                                                    |                   | veen GND pin and CSH.            |                                     |  |  |  |

| -    |                                                                                                                                                                                                                 |                                                                                                    |                   |                                  |                                     |  |  |  |

| Name |                 |                                       |             | Function           |                                    |                 |  |

|------|-----------------|---------------------------------------|-------------|--------------------|------------------------------------|-----------------|--|

| SEC  | Device test inp | out.                                  |             |                    |                                    |                 |  |

| 510  | SEC shall be c  | onnected to G                         | ND.         |                    |                                    |                 |  |

|      | Voice band sel  | ect.                                  |             |                    |                                    |                 |  |

| DOKA | -               | RCK1                                  | RCK         | 2 Upper L          | mit of Voice Band                  |                 |  |

| RCK1 | _               | 0                                     | 1           |                    | 3306 Hz                            |                 |  |

| RCK2 | _               | Х                                     | 0           |                    | 3400 Hz                            |                 |  |

|      | _               | 1                                     | 1           |                    | 3500 Hz                            |                 |  |

|      | Compandor pa    | ath selection.                        |             |                    |                                    |                 |  |

| 51/5 | BYP             |                                       | Transmit    | side               | Receive side                       |                 |  |

| BYP  | 0               | Compress                              | or is conne | ected to the path. | Expander is connected to the path. |                 |  |

|      | 1               | Compress                              | or is bypas | sed to the path.   | Expander is bypass                 | ed to the path. |  |

|      | Modem data s    | Modem data signaling rate select pin. |             |                    |                                    |                 |  |

| BR   |                 | _                                     | BR          | Date signaling     | rate                               |                 |  |

|      |                 | _                                     | 0           | 1200 bps           |                                    |                 |  |

|      |                 |                                       | 1           | 2400 bps           |                                    |                 |  |

| Name            | Function                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                        |                   |  |  |  |  |  |  |

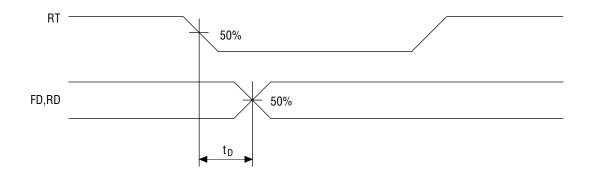

|-----------------|-------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|--|--|--|--|--|--|

| FDE             | When d<br>When d<br>to "1" le                         | Frame synchronous signal detector control.<br>When digital "0" is applied to this pin, FD pin is fixed to "0" level. RT and RD always work.<br>When digital "1" is applied to this pin, frame synchronous detector works, and RT and RD pins are fixed<br>to "1" level untill synchronous signal detector detects frame synchronous signal and FD becomes "1" level.<br>Refer to Fig.3 (receive signal timing).                                                                                                          |                                                                                                                                                                                                                                        |                   |  |  |  |  |  |  |

| BIT             | When B<br>signal a<br>When B<br>signal is             | Refer to Fig.3 (receive signal timing).<br>Bit synchronous signal detector control.<br>When BIT and FDE pins are digital "1" level and when bit synchronous signal and frame synchronous<br>signal are detected continously, FD becomes digital "1".<br>When BIT pin is digital "0" level and FDE pin is digital "1" level and when 16-bit frame synchronous<br>signal is detected, FD pin becomes digital "1" level.<br>Refer to FPS pin detection.                                                                     |                                                                                                                                                                                                                                        |                   |  |  |  |  |  |  |

|                 | Frame s                                               | synchro                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | nous pattern control.                                                                                                                                                                                                                  |                   |  |  |  |  |  |  |

|                 | BIT                                                   | FPS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Detect pattern                                                                                                                                                                                                                         | Receiver          |  |  |  |  |  |  |

|                 | 0                                                     | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 1001 0011 0011 0110 (=9336H)                                                                                                                                                                                                           | Handset side      |  |  |  |  |  |  |

| FPS             | 0                                                     | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 1100 0100 1101 0110 (=C4D6H)                                                                                                                                                                                                           | Base station      |  |  |  |  |  |  |

|                 | 1                                                     | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 1010 1001 0011 0011 0110 (=A9336H)                                                                                                                                                                                                     | Handset side      |  |  |  |  |  |  |

|                 | 1                                                     | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 1010 1100 0100 1101 0110(=AC4D6H)                                                                                                                                                                                                      | Base station      |  |  |  |  |  |  |

|                 |                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | (Note : This pattern is for Japanese Corc                                                                                                                                                                                              | lless Telephone.) |  |  |  |  |  |  |

| FD              | When re<br>When F                                     | eceive<br>DE is a                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | nous detector output.<br>data correspond to detection pattern, FD pin is held to digital "1"<br>pplied to digital "0" level, FD pin is reset to digital "0" level.<br>power down state (PDN = "1", RVE = "0"), FD pin is reset to digi |                   |  |  |  |  |  |  |

| RD              | The dat                                               | a are s <u>y</u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | erial data output.<br>/nchronized with the re-generated timing clock of RT.<br>igital "1" level and also FD is digital "0" level, RD is fixed to digita                                                                                | al "1" level.     |  |  |  |  |  |  |

| RT              | Receive<br>This sig<br>with the<br>The risi<br>When F | When FDE is digital "1" level and also FD is digital "0" level, RD is fixed to digital "1" level.         Receive data timing clock output.         This signal is re-generated by internal digital PLL. The falling edge of this clock output is coincident with the transitions of RD.         The rising edge of RT can be used to latch the valid receive data.         When FDE pin is applied to digital "1" level and also FD pin output digital "0" level, RT pin is fixed to digital "1" level. Refer to Fig.3. |                                                                                                                                                                                                                                        |                   |  |  |  |  |  |  |

| RVE             | Receive                                               | voice                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | signal control.<br>vin description.                                                                                                                                                                                                    |                   |  |  |  |  |  |  |

| V <sub>DD</sub> | This d<br>A bypa                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | s sensitive to power supply noises as switched capacitor tequnion acitor of more than 10 $\mu F$ between $V_{DD}$ and GND pin should be                                                                                                | •                 |  |  |  |  |  |  |

|          | Function                                                   |                                                             |                                                     |                                              |                          |                      |                        |                                   |  |  |  |

|----------|------------------------------------------------------------|-------------------------------------------------------------|-----------------------------------------------------|----------------------------------------------|--------------------------|----------------------|------------------------|-----------------------------------|--|--|--|

|          | Power down control.                                        |                                                             |                                                     |                                              |                          |                      |                        |                                   |  |  |  |

|          | Power down state is controlled by PDN, ME, RVE, and TVE.   |                                                             |                                                     |                                              |                          |                      |                        |                                   |  |  |  |

|          |                                                            | PDN                                                         | ME                                                  | RVE                                          | TVE                      | Voice control        | Transmit side          | Receive side                      |  |  |  |

|          | Madat                                                      | 1                                                           | Х                                                   | 0                                            | x                        | path<br>OFF          | modem<br>OFF           | 0FF                               |  |  |  |

|          | Mode1                                                      |                                                             |                                                     | -                                            |                          |                      |                        |                                   |  |  |  |

| PDN      | Mode2                                                      | 1                                                           | Х                                                   | 1                                            | X                        | OFF                  | OFF                    | ON                                |  |  |  |

|          | Mode3                                                      | 0                                                           | 1                                                   | 0                                            | 0                        | OFF                  | ON                     | ON                                |  |  |  |

|          | Mode4                                                      |                                                             | oth                                                 | ners                                         |                          | ON                   | ON                     | ON                                |  |  |  |

|          |                                                            |                                                             | ,                                                   | demodu                                       |                          | cuit and FD pin shou | Ild be reset by settin | g Mode1.                          |  |  |  |

| X1       | Crystal conn<br>3.6864 MHz<br>When an ext                  | crystal s                                                   | hall be                                             | connect                                      | ed.                      |                      |                        | -                                 |  |  |  |

| X1<br>X2 | 3.6864 MHz                                                 | crystal s<br>ernal ma                                       | hall be<br>ster clo                                 | connect<br>ock is ap                         | ed.<br>plied, the        |                      |                        | g Mode1.<br>a 200 pF capacitor fo |  |  |  |

|          | 3.6864 MHz<br>When an extended<br>AC coupling<br>MSK moudu | crystal s<br>ernal ma<br>and X1 s<br>lator out<br>"1" is ap | hall be<br>ster clo<br>should l<br>put.<br>plied to | connect<br>ick is ap<br>be opene<br>this pin | ed.<br>plied, the<br>ed. | e clock should be su |                        | a 200 pF capacitor fo             |  |  |  |

#### **ABSOLUTE MAXIMUM RATINGS**

| Parameter                | Symbol           | Condition               | Rating            | Unit |

|--------------------------|------------------|-------------------------|-------------------|------|

| Power Supply Voltage     | V <sub>DD</sub>  | Ta = 25°C               | -0.3 to +7.0      |      |

| Analog Input Voltage *1  | VIA              | a = 250<br>Refer to GND |                   | V    |

| Digital Input Voltage *2 | VID              |                         | -0.3 to VDD + 0.3 |      |

| Storage Temperature      | T <sub>STG</sub> | _                       | -55 to +150       | °C   |

\*1 : LIM, VR2, TVI, RAI, CMPI

\*2 : SD, EMP, DYN, SEC, RCK1, RCK2, BYP, BR, FDE, BIT, FPS, RVE, PDN, X2, ME, TVE

#### **RECOMMENDED OPERATING CONDITIONS**

| Parameter                 | Symbol             | Condition             |            | Min.   | Тур.   | Max.   | Unit    |

|---------------------------|--------------------|-----------------------|------------|--------|--------|--------|---------|

| Power Supply Voltage      | V <sub>DD</sub>    | from                  | DYN = "0"  | 2.7    | 3.6    | 5.5    | V       |

| Fower Supply voltage      |                    | GND level             | DYN= "1"   | 4.5    | 5.0    | 5.5    | v       |

| Operating Temperature     | T <sub>op</sub>    | V <sub>DD</sub> = 2.7 | V to 5.5 V | -30    | +25    | +70    | °C      |

| Crystal Oscillating Freq. | f <sub>X'TAL</sub> | -                     | _          | 3.6860 | 3.6864 | 3.6868 | MHz     |

| Data Signaling Rate       | т.                 | BR                    | = 0"       |        | 1200   | —      | bit/sec |

|                           | T <sub>S</sub>     | BR = "1"              |            |        | 2400   | —      | DIL/Sec |

| C4, C5, C11, C12, C15     |                    | -                     | _          |        | 1.0    |        |         |

| 06 010                    | —                  | DYN = "0"             |            | _      | 0.22   | —      |         |

| C6, C13                   | —                  | DYN = "1"             |            |        | 0.47   | —      |         |

| C7, C8                    |                    | -                     | _          |        | 1.0    |        | μF      |

| C9, C10                   |                    | RL≥                   | 40kΩ       | _      | 0.22   |        |         |

| C14                       | _                  | -                     | _          |        | 10     | _      |         |

| C19                       |                    | -                     | _          |        | 0.47   |        |         |

| C20, C21                  | _                  | -                     | _          | _      | 20     | _      | pF      |

#### **ELECTRICAL CHARACTERISTICS**

#### **DC Characteristics**

$\left(\begin{array}{c} DYN = "0": V_{DD} = 2.7 \ V \ to \ 5.5 \ V, \ Ta = -30^{\circ}C \ to \ 70^{\circ}C \\ DYN = "1": V_{DD} = 4.5 \ V \ to \ 5.5 \ V, \ Ta = -30^{\circ}C \ to \ 70^{\circ}C \end{array}\right)$

| Parameter                | Symbol            | Condit               | Condition |                    | Тур. | Max.               | Unit |  |

|--------------------------|-------------------|----------------------|-----------|--------------------|------|--------------------|------|--|

|                          | loo               | Normal 3.6 V         |           | _                  | 9.0  | 18                 | mA   |  |

|                          | I <sub>DD</sub>   | mode<br>(mode 4)     | 5.5 V     | _                  | 14.0 | 24                 | ША   |  |

| Dawar Cumply Current *   | I <sub>DDS1</sub> | Power down<br>mode 1 | 5.5 V     | _                  | 1.0  | 20                 | μΑ   |  |

| Power Supply Current *1  | I <sub>DDS2</sub> | Power down<br>mode 2 | 3.6 V     | _                  | 3.8  | 7.0                | mA   |  |

|                          | I <sub>DDS3</sub> | Power down<br>mode 3 | 3.0 V     | _                  | 4.6  | 9.0                |      |  |

| Input Leakage Current *2 | I <sub>IL</sub>   | $V_{IN} = 0$         | V         | -10                |      | +10                | μA   |  |

| Input Leakage outfent 2  | I <sub>IH</sub>   | V <sub>IN</sub> = V  | DD        | -10                | —    | +10                | μΛ   |  |

| Input Voltege *2         | ١ <sub>IL</sub>   |                      |           | 0                  | —    | 0.2V <sub>DD</sub> |      |  |

| input voltege Z          | I <sub>IH</sub>   |                      |           | $0.7V_{DD}$        |      | V <sub>DD</sub>    | v    |  |

| Output Voltege *3        | V <sub>OL</sub>   | $I_{0L} = -20$       | ) μΑ      | 0                  | _    | 0.1V <sub>DD</sub> | v    |  |

| Output voltege 3         | V <sub>OH</sub>   | I <sub>0H</sub> = 20 | μA        | 0.8V <sub>DD</sub> | _    | V <sub>DD</sub>    |      |  |

\*1 Refer to PDN pin description

\*2 SD, EMP, DYN, SEC, RCK1, RCK2, BYP, BR, FDE, BIT, FPS, RVE, PDN, ME, TVE

\*3 ST, FD, RD, RT

#### **AC Characteristics**

|                                |          |                 |                                                                                                                   | \ D                   | DYN = "1" : $V_{DD}$ = 4.5 V to 5.5 V, Ta = -30°C to 70°C / |                      |      |      |

|--------------------------------|----------|-----------------|-------------------------------------------------------------------------------------------------------------------|-----------------------|-------------------------------------------------------------|----------------------|------|------|

| Paramete                       | ər       | Symbol          | Cond                                                                                                              | ition                 | Min.                                                        | Тур.                 | Max. | Unit |

|                                |          | f <sub>M1</sub> | SD = "1"                                                                                                          | BR = "0"              | 1199                                                        | 1200                 | 1201 |      |

| Transmit                       | Transmit |                 | SD= "0"                                                                                                           | ME= "1"               | 1799                                                        | 1800                 | 1801 | Hz   |

| Carrier Frequenc               | cy .     | f <sub>M2</sub> | SD = "1"                                                                                                          | BR = "1"              | 1199                                                        | 1200                 | 1201 | 112  |

|                                |          | f <sub>S2</sub> | SD= "0"                                                                                                           | ME= "1"               | 2399                                                        | 2400                 | 2401 |      |

| Transmit                       |          | N               | D1 D0                                                                                                             | DYN = "0"             | -11                                                         | -9                   | -7   |      |

| Carrier Level                  |          | V <sub>OX</sub> | R1 = R2                                                                                                           | DYN = "1"             | -3                                                          | -1                   | +1   | dBV  |

| Receive Carrier<br>Input Level |          | V <sub>IR</sub> |                                                                                                                   |                       | -32                                                         | _                    | -2   | uDv  |

|                                | 1200     |                 | Defined at RAIO                                                                                                   | 8 dB                  | _                                                           | 1 × 10 <sup>-3</sup> | _    |      |

| Bit Error Rate                 | bps      | B <sub>ER</sub> |                                                                                                                   | 10 dB                 |                                                             | 5 × 10 <sup>-5</sup> |      |      |

| DIL ETTUT HALE                 | 2400     | DER             |                                                                                                                   | 11 dB                 | _                                                           | 1 × 10 <sup>-3</sup> |      |      |

|                                | bps      |                 |                                                                                                                   | 13 dB                 | _                                                           | 5 × 10 <sup>-5</sup> |      |      |

| Number of PLL I                | Lock-in  |                 | Number of data bits<br>required for the PLL to<br>be locked in within the<br>phase difference of<br>22.5° or less |                       | _                                                           | _                    | 18   | bit  |

| Data Bits *1                   |          | V <sub>IR</sub> | Number of o<br>required for<br>be locked in<br>phase differ<br>90° or less                                        | the PLL to within the | _                                                           | _                    | 11   |      |

$(DYN = "0" : V_{DD} = 2.7 V \text{ to } 5.5 V, Ta = -30^{\circ}C \text{ to } 70^{\circ}C)$ DYN = "1" : V\_{DD} = 4.5 V to 5.5 V, Ta = -30^{\circ}C to 70^{\circ}C)

\*1 Receive MSK signal is bit synchronous signal (modulated signal of alternating "0", "1" pattern).

| Voice | Signal | Interfaces |

|-------|--------|------------|

|       | e gua  |            |

| Voice Sign    | al Interfac                         | es               |                              |                | 0" : V <sub>DD</sub> = 2.<br>1" : V <sub>DD</sub> = 4. |       |       |      |

|---------------|-------------------------------------|------------------|------------------------------|----------------|--------------------------------------------------------|-------|-------|------|

| Para          | meter                               | Symbol           | Conc                         | lition         | Min.                                                   | Тур.  | Max.  | Unit |

| RVO Maximi    | um Output                           |                  | fin = 1 kHz                  | DYN = "0"      | _                                                      |       | -6    |      |

| Signal Level  |                                     | V <sub>OUT</sub> | BYP = "0" *1                 | DYN = "1"      | _                                                      | _     | +2    |      |

|               |                                     |                  | fin = 1 kHz                  | DYN = "0"      | -10                                                    | -9    | -8    | dBV  |

| Limiter Clam  | ip Level                            | V <sub>LIM</sub> | LIM = open                   | DYN = "1"      | -2                                                     | -1    | 0     |      |

| Transmit Ou   | tput Distortion                     | H <sub>DT</sub>  | fIN = 1  kHz, -              | 12 dBV         | _                                                      | -40   | _     |      |

| Receive Out   | put Distortion                      | H <sub>DR</sub>  | BYP = "0", EM                | P = "1"        |                                                        | -40   | _     |      |

| Transmit Ga   | in                                  | GT               | fin = 1 kHz, B               | (P = EMP = "1" | -1.5                                                   | -0.2  | +1    | dB   |

| Receive Gair  | l                                   | G <sub>R</sub>   | fin = 1 kHz, BYP = EMP = "1" |                | -1.5                                                   | -0.2  | +1    |      |

| Transmit Idle | e Noise                             | HIT              | BYP = "0"                    |                | —                                                      | -51   | —     |      |

| Receive Idle  | Noise                               | H <sub>IR</sub>  | EMP = "1"                    |                |                                                        | -85   |       |      |

| Cross Talk    | $R_{CV.} {\rightarrow} T_{ran.}$    | C <sub>TT</sub>  | RAIO = -2 dB'                | V *2           | _                                                      | -75   | -60   | dBV  |

| 01055 Taik    | T <sub>ran.→</sub> R <sub>CV.</sub> | CTR              | TVIO = -2 dBV                | / 2            | —                                                      | -80   | -60   |      |

|               |                                     | FT1              | EMP = "1"                    | 100 Hz         | _                                                      | -28   | -23   |      |

| Transmit Filt | or                                  | FT3              | EWP = 1<br>BYP = "1"         | 300 Hz         | -12.5                                                  | -10.5 | -8.5  | -    |

|               | .61                                 | FT25             | BTP = 1<br>RCK2 = "0"        | 2.5 kHz        | +6.5                                                   | +8.0  | +9.5  |      |

| Response      |                                     | FT34             |                              | 3.4 kHz        | +8.5                                                   | +10.5 | +12.5 |      |

|               |                                     | FT60             | Ref. = 1 kHz                 | 6 kHz          |                                                        | -40   | -30   |      |

|               |                                     | FR1              |                              | 100 Hz         | +1.5                                                   | +3.0  | +4.5  | dB   |

|               |                                     | FR3              | EMP = "1"                    | 300 Hz         | +8.0                                                   | +9.5  | +11.0 |      |

| Receive Filte | 1                                   | FR25             | BYP = "1"                    | 2.5 kHz        | -9.5                                                   | -8.0  | -6.5  |      |

| Response      |                                     | FR34             | RCK2 = "0"                   | 3.4 kHz        | -12.5                                                  | -10.5 | -8.5  |      |

|               |                                     | FR60             | Ref. = 1 kHz                 | 6 kHz          |                                                        | -40   | -30   |      |

\*1 S/D  $\ge$  20 dB

\*2 fIN = 1 kHz, BYP = EMP = "1"

| \ DYN = "1" : V <sub>DD</sub> = 4.5 V to 5.5 V, Ta = |                |                  |                            |           |       |       |       |      |

|------------------------------------------------------|----------------|------------------|----------------------------|-----------|-------|-------|-------|------|

|                                                      | Parameter      | Symbol           | Condit                     | ion       | Min.  | Тур.  | Max.  | Unit |

|                                                      | Standard Input | Vier             |                            | DYN = "0" | -16.1 | -13.7 | -11.3 |      |

|                                                      | Level          | V <sub>ICS</sub> |                            | DYN = "1" | -7.1  | -5.5  | -3.9  | 101/ |

|                                                      | Maximum Input  | V                | f <sub>IN</sub> = 1 kHz    | DYN = "0" | —     | _     | -7    | dBV  |

| <u>ب</u>                                             | Level          | V <sub>ICM</sub> |                            | DYN = "1" | —     | —     | +1.0  |      |

| Compressor                                           | Output         | GC2              |                            | –20 dB    | -10.6 | -9.9  | -9.2  |      |

| npre                                                 | Level *3       | GC4              | f <sub>IN</sub> = 1 kHz    | -40 dB    | -21.0 | -19.8 | -18.6 | dB   |

| Cor                                                  | Level 5        | GC5              |                            | -60 dB    | —     | -29.5 |       |      |

|                                                      | Attack Time    | T <sub>AT1</sub> | DYN = "0", C6 = 0          | .22 μF    | —     | 3.4   | _     |      |

|                                                      | Attack Time    | T <sub>AT2</sub> | DYN = "1", C6 = 0          | .47 μF    | —     | 3.5   | —     | ms   |

|                                                      | Decover / Time | T <sub>RE1</sub> | DYN = "0", C6 = 0          | .22 μF    | —     | 17    |       |      |

|                                                      | Recovery Time  | T <sub>RE2</sub> | DYN = "1", C6 = 0          | .47 μF    | —     | 16    |       |      |

|                                                      | Standard Input | V <sub>IES</sub> |                            | *4        | -12.9 | -10.8 | -8.7  | dBV  |

|                                                      | Level          |                  |                            | *5        | -13.3 | -11.2 | -9.1  |      |

|                                                      |                |                  | f <sub>IN</sub> = 1 kHz    | *6        | -4.7  | -3.1  | -1.5  |      |

|                                                      | Maximum        | VIEM             |                            | DYN = "0" |       | _     | -6    |      |

| der                                                  | Output Level   |                  |                            | DYN = "1" | —     | —     | +2    |      |

| Expander                                             | Output         | GE1              |                            | -10 dB    | -21.5 | -20   | -18.3 |      |

| Ä                                                    | Level          | GE2              | f <sub>IN</sub> = 1 kHz *3 | –20 dB    | -42.2 | -40   | -37.5 | dB   |

|                                                      | Levei          | GE3              |                            | -30 dB    | —     | -59   |       | 1    |

|                                                      | Attack         | T <sub>AT3</sub> | DYN = "0", C13 =           | 0.22 μF   | _     | 3.4   |       |      |

|                                                      | Time           | T <sub>AT4</sub> | DYN = "1", C13 =           | 0.47 μF   | —     | 3.5   |       | ms   |

|                                                      | Recovery       | T <sub>RE3</sub> | DYN = "0", C13 =           | 0.22 μF   | _     | 17    | —     |      |

|                                                      | Time           | T <sub>RE4</sub> | DYN = "1", C13 =           | 0.47 μF   | _     | 16    | —     |      |

$\begin{pmatrix} DYN = "0" : V_{DD} = 2.7 V \text{ to } 5.5 V, Ta = -30^{\circ}C \text{ to } 70^{\circ}C \\ DYN = "1" : V_{DD} = 4.5 V \text{ to } 5.5 V. Ta = -30^{\circ}C \text{ to } 70^{\circ}C \end{pmatrix}$

\*3 0 dB is defined as the input level and the output level when the standard input level is input.

\*4  $V_{DD} = 3.6 V, DYN = "0"$

\*5  $V_{DD} = 5.0 \text{ V}, \text{DYN} = "0"$

\*6  $V_{DD} = 5.0 V$ , DYN = "1"

| Common Characteristics |                   | $\left(\begin{array}{c} DYN = "0": V_{DD} = 2.7 \; V \; to \; 5.5 \; V, \; Ta = -30^\circ C \; to \; 70^\circ C \\ DYN = "1": V_{DD} = 4.5 \; V \; to \; 5.5 \; V, \; Ta = -30^\circ C \; to \; 70^\circ C \end{array}\right)$ |      |                           |                    |                           |      |  |

|------------------------|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|---------------------------|--------------------|---------------------------|------|--|

| Parameter              | Symbol            | Condition                                                                                                                                                                                                                      |      | Min.                      | Тур.               | Max.                      | Unit |  |

| Input Resistance       | RIA               | TVI, RAI, VR2                                                                                                                                                                                                                  |      | _                         | 10                 | _                         | MΩ   |  |

|                        | RIC               | LIM                                                                                                                                                                                                                            |      | —                         | 200                | —                         | kΩ   |  |

| Output Resistance      | Rox1              | TAO                                                                                                                                                                                                                            |      |                           | 1750               | —                         |      |  |

|                        | R <sub>0x2</sub>  | VR1, VR3, RV0                                                                                                                                                                                                                  |      |                           | 600                |                           | Ω    |  |

|                        | R <sub>0x</sub> 3 | TVIO, RAIO                                                                                                                                                                                                                     |      | —                         | 100                | —                         |      |  |

| Output Load Resistance | RXL1              | $S/D \ge 20 \text{ dB}$                                                                                                                                                                                                        | *1   | 40                        | _                  | _                         | kΩ   |  |

|                        | RXL2              |                                                                                                                                                                                                                                | TVI0 | 60                        | —                  | _                         |      |  |

| Output DC Voltage      | V <sub>SG</sub>   | SG                                                                                                                                                                                                                             |      | $\frac{V_{DD}}{2} - 0.1$  | $\frac{V_{DD}}{2}$ | $\frac{V_{DD}}{2} + 0.1$  | V    |  |

|                        | V <sub>AO</sub>   | TAO, RVO                                                                                                                                                                                                                       |      | $\frac{V_{DD}}{2} - 0.15$ | $\frac{V_{DD}}{2}$ | $\frac{V_{DD}}{2} + 0.15$ | V    |  |

#### **Common Characteristics**

\*1 VR1, VR3, TAO, RVO, RAIO

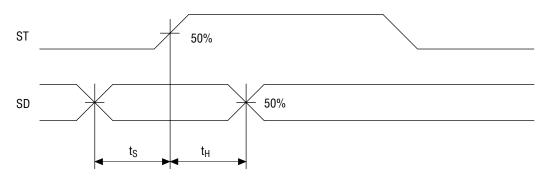

#### **Digital Timing Characteristics**

$\left(\begin{array}{l} DYN = "0": V_{DD} = 2.7 \ V \ to \ 5.5 \ V, \ Ta = -30^\circ C \ to \ 70^\circ C \\ DYN = "1": V_{DD} = 4.5 \ V \ to \ 5.5 \ V, \ Ta = -30^\circ C \ to \ 70^\circ C \end{array}\right)$

| Parameter            | Symbol          | Condition           | Min. | Тур.  | Max. | Unit |

|----------------------|-----------------|---------------------|------|-------|------|------|

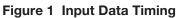

| Transmit Data        | t <sub>S</sub>  | Refer to Fig. 1     | 1    | _     |      | μs   |

| Set-up Time          |                 |                     |      |       |      |      |

| Transmit Data        |                 |                     | 1    |       |      |      |

| Hold Time            | t <sub>H</sub>  |                     |      |       |      |      |

| Receive Data         | ta              | Refer to Fig. 1 -30 | 000  | 300 — | 300  | ns   |

| Output Delay         | t <sub>D</sub>  |                     | -300 |       |      |      |

| Sync-signal          | t               | Refer to Fig. 1     | 0    | _     | 834  | μs   |

| Output Delay (ME→ST) | t <sub>MS</sub> |                     |      |       |      |      |

#### **TIMING DIAGRAM**

#### **OPERATION DESCRIPTION**

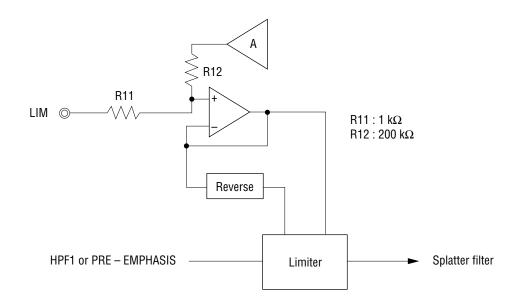

#### Limiter Circuit

| DYN = "0" | : Clamp level = VSG $\pm 0.50$ V |

|-----------|----------------------------------|

| DYN = "1" | : Clamp level = VSG $\pm 1.26$ V |

2. In case of using external voltage reference

LIM pin shall be supplied over VSG voltage.

- Notes 1 ) R11 is protection resister from external extra voltage.

- 2 ) Resistor value of R11 and R12 changes 0.7 to 1.3 times from the typical value by lot variation and temperature variation.

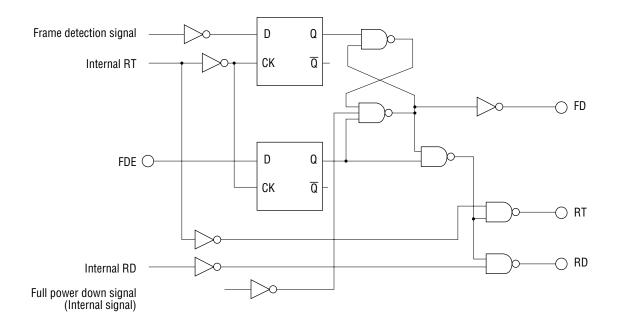

#### Frame Detector

Frame detection pattern is defined by BIT and FPS.

| BIT | FPS | Sync-pattern | Receiver | Note                    |

|-----|-----|--------------|----------|-------------------------|

| 0   | 0   | 9336H        | S.H.     | Frame synchronous       |

| 0   | 1   | C4D6H        | M.T.     | Frame synchronous       |

| 1   | 0   | A9336H       | S.H.     | Bit + Frame synchronous |

| 1   | 1   | AC4D6H       | M.T.     | Bit + Frame synchronous |

M.T. = Master telephone

S.H. = Slave handset

Fig 3 shows detection timing

First, put digital "0" level to FDE pin more than 1 ms, then FD pin is reset to "0" level.

Next, put digital "1" level to FDE pin, then RT and RD output digital "1" level until frame synchronous signal detected.

When synchronous pattern is detected, FD pin is held to digital "1" level.

At the full power down state (PDN = "1", RVE = "0"), FD pin becomes reset state.

In order to detect frame synchronous signal certainly, receive side PLL should be locked in sufficiently.

When a modem starts data transmittion, the bit-synchronous signal of more than 18 bits should be transmitted before frame pattern of the upper table.

#### **Application Circuit**

**Note** : An arrow mark of  $(\downarrow)$  indicates connection to the SG pin.

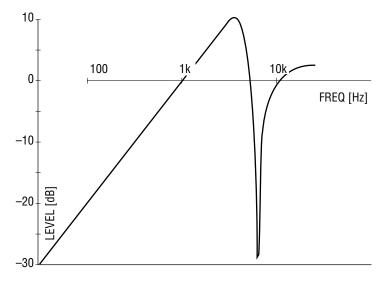

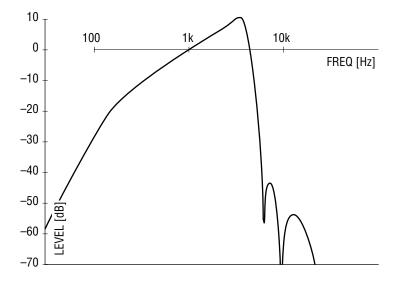

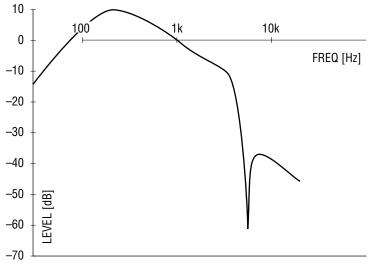

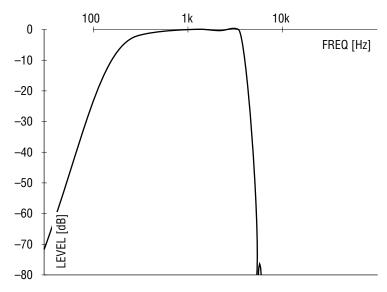

#### **MSM7557 Filter Characteristics**

MSM7557 has wide band filters (0.3 kHz to 3.4 kHz) as follows.

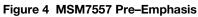

| Pre-Emphasis Fig.                                    | 4 |

|------------------------------------------------------|---|

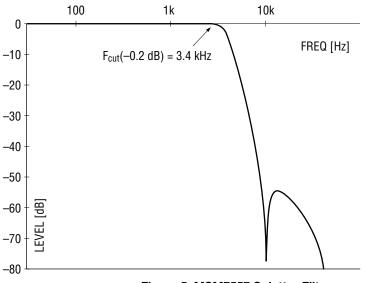

| Splatter Filter Fig.                                 | 5 |

| RBPF                                                 |   |

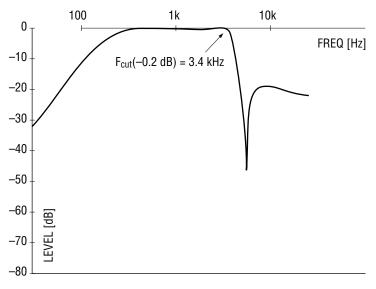

| De-Emphasis Fig.                                     |   |

| Transmit Total (HPF1 + Pre-Emphasis + Splatter) Fig. |   |

| Receive Total (RBPF + De-Emphasis) Fig.              |   |

| Transmit and Receive Total Fig.                      |   |

Fig. 4 to Fig. 10 show the filter characteristics when RCK2 is digital "0". When RCK1 is digital "0" and RCK2 is digital "1", the filter characteristics change 0.972 times on the frequency axis. (pass-band becomes narrow) When RCK1 is digital "1" and RCK2 is digital "1", the filter characteristics change 1.029 times on the frequency axis. (pass-band becomes wide)

Figure 5 MSM7557 Splatter Filter