# **Multi-Channel ATM AAL1 SAR**

#### **Features**

- AAL1 Segmentation and Reassembly device compatible with Structured Data Transfer (SDT) as per ANSI T1.630 and ITU I.363 standards

- Transports 64kbps and N x 64kbps traffic over ATM AAL1 cells (also over AAL5 or AAL0)

- Simultaneous processing of up to 1024 bidirectional Virtual Circuits

- Flexible aggregation capabilities (Nx64) to allow any combination of 64 kbps channels while maintaining frame integrity (DS0 grooming)

- Support for clock recovery Adaptive Clock Recovery, Synchronous Residual Time Stamp (SRTS), or external

- Primary UTOPIA port (Level 1, 25 MHz) for connection to external PHY devices with data throughput of up to 155 Mbps

- Secondary UTOPIA port for connection to an external AAL5 SAR processor, or for chaining multiple MT90500 devices

- 16-bit microprocessor port, configurable to Motorola or Intel timing

- TDM bus provides 16 bidirectional serial TDM

DS5171 ISSUE 4 April 1999

### **Ordering Information**

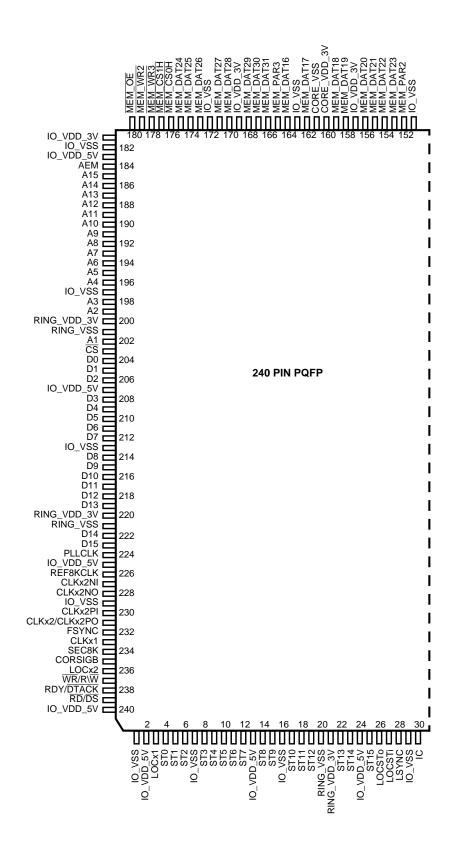

MT90500AL 240 Pin Plastic QFP

-40 to +85 C

streams at 2.048, 4.096, or 8.192 Mbps for up to 2048 TDM 64 kbps channels

- Compatible with ST-BUS, MVIP, H-MVIP and SCSA interfaces

- Supports master and slave TDM bus clock operation

- Loopback function at TDM bus interface

- Local TDM bus provides clocks, input pin and output pin for 2.048 Mbps operation

- Master clock rate up to 60 MHz

- Dual rails (3.3V for power minimization, 5V for standard I/O)

- IEEE1149 (JTAG) interface

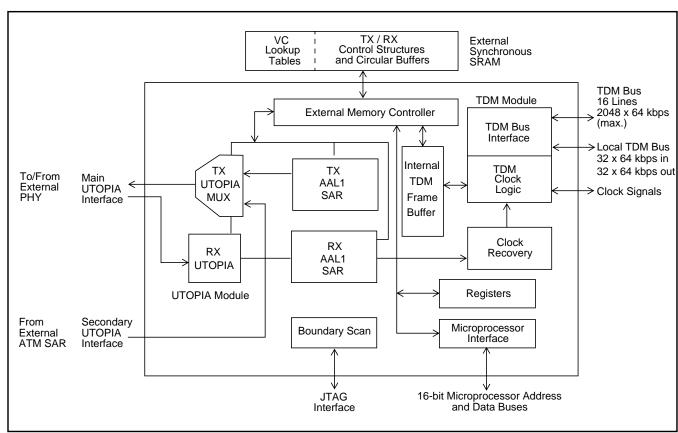

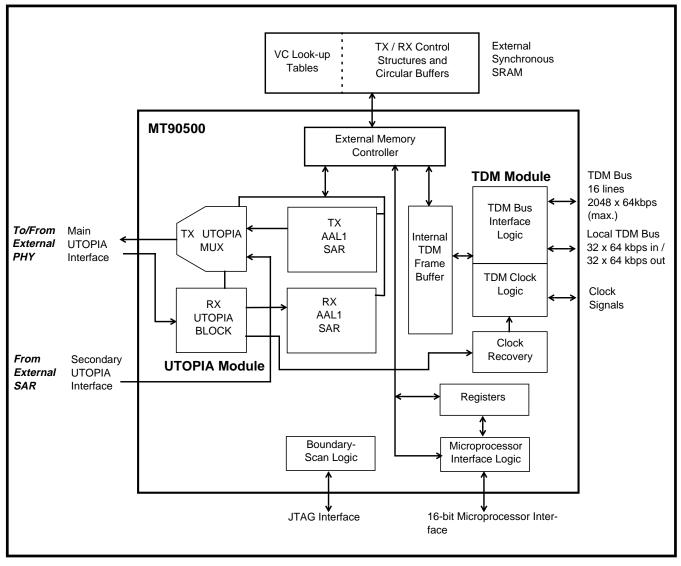

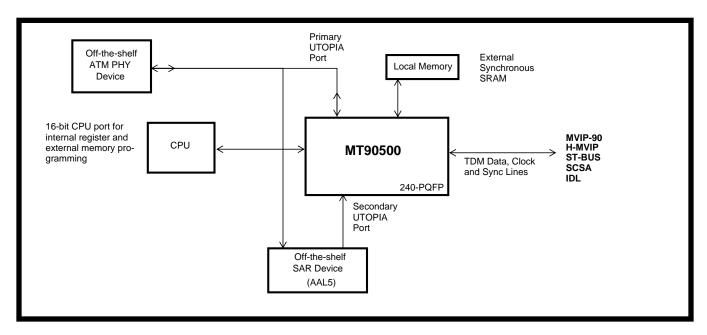

Figure A - MT90500 Block Diagram

## **Applications**

- B-ISDN (Broadband ISDN) systems requiring flexible N x 64kbps transport

- Connecting TDM backplane to TDM backplane over ATM network (GO-MVIP MC4, or other)

- Systems requiring ANSI T1.630 Structured Data Transfer services for 1 to 122 TDM channels per VC

- Systems requiring ITU-T I.363.1 circuit transport over Structured Data Transfer for 1 to 96 TDM channels per VC

- Systems requiring AF-VTOA-0078.000 (ATM Forum CES v2.0) "Logical Nx64 Basic Service"

- Systems requiring AF-VTOA-0083.000 Voice and Telephony over ATM (CBR-AAL5).

- Mapping between CBR-AAL0, CBR-AAL5, and AAL1

- Mapping between CBR partially-filled cells and full cells

- Mapping between CBR single-voice cells and Nx64 cells

- ATM uplink for expansion of COs, PBXs, or open switching platforms using an adjunct ATM switch

- ATM Public Network access for PBX or CO

- ATM Edge Switches and CPE Integrated-Access over ATM

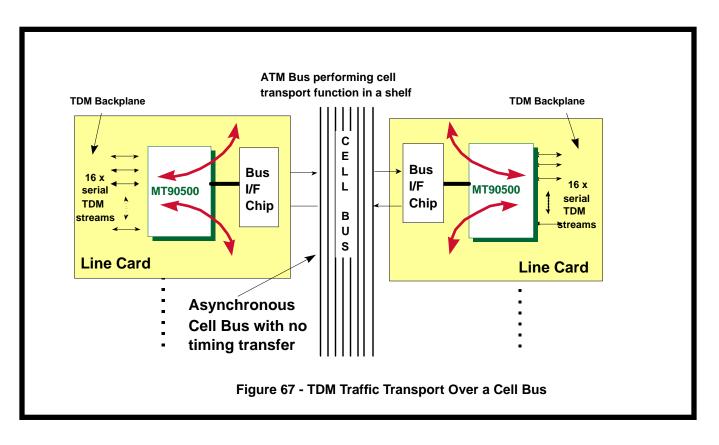

- TDM traffic transfer over an asynchronous cell

bus

- Systems requiring Nx64 over CBR-AAL5.

## **Description**

The MT90500 Multi-Channel AAL1 SAR is a highly integrated solution which allows systems based on a telecom bus to be interfaced to ATM networks using ATM Adaptation Layer 1 (AAL1), ATM Adaptation Layer 5 (AAL5) and ATM Adaptation Layer 0 (AAL0). The MT90500 can be connected directly to a ST-BUS time division multiplexed (TDM) backplane containing up to 1024 full duplex 64kbps channels. Up to 1024 bi-directional ATM VC connections can be simultaneously processed by the MT90500 AAL1 SAR device.

On the synchronous TDM bus side, the MT90500 device interfaces with sixteen bidirectional ST-BUS serial links operating at 2.048, 4.096 or 8.192 Mbps. TDM bus compatibility with MVIP-90, H-MVIP, and SCSA interfaces is also provided.

On the ATM interface side, the MT90500 device meets the ATM Forum standard UTOPIA Bus Level 1. This supports connection to a range of standard physical layer (PHY) transceivers.

The MT90500 provides a built-in UTOPIA multiplexer which allows external ATM cells to be multiplexed with internally-generated cells in the transmit direction. This feature can be used to connect another MT90500 (to expand the TDM bandwidth of the system to 4096 TDM channels), or to connect an external AAL5 SAR (to multiplex non-CBR ATM cell traffic with the MT90500 CBR stream).

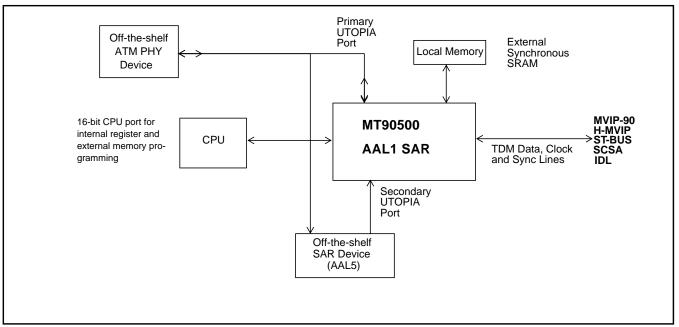

Figure B - MT90500 Device Application Block Diagram

# **Table of Contents**

| 1. | Introduction                                                  |      |

|----|---------------------------------------------------------------|------|

|    | 1.1 Functional Overview                                       |      |

|    | 1.2 Reference Documents                                       |      |

|    | 1.3 ATM Glossary                                              | . 13 |

| 2. | Features                                                      | . 15 |

|    | 2.1 General                                                   |      |

|    | 2.2 Serial TDM Bus                                            |      |

|    | 2.3 CBR ATM Cell Processor                                    |      |

|    | 2.4 External Memory Interface                                 |      |

|    | 2.5 UTOPIA Interface and Multiplexer                          |      |

|    | 2.6 Microprocessor Interface                                  |      |

|    | 2.7 Miscellaneous                                             |      |

|    | 2.8 Interrupts                                                | . 17 |

|    | 2.8.1 Module Level Interrupts                                 | . 17 |

|    | 2.8.2 TX_SAR Interrupts                                       | . 17 |

|    | 2.8.3 RX_SAR Interrupts                                       | . 17 |

|    | 2.8.4 UTOPIA Interrupts                                       | . 17 |

|    | 2.8.5 TDM Interrupts                                          | . 17 |

|    | 2.8.6 Timing Module Interrupts                                | . 18 |

|    | 2.9 Statistics                                                |      |

|    | 2.9.1 RX_SAR Statistics                                       | . 18 |

|    | 2.9.2 TDM Statistics                                          |      |

|    | 2.9.3 Timing Recovery Statistics                              | . 18 |

| 3. | Pin Descriptions                                              | . 19 |

| 4. | Functional Description                                        | . 28 |

|    | 4.1 TDM Module                                                |      |

|    | 4.1.1 TDM Clock Logic                                         |      |

|    | 4.1.1.1 TDM Timing Modes                                      |      |

|    | 4.1.1.2 REF8KCLK Selection Logic                              |      |

|    | 4.1.1.3 Main TDM Bus Timing and Clock Generation Logic        |      |

|    | 4.1.1.4 TDM Clock Drivers                                     |      |

|    | 4.1.1.5 Clock Failure Detection                               |      |

|    | 4.1.2 TDM Interface Operation                                 | . 32 |

|    | 4.1.2.1 Main TDM Bus Operation                                |      |

|    | 4.1.2.2 TDM Loopback                                          | . 32 |

|    | 4.1.2.3 Per-channel Output Enable Feature                     | . 32 |

|    | 4.1.2.4 Local Bus Operation                                   | . 32 |

|    | 4.1.2.5 Local Bus Data Transfer Process                       | . 33 |

|    | 4.1.3 TDM Data to External Memory Process                     |      |

|    | 4.1.3.1 General                                               |      |

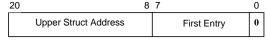

|    | 4.1.3.2 Transmit Circular Buffer Control Structures           |      |

|    | 4.1.3.3 Transmit Circular Buffers                             |      |

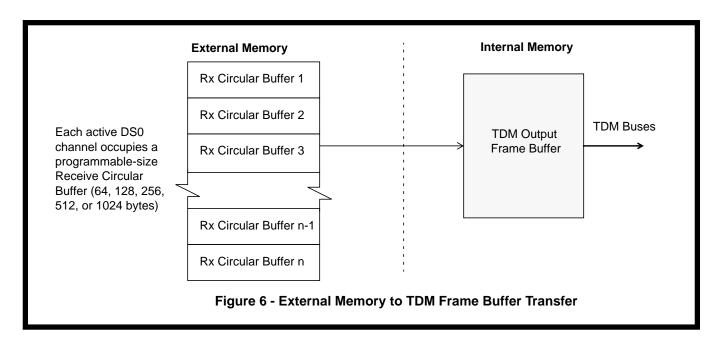

|    | 4.1.4 External Memory to TDM Data Output Process              |      |

|    | 4.1.4.1 General                                               |      |

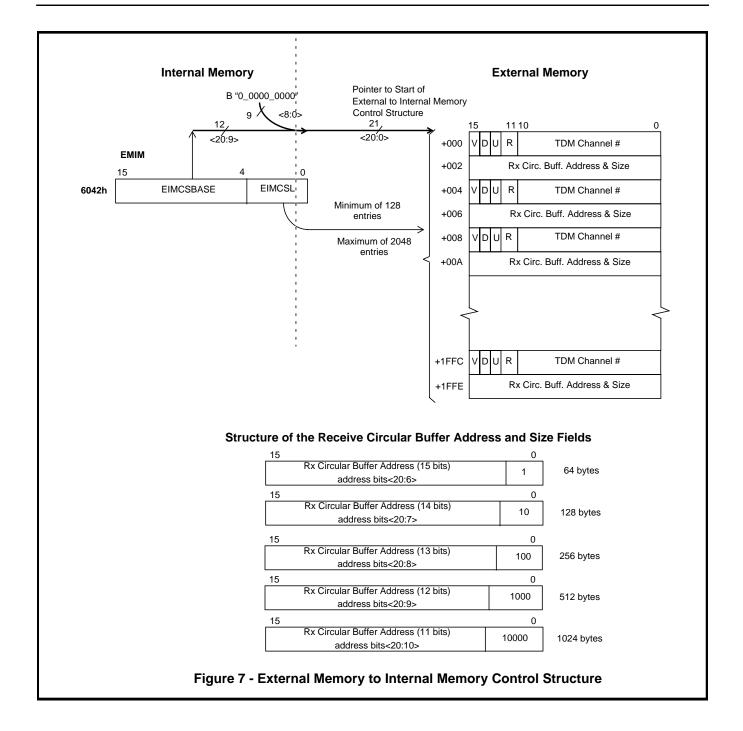

|    | 4.1.4.2 External Memory to Internal Memory Control Structures |      |

|    | 4.2 External Memory Controller                                |      |

|    | 4.3 TX_SAR Module                                             |      |

|    | 4.3.1 TX_SAR Overview                                         |      |

|    | 4.3.1.1 General                                               |      |

|    | 4.3.1.2 Supported ATM Cell Formats.                           |      |

|    | 4.3.1.3 Transmit Event Scheduler Overview                     |      |

|    | 4.3.1.3.1 Introduction                                        |      |

|    | 4.3.1.3.2 Fixed TDM Payload Schedulers                        |      |

|    | 4.3.1.3.3 AAL1 Long/Short Schedulers                          |      |

|    | 4.3.1.3.4 Other Considerations                                | . 41 |

# MT90500

|    | 4.3.2 TX_SAR Process                                          | 48  |

|----|---------------------------------------------------------------|-----|

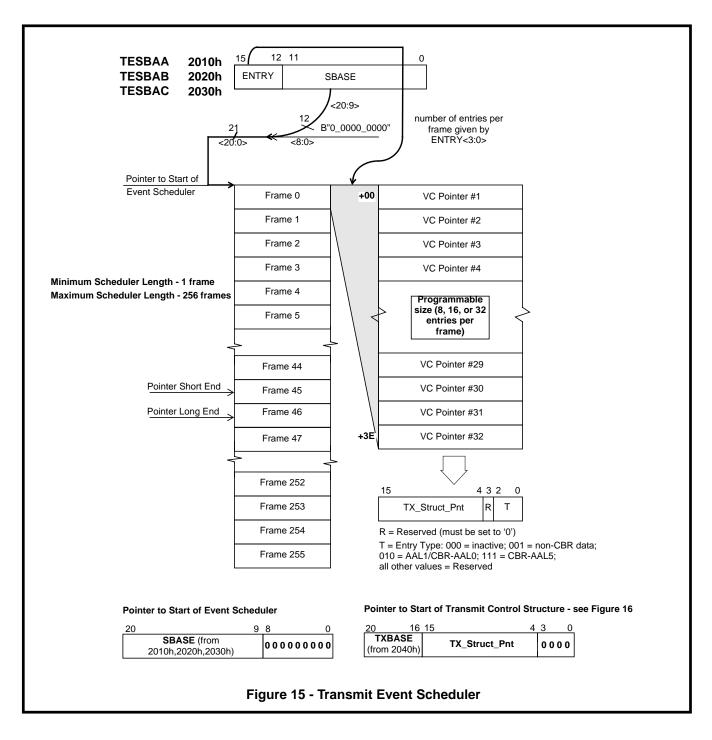

|    | 4.3.2.1 Transmit Event Schedulers                             | 48  |

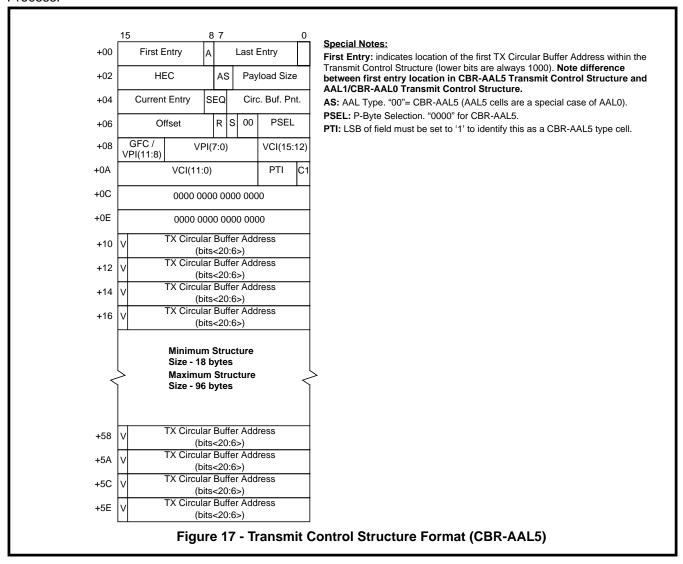

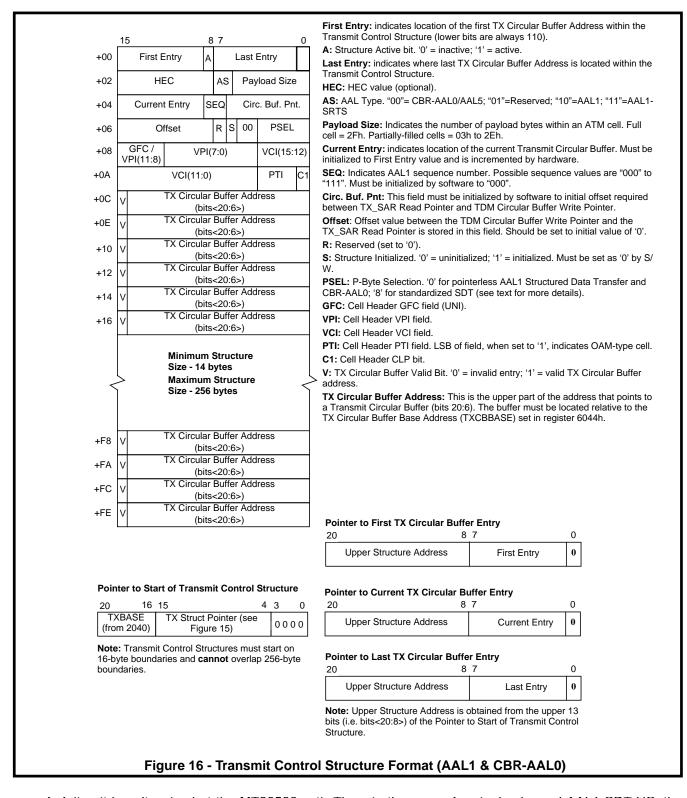

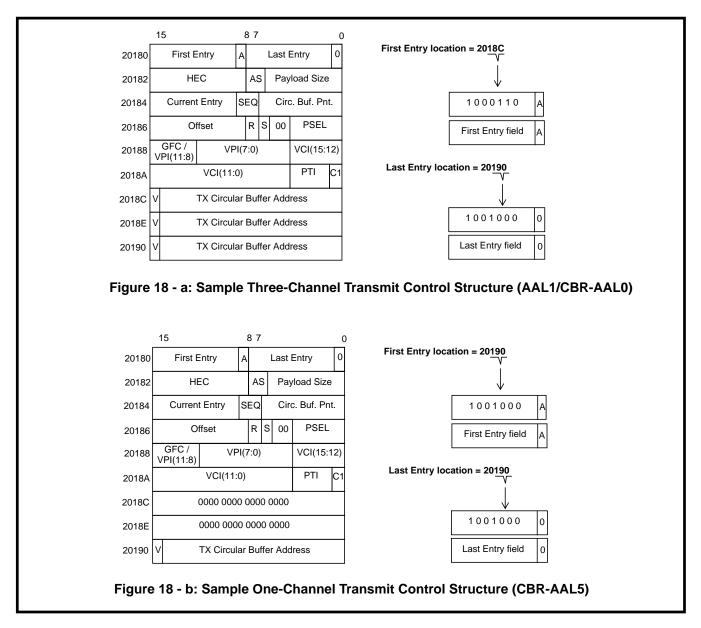

|    | 4.3.2.2 Transmit Control Structures                           | 50  |

|    | 4.3.3 Non-CBR Data Cell Transmission Capability               | 55  |

|    | 4.4 The RX_SAR Module                                         |     |

|    | 4.4.1 RX SAR Overview                                         |     |

|    | 4.4.2 RX SAR Process                                          | 57  |

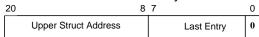

|    | 4.4.2.1 RX_SAR Control Structures                             | 58  |

|    | 4.4.2.2 RX_SAR Error Counter and Interrupt Sources            |     |

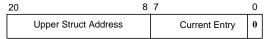

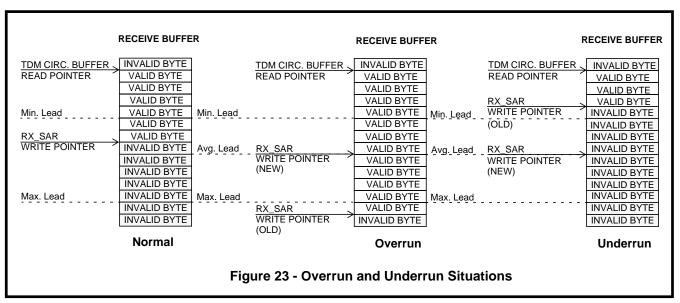

|    | 4.4.2.3 Receive Overruns and Underruns.                       |     |

|    | 4.4.2.4 Lost Cell Handling                                    |     |

|    | 4.5 UTOPIA Module                                             |     |

|    | 4.5.1 UTOPIA Overview                                         |     |

|    | 4.5.2 Cell Transmission and Mux Process                       | 63  |

|    | 4.5.3 Receive Cell Selection Process                          |     |

|    | 4.5.4 Non-CBR Data Cell Reception Ability                     |     |

|    | 4.6 Clock Recovery from ATM Link                              |     |

|    | 4.6.1 Adaptive Clock Recovery Sub-Module                      |     |

|    | 4.6.2 SRTS Clock Recovery Description                         |     |

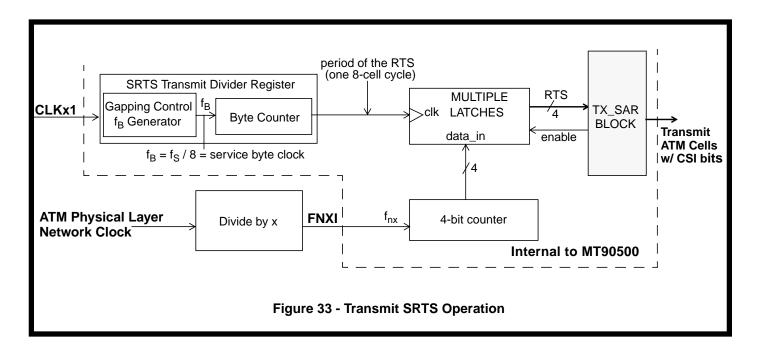

|    | 4.6.2.1 Transmit SRTS Operation                               |     |

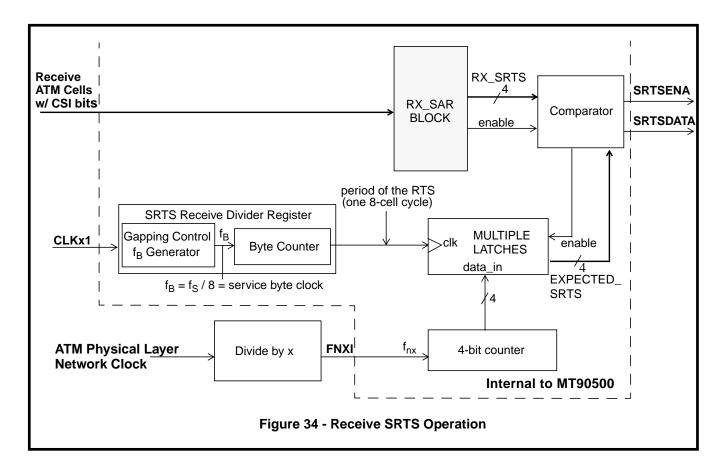

|    | 4.6.2.2 Receive SRTS Operation                                |     |

|    | 4.7 Microprocessor Interface                                  |     |

|    | 4.7.1 General                                                 |     |

|    | 4.7.2 A Programming Example - How to Set Up a VC              |     |

|    | 4.7.3 Microprocessor Access and Device Reset                  |     |

|    | 4.8 Test Interface                                            |     |

|    | 4.8.1 Test Access Port                                        |     |

|    | 4.8.2 JTAG ID                                                 | 79  |

|    | 4.8.3 Boundary Scan Instructions                              |     |

|    | 4.8.4 BSDL                                                    | 79  |

| 5  | Register Map                                                  | 80  |

| ٠. | 5.1 Register Overview                                         |     |

|    | 5.1.1 General                                                 |     |

|    | 5.1.2 Interrupt Structure.                                    |     |

|    | 5.1.3 Register Summary                                        |     |

|    | 5.2 Register Description                                      |     |

|    | 5.2.1 Microprocessor Interface Registers                      |     |

|    | 5.2.2 TX_SAR Registers                                        |     |

|    | 5.2.3 RX_SAR Registers                                        |     |

|    | 5.2.4 UTOPIA Registers                                        |     |

|    | 5.2.5 TDM Interface and Clock Interface Registers             |     |

|    | 5.2.6 TDM Time Slot Control                                   |     |

| 6  | Electrical Specification                                      |     |

| υ. | 6.1 DC Characteristics                                        |     |

|    | 6.2 AC Characteristics                                        |     |

|    | 6.2.1 Main TDM Bus                                            |     |

|    | 6.2.2 Local TDM Bus                                           |     |

|    | 6.2.3 CPU Interface - Accessing Registers and External Memory |     |

|    | 6.2.4 Interface with External Memory                          |     |

|    | 6.2.5 UTOPIA Interfaces                                       |     |

|    | 6.2.5.1 Primary UTOPIA Interface                              |     |

|    | 6.2.5.2 Secondary UTOPIA Interface                            |     |

|    | 6.2.6 SRTS User Interface                                     |     |

|    | 6.2.7 Message Channel Interface                               |     |

|    | 6.2.8 Boundary-Scan Test Access Interface                     |     |

| _  | ·                                                             |     |

| 1. | Applications                                                  |     |

|    | 7.1 Board Level Applications                                  | 13/ |

# MT90500

|    | 7.2 System Level Applications                         |       |

|----|-------------------------------------------------------|-------|

|    | 7.3 TDM Clock Recovery Applications                   |       |

|    | 7.3.2 SRTS Clock Recovery Considerations              |       |

|    | 7.3.3 Free-running Clocks                             |       |

|    | 7.4 External Memory Space and Bandwidth Calculations  | . 147 |

|    | 7.4.1 External Memory Space Requirements              |       |

|    | 7.4.2 Memory Structure Summary                        | . 149 |

|    | 7.4.3 External Memory Bandwidth Requirements          | . 151 |

|    | 7.5 CBR Throughput Delay                              | . 153 |

|    | 7.6 Other Applications                                | . 154 |

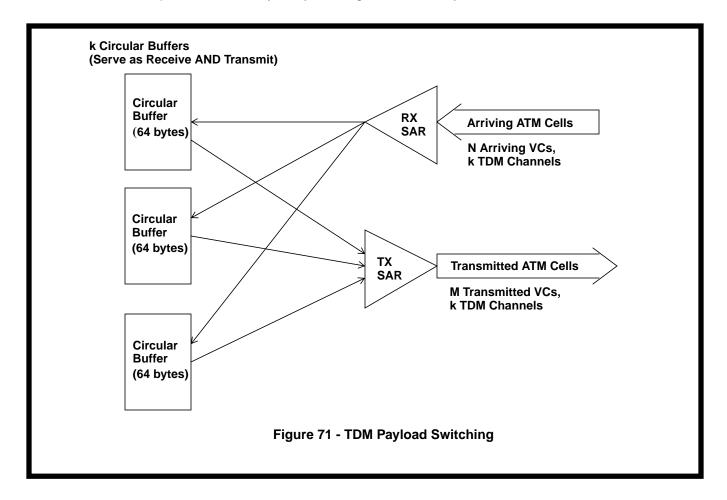

|    | 7.6.1 Payload Switching                               |       |

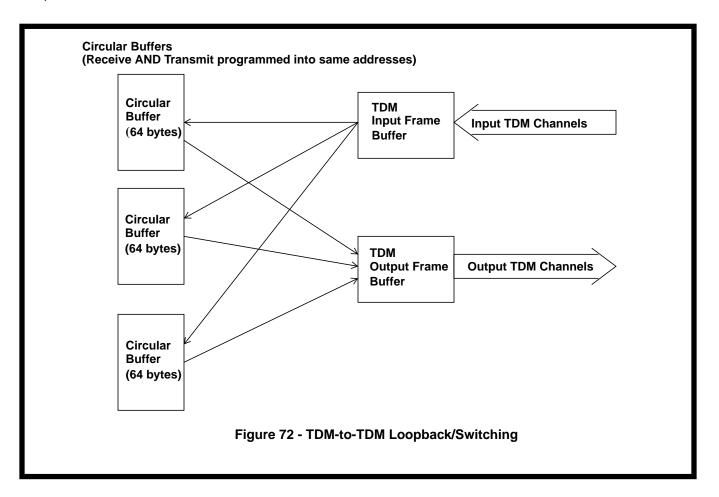

|    | 7.6.2 TDM Switching and Loopback                      | . 154 |

|    | 7.6.3 DS0 Trunking, or Dynamic TDM channel re-mapping | . 155 |

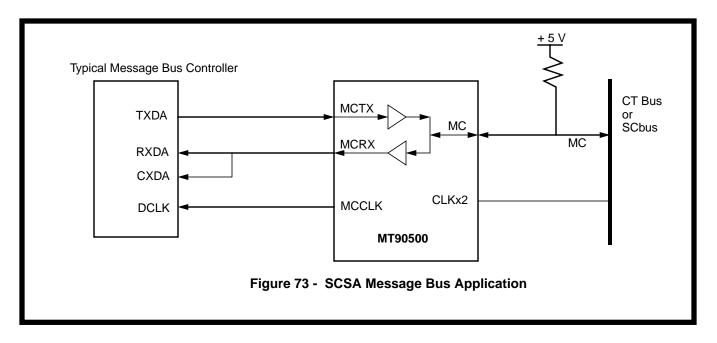

|    | 7.6.4 SCSA Message Channel                            |       |

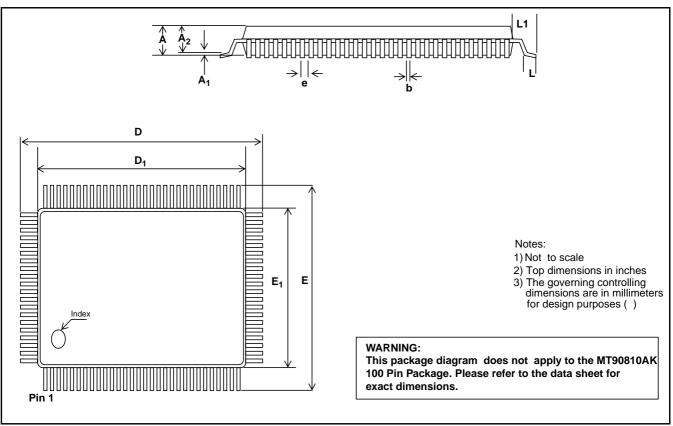

| 3. | Physical Specification                                | . 157 |

# **List of Figures**

| Figure 1 -  | MT90500 Block Diagram                                                    | 12   |

|-------------|--------------------------------------------------------------------------|------|

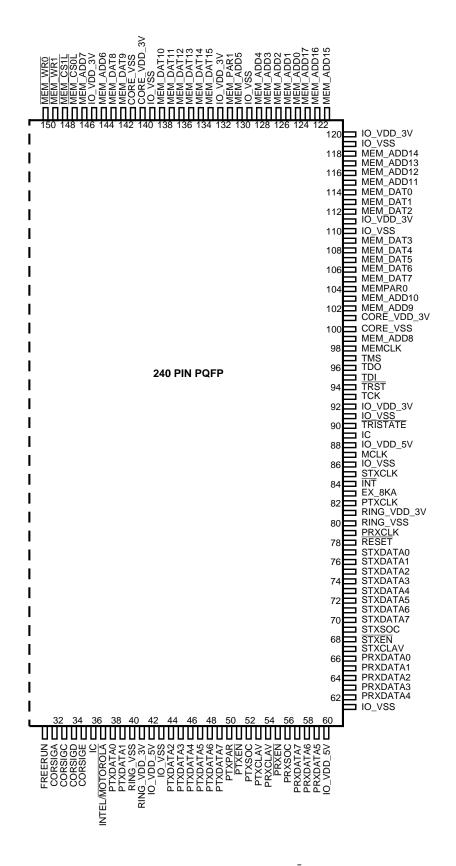

| Figure 2.   | Pin Connections                                                          |      |

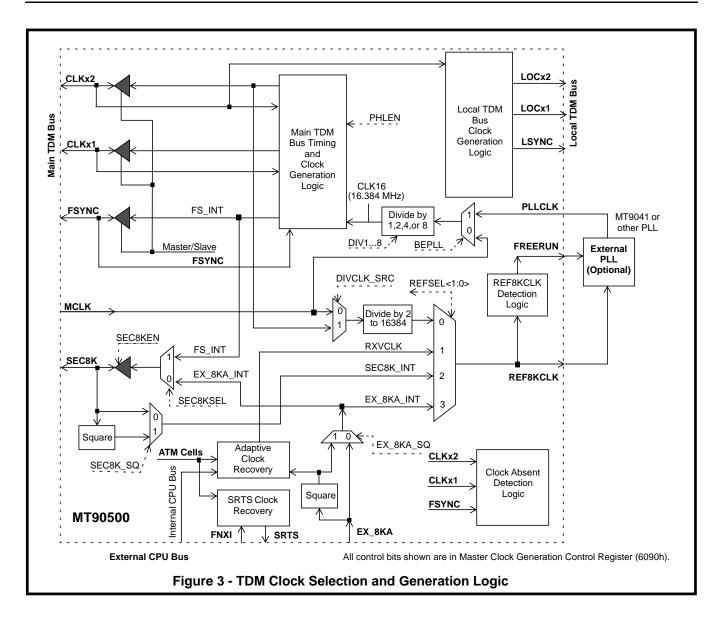

| Figure 3 -  | TDM Clock Selection and Generation Logic                                 | 29   |

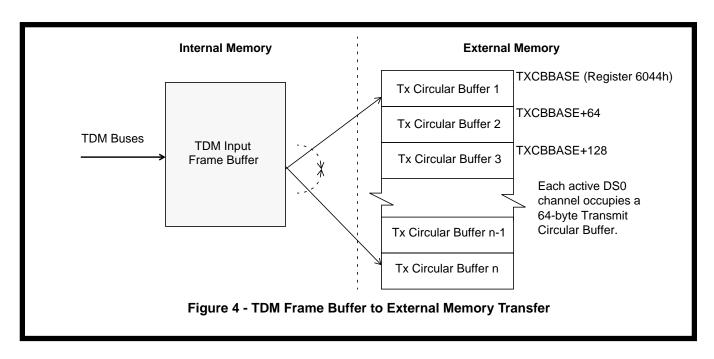

| Figure 4 -  | TDM Frame Buffer to External Memory Transfer                             | 33   |

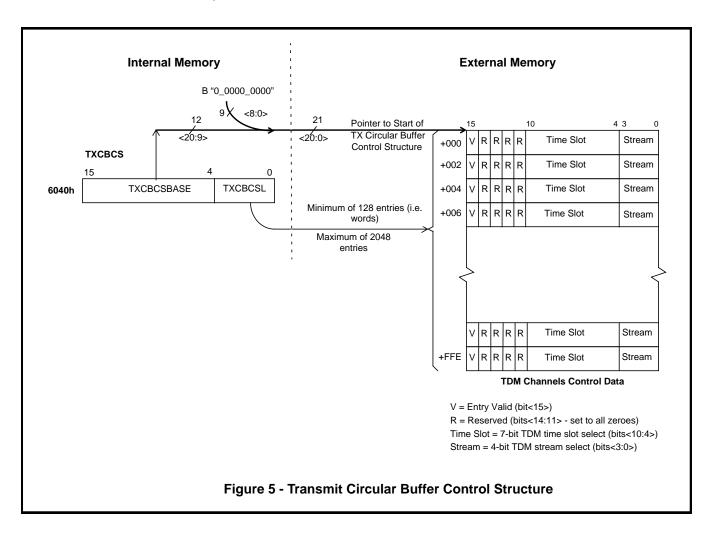

| Figure 5 -  | Transmit Circular Buffer Control Structure                               |      |

| Figure 6 -  | External Memory to TDM Frame Buffer Transfer                             |      |

| Figure 7 -  | External Memory to Internal Memory Control Structure                     | 37   |

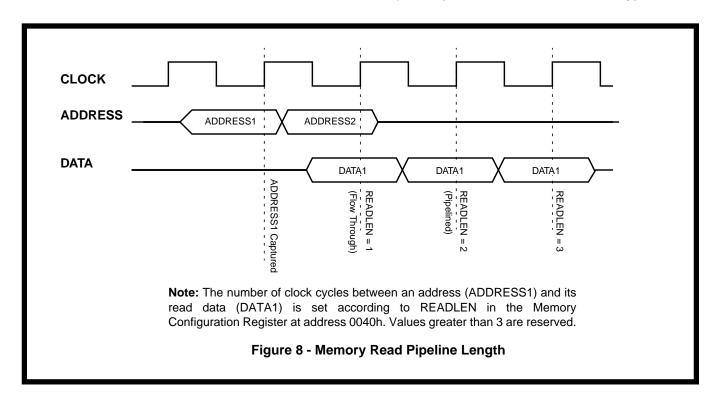

| Figure 8 -  | Memory Read Pipeline Length                                              | 38   |

| Figure 9 -  | Logical Byte Address vs. Physical Address and Memory Banks               | 39   |

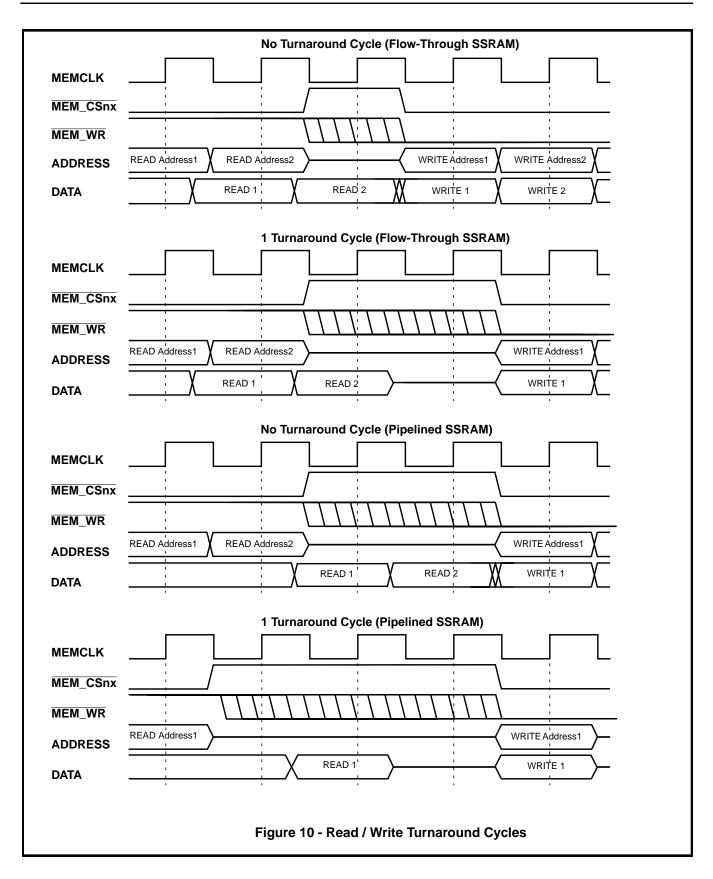

| Figure 10 - | Read / Write Turnaround Cycles                                           | 40   |

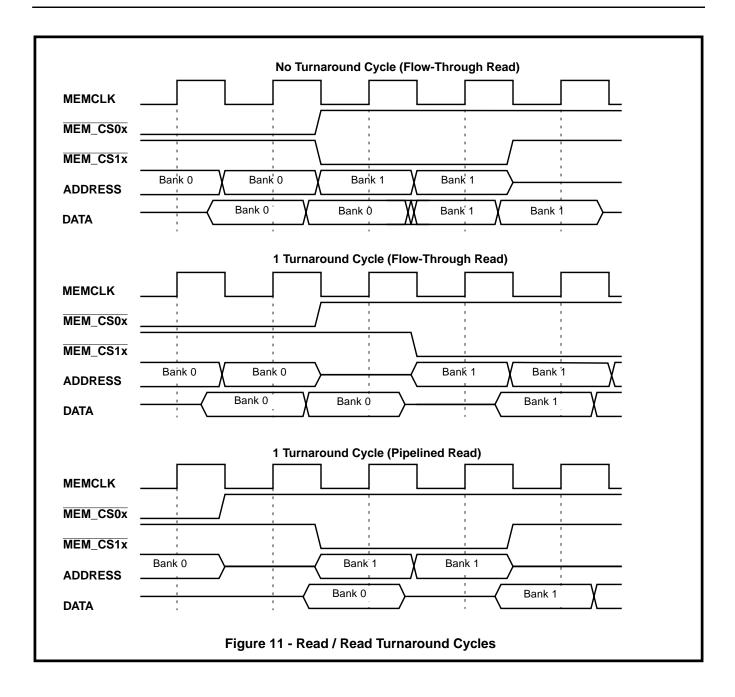

| Figure 11 - | Read / Read Turnaround Cycles                                            | 41   |

| Figure 11 - | Read / Write turnaround Cycles                                           | 41   |

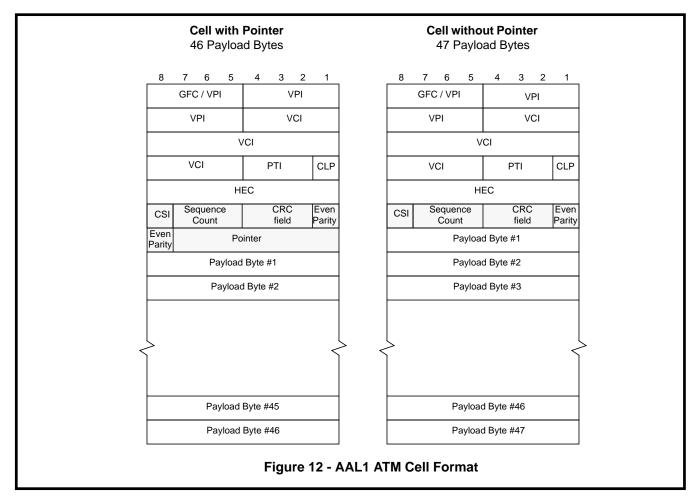

| Figure 12 - | AAL1 ATM Cell Format                                                     | 42   |

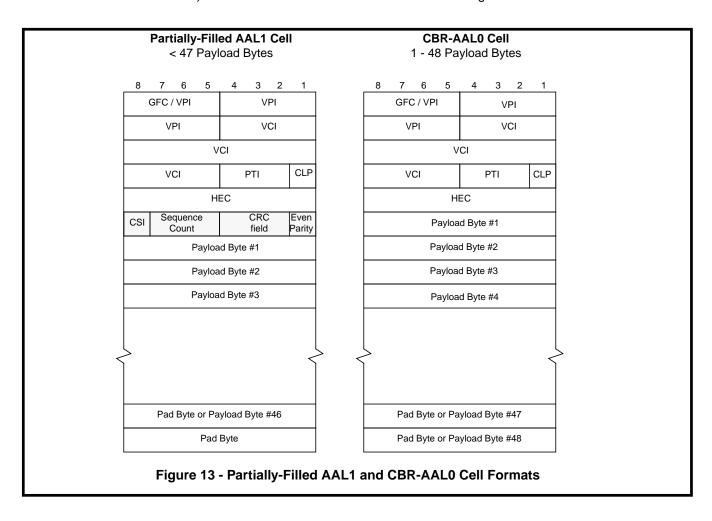

| Figure 13 - | Partially-Filled AAL1 and CBR-AAL0 Cell Formats                          | 43   |

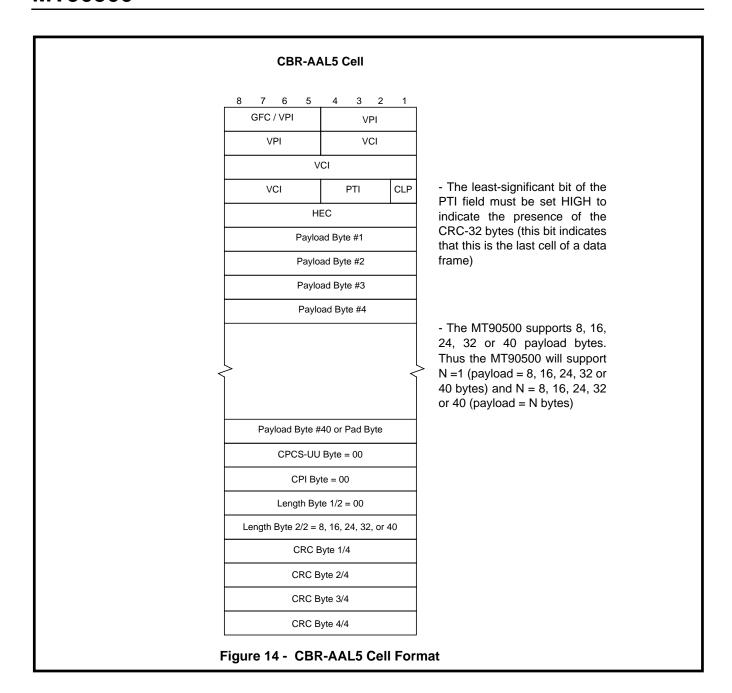

| Figure 14 - | CBR-AAL5 Cell Format                                                     | 44   |

| Figure 15 - | Transmit Event Scheduler                                                 | 49   |

| Figure 17 - | Transmit Control Structure Format (CBR-AAL5)                             | 50   |

| Figure 16 - | Transmit Control Structure Format (AAL1 & CBR-AAL0)                      | 51   |

| Figure 18 - | a: Sample Three-Channel Transmit Control Structure (AAL1/CBR-AAL0)       | 53   |

| Figure 18 - | b: Sample One-Channel Transmit Control Structure (CBR-AAL5)              | 53   |

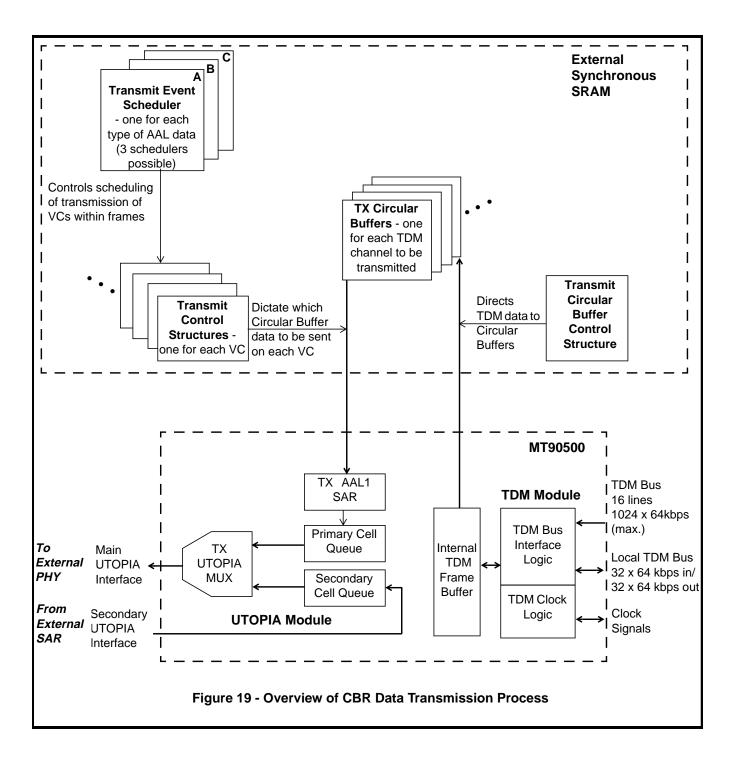

|             | Overview of CBR Data Transmission Process                                |      |

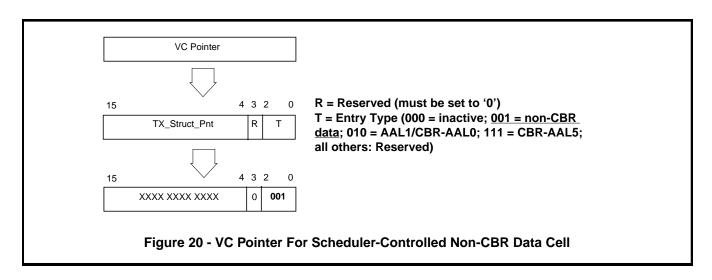

| Figure 20 - | VC Pointer For Scheduler-Controlled Non-CBR Data Cell                    | 55   |

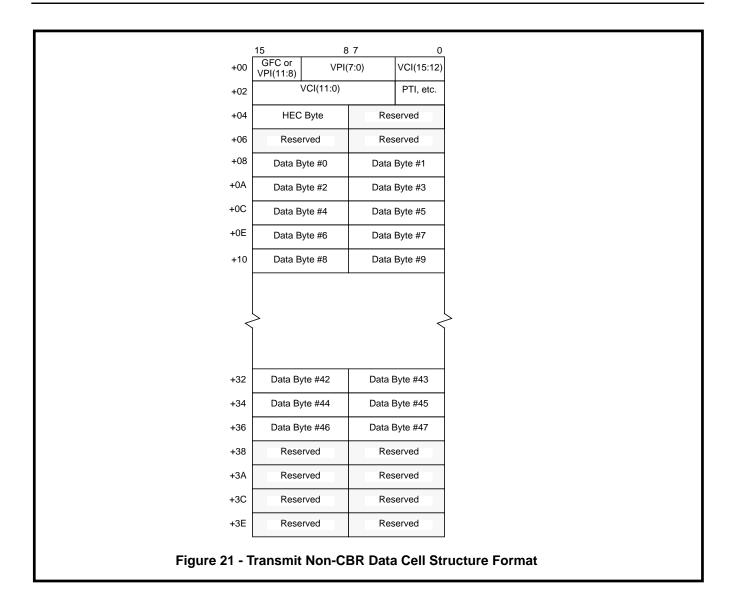

|             | Transmit Non-CBR Data Cell Structure Format                              |      |

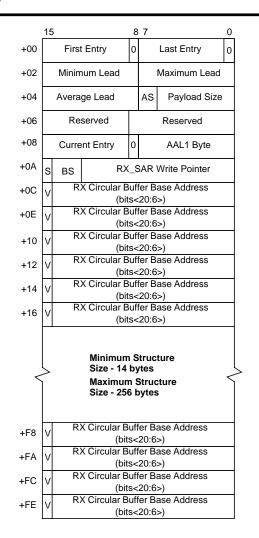

| Figure 22 - | RX_SAR Control Structure                                                 | 58   |

| Figure 23 - | Overrun and Underrun Situations                                          | 60   |

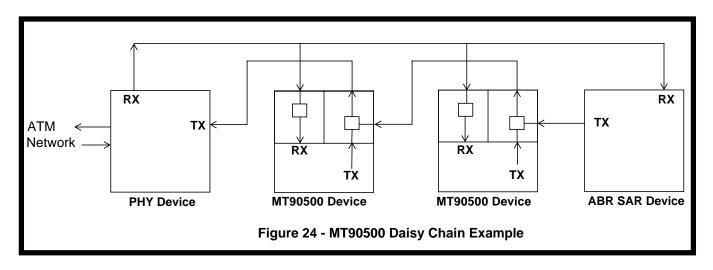

| Figure 24 - | MT90500 Daisy Chain Example                                              | 62   |

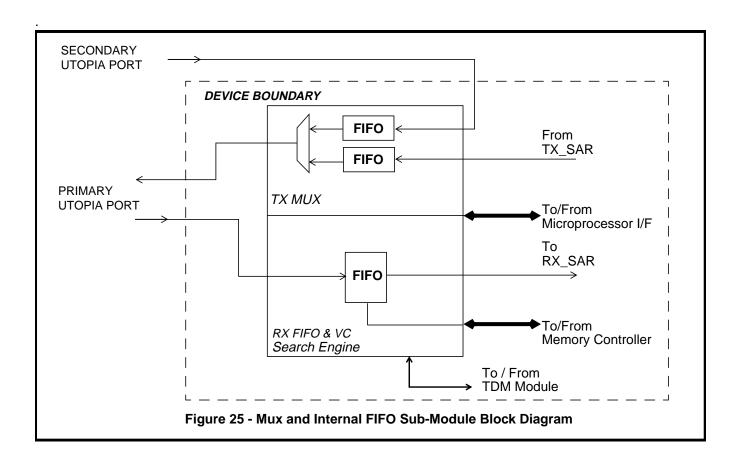

| -           | Mux and Internal FIFO Sub-Module Block Diagram                           |      |

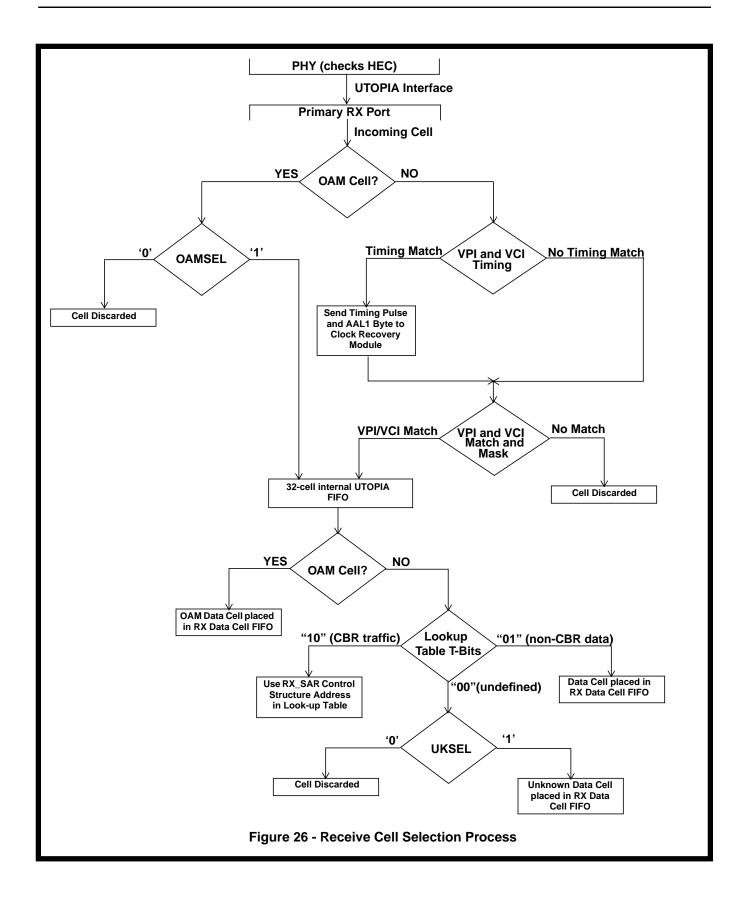

| Figure 26 - | Receive Cell Selection Process                                           | 65   |

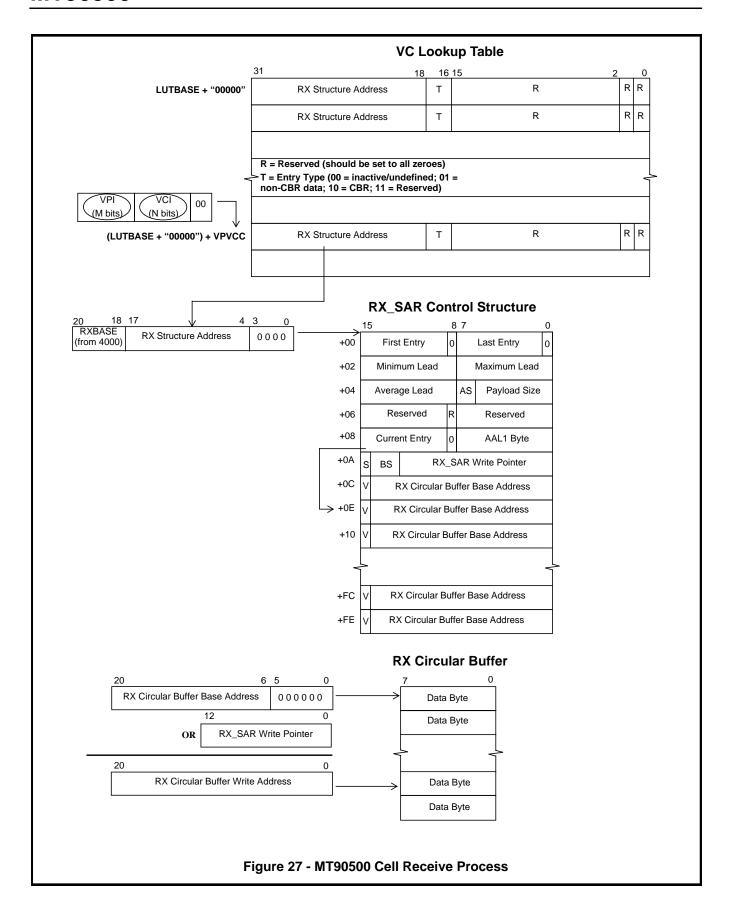

| Figure 27 - | MT90500 Cell Receive Process                                             | 66   |

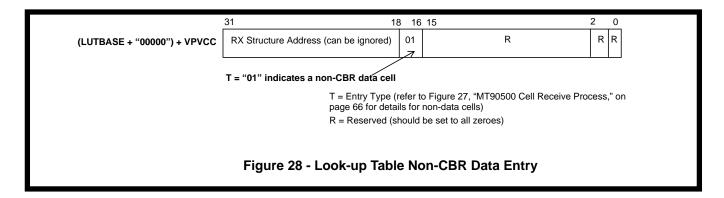

| •           | Look-up Table Non-CBR Data Entry                                         |      |

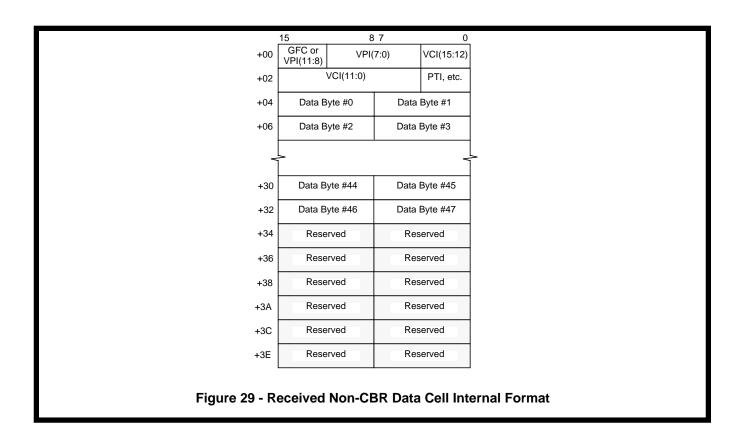

| Figure 29 - | Received Non-CBR Data Cell Internal Format                               | 68   |

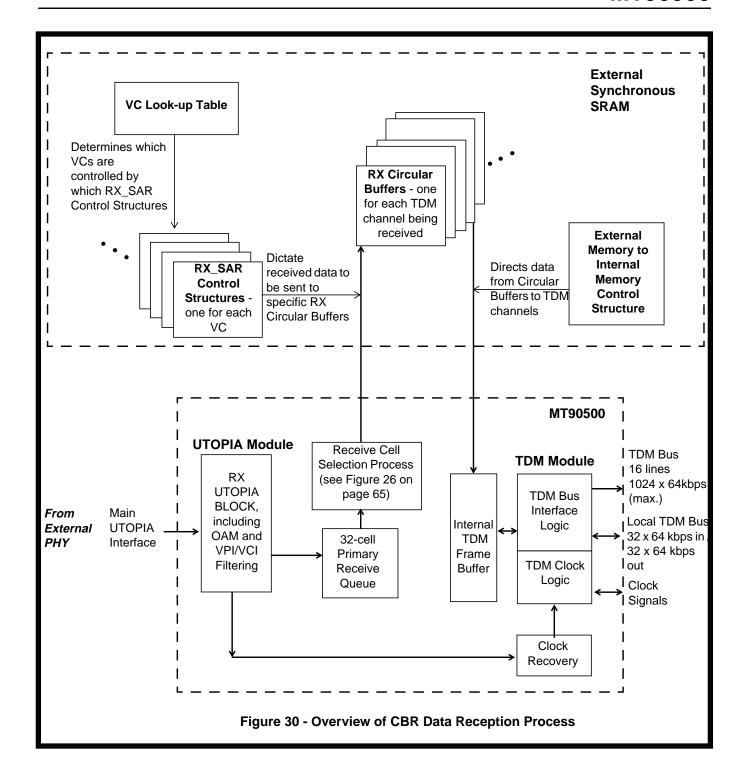

| -           | Overview of CBR Data Reception Process                                   |      |

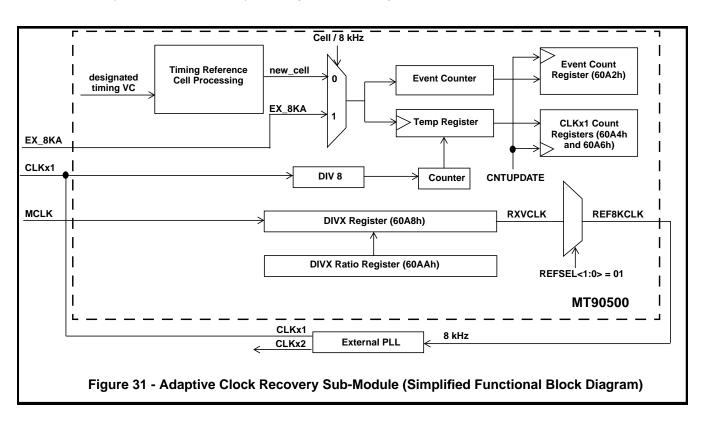

| Figure 31 - | Adaptive Clock Recovery Sub-Module (Simplified Functional Block Diagram) | 70   |

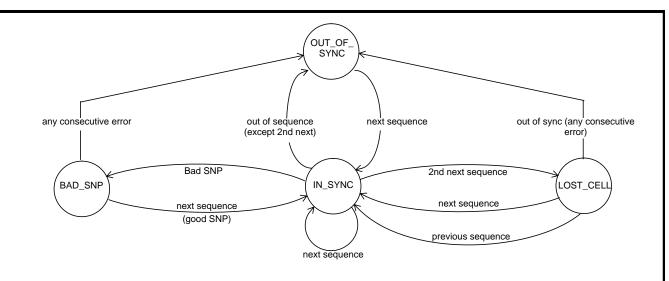

| Figure 32 - | Timing Reference Cell Processing State Machine                           | 71   |

| -           | Transmit SRTS Operation                                                  |      |

| -           | Receive SRTS Operation                                                   |      |

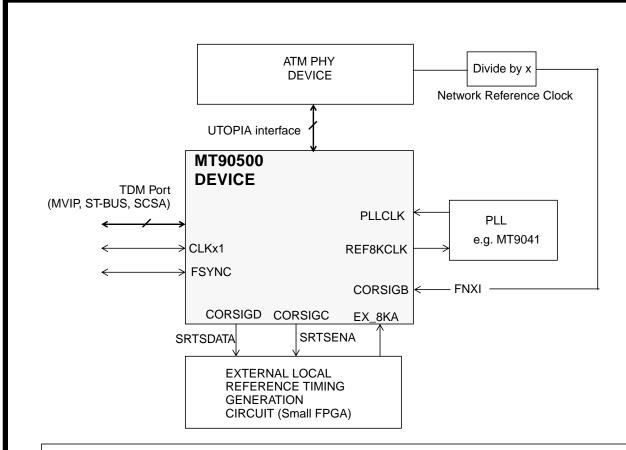

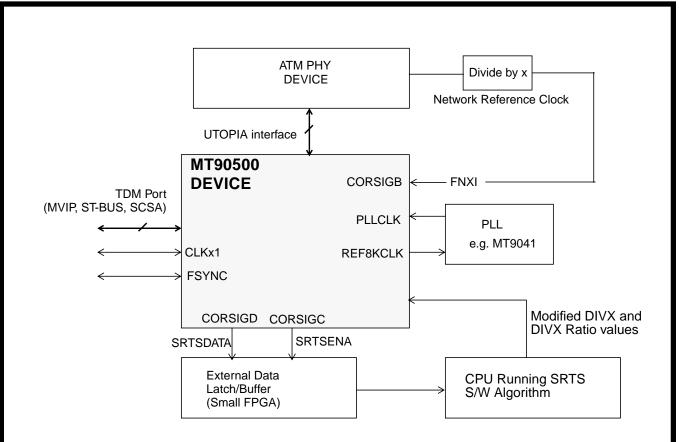

| Figure 35 - | Clock Recovery Using SRTS Method (Hardware)                              | 75   |

| •           | Clock Recovery Using SRTS Method (CPU)                                   |      |

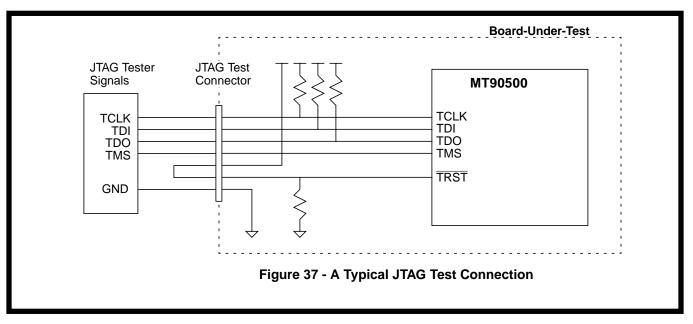

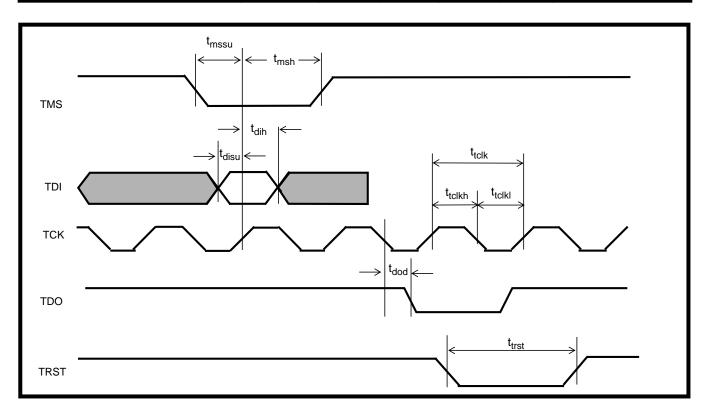

| Figure 37 - | A Typical JTAG Test Connection                                           | 79   |

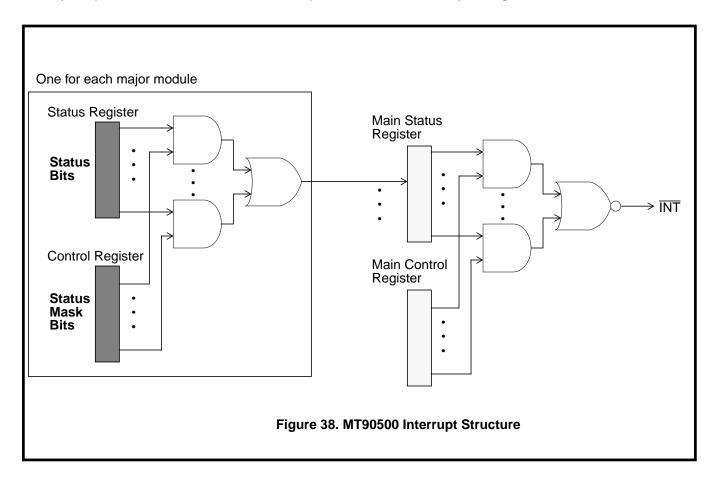

| -           | MT90500 Interrupt Structure                                              |      |

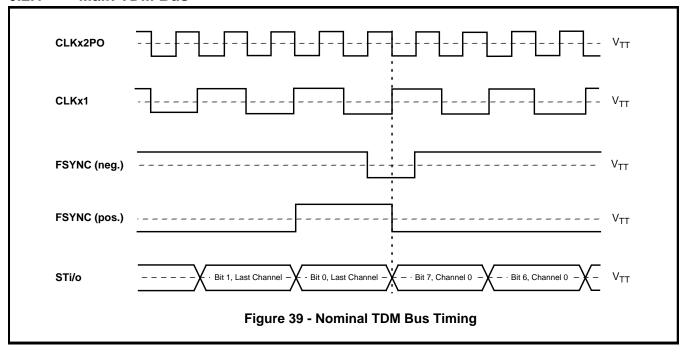

| -           | Nominal TDM Bus Timing                                                   |      |

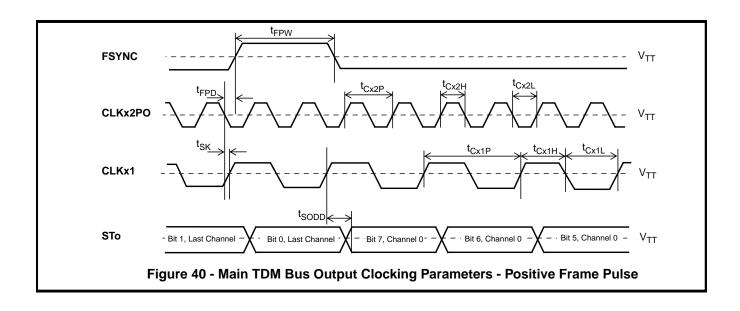

| Figure 40 - | Main TDM Bus Output Clocking Parameters - Positive Frame Pulse           | .115 |

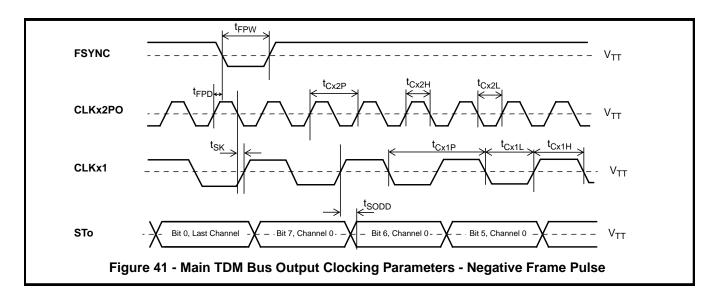

| •           | Main TDM Bus Output Clocking Parameters - Negative Frame Pulse           |      |

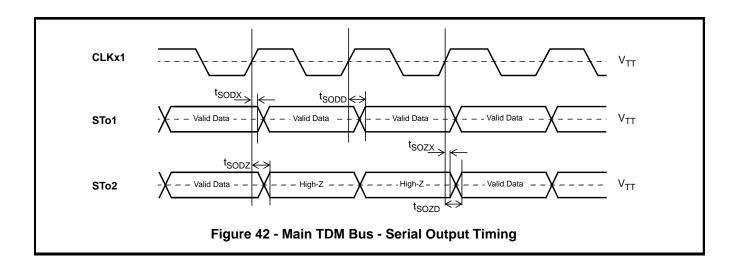

| -           | Main TDM Bus - Serial Output Timing                                      |      |

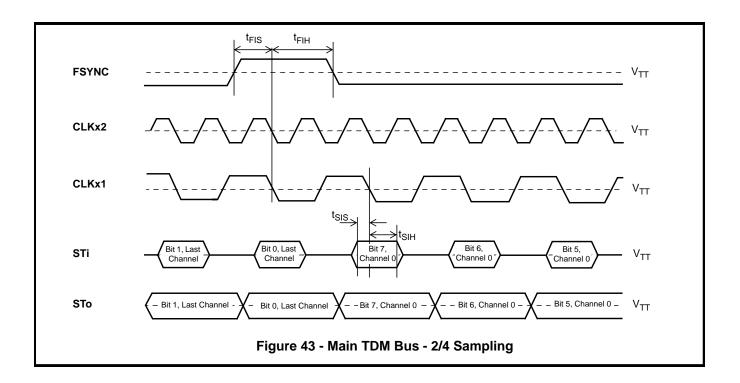

| •           | Main TDM Bus - 2/4 Sampling                                              |      |

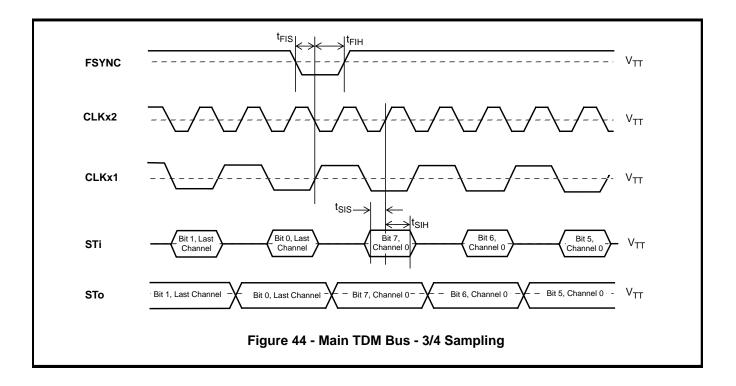

| •           | Main TDM Bus - 3/4 Sampling                                              |      |

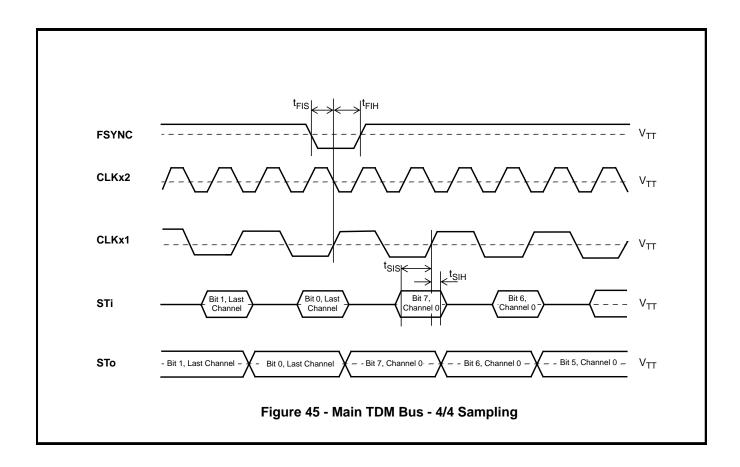

| -           | Main TDM Bus - 4/4 Sampling                                              |      |

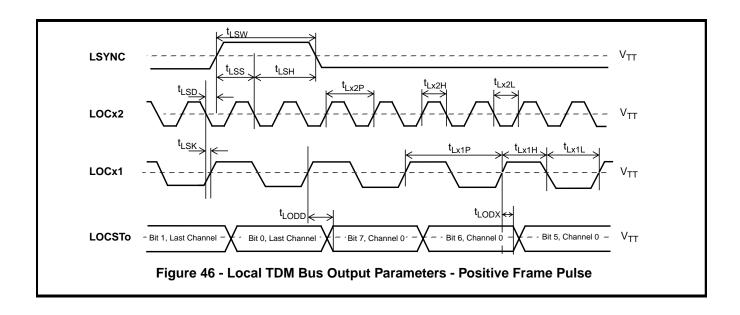

| Figure 46 - | Local TDM Bus Output Parameters - Positive Frame Pulse                   | .121 |

# MT90500

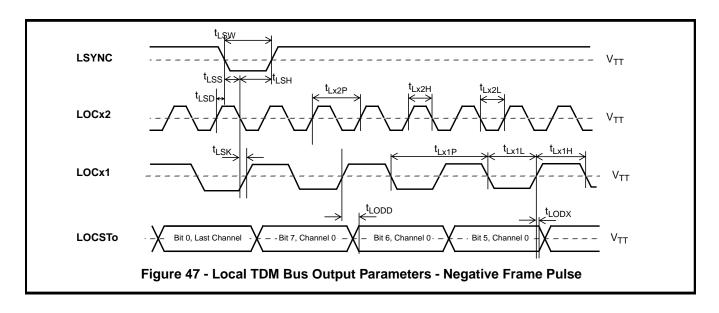

| Figure 47 - | Local TDM Bus Output Parameters - Negative Frame Pulse                 | 121 |

|-------------|------------------------------------------------------------------------|-----|

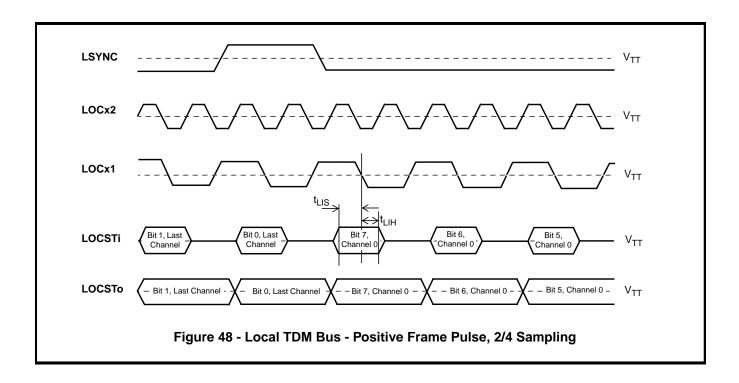

| Figure 48 - | Local TDM Bus - Positive Frame Pulse, 2/4 Sampling                     | 122 |

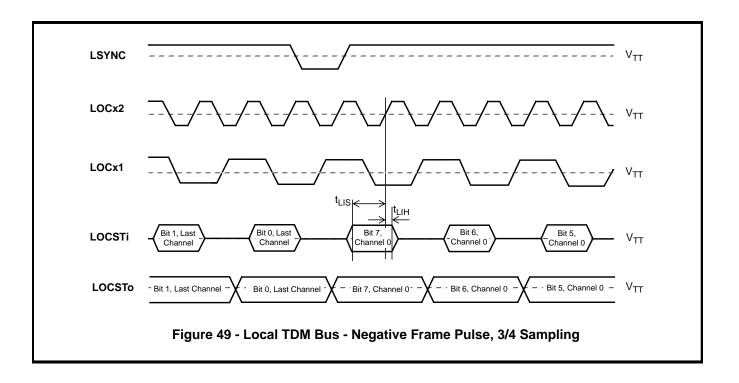

| Figure 49 - | Local TDM Bus - Negative Frame Pulse, 3/4 Sampling                     | 123 |

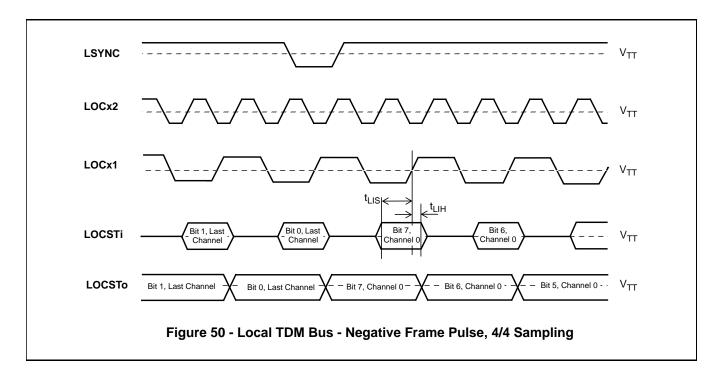

| Figure 50 - | Local TDM Bus - Negative Frame Pulse, 4/4 Sampling                     | 123 |

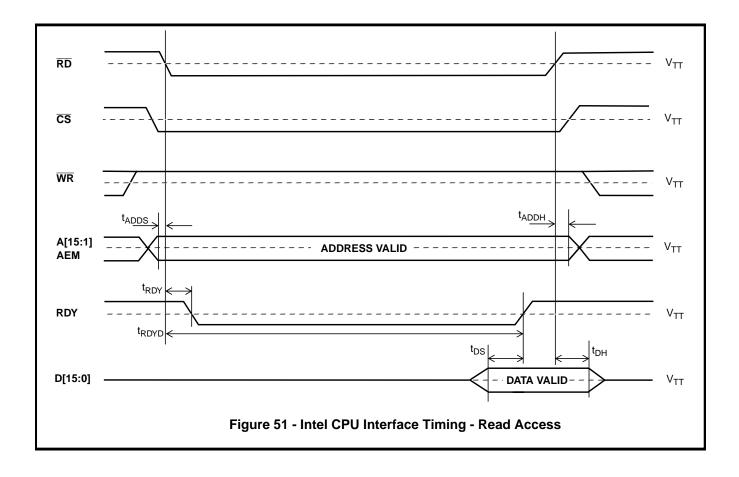

| Figure 51 - | Intel CPU Interface Timing - Read Access                               | 124 |

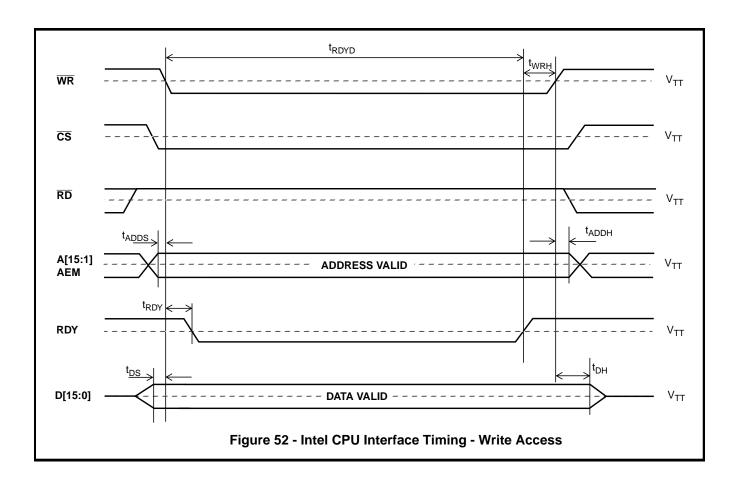

| Figure 52 - | Intel CPU Interface Timing - Write Access                              | 125 |

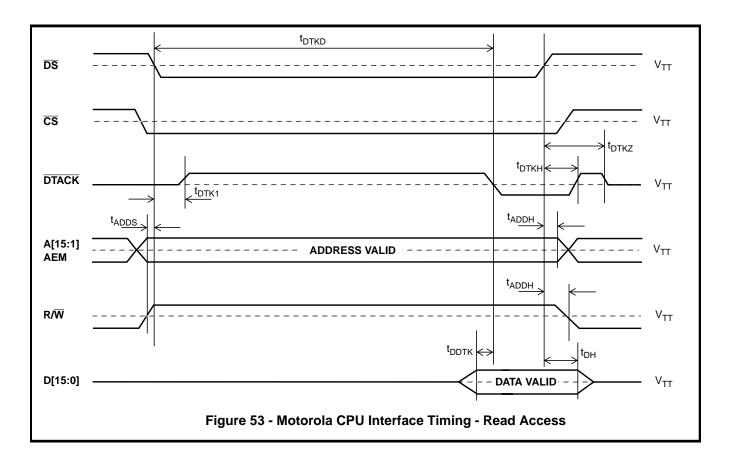

| Figure 53 - | Motorola CPU Interface Timing - Read Access                            | 126 |

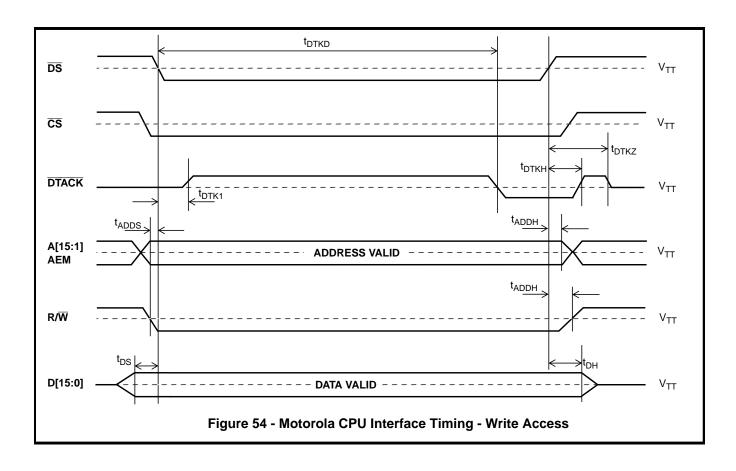

| Figure 54 - | Motorola CPU Interface Timing - Write Access                           | 127 |

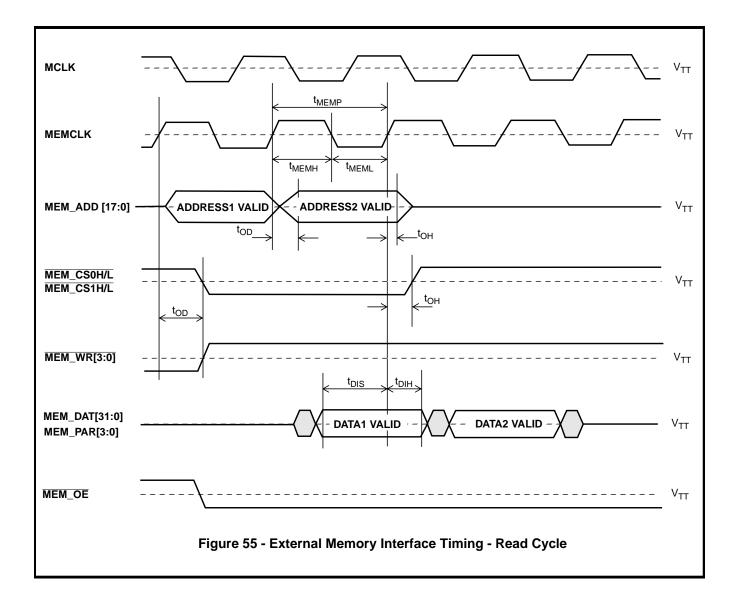

| Figure 55 - | External Memory Interface Timing - Read Cycle                          | 129 |

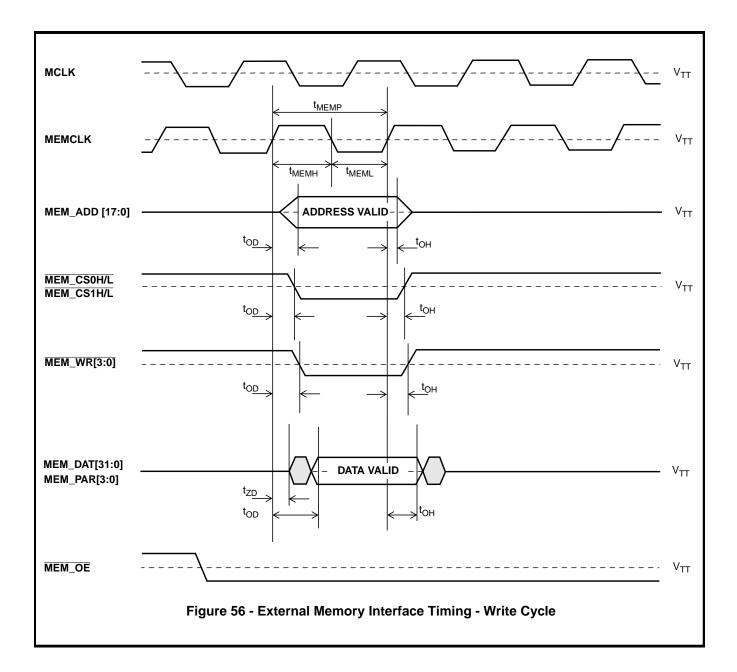

| Figure 56 - | External Memory Interface Timing - Write Cycle                         | 130 |

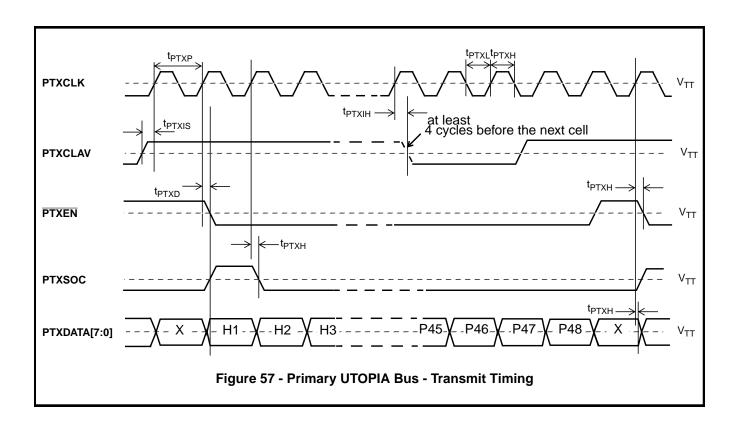

| Figure 57 - | Primary UTOPIA Bus - Transmit Timing                                   | 131 |

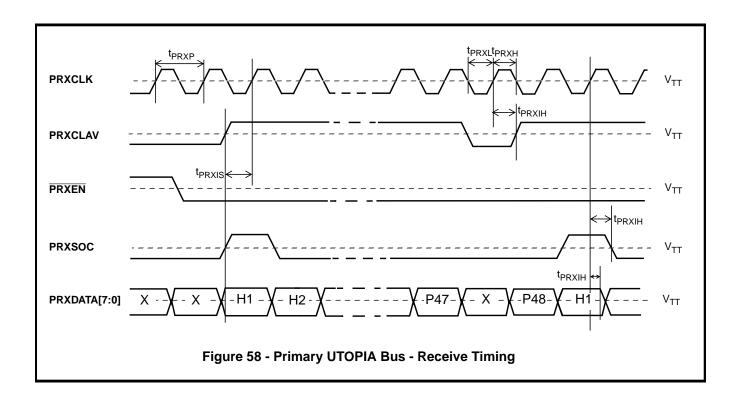

| Figure 58 - | Primary UTOPIA Bus - Receive Timing                                    | 132 |

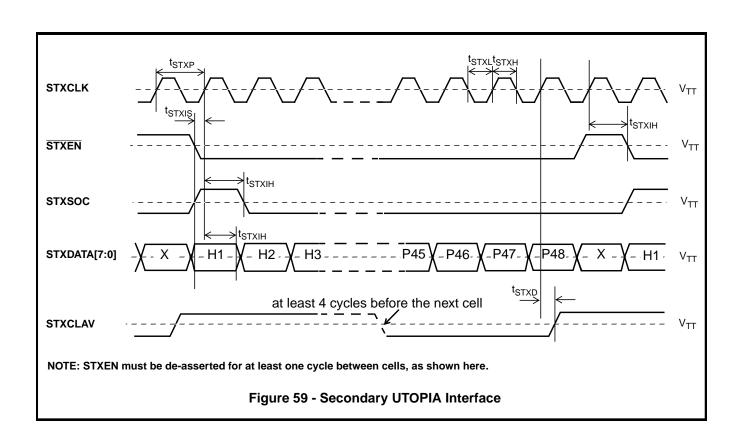

| •           | Secondary UTOPIA Interface                                             |     |

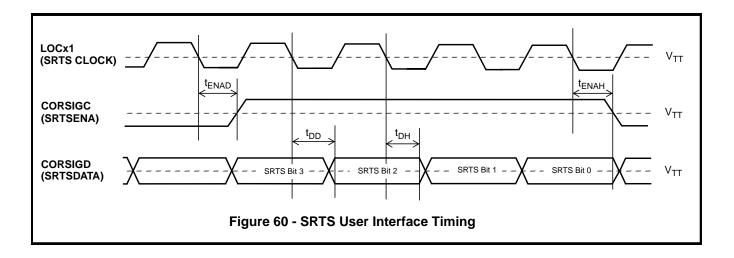

| Figure 60 - | SRTS User Interface Timing                                             | 134 |

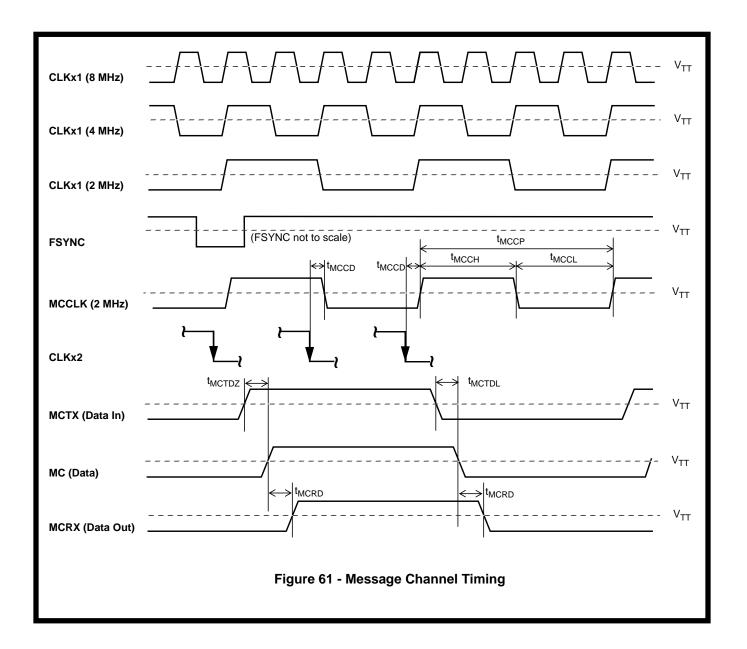

| Figure 61 - | Message Channel Timing                                                 | 135 |

| Figure 62 - | MT90500 Device Application Block Diagram                               | 137 |

| Figure 63 - | UTOPIA Bus Interconnections for Two MT90500s and an AAL5 SAR           | 139 |

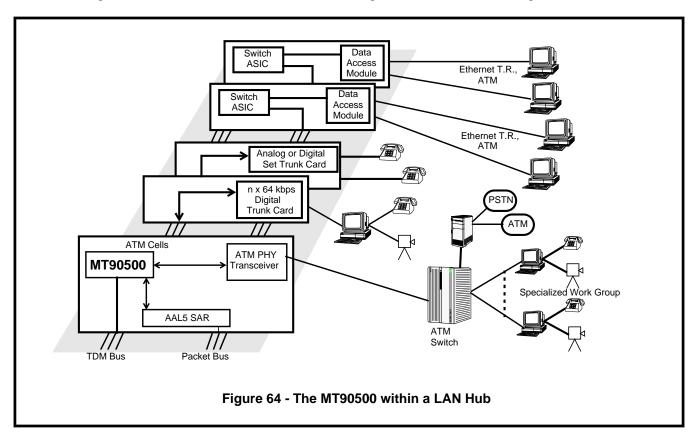

| Figure 64 - | The MT90500 within a LAN Hub                                           | 141 |

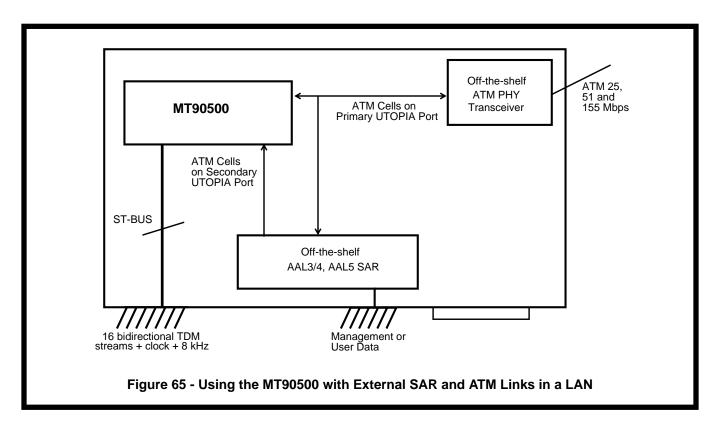

| Figure 65 - | Using the MT90500 with External SAR and ATM Links in a LAN Environment | 142 |

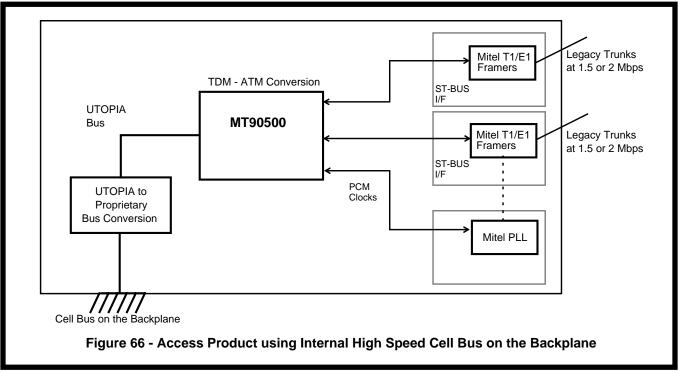

| Figure 66 - | Access Product using Internal High Speed Cell Bus on the Backplane     | 142 |

| -           | TDM Traffic Transport Over a Cell Bus                                  |     |

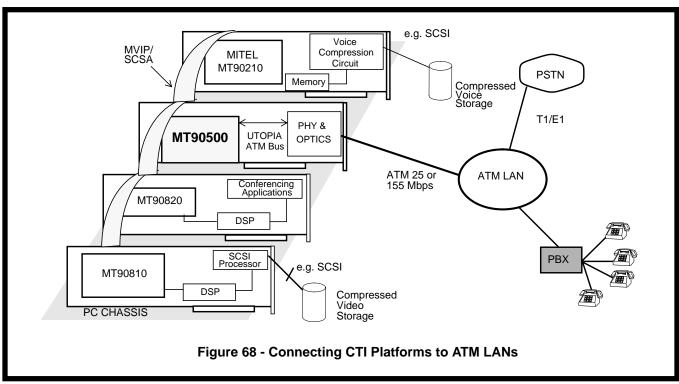

| Figure 68 - | Connecting CTI Platforms to ATM LANs                                   | 143 |

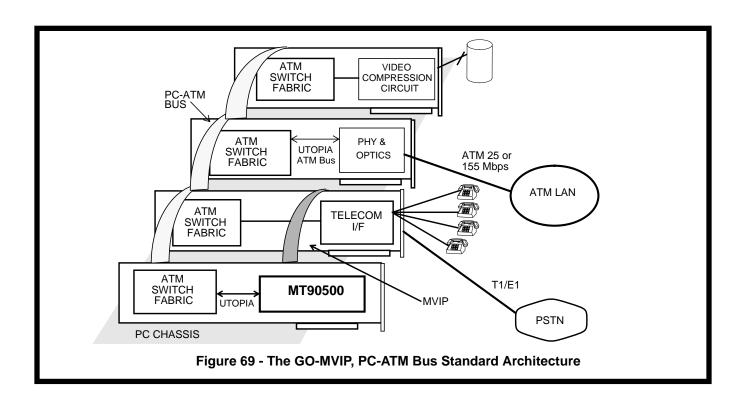

|             | The GO-MVIP, PC-ATM Bus Standard Architecture                          |     |

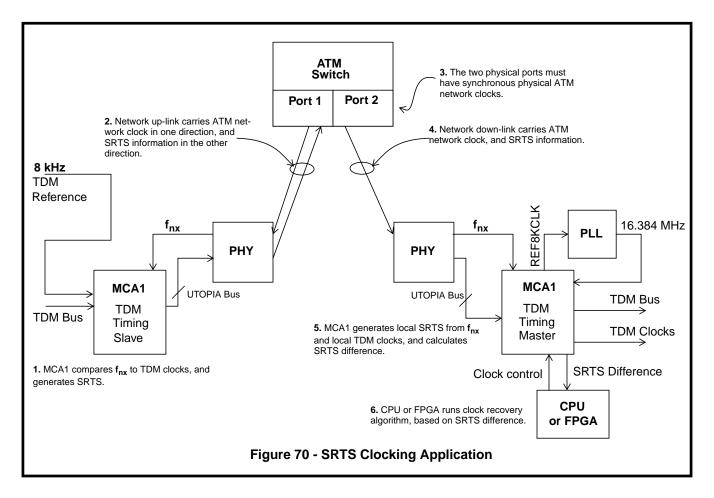

| Figure 70 - | SRTS Clocking Application                                              | 146 |

| Figure 71 - | TDM Payload Switching                                                  | 154 |

| Figure 72 - | TDM-to-TDM Loopback/Switching                                          | 155 |

| Figure 73 - | SCSA Message Bus Application                                           | 156 |

# **List of Tables**

| Table 1 -  | Primary UTOPIA Bus Pins                        | 19 |

|------------|------------------------------------------------|----|

| Table 2 -  | Secondary UTOPIA Bus Pins                      | 20 |

| Table 3 -  | Microprocessor Bus Interface Pins              | 20 |

| Table 4 -  | External Memory Interface Pins                 | 21 |

| Table 5 -  | Master Clock, Test, and Power Pins             | 22 |

| Table 6 -  | TDM Port Pins                                  | 23 |

| Table 7 -  | Reset State of I/O and Output Pins             | 24 |

| Table 8 -  | Pinout Summary                                 | 25 |

| Table 9 -  | Memory Size Combinations                       | 39 |

| Table 10 - | Effect of PSEL Field on P-byte Generation      | 53 |

| Table 11 - | Register Summary                               | 82 |

| Table 12 - | Main Control Register                          | 84 |

| Table 13 - | Main Status Register                           | 84 |

| Table 14 - | Window to External Memory Register - CPU       | 85 |

| Table 15 - | Read Parity Register                           | 85 |

| Table 16 - | Memory Configuration Register                  | 86 |

| Table 17 - | TX_SAR Control Register                        | 87 |

| Table 18 - | TX_SAR Status Register                         | 87 |

| Table 19 - | TX_SAR Scheduler Base Register                 | 88 |

| Table 20 - | TX_SAR Frame End Register                      | 88 |

| Table 21 - | TX_SAR End Ratio Register                      | 88 |

| Table 22 - | TX_SAR Control Structure Base Address Register | 89 |

| Table 23 - | Transmit Data Cell FIFO Base Address Register  | 89 |

| Table 24 - | Transmit Data Cell FIFO Write Pointer Register | 89 |

| Table 25 - | Transmit Data Cell FIFO Read Pointer Register  | 90 |

| Table 26 - | RX_SAR Control Register                        | 91 |

| Table 27 - | RX_SAR Status Register                         | 92 |

| Table 28 - | RX_SAR Misc. Event ID Register                 | 92 |

| Table 29 - | RX_SAR Misc. Event Counter Register            | 92 |

| Table 30 - | RX_SAR Underrun Event ID Register              | 93 |

| Table 31 - | RX_SAR Underrun Event Counter Register         | 93 |

| Table 32 - | RX_SAR Overrun Event ID Register               | 93 |

| Table 33 - | RX_SAR Overrun Event Counter Register          | 93 |

| Table 34 - | UTOPIA Control Register                        | 94 |

| Table 35 - | UTOPIA Status Register                         | 94 |

| Table 36 - | VPI / VCI Concatenation Register               | 95 |

| Table 37 - | VPI Match Register                             | 95 |

| Table 38 - | VPI Mask Register                              | 95 |

| Table 39 - | VCI Match Register                             | 95 |

| Table 40 - | VCI Mask Register                              | 96 |

| Table 41 - | VPI Timing Register                            | 96 |

| Table 42 - | VCI Timing Register                            | 96 |

| Table 43 - | Lookup Table Base Address Register             | 96 |

| Table 44 - | Receive Data Cell FIFO Base Address Register   | 97 |

| Table 45 - | Receive Data Cell FIFO Write Pointer Register  | 97 |

| Table 46 - | Receive Data Cell FIFO Read Pointer Register   | 97 |

| Table 47 - | TDM Interface Control Register                 | 98 |

| Table 48 - | TDM Interface Status Register                  | 99 |

| Table 49 - | TDM I/O Register                                                  | 100 |

|------------|-------------------------------------------------------------------|-----|

| Table 50 - | TDM Bus Type Register                                             | 101 |

| Table 51 - | Local Bus Type Register                                           | 102 |

| Table 52 - | TDM Bus to Local Bus Transfer Register                            | 102 |

| Table 53 - | Local Bus to TDM Bus Transfer Register                            | 103 |

| Table 54 - | TX Circular Buffer Control Structure Base Register                | 103 |

| Table 55 - | External to Internal Memory Control Structure Base Register       | 103 |

|            | TX Circular Buffer Base Address Register                          |     |

|            | TDM Read Underrun Address Register                                |     |

|            | TDM Read Underrun Count Register                                  |     |

|            | Clock Module General Control Register                             |     |

|            | Clock Module General Status Register                              |     |

| Table 61 - | Master Clock Generation Control Register                          |     |

| Table 62 - | Master Clock / CLKx2 Division Factor                              |     |

|            | Timing Reference Processing Control Register                      |     |

|            | Event Count Register                                              |     |

|            | CLKx1 Count - Low Register                                        |     |

|            | CLKx1 Count - High Register                                       |     |

|            | DIVX Register                                                     |     |

|            | DIVX Ratio Register                                               |     |

|            | SRTS Transmit Gapping Divider Register                            |     |

|            | SRTS Transmit Byte Counter Register                               |     |

|            | SRTS Receive Gapping Divider Register                             |     |

|            | SRTS Receive Byte Counter Register                                |     |

|            | Output Enable Registers                                           |     |

|            | Absolute Maximum Ratings                                          |     |

|            | Recommended Operating Conditions                                  |     |

|            | DC Characteristics                                                |     |

| Table 77 - |                                                                   |     |

|            | Main TDM Bus Data Output Parameters                               |     |

| Table 79 - | Main TDM Bus Input Clock Parameters                               |     |

| Table 80 - | ·                                                                 |     |

|            | Local TDM Bus Clock Parameters                                    |     |

|            | Local TDM Bus Data Output Parameters                              |     |

| Table 83 - | Local TDM Bus Data Input Parameters                               |     |

| Table 84 - | Intel Microprocessor Interface Timing - Read Cycle Parameters     |     |

| Table 85 - | Intel Microprocessor Interface Timing - Write Cycle Parameters    |     |

| Table 86 - | Motorola Microprocessor Interface Timing - Read Cycle Parameters  |     |

| Table 87 - | Motorola Microprocessor Interface Timing - Write Cycle Parameters |     |

| Table 88 - | MCLK - Master Clock Input Parameters                              |     |

| Table 89 - | External Memory Interface Timing - Clock Parameters               |     |

| Table 90 - | External Memory Interface Timing - Read Cycle Parameters          |     |

| Table 91 - | External Memory Interface Timing - Write Cycle Parameters         |     |

| Table 92 - | Primary UTOPIA Interface Parameters - Transmit                    |     |

| Table 93 - | Primary UTOPIA Interface Parameters - Receive                     |     |

| Table 94 - | Secondary UTOPIA Parameters Timing                                |     |

| Table 95 - | SRTS Interface Parameters                                         |     |

| Table 96 - | Message Channel Parameters                                        |     |

| Table 97 - | Boundary-Scan Test Access Port Timing                             |     |

| Table 98 - | ·                                                                 |     |

|            | · · · · · · · · · · · · · · · · · · ·                             |     |

# MT90500

| Гable 99 -  | MT90500 Connections to 32/36-bit Synchronous SRAM | 138 |

|-------------|---------------------------------------------------|-----|

|             | MT90500 UTOPIA Signal Directions                  |     |

|             | Recommended TDM Channel Numbers for SRTS VCs      |     |

| Гable 102 - | Limits on CDV on Receive SRTS VC                  | 146 |

| Гable 103 - | Summary of External Memory Structures             | 149 |

## 1. Introduction

#### 1.1 Functional Overview

The Mitel MT90500 Multi-Channel AAL1 SAR bridges a standard isochronous TDM (Time Division Multiplexed) backplane to a standard ATM (Asynchronous Transfer Mode) bus. On the TDM bus side, the MT90500 can interface to 16 bidirectional TDM bus links operating at 2.048, 4.096 or 8.192 Mbps (compatible with MVIP / H-MVIP, SCSA and Mitel ST-BUS). On the ATM interface side, the MT90500 provides the UTOPIA bus standardized by the ATM Forum. The device provides the AAL1 Structured Data Transfer (referred to as SDT from now on in this document) and pointerless Structured Data Transfer mappings defined by ANSI T1.630-1993 and ITU-T I.363. In addition, the MT90500 provides CBR (Constant Bit Rate) mapping of TDM to AAL0, and to AAL5 (CBR-AAL5). In all data transfer formats, the user simply ports the T1/E1, T3/E3, etc. traffic onto the TDM backplane before applying it to the MT90500. As well, the device also supports TDM clock recovery using adaptive, SRTS, or external clock recovery.

In the receive direction, ATM cells with VCs destined for the MT90500 are extracted from the UTOPIA bus and sent toward the TDM interface. In the transmit direction, the MT90500 provides multiplexing capabilities at the UTOPIA interface to allow the use of an external AAL5 SAR device, or multiple MT90500 devices. This is useful when CBR data and VBR/ABR/UBR data traffic must be transmitted from the local node on the same physical link. As well, the ability to multiplex internal AAL1 cells with external AAL5 cells can be used to interleave associated signalling cells and control messages with the AAL1 CBR traffic.

The MT90500 also offers some internal support for non-CBR data traffic. If the application's signalling (non-CBR) data throughput is not high, the MT90500 can transmit and receive AAL5 (or other non-CBR data) to / from a pair of FIFOs. This requires the microprocessor to perform SAR functions via software, but may remove the requirement for an external data SAR. Alternatively, if standard AAL5 signalling is not required by the system, the user can use some TDM channels for HDLC or proprietary signalling.

Segmentation and reassembly of TDM data to / from ATM cells is highly flexible. The MT90500 allows the user to select one or more TDM channels to be carried on an ATM logical connection with associated VPI/VCI. The number of TDM channels (1 to 122), the VPI/VCI, the data transfer method (SDT or pointerless Structured Data Transfer), cell partial-fill level, and the AAL (AAL1, CBR-AAL5, or CBR-AAL0) are all programmable. The time slot assignment circuit has 64 kbps granularity and allows a group of TDM channels to be carried on a single ATM logical channel (channel grooming). There is no limitation for distributing n x 64 channels on the TDM bus (i.e. TDM channels on a given VC can be concatenated or dispersed anywhere on the 16 serial data streams).

Up to 1024 bidirectional virtual circuits (VCs) can be handled simultaneously by the internal AAL1 processors. At the maximum TDM rate of 8.192 Mbps, up to 2048 input/output 64 kbps channels are available (1024 bidirectional TDM channels). If the ATM VCs are carrying multiple TDM channels (n x 64), less VCs will be created. The user is given the ability to flexibly define which 64 kbps channels will be converted into ATM VCs. It should be noted that since the MT90500's serial TDM port is fully bidirectional, the ATM logical connections can be defined as full duplex channels (e.g. voice conversation) or one-way connections (e.g. video playback). Using the full duplex capabilities, up to 1024 simultaneous phone calls could be handled by the MT90500.\_

The MT90500 allows the user to scale the size of the external synchronous memory to suit the application. The external memory's size is influenced by the number of virtual circuits required, the number of TDM channels being handled, and the amount of cell delay variation (CDV) tolerance required for the receive VCs. User-defined lookup tables, data cell FIFOs, and multiple event schedulers also influence the amount of external memory required.

The MT90500 supports two clocking schemes on the TDM bus: clock master and clock slave. In clock master, the MT90500 drives the clocks onto the TDM backplane (the TDM clock is recovered from an incoming ATM VC, or from an external source). In clock slave mode, the MT90500 receives its 8 kHz framing and clocks (4.096, 8.192 or 16.384 MHz) from the TDM backplane, and times its internal functions from that.

Figure 1 on page 12 shows the MT90500 block diagram. The Applications section of this document illustrates several connectivity options with external PHY and SAR devices.

Figure 1 - MT90500 Block Diagram

#### 1.2 Reference Documents

MT90500 Programmer's Manual.

MSAN-171 - TDM Clock Recovery from CBR-over-ATM Links Using the MT90500.

ITU-T Rec. I.363.1, "B-ISDN ATM Adaptation Layer Specification: Type 1 AAL," 08/1996.

ANSI T1.630, "Broadband ISDN - ATM Adaptation Layer for Constant Bit Rate Services Functionality and Specification," 1993.

AF-PHY-0017, "UTOPIA, An ATM-PHY Interface Specification: Level 1, Version 2.01," March 21, 1994.

AF-VTOA-0078.000, "Circuit Emulation Service Interoperability Specification, Version 2.0," Jan. 1997.

AF-VTOA-0083.000, "Voice and Telephony Over ATM to the Desktop Specification, Version 2.0," May 1997.

M. Noorchasm *et al.*, "Buffer Design for Constant Bit Rate Services in Presence of Cell Delay Variation," ATM Forum Contribution 95-1454.

Paul E. Fleischer and Chi-Leung Lau, "Synchronous Residual Time Stamp for Timing Recovery in a Broadband Network," United States Patent 5,260,978, Nov. 1993.

IEEE Std. 1149.1a-1993, "IEEE Standard Test Access Port and Boundary Scan Architecture."

## 1.3 ATM Glossary

- **AAL -** *ATM Adaptation Layer*; standardized protocols used to translate higher layer services from multiple applications into the size and format of an ATM cell.

- AAL0 native ATM cell transmission; proprietary protocol featuring 5-byte header and 48-byte user payload.

- **AAL1 ATM Adaptation Layer** used for the transport of constant bit rate, time-dependent traffic (e.g. voice, video); requires transfer of timing information between source and destination; maximum of 47-bytes of user data permitted in payload as an additional header byte is required to provide sequencing information.

- **AAL5 ATM Adaptation Layer** usually used for the transport of variable bit rate, delay-tolerant data traffic and signalling which requires little sequencing or error-detection support.

- **ANSI T1.630** American National Standards Institute specification: Broadband ISDN ATM Adaptation Layer for Constant Bit Rate Services Functionality and Specification.

- **Asynchronous** 1. Not **synchronous**; not periodic. 2. The temporal property of being sourced from independent timing references. Asynchronous signals have different frequencies, and no fixed phase relationship. 3. In telecom, data which is not synchronized to the public network clock. 4. The condition or state when an entity is unable to determine, prior to its occurrence, exactly when an event will transpire.

- **ATM** Asynchronous Transfer Mode; a method in which information to be transferred is organized into fixed-length cells; asynchronous in the sense that the recurrence of cells containing information from an individual user is not necessarily periodic. (While ATM cells are transmitted synchronously to maintain clock between sender and receiver, the sender transmits data cells when it has something to send and transmits empty cells when idle, and is not limited to transmitting data every Nth cell.)

- **Cell** fixed-size information package consisting of 53 bytes (octets) of data; of these, 5 bytes represent the cell header and 48 bytes carry the user payload and required overhead.

- **CBR** Constant Bit Rate; an ATM service category supporting a constant or guaranteed rate, with timing control and strict performance parameters. Used for services such as voice, video, or circuit emulation.

- **CDV** *Cell Delay Variation*; a **QoS** parameter that measures the peak-to-peak cell delay through the network; results from buffering and cell scheduling.

- **CES** *Circuit Emulation Service*; ATM Forum service providing a virtual circuit which emulates the characteristics of a constant bit rate, dedicated-bandwidth circuit (e.g. T1).

- **CLP** *Cell Loss Priority*; a 1-bit field in the ATM cell header that corresponds to the loss priority of a cell; cells with CLP = 1 can be discarded in a congestion situation.

- **CSI** Convergence Sublayer Indication bit in the AAL1 header byte; when present in an even-numbered cell using **SDT**, indicates the presence of a pointer byte; used to transport **RTS** values in odd-numbered cells using **SRTS** for clock recovery.

- **GFC** *Generic Flow Control*; 4-bit field in the ATM header used for local functions (not carried end-to-end); default value is "0000", meaning that GFC protocol is not enforced.

- **HEC** Header Error Control; using the fifth octet in the ATM cell header, ATM equipment (usually the **PHY**) may check for an error and correct the contents of the header; CRC algorithm allows for single-error correction and multiple-error detection.

- I.363 ITU-T Recommendation specifying the AALs for B-ISDN (Broadband ISDN).

- **Isochronous** The temporal property of an event or signal recurring at known periodic time intervals (e.g. 125 μs). Isochronous signals are dependent on some uniform timing, or carry their own timing information embedded as part of the signal. Examples are DS-1/T1, E1 and TDM in general. From the root words, "iso" meaning equal, and "chronous" meaning time.

- **OAM bit** Operations, Administration and Maintenance; MSB within the **PTI** field of the ATM cell header which indicates if the ATM cell carries management information such as fault indications.

- **Plesiochronous** The temporal property of being arbitrarily close in frequency to some defined precision. Plesiochronous signals occur at nominally the same rate, any variation in rate being constrained within specific limits. Since they are not identical, over the long term they will be skewed from each other. This will force a

## MT90500

- switch to occasionally repeat or delete data in order to handle buffer underflow or overflow. (In telecommunications, this is known as a frame slip).

- **PHY** *Physical Layer*; bottom layer of the ATM Reference Model; provides ATM cell transmission over the physical interfaces that interconnect the various ATM devices.

- **PTI** Payload Type Identifier; 3-bit field in the ATM cell header MSB indicates if the cell contains **OAM** information or user data; LSB indicates that a **AAL5** cell is the final cell in a frame.

- **QoS** *Quality of Service*; ATM performance parameters that characterize the transmission quality over a given VC (e.g cell delay variation; cell transfer delay, cell loss ratio).

- RTS Residual Time Stamp; see SRTS.

- **SAR** Segmentation and Reassembly; method of partitioning, at the source, frames into ATM cells and reassembling, at the destination, these cells back into information frames; lower sublayer of the **AAL** which inserts data from the information frames into cells and then adds the required header, trailer, and/or padding bytes to create 48-byte payloads to be transmitted to the ATM layer.

- **SDT -** Structured Data Transfer; format used within **AAL1** for blocks consisting of N \* 64 kbps channels; blocks are segmented into cells for transfer and additional overhead bytes (pointers) are used to indicate structure boundaries within cells (therefore aiding clock recovery).

- **SN** Sequence Number; 4-bit field in the **AAL1** header byte used as a sequence counter for detecting lost or misinserted ATM cells.

- **SNP** Sequence Number Protection; 4-bit field in the **AAL1** header byte consisting of a CRC and a parity bit which are designed to provide error-correction on the **SN**.

- **SRTS** *Synchronous Residual Time Stamp*; method for clock recovery in which difference signals between a source clock and the network reference clock (time stamps) are transmitted to allow reconstruction of the source clock. The destination reconstructs the source clock based on the time stamps and the network reference clock. (Note that the same network reference clock is required at both ends.)

- **SSRAM -** Synchronous Static RAM.

- **Synchronous** 1. The temporal property of being sourced from the same timing reference. Synchronous signals have the same frequency, and a fixed (often implied to be zero) phase offset. 2. A mode of transmission in which the sending and receiving terminal equipment are operating continually at the same rate and are maintained in a desired phase relationship by an appropriate means.

- **UDT -** *Unstructured Data Transfer*; format used within **AAL1** for transmission of user data without regard for structure boundaries (e.g. circuit emulation); term used within ANSI standard not explicitly stated in ITU.

- **UTOPIA** *Universal Test and Operations Physical Interface for ATM;* a **PHY**-level interface to provide connectivity between ATM components.

- **VC** *Virtual Channel;* one of several logical connections defined within a virtual path (**VP**) between two ATM devices; provides sequential, unidirectional transport of ATM cells. Also *Virtual Circuit*.

- **VCI** *Virtual Channel Identifier*; 16-bit value in the ATM cell header that provides a unique identifier for the virtual channel (**VC**) within a virtual path (**VP**) that carries a particular cell.

- **VP** *Virtual Path*; a unidirectional logical connection between two ATM devices; consists of a set of virtual channels (**VC**).

- **VPI** *Virtual Path Identifier*; 8-bit value in the ATM cell header that indicates the virtual path (**VP**) to which a cell belongs.

- **VTOA** *Voice and Telephony over ATM;* intended to provide voice connectivity to the desktop, and to provide interoperability with existing N-ISDN and PBX services.

#### **Glossary References:**

The ATM Glossary - ATM Year 97 - Version 2.1, March 1997

The ATM Forum Glossary - May 1997

ATM and Networking Glossary (http://www.techguide.com/comm/index.html)

Mitel Semiconductor Glossary of Telecommunications Terms - May 1995.

#### 2. Features

#### 2.1 General

The MT90500 device external interfaces are:

- TDM (Time Division Multiplexed) bus composed of 16 serial streams running at up to 8.192 Mbps, plus related clocks and control signals, configurable by software. This interface also includes various signals for TDM clock signal generation. This bus carries telecom or other data in N x 64 kbps streams.

- Local serial TDM bus interface (a TDM input pin, a TDM output pin, and clocks).

- A primary UTOPIA bus running at up to 25 MHz, suitable for connection to a 25 Mbps or 155 Mbps PHY device.

- A secondary UTOPIA bus, for connection of an optional external SAR (e.g. data) device running at up to 25 MHz. In this case, the MT90500 device emulates a PHY device for the external SAR.

- A synchronous 36-bit wide memory interface running at up to 60 MHz.

- A 16-bit microprocessor interface used for device configuration, status, and control.

- Signals for general clocking, reset, and JTAG boundary-scan.

#### 2.2 Serial TDM Bus

- Compatible with ST-BUS, MVIP, H-MVIP, IDL, and SCSA interfaces.

- Provides 16 bidirectional serial streams that can operate at TDM data rates of 2.048, 4.096 or 8.192 Mbps for up to 2048 TDM 64 kbps channels (1024 bidirectional DS0 channels: supports 32 E1 framers, or 42 T1 framers, or 10 J2 framers).

- Serial TDM bus clocking schemes: TDM timing bus slave (MT90500 slaved to TDM bus), TDM timing bus master (MT90500 drives clocks onto TDM bus freerun, or synchronized to 8 kHz reference) and TDM bus master-alternate (MT90500 slaved to TDM bus, but ready to switch to 8 kHz reference).

- Additional Local TDM Bus interface (2.048 Mbps) allows local TDM devices to access the main TDM bus.

#### 2.3 CBR ATM Cell Processor

- Independent Segmentation and Reassembly blocks for receive and transmit (RX\_SAR and TX\_SAR) support CBR (Constant Bit Rate) transport of half- or full-duplex TDM channels.

- Compatible with "Structured Data Transfer (SDT) services" as per ANSI T1.630 standard for 1 to 122 TDM channels per VC.

- Compatible with ITU-T I.363.1 "circuit transport" of 8 kHz structured data using Structured Data Transfer (SDT) for 1 to 96 TDM channels per VC (using buffer-fill level monitoring).

- Compatible with ITU-T I.363.1 "voiceband signal transport."

- Compatible with AF-VTOA-0078.000 "N x 64 Basic Service" (non-CAS) Circuit Emulation (using buffer-level monitoring, rather than lost cell insertion).

- Compatible with AF-VTOA-0078.000 for SDT of partially-filled AAL1 cells with N-channel structures (where N does not exceed the value of the partial-fill).

- AAL1 SAR-PDU Header processing (AAL1 Sequence Number checking).

- Supports up to 1024 bidirectional VCs (virtual circuits) simultaneously.

- Supports up to 1024 transmit TDM channels and 1024 receive TDM channels simultaneously.

- Supports CBR-AAL0 (48 byte cell payload).

- Supports CBR-AAL5 as per AF-VTOA-0083.000, also supports Nx64 trunking over CBR-AAL5.

- Supports partially-filled cells (AAL1, CBR-AAL5, and CBR-AAL0).

- User-defined, per-VC, Cell Delay Variation tolerance: 8 to 128 ms buffer size (up to 64 ms CDV).

- Handles TDM channels at 64 kbps granularity.

- Each individual VC can be composed of N x 64 kbps wideband channels (N = 1, 2, ..., 122).

- Flexible aggregation capability (N x 64 kbps) maintains frame integrity, while allowing any combination of 64 kbps channels (DS0 grooming).

- Supports "multi-casting" of one TDM DS0 input channel to multiple Transmit ATM VCs, and of one Receive ATM DS0 to multiple TDM outputs.

- A VC can contain any combination of TDM channels from any combination of TDM streams (Nx64) and maintain frame integrity for those channels.

- Supports several 8 kHz synchronisation operations: synchronized to external 8 kHz reference, synchronized to network clock, and synchronized to timing derived from an ATM VC (including ITU-T I.363.1 Adaptive and SRTS clock recovery mechanisms).

## 2.4 External Memory Interface

- To implement SAR functions and buffers, the MT90500 device uses external Synchronous SRAM.

- External Synchronous SRAM size is chosen by user, and depends on Cell Delay Variation (CDV)

and the number of simultaneous 64 kbps channels handled. The amount of Synchronous SRAM is

scalable to suit the application, and may range from 128 Kbytes to 2,048 Kbytes.

## 2.5 UTOPIA Interface and Multiplexer

- UTOPIA Level 1 compatible 8-bit bus, running at up to 25 Mbyte/s, for connection to PHY devices with data throughput of up to 155 Mbps.

- Transmit multiplexer mixes cells from TX\_SAR and Secondary UTOPIA port, supporting another MT90500, and/or an external SAR device (e.g. AAL5) connected to a single PHY device.

- Programmable multiplexer priority gives internally generated AAL1 cells equal, or higher, priority than cells coming from Secondary UTOPIA port.

- Supports non-CBR data cells and OAM cells destined for microprocessor with Receive and Transmit Data Cell FIFOs.

- Flexible receive cell handling: AAL1 (as well as CBR-AAL0 and CBR-AAL5) cells are sent to the TDM port; data cells (non-CBR data and OAM cells) are sent to the Receive Data Cell FIFO; cells with unrecognized VCs may be queued or ignored.

- Cell reception based on look-up-table allows flexible VC assignment for CBR VCs (allows noncontiguous VC assignment).

- Programmable VPI/VCI Match and Mask filtering reduces unnecessary look-up-table accesses.

## 2.6 Microprocessor Interface

- 16-bit microprocessor port, configurable to Motorola or Intel timing.

- Programmable interrupts for control and statistics.

- Allows access to internal registers for initialization, control, and statistics.

- Allows access to external SSRAM for initialization, control, and observation.

#### 2.7 Miscellaneous

- Master clock rate up to 60 MHz.

- Dual rails (3.3V for power minimization, 5V for standard I/O).

- Loopback function provided at the TDM interface.

- IEEE 1149 (JTAG) Boundary-Scan Test Access Port for testing board-level interconnect.

- Packaging: 240-pin PQFP.

#### 2.8 Interrupts

The MT90500 provides a wide variety of interrupt source bits, allowing for easy monitoring of MT90500 operation. All interrupt source bits, including the module level interrupt bits, have an associated mask bit which enables or disables assertion of the interrupt pin. This enables the user to tailor the interrupt pin activity to the application. Interrupt source bits are set regardless of the state of the associated mask bit, so even source bits which are disabled from causing an interrupt pin assertion may be polled by the CPU by reading the appropriate register.

## 2.8.1 Module Level Interrupts

The following interrupt bits are used to indicate which MT90500 circuit module is the source of the interrupt. They are set when one or more interrupt source bits in the particular circuit module is set. The CPU can find the source of an interrupt by reading the register containing these bits and then reading the indicated module's interrupt register.

- TX\_SAR Module Interrupt

- RX\_SAR Module Interrupt

- UTOPIA Module Interrupt

- TDM Module Interrupt

- Timing (TDM Clock Generation) Module Interrupt

## 2.8.2 TX\_SAR Interrupts

- Transmit Non-CBR Data Cell FIFO Overrun Interrupt

- Scheduler error (Indicates that the TX\_SAR has too heavy a work load.)

#### 2.8.3 RX SAR Interrupts

- AAL1-byte Parity Error Interrupt

- AAL1-byte CRC Error Interrupt

- AAL1-byte Sequence Number Error Interrupt

- Pointer-byte Parity Error Interrupt

- Pointer-byte Out of Range Error Interrupt

- Underrun Error Interrupt

- Overrun Error Interrupt

- Miscellaneous Counter Rollover Interrupt

- Underrun Counter Rollover Interrupt

- Overrun Counter Rollover Interrupt

### 2.8.4 UTOPIA Interrupts

- Receive Non-CBR Data Cell FIFO Overrun Interrupt

- RX UTOPIA Module Internal FIFO Overrun Interrupt

- Receive Non-CBR Data Cell FIFO Receive Cell Interrupt

#### 2.8.5 TDM Interrupts

- Clock Absent Interrupt

- Clock Fail Interrupt

- TDM Out of Bandwidth Interrupt

- TDM Read Underrun Error Interrupt

- TDM Read Underrun Counter Rollover Interrupt

## 2.8.6 Timing Module Interrupts

- 8 kHz Reference Failure Interrupt

- SRTS TX Underrun Interrupt

- SRTS TX Overrun Interrupt

- SRTS RX Underrun Interrupt

- SRTS RX Overrun Interrupt

- Adaptive Clock Loss of Timing Reference Cell Interrupt

- Adaptive Clock Loss of Synchronization Interrupt

#### 2.9 Statistics

The MT90500 provides a number of statistics to allow monitoring of the MT90500. These statistics generally parallel the operation of some of the interrupt source bits. The counters (except the Timing Recovery counters) also set rollover interrupt source bits when they reach their terminal counts and return to zero.

#### 2.9.1 RX\_SAR Statistics

- Miscellaneous Event Counter: This 16-bit register's value is incremented each time a (mask-selected) miscellaneous error occurs.

- AAL1-byte Parity Error

- AAL1-byte CRC Error

- AAL1 Sequence Number Error

- Pointer-byte Parity Error

- Pointer-byte Out of Range Error

- Miscellaneous Event ID Register: The address of the RX Control Structure that caused the last miscellaneous error.

- Underrun Count: This 16-bit register's value is incremented each time a CBR Receive Underrun

occurs.

- Underrun ID Number: The address of the RX Control Structure that caused the last underrun error.

- Overrun Count: This 16-bit register is incremented each time a CBR Receive Overrun occurs.

- Overrun ID Number: The address of the RX Control Structure that caused the last overrun error.

#### 2.9.2 TDM Statistics

- TDM Read Underrun Time Slot Stream. Contains the time slot and stream on which the last TDM read underrun was detected.

- TDM Read Underrun Counter. Each time a TDM read underrun occurs, this register's value is incremented.

#### 2.9.3 Timing Recovery Statistics

- Event Counter: Counts the reception of timing reference cells or 8 kHz markers.

- CLKx1 Counter: 24-bit counter which keeps a running count of TDM byte-periods.

# 3. Pin Descriptions

I/O types are: Output (O), Input (I), Bidirectional (I/O), Power (PWR), or Ground (GND).

Input pad types are: TTL, CMOS, Differential, or Schmitt. The notations "PU" and "PD" are used, respectively, to indicate that a pad has an internal pullup or pulldown resistor. TTL (5V) inputs are pulled-up to the 5V rail, CMOS (3.3V) inputs are pulled-up to the 3.3V rail. These weak internal resistors should not be relied upon for fast data transitions. The 3.3V CMOS inputs have a switching threshold of 1.6V, and tolerate input levels of up to 5V; therefore they are 5V TTL compatible (with the exception of the TRISTATE pin, which is not 5V tolerant).

Output pad types are generally described by voltage and current capability. Output types used are: 3.3V, 4mA; 5V, 4mA; 5V, 12mA; and open-drain. A notation of "SR" indicates that the pad is slew-rate limited. 3.3V CMOS outputs will satisfy 5V TTL input thresholds at the rated current.

**Table 1 - Primary UTOPIA Bus Pins**

| Pin#                              | Pin Name     | I/O | Туре                      | Description                                                                                                                                                                                                                                                                                                                                                                                        |

|-----------------------------------|--------------|-----|---------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 49, 48, 47, 46,<br>45, 44, 39, 38 | PTXDATA[7:0] | 0   | 5V, 4mA                   | Primary UTOPIA transmit data bus. Byte-wide data driven from MT90500 to PHY device. Bit 7 is the MSB.                                                                                                                                                                                                                                                                                              |

| 52                                | PTXSOC       | 0   | 5V, 4mA                   | Primary UTOPIA transmit start of cell signal. Asserted by the MT90500 when PTXDATA[7:0] contains the first valid byte of the cell.                                                                                                                                                                                                                                                                 |

| 51                                | PTXEN        | 0   | 5V, 4mA                   | Primary UTOPIA transmit data enable. Active LOW signal asserted by the MT90500 during cycles when PTXDATA[7:0] contains valid cell data.                                                                                                                                                                                                                                                           |

| 53                                | PTXCLAV      | I   | TTL PU                    | Primary UTOPIA transmit cell available indication signal. For cell level flow control, PTXCLAV is asserted by the PHY to indicate to the MT90500 that the PHY can accept the transfer of a complete cell.                                                                                                                                                                                          |

| 82                                | PTXCLK       | I/O | TTL PU /<br>5V, 4mA<br>SR | Primary UTOPIA transmit clock. Data transfer & synchronization clock provided by the MT90500 to the PHY for transmitting data on PTXDATA[7:0]; software configurable (in Main Control Register at 0000h) to run at up to 25 MHz. Note that this pin should be configured as an output for exact compliance with UTOPIA Level 1, V2.01.                                                             |

| 50                                | PTXPAR       | 0   | 5V, 4mA                   | Primary UTOPIA transmit parity. This signal is the odd parity bit over PTXDATA[7:0].                                                                                                                                                                                                                                                                                                               |

| 57, 58, 59, 62,<br>63, 64, 65, 66 | PRXDATA[7:0] | ı   | TTL PU                    | Primary UTOPIA receive data bus. Byte-wide data driven from the PHY to the MT90500. PRXDATA[7] is the MSB.                                                                                                                                                                                                                                                                                         |

| 56                                | PRXSOC       | I   | TTL PU                    | Primary UTOPIA receive start of cell signal. Asserted by the PHY when PRXDATA[7:0] contains the first valid byte of a cell.                                                                                                                                                                                                                                                                        |

| 55                                | PRXEN        | I   | TTL PU                    | Primary UTOPIA bus data enable. Active LOW signal normally asserted by the secondary SAR to indicate that PRXDATA[7:0], PRXSOC, and PRXCLAV will be sampled at the end of the next clock cycle. If no secondary SAR is used, ground this pin at the MT90500 and PHY devices. Note that the UTOPIA standard permits this signal to be permanently asserted (see UTOPIA Level 1, V2.01, footnote 6). |

| 54                                | PRXCLAV      | I   | TTL PU                    | Primary UTOPIA receive cell available indication signal. For cell level flow control, PRXCLAV is asserted by the PHY to indicate it has a complete cell available for transfer to the RX UTOPIA port.                                                                                                                                                                                              |

| 79                                | PRXCLK       | I   | TTL PU                    | Primary UTOPIA bus receive clock. This clock, which can run at up to 25 MHz, is provided by the secondary SAR device. If no secondary SAR is used, connect to PTXCLK (this will provide exact compliance with the UTOPIA Level 1, V2.01 specification).                                                                                                                                            |

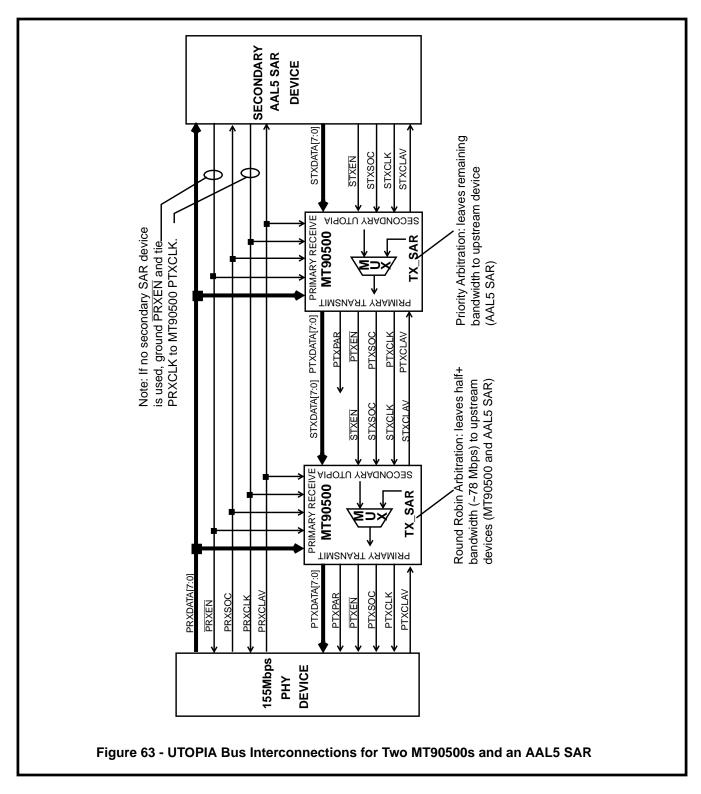

Refer to Figure 63 on page 139 for implementation details regarding the interface between two MT90500s and an external AAL5 SAR.

Table 2 - Secondary UTOPIA Bus Pins

| Pin#                              | Pin Name     | 1/0 | Туре    | Description                                                                                                                                                                                                              |

|-----------------------------------|--------------|-----|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 70, 71, 72, 73,<br>74, 75, 76, 77 | STXDATA[7:0] | I   | TTL PU  | Secondary UTOPIA transmit data bus. Byte-wide data driven from the external SAR to the MT90500. Bit 7 is the MSB.                                                                                                        |

| 69                                | STXSOC       | I   | TTL PU  | Secondary UTOPIA transmit start of cell signal. Asserted by the external SAR device when STXDATA[7:0] contains the first valid byte of the cell.                                                                         |

| 68                                | STXEN        | I   | TTL PU  | Secondary UTOPIA transmit data enable. Active LOW signal asserted by the external SAR during cycles when STXDATA[7:0] contains valid cell data.                                                                          |

| 67                                | STXCLAV      | 0   | 5V, 4mA | Secondary UTOPIA transmit cell available indication signal. For cell level flow control, STXCLAV is asserted by the MT90500 to indicate to the external SAR that the MT90500 can accept the transfer of a complete cell. |

| 85                                | STXCLK       | I   | TTL PU  | Secondary UTOPIA transmit clock, which can run at up to 25 MHz. Data transfer & synchronization clock provided by the external SAR to the MT90500 for transmitting data over STXDATA[7:0].                               |

**Note:** MT90500 Secondary UTOPIA port emulates a PHY device for connection to an external SAR (ATM-layer device). Refer to Figure 63 on page 139 for implementation details regarding the interface between the MT90500 and an external AAL5 SAR.

**Table 3 - Microprocessor Bus Interface Pins**

| Pin #                                                                                         | Pin Name                                | 1/0 | Туре                       | Description                                                                                                                                                                                                                |

|-----------------------------------------------------------------------------------------------|-----------------------------------------|-----|----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 37                                                                                            | Intel/Motorola                          | ı   | TTL PU                     | Intel interface (1) / Motorola interface (0)                                                                                                                                                                               |

| 36                                                                                            | IC                                      | ı   | TTL PU                     | Internal connection (must be HIGH).                                                                                                                                                                                        |

| 203                                                                                           | CS                                      | 1   | TTL PU                     | Active LOW chip select signal.                                                                                                                                                                                             |

| 237                                                                                           | $\overline{WR}/R\backslash\overline{W}$ | 1   | TTL PU                     | Active LOW Write Strobe (Intel) / Read-Write (Motorola).                                                                                                                                                                   |

| 239                                                                                           | RD/DS                                   | ı   | TTL PU                     | Active LOW Read Strobe (Intel) / Active LOW Data Strobe (Motorola).                                                                                                                                                        |

| 238                                                                                           | RDY/DTACK                               | 0   | 5V, 4mA                    | Ready (Intel) / Data Transfer Acknowledge (Motorola). Acts as active LOW pseudo-open-drain in Motorola mode (DTACK, see Figure 53 on page 126). Acts as normal output in Intel mode, high impedance when CS is HIGH (RDY). |

| 84                                                                                            | ĪNT                                     | 0   | 5V, 4mA SR<br>(Open-Drain) | Active LOW interrupt line.                                                                                                                                                                                                 |

| 223, 222, 219,<br>218, 217, 216,<br>215, 214, 212,<br>211, 210, 209,<br>208, 206, 205,<br>204 | D[15:0]                                 | I/O | TTL PU /<br>5V, 4mA SR     | CPU data bus.                                                                                                                                                                                                              |

| 184                                                                                           | AEM                                     | I   | TTL PU                     | Access External Memory - CPU accesses external memory when HIGH (internal memory and registers when LOW).                                                                                                                  |

| 185, 186, 187,<br>188, 189, 190,<br>191, 192, 193,<br>194, 195, 196,<br>198, 199, 202         | A[15:1]                                 | I   | TTL PU                     | CPU Address lines A15-A1.  All microprocessor accesses to the device are word-wide, but addresses in this document are given as byte-addresses. The virtual A[0] bit selects between high and low bytes in a word.         |

Note: MT90500 TTL inputs are pulled up to the 5 Volt rail. See Table 76 on page 112.

**Table 4 - External Memory Interface Pins**

| Pin#                                                                                                                                                           | Pin Name      | I/O | Туре                       | Description                                                                                                                                                                                                                                                                                                                                     |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|-----|----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 98                                                                                                                                                             | MEMCLK        | 0   | 3.3V, 4mA                  | Memory Clock. Internally connected to MCLK.                                                                                                                                                                                                                                                                                                     |

| 147                                                                                                                                                            | MEM_CS0L      | 0   | 3.3V, 4mA                  | Active LOW memory chip select signal. This chip select is used in all memory modes. When there are two chips per bank, $\overline{\text{MEM\_CSOL}}$ is associated with MEM_DAT[15:0] of Bank 0.                                                                                                                                                |

| 176                                                                                                                                                            | MEM_CS0H      | 0   | 3.3V, 4mA                  | Active LOW memory chip select signal. This chip select is used when there are two 16-bit memory chips per bank. MEM_CS0H is associated with MEM_DAT[31:16] of Bank 0.                                                                                                                                                                           |

| 148                                                                                                                                                            | MEM_CS1L      | 0   | 3.3V, 4mA                  | Active LOW memory chip select signal. This chip select is used when there are two banks and two chips per bank. $\overline{\text{MEM\_CS1L}}$ is associated with MEM_DAT[15:0] of Bank 1.                                                                                                                                                       |

| 177                                                                                                                                                            | MEM_CS1H      | 0   | 3.3V, 4mA                  | Active LOW memory chip select signal. This chip select is used when there are two banks and two chips per bank. MEM_CS1H is associated with MEM_DAT[31:16] of Bank 1.                                                                                                                                                                           |

| 178, 179, 149,<br>150                                                                                                                                          | MEM_WR[3:0]   | 0   | 3.3V, 4mA                  | Active LOW byte-write enables. MEM_WR[3] is associated with MEM_DAT[31:24]; MEM_WR[2] is associated with MEM_DAT[23:16]; MEM_WR[1] is associated with MEM_DAT[15:8]; MEM_WR[0] is associated with MEM_DAT[7:0].                                                                                                                                 |

| 180                                                                                                                                                            | MEM_OE        | 0   | 3.3V, 4mA                  | Active LOW output enable.                                                                                                                                                                                                                                                                                                                       |

| 123, 122, 121,<br>118, 117, 116,<br>115, 103, 102,<br>99, 146, 144,<br>130, 128, 127,<br>126, 125, 124                                                         | MEM_ADD[17:0] | 0   | 3.3V, 4mA                  | Memory address lines.                                                                                                                                                                                                                                                                                                                           |

| 166, 167, 168, 170, 171, 173, 174, 175, 153, 154, 155, 156, 158, 159, 162, 164, 133, 134, 135, 136, 137, 138, 142, 143, 105, 106, 107, 108, 109, 112, 113, 114 | MEM_DAT[31:0] | I/O | 3.3V CMOS<br>PU/3.3V 4mA   | Memory data lines. MEM_DAT[31:24] represent the upper byte; MEM_DAT[23:16] represent the upper-middle byte; MEM_DAT[15:8] represent the lower-middle byte; MEM_DAT[7:0] represent the lower byte.                                                                                                                                               |

| 165, 152, 131,<br>104                                                                                                                                          | MEM_PAR[3:0]  | I/O | 3.3V CMOS<br>PU / 3.3V 4mA | Memory parity lines. MEM_PAR[3:0] are the optional "parity" bits that allow TDM Read Underrun detection. MEM_PAR[3] is related to MEM_DAT[31:24], MEM_PAR[2] is related to MEM_DAT[23:16], MEM_PAR[1] is related to MEM_DAT[15:8], and MEM_PAR[0] is related to MEM_DAT[7:0]. When unused, these pins must be pulled up via external resistors. |

Note: MT90500 3.3 V CMOS inputs are pulled up to the 3.3 Volt rail. See Table 76 on page 112.

Table 5 - Master Clock, Test, and Power Pins

| Pin #                                                                                              | Pin Name    | I/O | Туре                                | Description                                                                                                                                                                                                                                                                                                                                                                                            |  |  |