# CMOS **MT90737 DS3/DS1 MUX/DEMUX (M13)**

## **Preliminary Information**

June 1995

## **Features**

- Multiplexes/demultiplexes 28 DS1 signals to/from a DS3 signal

- Selectable M13 or C-bit parity mode

- · Separate interface for C-bits

- FEBE, C or P-bit parity error insertion

- DS3 LOS, LOF, P-bit parity, C-bit parity, AIS and idle signal detection

- DS3 AIS and idle signal generation

- Access to DS3 and DS2 X-bits

- DS3 and DS1 loopbacks

- Detects DS2 LOF

- DS1 idle signal (QRS, AIS or ESF) generation

- DS1 LOS detection on transmit or receive path

- Multiplexed and non-multiplexed microprocessor bus interfaces

## **Applications**

- Single-board M13 multiplexer

- Compact add/drop mux

- Fractional T3

- Digital Cross-connect Systems

- CSU/DSU

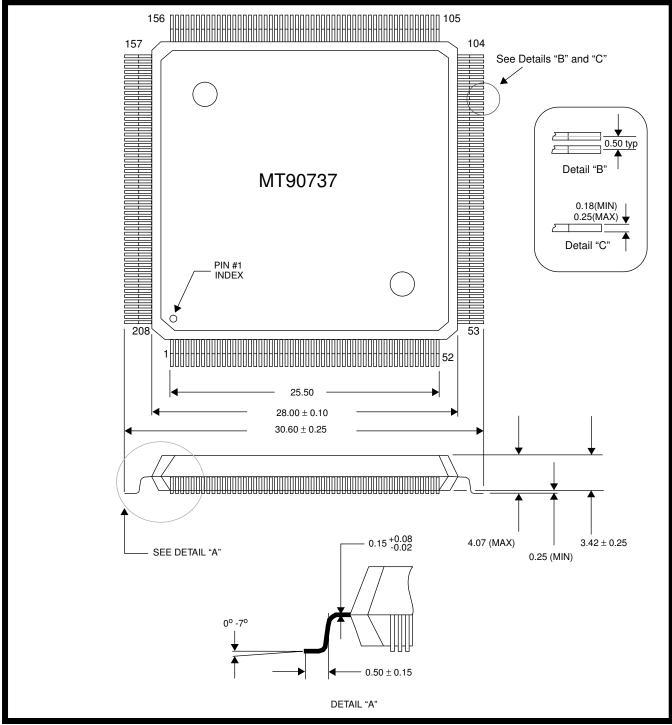

## ISSUE 1 Ordering Information

MT90737AM 208 Pin PQFP

-40° to 85°C

## Description

The MT90737 DS3/DS1 Multiplexer/Demultiplexer (M13) is designed to multiplex and demultiplex 28 independent DS1 signals to and from a DS3 signal with either an M13 or C-bit frame format. The MT90737 complies with Bellcore's TR-TSY-000499, ANSI's T1.107-1988 and supplement T1.107a-1990.

The MT90737 provides a separate transmit (13 bits) and receive (14 bits) interface for C-bits while operating in the C-bit parity mode. The FEAC channel (C3) is accessed via MT90737 memory. The MT90737 uses 37 byte register locations for software control, performance counters, and alarm reporting. Both multiplexed and non-multiplexed bus types are supported by the microprocessor interface.

U.S. Patent Number 5040170

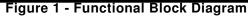

Figure 2 - Pin Connections

## **Pin Description**

Power Supply, Ground and No Connect.

| Pin #                                                                                                     | Name | I/O/P | Description                |

|-----------------------------------------------------------------------------------------------------------|------|-------|----------------------------|

| 5, 32, 75,<br>88, 94,<br>126, 138<br>183, 200                                                             | VDD  | Р     | Power Supply. +5V±5%.      |

| 18, 49, 55,<br>56, 67, 70,<br>84,101,102,<br>110, 124,<br>146, 153,<br>159, 160,<br>166, 191,<br>205, 206 | VSS  | Ρ     | Ground.                    |

| 1-4, 50-54,<br>103-107,<br>154-158,<br>207, 208                                                           | NC   |       | No Connection. leave open. |

Note: I = Input; O = Output; P = Power. See DC Characteristics section for CMOS and TTL Type definitions.

## **DS1 Receive Interfaces**

| Pin # | Name | I/O/P | Description                                                                     |

|-------|------|-------|---------------------------------------------------------------------------------|

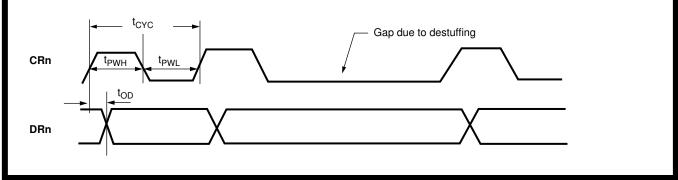

| 62    | CR1  | 0     | Receive Clock Channels 1 - 28. TTL Type III compatible. Receive data is         |

| 43    | CR2  |       | clocked out of the MT90737 on positive transitions. The clock for the first DS1 |

| 41    | CR3  |       | channel corresponds to CR1, while the clock for the last DS1 channel corre-     |

| 39    | CR4  |       | sponds to CR28. The DS1 clock signals are derived from the DS3 clock signal     |

| 37    | CR5  |       | (DS3CR). During periods of DS3/DS2 out of frame or AIS, the MT90737 pro-        |

| 35    | CR6  |       | vides a DS1 clock signal for clocking out AIS which is derived from the XCK     |

| 33    | CR7  |       | clock (pin 90).                                                                 |

| 30    | CR8  |       |                                                                                 |

| 28    | CR9  |       |                                                                                 |

| 26    | CR10 |       |                                                                                 |

| 24    | CR11 |       |                                                                                 |

| 22    | CR12 |       |                                                                                 |

| 20    | CR13 |       |                                                                                 |

| 17    | CR14 |       |                                                                                 |

| 15    | CR15 |       |                                                                                 |

| 13    | CR16 |       |                                                                                 |

| 11    | CR17 |       |                                                                                 |

| 9     | CR18 |       |                                                                                 |

| 184   | CR19 |       |                                                                                 |

| 186   | CR20 |       |                                                                                 |

| 188   | CR21 |       |                                                                                 |

| 190   | CR22 |       |                                                                                 |

| 193   | CR23 |       |                                                                                 |

| 195   | CR24 |       |                                                                                 |

| 197   | CR25 |       |                                                                                 |

| 201   | CR26 |       |                                                                                 |

| 203   | CR27 |       |                                                                                 |

| 7     | CR28 |       |                                                                                 |

### DS1 Receive Interfaces

| Pin #            | Name            | I/O/P    | Description                                                                |

|------------------|-----------------|----------|----------------------------------------------------------------------------|

| 63               | DR1             | 0        | Receive Data DS1 Channels 1 - 28. TTL Type III compatible. Demultiplexed   |

| 44               | DR2             |          | DS1 channels. The first DS1 channel corresponds to DR1, while the last DS1 |

| 42               | DR3             |          | channel corresponds to DR28.                                               |

| 40               | DR4             |          |                                                                            |

| 38               | DR5             |          |                                                                            |

| 36               | DR6             |          |                                                                            |

| 34               | DR7             |          |                                                                            |

| 31               | DR8             |          |                                                                            |

| 29               | DR9             |          |                                                                            |

| 27               | DR10            |          |                                                                            |

| 25               | DR11            |          |                                                                            |

| 23               | DR12            |          |                                                                            |

| 21               | DR13            |          |                                                                            |

| 19               | DR14            |          |                                                                            |

| 16               | DR15            |          |                                                                            |

| 14               | DR16            |          |                                                                            |

| 12               | DR17            |          |                                                                            |

| 10               | DR18            |          |                                                                            |

| 8                | DR19            |          |                                                                            |

| 185              | DR20            |          |                                                                            |

| 187              | DR21            |          |                                                                            |

| 189              | DR22            |          |                                                                            |

| 192              | DR23            |          |                                                                            |

| 194              | DR24            |          |                                                                            |

| 196              | DR25            |          |                                                                            |

| 199              | DR26            |          |                                                                            |

| 202              | DR27            |          |                                                                            |

| 6                | DR28            |          |                                                                            |

| Note: I = Input; | O = Output; P = | Power. S | See DC Characteristics section for CMOS and TTL Type definitions.          |

#### **DS1 Transmit Interfaces**

| Pin # | Name       | I/O/P | Description                                                                      |

|-------|------------|-------|----------------------------------------------------------------------------------|

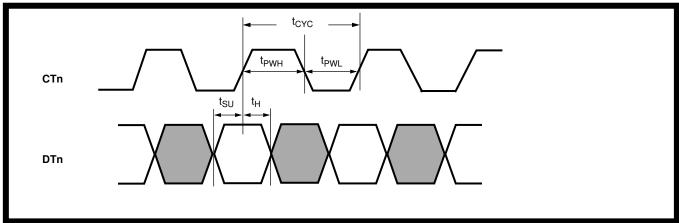

| 175   | CT1        | I     | Transmit DS1 Clocks Channels 1 - 28. TTL Type I compatible. Transmit data        |

| 177   | CT2        |       | is clocked into the MT90737 on positive transitions. The clock for the first DS1 |

| 179   | CT3        |       | channel corresponds to CT1, while the clock for the last DS1 channel corre-      |

| 181   | CT4        |       | sponds to CT28.                                                                  |

| 167   | CT5        |       |                                                                                  |

| 169   | CT6        |       |                                                                                  |

| 171   | CT7        |       |                                                                                  |

| 173   | CT8        |       |                                                                                  |

| 139   | CT9        |       |                                                                                  |

| 141   | CT10       |       |                                                                                  |

| 143   | CT11       |       |                                                                                  |

| 147   | CT12       |       |                                                                                  |

| 130   | CT13       |       |                                                                                  |

| 132   | CT14       |       |                                                                                  |

| 134   | CT15       |       |                                                                                  |

| 136   | CT16       |       |                                                                                  |

|       | (continued |       |                                                                                  |

|       | next page) |       |                                                                                  |

|       |            |       |                                                                                  |

### DS1 Transmit Interfaces

| Pin #                                                                                                                                                                                          | Name                                                                                                                                                                                                                                                        | I/O/P | Description                                                                                                                                         |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| 119<br>121<br>123<br>128<br>111<br>113<br>115<br>117<br>95<br>97<br>99<br>108                                                                                                                  | CT17<br>CT18<br>CT19<br>CT20<br>CT21<br>CT22<br>CT23<br>CT24<br>CT25<br>CT26<br>CT26<br>CT27<br>CT28                                                                                                                                                        | 1     | Transmit DS1 Clocks (continued from previous page).                                                                                                 |

| 176<br>178<br>180<br>182<br>168<br>170<br>172<br>174<br>140<br>142<br>145<br>165<br>131<br>133<br>135<br>137<br>120<br>122<br>127<br>129<br>112<br>114<br>116<br>118<br>96<br>98<br>100<br>109 | DT1<br>DT2<br>DT3<br>DT4<br>DT5<br>DT6<br>DT7<br>DT8<br>DT9<br>DT10<br>DT11<br>DT12<br>DT13<br>DT14<br>DT15<br>DT16<br>DT17<br>DT18<br>DT16<br>DT17<br>DT18<br>DT19<br>DT20<br>DT21<br>DT20<br>DT21<br>DT22<br>DT23<br>DT24<br>DT25<br>DT26<br>DT27<br>DT28 |       | Transmit Data DS1 Channels 1 - 28. TTL Type I compatible. The first DS1 channel corresponds to DT1, while the last DS1 channel corresponds to DT28. |

## **DS3 Interface**

| Pin # | Name  | I/O/P | Description                                                                                                                                                                                                                                                                                                                                                   |

|-------|-------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

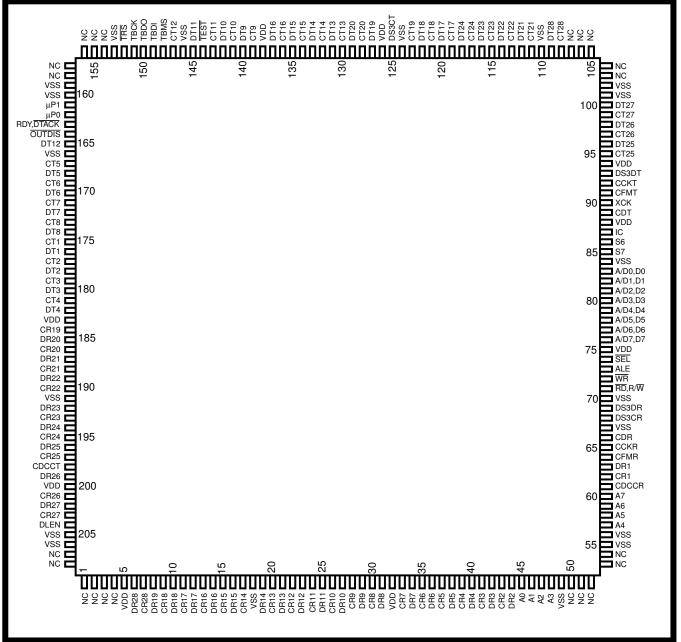

| 68    | DS3CR | I     | <b>DS3 Receive Clock.</b> CMOS compatible. A 44.736 MHz clock that is used to clock DS3 data into the MT90737. This clock is used as the time base for demultiplexing the DS3 data. When the loop timing feature is active (a one written into bit 3 (LPTIME) in 02H), or when the DS3 external transmit clock (XCK) fails, DS3CR becomes the transmit clock. |

| 69    | DS3DR | I     | <b>DS3 Receive Data.</b> CMOS compatible. Receive 44.736 Mbit/s data is clocked into the MT90737 on positive transitions of the receive clock (DS3CR).                                                                                                                                                                                                        |

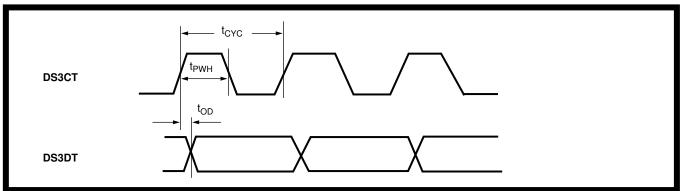

| 125   | DS3CT | 0     | <b>DS3 Transmit Clock.</b> TTL Type IV compatible. A 44.736 MHz clock which is derived from the external transmit clock input signal (XCK). It is used to clock DS3 data from the MT90737.                                                                                                                                                                    |

| 93    | DS3DT | 0     | <b>DS3 Transmit Data.</b> TTL Type IV compatible. Transmit C-bit parity or M13 for-<br>matted DS3 data is clocked out of the MT90737 on positive transitions of the<br>transmit clock (DS3CT).                                                                                                                                                                |

Note: I = Input; O = Output; P = Power. See DC Characteristics section for CMOS and TTL Type definitions.

### **Microprocessor Interface**

| Pin #          | Name                | I/O/P | Description                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |

|----------------|---------------------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

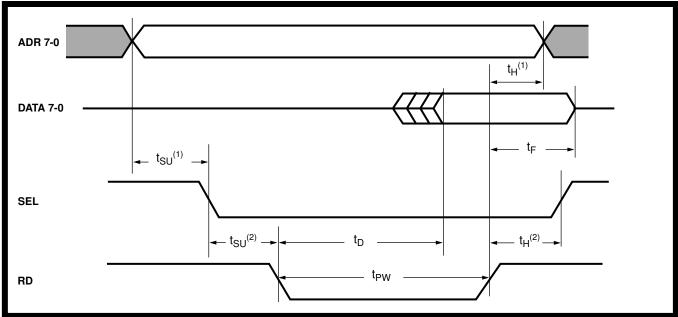

| 60-57<br>48-45 | A(7-4)<br>A(3-0)    | I     | Address Bus (Intel/Motorola). TTL Type II compatible. These are active high address inputs that are used by the microprocessor for accessing the MT90737 registers for a read/write operation. A7 is the most significant bit. These signals are ignored when the multiplexed interface is selected.                                                                                                                                                   |  |  |

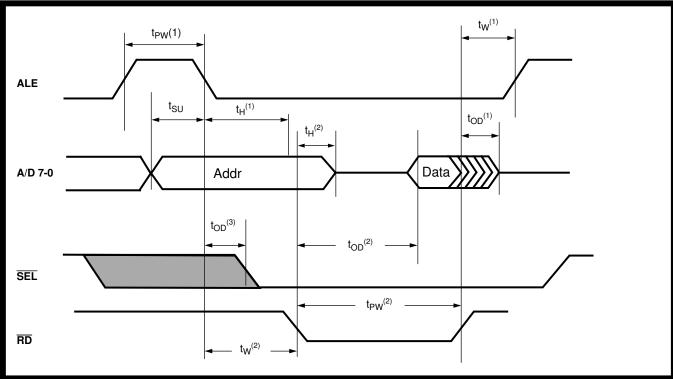

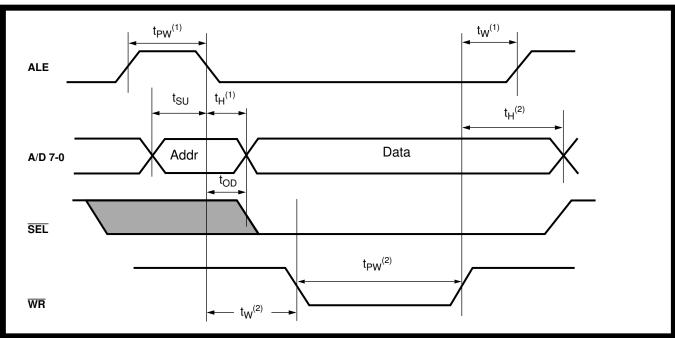

| 76-83          | A/D (7-0)<br>D(7-0) | I/O   | Address/Data Bus (Multiplexed), Data Bus (Intel/Motorola). TTL Type IV compatible. For a multiplexed interface, these bi-directional leads constitute address/data buses for accessing the MT90737 registers. For either the Intel or Motorola interface, these bi-directional leads are used for transferring data. The most significant bit is A/D7 or D7.                                                                                           |  |  |

| 74             | SEL                 | I     | <b>Select.</b> TTL Type I compatible. A low enables data transfers between the microprocessor and the MT90737 registers during a read/write bus cycle.                                                                                                                                                                                                                                                                                                 |  |  |

| 71             | RD<br>R/W           | I     | <b>Read (Intel/Multiplexed) or Read/Write (Motorola).</b> TTL Type I compatible.<br>Intel/Multiplexed - An active low signal generated by the microprocessor for<br>reading the MT90737 register locations. Motorola - An active high signal gen-<br>erated by the microprocessor for reading the MT90737 register locations. An<br>active low signal is used to write to the MT90737 register locations.                                              |  |  |

| 73             | ALE                 | I     | Address Latch Enable (Multiplexed). TTL Type I compatible. An active high enable signal generated by the microprocessor. The falling transition is used to store an address during a read/write bus cycle.                                                                                                                                                                                                                                             |  |  |

| 72             | WR                  | I     | Write (Intel/Multiplexed). TTL Type I compatible. An active low signal gener-<br>ated by the Intel/Multiplexed microprocessor for writing to the MT90737 regis-<br>ter locations. Not used for the Motorola microprocessor interface.                                                                                                                                                                                                                  |  |  |

| 163            | RDY<br>DTACK        | 0     | <b>Ready (Intel) or Data Transfer Acknowledge (Motorola Mode).</b> TTL Type IV compatible. Intel - The MT90737 is always Ready. Connection to an Intel Microprocessor is optional. If connected, a pull-up resistor is required. Motorola - During a read cycle, a low signal indicates the information on the data bus is valid. During a write cycle, a low signal acknowledges the acceptance of data. A pull-up resistor is required for this pin. |  |  |

## Microprocessor Interface

| Pin #      | Name       | I/O/P | Description                                                                 |                                                                                                                                                 |                                                                            |                                                                                                                                                                                                                      |                                                               |

|------------|------------|-------|-----------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------|

| 162<br>161 | μΡ0<br>μΡ1 | I     |                                                                             | <b>Microprocessor Interface Type Select.</b> TTL Type II compatible. The type of microprocessor interface selected is given in the table below: |                                                                            |                                                                                                                                                                                                                      |                                                               |

|            |            |       |                                                                             | μP1                                                                                                                                             | μP0                                                                        | Interface                                                                                                                                                                                                            |                                                               |

|            |            |       |                                                                             | 0                                                                                                                                               | 0                                                                          | Intel Compatible                                                                                                                                                                                                     |                                                               |

|            |            |       |                                                                             | 0                                                                                                                                               | 1                                                                          | Motorola Compatible                                                                                                                                                                                                  |                                                               |

|            |            |       |                                                                             | 1                                                                                                                                               | 0                                                                          | Multiplexed                                                                                                                                                                                                          |                                                               |

|            |            |       |                                                                             | 1                                                                                                                                               | 1                                                                          | Not Used                                                                                                                                                                                                             |                                                               |

|            |            |       | select, address<br>The Intel compa<br>eight bi-direction<br>The Motorola co | latch enabl<br>atible interfa<br>nal data lea<br>ompatible ir                                                                                   | e, read, a<br>ace (80X8<br>ads, select<br>aterface (6                      | eight bi-directional addrese<br>nd write.<br>6 family) consists of eight<br>t, read, write, and ready.<br>680X0 family) consists of e<br>, select, read/write, and da                                                | address leads,<br>eight address                               |

| 85, 86     | S(7-6)     | Ι     | plexed micropro<br>address straps,<br>of memory. The<br>register is partit  | ocessor inte<br>S7 and S6<br>straps defi<br>ioned as sh                                                                                         | rfaces are<br>, allow the<br>ne the ad<br>nown belo<br>e 2 MSBs<br>6<br>37 | atible. When the Intel, Mote<br>e selected by μP0 and μP <sup>-</sup><br>MT90737 to be partitione<br>dress offset of the device.<br>w. The data register pointe<br>s match the address straps<br>Register<br>Address | I, the two<br>d as a segment<br>The address<br>ed to by the 6 |

| 87         | IC         | -     | Internal Conne                                                              | ction. Kee                                                                                                                                      | o open.                                                                    |                                                                                                                                                                                                                      |                                                               |

### **Receive C-Bit Interface**

| Pin # | Name  | I/O/P | Description                                                                                                                                                                                                                                                                                                                                                                                     |  |

|-------|-------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

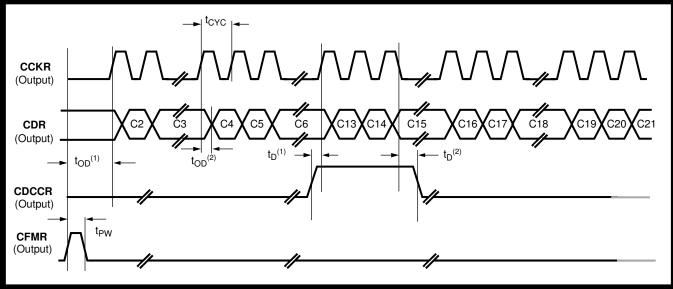

| 65    | CCKR  | 0     | <b>Receive C-Bit Clock.</b> TTL Type IV compatible. A gapped clock signal provided for clocking out the selected receive C-bit data. Data (CDR) is clocked out on positive transitions.                                                                                                                                                                                                         |  |

| 66    | CDR   | 0     | <b>Receive C-Bit Data.</b> TTL Type IV compatible. The following C-bits are provided at this interface. C2, C3, C4, C5, C6, C13, C14, C15, C16, C17, C18, C19, C20, and C21.                                                                                                                                                                                                                    |  |

| 64    | CFMR  | 0     | <b>Acceive C-Bit Framing Pulse.</b> TTL Type IV compatible. This positive framing ulse occurs prior to the C2 bit.                                                                                                                                                                                                                                                                              |  |

| 61    | CDCCR | 0     | <b>Receive Data Link Indication.</b> TTL Type IV compatible. A positive pulse that identifies the location of the three data link C-bits (C13, C14, and C15). The receive C-bit clock (CCKR) may be AND'ed with this signal to provide a gapped data link clock for loading the three C-bits from the C-bit data (CDR) into external circuitry. CDCCR is enabled by placing a high on DLEN pin. |  |

Note: I = Input; O = Output; P = Power. See DC Characteristics section for CMOS and TTL Type definitions.

## Transmit C-Bit Interface

| Pin # | Name  | I/O/P | Description                                                                                                                                                                                                                                                                                                               |  |

|-------|-------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

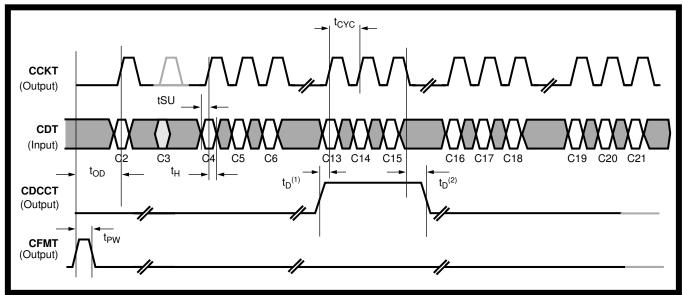

| 92    | CCKT  | 0     | <b>Transmit C-Bit Clock.</b> TTL Type IV compatible. A gapped clock signal provided for clocking in selected transmit C-bit data (CDT). Data is clocked into the MT90737 on positive transitions.                                                                                                                         |  |

| 89    | CDT   | I     | <b>Transmit C-Bit Data.</b> TTL Type I compatible. The transmit gapped clock (CCKT) provided for clocking in the following C-bits: C2, C4, C5, C6, C13, C14, C15, C16, C17, C18, C19, C20, and C21. An unused C-bit should be transmitted as a one.                                                                       |  |

| 91    | CFMT  | 0     | <b>Transmit C-Bit Framing Pulse.</b> TTL Type IV compatible. This positive framing pulse occurs prior to the C2 bit.                                                                                                                                                                                                      |  |

| 198   | CDCCT | 0     | <b>Transmit Data Link Indication.</b> TTL Type IV compatible. A positive pulse that identifies the location of the three data link C-bits (C13, C14, and C15). The transmit C-bit clock (CCKT) may be AND'ed with this signal to provide a gapped data link clock signal. CDCCT is enabled by placing a high on DLEN pin. |  |

## Control Bits

| Pin # | Name   | I/O/P | Description                                                                                                                                                                                                                                                                                                                 |

|-------|--------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 164   | OUTDIS | I     | <b>Outputs Disable.</b> TTL Type II compatible. A low causes all MT90737 outputs and bi-directional signal leads to be set to a high impedance state for test purposes except the CDCCR and CDCCT pins. The CDCCR and CDCCT outputs are controlled by DLEN pin. OUTDIS is provided with an internal pull-up resistor.       |

| 204   | DLEN   | I     | <b>Data Link Enable.</b> TTL Type II compatible. Normally left open. A high enables the transmit and receive data link indication signals, CDCCT and CDCCR. The data link indication signals identify the location of the three data link C-bits (C13, C14, and C15). A low puts CDCCR and CDCCT into high impedance state. |

| 144   | TEST   | 0     | Test Pin. Leave open.                                                                                                                                                                                                                                                                                                       |

Note: I = Input; O = Output; P = Power. See DC Characteristics section for CMOS and TTL Type definitions.

### External Clock

| Pin # | Name | I/O/P | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|-------|------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 90    | ХСК  | I     | <b>External Transmit Clock.</b> CMOS compatible. An external clock having a frequency of 44.736 MHz $\pm$ 20 ppm is required to meet DSX-3 cross-connect requirements. The clock duty cycle should be 50 $\pm$ 5%. The transmit clock is also used to operate the microprocessor interface. The MT90737 monitors this clock for transitions. When a clock failure is detected, the MT90737 automatically switches to the receive clock (DS3CR) for multiplexer and microprocessor operation. Receive loop timing (a one written to bit 3, LPTIME, in 02H) also causes the receive clock to become the transmit clock. |

Note: I = Input; O = Output; P = Power. See DC Characteristics section for CMOS and TTL Type definitions.

## **Boundary Scan Pins**

| Pin # | Name | I/O/P | Description                                                                                                                                                                                                                                                                                                                                                                                  |

|-------|------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 148   | TBMS | I     | <b>Test Boundary Mode Select.</b> TTL Type II compatible. The signal present on this lead is clocked in by the positive transitions of TBCK to control test operations.                                                                                                                                                                                                                      |

| 149   | TBDI | I     | <b>Test Boundary Data Input.</b> TTL Type II compatible. Serial data input clocked in by positive transitions of TBCK as boundary scan test messages.                                                                                                                                                                                                                                        |

| 150   | TBDO | 0     | <b>Test Boundary Data Output.</b> TTL Type IV compatible. Serial data output whose information is clocked out on negative transitions of TBCK. A pull-up resistor is required for this tri-stating pin.                                                                                                                                                                                      |

| 151   | TBCK | I     | <b>Test Boundary Scan Clock.</b> TTL Type II compatible. The input clock for boundary scan testing.                                                                                                                                                                                                                                                                                          |

| 152   | TRS  | I     | <b>Test Boundary Scan Reset.</b> TTL Type II compatible. When a low signal is applied to this pin, the MT90737 Test Access Port (TAP) controller resets and the boundary scan is disabled. The TAP is also reset upon power-up or by holding the TBMS signal lead high for at least five rising clock transitions of TBCK. When the boundary scan feature is not used, TRS must be held low. |

## **Functional Description**

The MT90737 (M13) multiplexes and demultiplexes 28 DS1 signals to and from a DS3 signal in either M13 or C-bit parity mode. In the C-bit parity mode, the MT90737 provides a separate transmit (13 bits) and receives (14 bits) interface for C-bits. The Far End Alarm and Control (FEAC) channel (C3) is accessed via internal memory. The MT90737 has 37 byte registers for software control, performance counters, and alarm reporting. The microprocessor interface is selectable via two external hardware straps. Interface options are Multiplexed and Non-Multiplexed bus types (such as Intel 80X86 and Motorola 680X0 families).

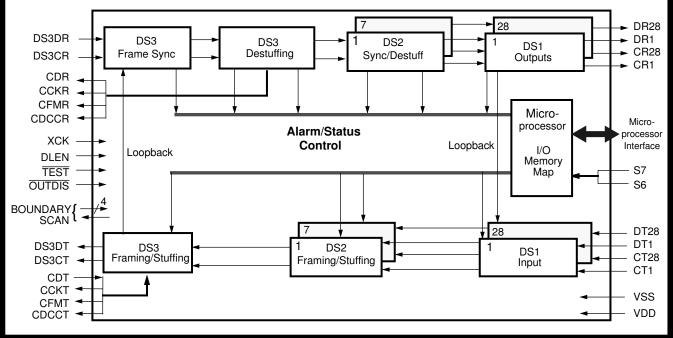

The MT90737 supports Bellcore's TR-TSY-000499, ANSI's T1.107-1988 and supplement T1.107a-1990. Figure 1 shows a functional block diagram of the MT90737.

#### **Multiplex (Transmit)**

In the transmit direction, DS1 transmit data (DTn) is clocked into the MT90737 on positive transitions of the clock input (CTn) for each of the 28 DS1 channels. A DS1 Input Block, which consists of a FIFO and supporting logic, is provided for each DS1 channel. Under software control, the MT90737 can invert the transmit data signals, or the clock signals for all 28 DS1 channels. The data inversion feature provides compatibility with certain T1 line interface devices, while the clock inversion feature allows back-to-back M13 operation.

The DS1 Input Block is also used to insert one of three available idle patterns from a common generator into a DS1 bit stream, under software control. The selection of the idle pattern is common to all 28 DS1 channels. The idle patterns are: a Quasi-Random Sequence (QRS), an Extended Super Frame DS1 (ESF) format with all ones in channels one through 24, and an AIS format (unframed all ones).

Each DS1 signal is bit-multiplexed into the respective DS2 frame, with the stuff bits inserted based on the fill level of an internal FIFO. When the level of the FIFO drops below half full, a stuff bit is inserted into the DS1 bit stream in the DS2 signal. The DS2 signal is formed by combining four DS1 signals. In each DS2 frame there are 287 data bit positions per DS1 channel, one stuff bit per DS1 channel and 24 overhead bits for a total of 1176 bits. The overhead bits are used for framing, X-bit channel and stuff control.

The DS3 signal is partitioned into M-frames of 4760 bits each. The M-frames are divided into seven M-sub-frames having 680 bits each. Each M-subframe is further divided into eight blocks of 85 bits each. Each block uses 84 bits for payload and one bit for frame

overhead. There are 56 overhead bits in each Mframe. the M-frame alignment uses three bits, the Msubframe alignment (F-bits) uses 28 bits, 21 bits are defined as C-bits, two bits are assigned for parity, and two bits are assigned for the X-bit channel.

The DS3 frame is constructed and timed according to the operating mode, i.e., C-bit parity mode or M13 mode.

### C-Bit Parity Mode

In the C-bit parity mode, all seven of the DS2 stuff bits are fixed as stuff, resulting in 7 pseudo DS2 frames of 671 bits per DS2 frame in each DS3 frame, for a DS2 rate of 6.3062723 Mbit/s. Since stuffing always occurs, the 21 C-bits are assigned for other functions, as shown in Figure 2. A C-bit interface is provided for transmitting 13 C-bits (C2, C4, C5, C6, C13, C14, C15, C16, C17, C18, C19, C20, C21). The external transmit C-bit interface consists of a serial data input (CDT), an output clock (CCKT), a data link indicator pulse (CDCCT), and an output framing pulse (CFMT). The data link indicator pulse identifies the location of the three data link bits, C13, C14, and C15. In addition, a control bit (C3CLKI) is provided in the memory map (register 19H) which enables the MT90737 to generate an extra clock cycle in CCKT during the C3 bit time.

Of the eight remaining C-bits, C1 is used as an identification channel; C3 is defined as a Far End Alarm and Control (FEAC) bit; C7, C8, and C9 (CP-bits) are used for C-bit parity; and the remaining three bits, C10, C11, and C12, are used to transmit a Far End Block Error (FEBE) indication. C1 should be set to 1 under C-bit parity mode. The FEAC channel carries alarm or status information from the far-end terminal to the nearend terminal, and is also used to initiate DS3 and DS1 loopbacks at the far-end terminal from the near-end terminal. The CP-bits are used to carry DS3-path parity information for end-to-end parity checking. Since the CP-bits pass through the network unchanged (except in the case of an AIS or CP-bit errors), the DS3 receiver can determine if an error has occurred in an M-frame by computing the contents of the given Mframe and comparing this parity value with the parity received in the CP-bits in the following M-frame. If a received C-bit parity error or framing error is detected, the FEBE bits shall be returned to the transmitting terminal to indicate the error occurrence. Thus, the overall performance of the full-duplex DS3 path, under Cbit parity mode, can be determined at either end or at any place along the path with the FEAC and FEBE signals.

| C1   | C2*  | C3** | C1 = C-bit parity mode                                                                     |

|------|------|------|--------------------------------------------------------------------------------------------|

|      |      |      | C2 = Reserved<br>C3 = Far End Alarm & Control (FEAC)                                       |

| C4*  | C5*  | C6*  | Not defined, set to one                                                                    |

| C7   | C8   | C9   | C-Parity bits (CP-bits)                                                                    |

| C10  | C11  | C12  | Far End Block Error (FEBE)                                                                 |

| C13* | C14* | C15* | Maintenance data link (28 Kbit/s)                                                          |

| C16* | C17* | C18* | Not defined, set to one                                                                    |

| C19* | C20* | C21* | Not defined, set to one                                                                    |

|      |      | •    | ded at the C-bit interface in the C-bit mode the receive C-bit interface in the C-bit mode |

Figure 2 - C-Bit Assignments In C-bit Parity Format

#### M13 Mode

In the M13 mode, fixed DS2 to DS3 stuffing is used for M23 multiplexing at a rate of seven stuffs per every 18 DS3 stuff opportunities. This yields a DS2 frequency of +2.6 ppm above the desired frequency of 6.312 Mbit/s. Adding this to the tolerance of the DS3 clock signal,  $\pm$ 20 ppm, the frequency is still within the  $\pm$ 32 ppm allowed for a DS2 signal.

Other functions, which are common to the C-bit parity and M13 mode, provided by the MT90737 are as follows. Under software control, the MT90737 can generate DS3 idle and AIS signals, and loop back the transmitted DS3 signal to the receiver for test purposes. The MT90737 also provides DS1 loopback capability, and transmit clock failure protection.

#### **Demultiplex (Receive)**

In the receive direction, DS3 data (DS3DR) is clocked into the MT90737 on positive transitions of the DS3 input clock (DS3CR). The DS3 Frame Sync Block searches for and locks to the DS3 frame. The receive DS3 signal is monitored for out of frame, loss of signal, DS3 AIS, DS3 idle signal, P-bit parity, the state of the X-bits, and loss of clock. The DS3 AIS detection mechanism is software selectable, with a choice of six different patterns. These range from full compliance to T1.107/107a to unframed all ones AIS detection. Control bits are also provided in memory which allows all, some of, or none of the DS3 alarms to cause the insertion of AIS into the receive DS1 channels.

In the C-bit parity mode, the C-bits are allocated for network performance. The MT90737 performs Far End Alarm and Control (FEAC) detection, C-bit parity error detection, and Far End Block Error (FEBE) detection. FEAC loopback requests and alarm/status information is provided in the memory map. A receive C-bit interface is provided for extraction of 14 C-bits (C2, C3, C4, C5, C6, C13, C14, C15, C16, C17, C18, C19, C20, and C21). The receive C-bit interface consists of a serial data output (CDR), an output clock signal (CCKR), a framing pulse (CFMR), and a data link indicator pulse (CDCCR). The data link indicator pulse identifies the location of the data link C-bits, C13, C14, and C15.

In the M13 mode, destuffing from DS3 to DS2 is performed based on the states of the C-bits in the DS3 subframes. If two or three of the C-bits in a subframe are ones, the associated stuff bit is interpreted as being a stuff bit and is removed from the data stream and discarded.

The MT90737 synchronizes and extracts the 28 DS1 channels from the seven DS2 channels. Each of the DS2 channels is monitored for out of frame. The MT90737 may generate AIS in each of the DS1 signal tributaries corresponding to the DS2 channel(s) that lost frame, depending on the DS1 AIS alarm insertion control bits. DS2 to DS1 destuffing is based on the states of the three C-bits in each DS2 subframe. If two or three of the C-bits in one of the DS2 subframes are ones, the stuff bit for that subframe is discarded. In the M13 mode, the DS2 C-bits or stuffing bits are also used for DS1 remote loopback requests. The MT90737 provides control bits in the memory map for selecting the remote loopback detection mechanism. The destuffing operation is still active during loopback request and operation. In addition to DS2 synchronization, destuffing, and remote loopback detection, the MT90737 also extracts the X-bits from seven DS2 frames.

An option is provided that allows the received or transmitted DS1 channels to be monitored for loss of signal. Receive data for each of the DS1 channels (DRn) is clocked out of the MT90737 on positive transitions of the associated clock signal (CRn). In addition, the MT90737 provides a stable DS1 clock signal for the data signals received during AIS periods.

ter must be masked by software to avoid reading incorrect data.

### **Register Bit Map**

The MT90737 memory map consists of control bits, alarms (non-latched and latched), and counters accessed by a microprocessor read/write cycle. The unused bit positions (shown below shaded) in a regis-

| Address<br>(Hex) | Mode* | Bit7   | Bit6    | Bit5    | Bit4    | Bit3       | Bit2             | Bit1        | Bit0    |

|------------------|-------|--------|---------|---------|---------|------------|------------------|-------------|---------|

| 00               | R     | R3LOS  | R3OOF   | R3AIS   | R3IDL   | R3CKF      | T3CKF            | XR2         | XR1     |

| 01               | R/W   |        |         | T3AIS   | T3IDL   | FEBE       | PBITE            | PBITE CBITE |         |

| 02               | R/W   | IDLB   | IDLA    | TEST1   | 3LBK    | LPTIME     | INVCK            | 1INV        | MODE    |

| 03               | R     | CBIT1  | DS2OOF7 | DS2OOF6 | DS2OOF5 | DS2OOF4    | DS2OOF3          | DS2OOF2     | DS2OOF1 |

| 04               | R     | FB7    | FB6     | FB5     | FB4     | FB3        | FB2              | FB1         | FB0     |

| 05               | R     | CP7    | CP6     | CP5     | CP4     | CP3        | CP2              | CP1         | CP0     |

| 06               | R     | PP7    | PP6     | PP5     | PP4     | PP3        | PP2              | PP1         | PP0     |

| 07               | R/W   | EXEC   | CON/DIS | LBSEL   | D22     | D21        | D20              | D11         | D10     |

| 08               | R     | LBALL  | LB25    | LB21    | LB17    | LB13       | LB9              | LB5         | LB1     |

| 09               | R     | LBDS3  | LB26    | LB22    | LB18    | LB14       | LB10             | LB6         | LB2     |

| 0A               | R     |        | LB27    | LB23    | LB19    | LB15       | LB11             | LB7         | LB3     |

| 0B               | R     |        | LB28    | LB24    | LB20    | LB16       | LB12             | LB8         | LB4     |

| 0C               | R     |        | LOS25   | LOS21   | LOS17   | LOS13      | LOS9             | LOS5        | LOS1    |

| 0D               | R     |        | LOS26   | LOS22   | LOS18   | LOS14      | LOS10            | LOS6        | LOS2    |

| 0E               | R     |        | LOS27   | LOS23   | LOS19   | LOS15      | LOS11            | LOS7        | LOS3    |

| 0F               | R     |        | LOS28   | LOS24   | LOS20   | LOS16      | LOS12            | LOS8        | LOS4    |

| 10               | R/W   |        | IDL25   | IDL21   | IDL17   | IDL13      | IDL9             | IDL5        | IDL1    |

| 11               | R/W   |        | IDL26   | IDL22   | IDL18   | IDL14      | IDL10            | IDL6        | IDL2    |

| 12               | R/W   |        | IDL27   | IDL23   | IDL19   | IDL15      | IDL11            | IDL7        | IDL3    |

| 13               | R/W   |        | IDL28   | IDL24   | IDL20   | IDL16      | IDL12            | IDL8        | IDL4    |

| 14               | R     |        | R2X7    | R2X6    | R2X5    | R2X4       | R2X3             | R2X2        | R2X1    |

| 15               | R/W   |        | T2X7    | T2X6    | T2X5    | T2X4       | T2X3             | T2X2        | T2X1    |

| 16               | R(L)  | R3LOS  | R3OOF   | R3AIS   | R3IDL   | R3CKF      | T3CKF            | XR2         | XR1     |

| 17               | R(L)  | CERROR | DS2OOF7 | DS2OOF6 | DS2OOF5 | DS2OOF4    | DS2OOF3          | DS2OOF2     | DS2OOF1 |

| 18               |       | TEST   | TEST    | TEST    | TEST    | TEST       | TEST             | TEST        | TEST    |

| 19               | R/W   | C3CLKI | TEST    | TEST    | TEST    | TEST       | TEST             | TEST        | TEST    |

| 1A               |       | TEST   | TEST    | TEST    | TEST    | TEST       | TEST             | TEST        | TEST    |

| 1B               | R     | FME7   | FME6    | FME5    | FME4    | FME3       | FME2             | FME1        | FME0    |

| 1C               | R/W   | EXEC   | CONT/10 | TFEAC6  | TFEAC5  | TFEAC4     | TFEAC3           | TFEAC2      | TFEAC1  |

| 1D               | R     | FIDL   | NEW     | RFEAC6  | RFEAC5  | RFEAC4     | RFEAC3           | RFEAC2      | RFEAC1  |

| 1E               | R/W   | EXEC   | CON/DIS |         | LLB22   | LLB21      | LLB20            | LLB11       | LLB10   |

| 1F**             | R/W   |        |         |         |         | n Register |                  |             |         |

| 20               | R/W   | 1TRIST | 1LOSSEL | 1TAIS1  | 1TAIS0  | 1LBV3      | 1LBV2            | 1LBV1       | 1LBV0   |

| 21               | R/W   |        |         |         | R3AIS2  | R3AIS1     | R3AIS0 T3AIS1 T3 |             | T3AIS0  |

| 22               | R     | C1BZ7  | C1BZ6   | C1BZ5   | C1BZ4   | C1BZ3      | C1BZ2            | C1BZ1       | C1BZ0   |

| 23               | R     | ME7    | ME6     | ME5     | ME4     | ME3        | ME2              | ME1         | ME0     |

| 24               | R(L)  | AISX=1 | AISC=0  | TEST    | TEST    | TEST       | TEST             |             | SEF     |

\*Read/write (R/W); Read only (R); Read only - latched register R(L).

\*\*To initialize the MT90737, writing F0H followed by 00H to this location resets the entire device.

## **Register Bit Map Definitions**

| Addr | Bit | Symbol | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|------|-----|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 00   | 7   | R3LOS  | <b>Receive DS3 Loss of Signal.</b> A receive LOS alarm occurs (R3LOS is set to 1) when the incoming DS3 data (DS3DR) is stuck low for more than 1022 clock cycles (DS3CR). Recovery occurs (R3LOS is reset to 0) when two or more ones are detected in the incoming data bit stream. This bit position is unlatched.                                                                                                                                                                                                                      |

|      | 6   | R3OOF  | <b>Receive DS3 Out of Frame.</b> A receive OOF alarm occurs (R3OOF is set to 1) when three out of 16 F-bits are in error in a sliding window of 16 bits, or one or more M-bits are in error in two consecutive frames. Recovery occurs (R3OOF is reset to 0) when the F-bits pattern of 1001 and the M-bits of 010 are detected for two consecutive frames. Recovery takes approximately 0.95 milliseconds, worst case. This bit position is unlatched. An OOF also inhibits the performance counters (04H, 05H, 06H, 1BH, 22H, and 23H). |

|      | 5   | R3AIS  | <b>Receive AIS Alarm Indication Signal.</b> The MT90737 can detect one of six possible DS3 AIS's including the ANSI's standard AIS pattern. An 1 in R3AIS indicates a receive AIS has been detected. The pattern of AIS is selected by the states written to the three R3AISn bits in register 21H. R3AIS bit position is unlatched. When the MT90737 is configured to detect one of the framed AIS signals, the R3OOF (bit 6 of this register) should be examined to ensure that the MT90737 is detecting DS3 frame.                     |

|      | 4   | R3IDL  | <b>Receive DS3 Idle Pattern Signal.</b> A DS3 idle pattern signal has the valid M-bit, F-<br>bit, and P-bit channels. The information bits are a 1100 sequence that starts with<br>11 after each M-bit, F-bit, X-bit, P-bit, and C-bit channels. The C-bits (C7, C8, and<br>C9) in M-subframe 3 are set to zero.                                                                                                                                                                                                                          |

|      |     |        | A valid received DS3 idle signal is detected when the MT90737 detects zeros for C7, C8, and C9 in subframe 3 and the 1100 sequence. The 1100 pattern sequence is searched on a per DS3 frame basis. The MT90737 can tolerate up to and including 5 errored 4 bit groups of the 1100 pattern per DS3 frame and still recognize the 1100 pattern as valid. If the MT90737 detects 6 or more errored 4 bit groups of the 1100 pattern per DS3 frame the MT90737 will exit the R3IDL state. This bit position is unlatched.                   |

|      |     |        | A DS3 idle signal as defined in ANSI T1.107a-1990 is being received by the MT90737 device if this bit (R3IDL), bit 1 (XR2) and bit 0 (XR1) of this register are all set to 1.                                                                                                                                                                                                                                                                                                                                                             |

|      | 3   | R3CKF  | <b>Receive DS3 Clock Failure.</b> A receive DS3 clock failure alarm occurs (R3CKF is set to 1) when the receive clock (DS3CR) is stuck high or low for 30-100 DS3 clock periods. The demultiplexer does not function when the receive clock is lost. Recovery occurs on the first clock transition. This bit position is unlatched.                                                                                                                                                                                                       |

|      | 2   | T3CKF  | <b>Transmit DS3 Clock Failure.</b> A transmit DS3 clock failure alarm occurs (T3CKF is set to 1) when the transmit input clock (XCK) is stuck high or low for 30-100 DS3 clock periods. A failure causes the receive clock to become the transmit clock. This permits the MT90737 microprocessor interface and multiplexer to function. Recovery occurs when the first clock transition is detected.                                                                                                                                      |

|      | 1   | XR2    | <b>Receive DS3 X-bit Number 2.</b> This bit position indicates the receive state of X2. This bit position is updated each frame.                                                                                                                                                                                                                                                                                                                                                                                                          |

|      | 0   | XR1    | <b>Receive DS3 X-bit Number 1.</b> This bit position indicates the receive state of X1. This bit position is updated each frame.                                                                                                                                                                                                                                                                                                                                                                                                          |

| Addr | Bit | Symbol | Description                                                                                                                                                                                                                                                                                                                                                                                                               |

|------|-----|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 01   | 7,6 | -      | Not Used.                                                                                                                                                                                                                                                                                                                                                                                                                 |

|      | 5   | T3AIS  | <b>Transmit DS3 Alarm Indication Signal.</b> A one causes the MT90737 to transmit a DS3 AIS. The type of AIS sent is determined by the states written into bit 1 (T3AIS1) and bit 0 (T3AIS0) in register 21H. To terminate DS3 AIS transmission T3AIS needs to be reset to zero.                                                                                                                                          |

|      | 4   | T3IDL  | <b>Transmit DS3 Idle Signal.</b> To transmit a DS3 idle signal, a one must be written to T3IDL (bit 4) and XT (bit 0) of this register (01H), in addition, bit 0 (T3AIS0) and bit 1 (T3AIS1) of register 21H must be set to zero.                                                                                                                                                                                         |

|      | 3   | FEBE   | <b>Transmit Far End Block Error.</b> A one causes the MT90737 to transmit a single FEBE error indication (C10, C11, and C12 equal to 0) in the next DS3 frame. To send an additional FEBE indication, the microprocessor must first write a zero before writing another one to this bit.                                                                                                                                  |

|      | 2   | PBITE  | <b>Transmit P-Bit Parity Error.</b> A one causes the MT90737 to transmit a single P-bit parity error in the next DS3 frame. The P-bit error is transmitted by inverting the value of the two calculated bits. To send an additional error, the microprocessor must first write a zero before writing another one to this bit.                                                                                             |

|      | 1   | CBITE  | <b>Transmit C-Bit Parity Error.</b> A one causes the MT90737 to transmit a single C-bit parity error in the next available DS3 frame when the MT90737 is operating in the C-bit parity mode. The C-bit error is introduced by inverting the calculated C-bit parity bits in subframe 3 (C7, C8, and C9). To send an additional error, the micro-processor must first write a zero before writing another one to this bit. |

|      | 0   | ХТ     | <b>Transmit X-Bits.</b> The X-bits may be used to transmit a yellow alarm or may be used as a low speed signaling channel. A one or zero causes the MT90737 to transmit a one or zero for both X1 and X2. Not: Set to 1 when transmitting DS3 idle signal (see T3IDL in this register 01H).                                                                                                                               |

| Addr | Bit    | Symbol             | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|------|--------|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 02   | 7<br>6 | IDLB<br>IDLA       | <b>DS1 Idle Code Selection.</b> Three types of DS1 idle codes are provided according to the table given below. A selected idle code is common to all DS1 channels selected. One or more transmitted DS1 channels can be selected by writing a one in IDLn register locations 10, 11, 12, or 13 Hex, provided register 1E Hex has not selected these DS1 channels for loopback.                                                                                                                                                          |

|      |        |                    | IDLBIDLADS1 Idle Code Selected00Quasi-Random Signal (2 <sup>20</sup> - 1 QRS) including zero suppression.10Framed Extended Super Frame (ESF) signal format which consists<br>of a Framing Pattern Sequence of 001011 pattern, CRC-6 pattern,<br>and ones in the 64kbit/s channels 1 through 24.X1Unframed all ones signal (AIS).                                                                                                                                                                                                        |

|      | 5      | TEST1              | <b>Reserved for Testing Purposes.</b> A zero must be written into this bit position for normal operation.                                                                                                                                                                                                                                                                                                                                                                                                                               |

|      | 4      | 3LBK               | <b>DS3 Line Loopback.</b> A one disables the DS3 receive input and causes the DS3 transmit output to be looped back as receive data. Transmit data is provided at the output (DS3DT). A zero allows MT90737 to be in normal operation.                                                                                                                                                                                                                                                                                                  |

|      | 3      | LPTIME             | <b>Receive Loop Timing.</b> A one disables the transmit clock input (XCK), and causes the DS3 receive clock to become the DS3 transmit clock. If the DS3 receive clock fails in this mode, the MT90737 switches over to the transmit clock, and the demultiplexer becomes inoperative, however, the multiplexer and microprocessor interface continue to function.                                                                                                                                                                      |

|      | 2      | INVCK              | <b>Invert DS1 Transmit Clocks.</b> A one causes all transmit DS1 clock inputs (CTn) to be inverted. This is provided for back-to-back M13 operation.                                                                                                                                                                                                                                                                                                                                                                                    |

|      | 1      | 1INV               | <b>Invert DS1 Transmit Data.</b> A one causes the transmit data inputs for all DS1 channels (DTn) to be inverted.                                                                                                                                                                                                                                                                                                                                                                                                                       |

|      | 0      | MODE               | <b>Operating Mode.</b> A one enables the MT90737 to operate in the M13 mode as specified in Bellcore TR-TSY-000009, and the ANSI T1.107-1988 standard. A zero enables the MT90737 to operate in the C-bit parity mode as specified in the ANSI T1.107a-1990, supplement to ANSI T1.107-1988.                                                                                                                                                                                                                                            |

| 03   | 7      | CBIT1              | <b>C-bit Number 1.</b> This bit is updated each frame with the state of the received C1. The C1 bit is used to identify the DS3 application according to the table given below.                                                                                                                                                                                                                                                                                                                                                         |

|      |        |                    | C1 ValueApplicationRandomM13 formatAll 1sC-bit parity formatIn addition, the number of C1bits equal to zero is counted by the C1 Bit ZeroCounter (C1BZn) in 22 Hex.                                                                                                                                                                                                                                                                                                                                                                     |

|      | 6-0    | DS2OOFn<br>(n=7-1) | <b>DS2 Out of Frame Alarm Indication.</b> A one in bits 6-0 corresponds to an out of frame alarm for the respective DS2 channel (7-1). A DS2 OOF occurs when two out of four consecutive DS2 framing bits are in error. A DS2 OOF for a DS2 channel causes AIS to be inserted into its four DS1 channels. Recovery is based on searching for the correct DS2 framing pattern (0101). Once the framing pattern is found, one more frame is used to acquire alignment. Recovery takes approximately 6.8 milliseconds, worst case average. |

| Addr | Bit | Symbol         | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|------|-----|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 04   | 7-0 | FBn<br>(n=7-0) | <b>FEBE Performance Counter/DS3 F&amp;M Bit Error Counter.</b> This performance counter counts the number of FEBEs received since the last read cycle in the C-bit parity mode. A FEBE indication occurs when C10, C11, or C12 is received equal to zero in a DS3 frame. The counter is protected from overflow by stopping at the maximum count of 255 until read. The counter is protected during the period of a microprocessor read cycle and when the MT90737 updates the counter. When this occurs, the incoming error count indication is held until the counter is read and cleared. Afterwards, the counter increments. Only the indication of one error count is held during the microprocessor read and the counter update. The counter is inhibited during DS3 loss of signal or out of frame times, and is cleared on a microprocessor read cycle. |

|      |     |                | have been received in error since the last read cycle.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 05   | 7-0 | CPn<br>(n=7-0) | <b>C-Bit Parity Performance/Number of Frames Counter.</b> In the C-bit parity mode, this counter counts the number of C-bit parity errors received since the last read cycle. The counter is protected from overflow by stopping at the maximum count of 255 until read. The counter is protected during the period of a microprocessor read cycle and when the MT90737 updates the counter. When this occurs, the incoming error count indication is held until the counter is read and cleared. Afterwards, the counter increments. Only the indication of one error count is held during the microprocessor read and the counter update. The counter is inhibited during DS3 loss of signal or out of frame times, and is cleared on a microprocessor read cycle.                                                                                            |

| 06   | 7-0 | PPn<br>(n=7-0) | <b>P-Bit Parity Performance Counter.</b> This counter counts the number of P-bit parity errors received since the last read cycle. This performance count is valid in either operating mode. The counter is protected from overflow by stopping at the maximum count of 255 until read. The counter is protected during the period of a micro-processor read cycle and when the MT90737 updates the counter. When this occurs, the incoming error count indication is held until the counter is read and cleared. Afterward, the counter increments. Only the indication of one error count is held during the microprocessor read and the counter update. The counter is inhibited during DS3 loss of signal or out of frame times, and is cleared on a microprocessor read cycle.                                                                             |