# MX25L6406E

# DATASHEET

# Contents

| FEATURES                                                                 | 5  |

|--------------------------------------------------------------------------|----|

| GENERAL DESCRIPTION                                                      | 6  |

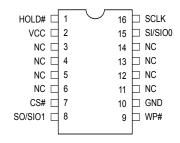

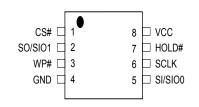

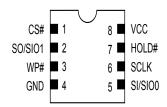

| PIN CONFIGURATIONS                                                       | 7  |

| PIN DESCRIPTION                                                          | 7  |

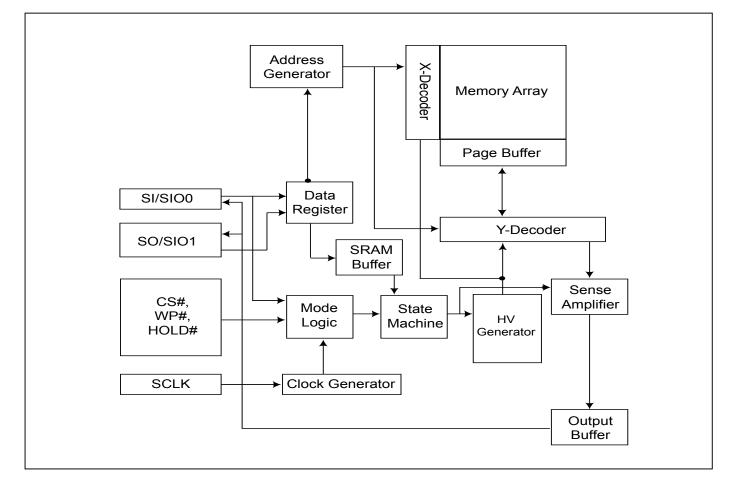

| BLOCK DIAGRAM                                                            | 8  |

| MEMORY ORGANIZATION                                                      | 9  |

| Table 1. Memory Organization                                             | 9  |

| DEVICE OPERATION                                                         | 10 |

| Figure 1. Serial Modes Supported                                         |    |

| DATA PROTECTION                                                          | 11 |

| Table 2. Protected Area Sizes                                            | 12 |

| Table 3. 512 bit Secured OTP Definition                                  |    |

| HOLD FEATURES                                                            | 13 |

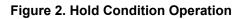

| Figure 2. Hold Condition Operation                                       | 13 |

| COMMAND DESCRIPTION                                                      | 14 |

| Table 4. COMMAND DEFINITION                                              | 14 |

| (1) Write Enable (WREN)                                                  | 15 |

| (2) Write Disable (WRDI)                                                 | 15 |

| (3) Read Status Register (RDSR)                                          | 15 |

| (4) Write Status Register (WRSR)                                         | 16 |

| Table 5. Protection Modes                                                | 17 |

| (5) Read Data Bytes (READ)                                               |    |

| (6) Read Data Bytes at Higher Speed (FAST_READ)                          |    |

| (7) Dual Output Mode (DREAD)                                             |    |

| (8) Sector Erase (SE)                                                    |    |

| (9) Block Erase (BE)                                                     | 19 |

| (10) Chip Erase (CE)                                                     | 19 |

| (11) Page Program (PP)                                                   | 19 |

| (12) Deep Power-down (DP)                                                | 20 |

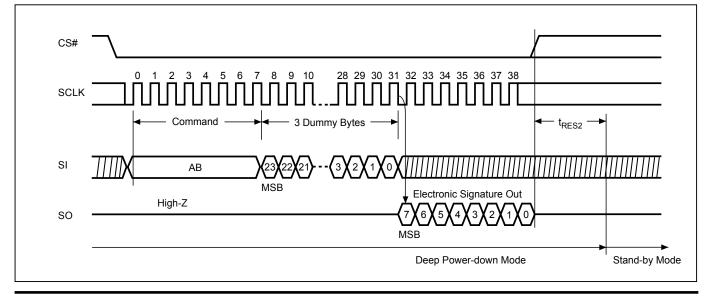

| (13) Release from Deep Power-down (RDP), Read Electronic Signature (RES) | 20 |

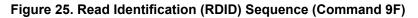

| (14) Read Identification (RDID)                                          | 21 |

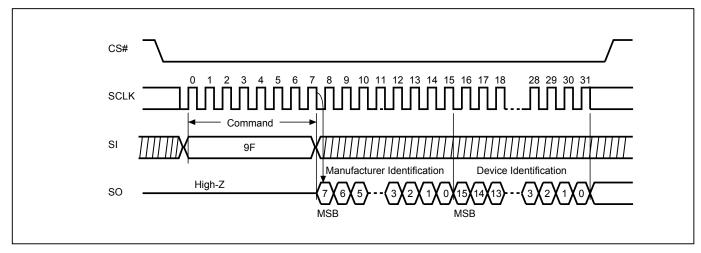

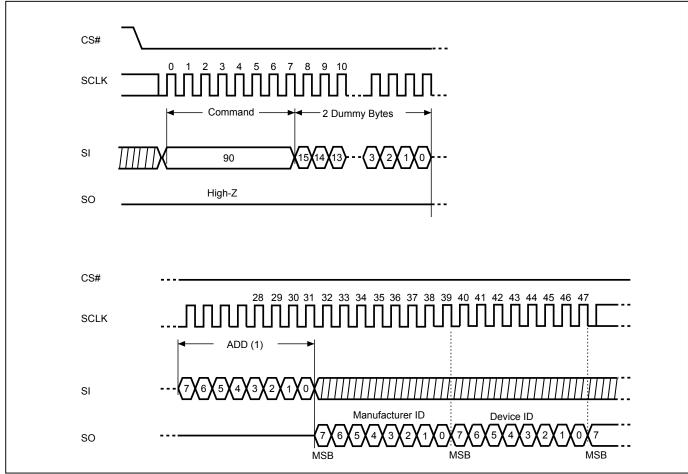

| (15) Read Electronic Manufacturer ID & Device ID (REMS)                  | 21 |

| Table 6. ID DEFINITIONS                                                  | 22 |

| (16) Enter Secured OTP (ENSO)                                            | 22 |

| (17) Exit Secured OTP (EXSO)                                             | 22 |

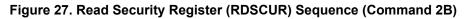

| (18) Read Security Register (RDSCUR)                                     | 23 |

| Table 7. SECURITY REGISTER DEFINITION                                    | 23 |

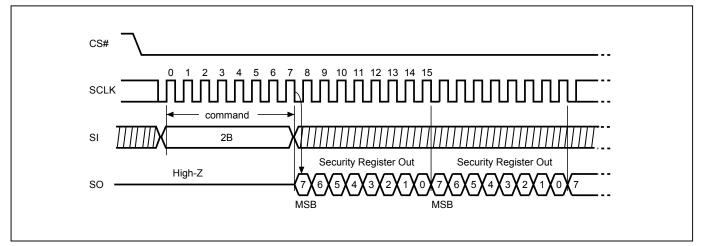

| (19) Write Security Register (WRSCUR)                                    | 23 |

| POWER-ON STATE                                                                             | 24         |

|--------------------------------------------------------------------------------------------|------------|

| ELECTRICAL SPECIFICATIONS                                                                  | 25         |

| ABSOLUTE MAXIMUM RATINGS                                                                   | 25         |

| Figure 3.Maximum Negative Overshoot Waveform                                               | 25         |

| CAPACITANCE TA = 25°C, f = 1.0 MHz                                                         |            |

| Figure 4. Maximum Positive Overshoot Waveform                                              | 25         |

| Figure 5. INPUT TEST WAVEFORMS AND MEASUREMENT LEVEL                                       |            |

| Figure 6. OUTPUT LOADING                                                                   |            |

| Table 8. DC CHARACTERISTICS                                                                | 27         |

| Table 9. AC CHARACTERISTICS                                                                |            |

| Timing Analysis                                                                            | 29         |

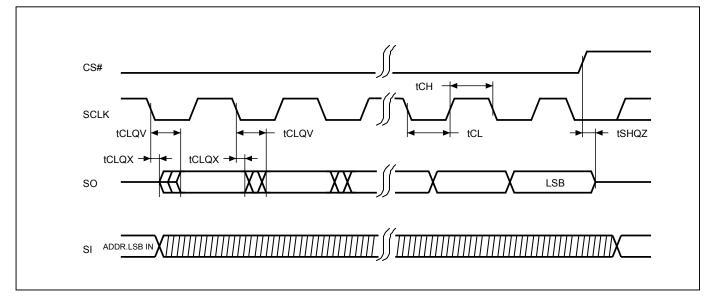

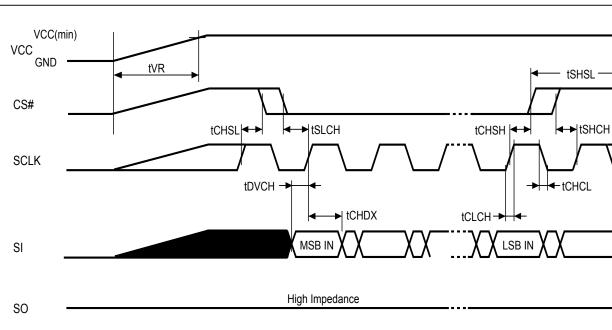

| Figure 7. Serial Input Timing                                                              |            |

| Figure 8. Output Timing                                                                    |            |

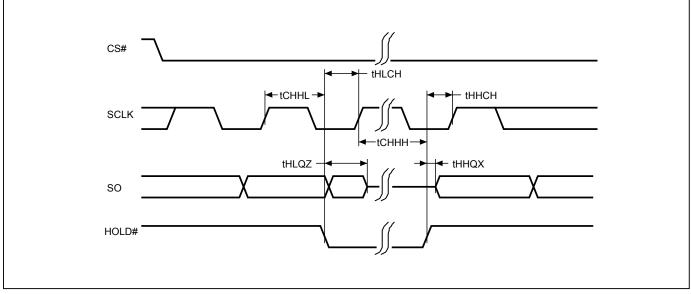

| Figure 9. Hold Timing                                                                      |            |

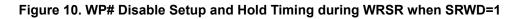

| Figure 10. WP# Disable Setup and Hold Timing during WRSR when SRWD=1                       |            |

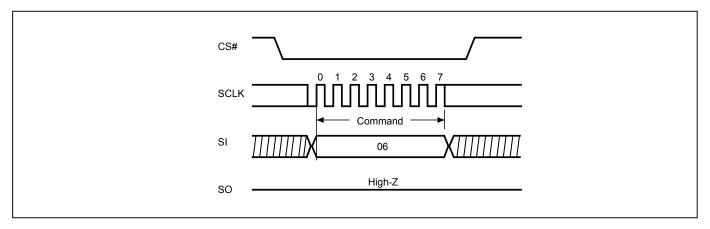

| Figure 11. Write Enable (WREN) Sequence (Command 06)                                       |            |

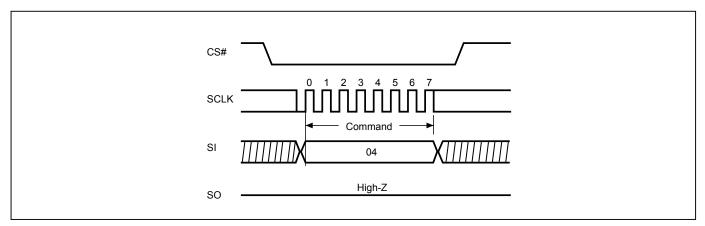

| Figure 12. Write Disable (WRDI) Sequence (Command 04)                                      |            |

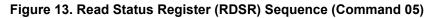

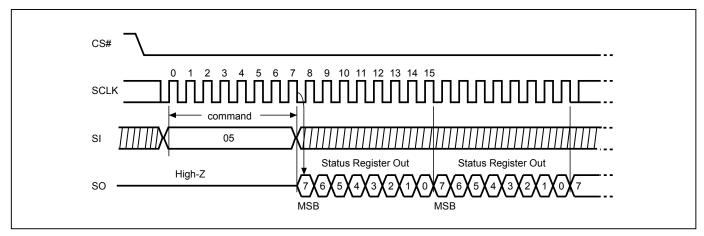

| Figure 13. Read Status Register (RDSR) Sequence (Command 05)                               |            |

| Figure 14. Write Status Register (WRSR) Sequence (Command 01)                              |            |

| Figure 15. Read Data Bytes (READ) Sequence (Command 03)                                    |            |

| Figure 16. Read at Higher Speed (FAST_READ) Sequence (Command 0B)                          |            |

| Figure 17. Dual Output Read Mode Sequence (Command 3B)                                     |            |

| Figure 18. Sector Erase (SE) Sequence (Command 20)                                         |            |

| Figure 19. Block Erase (BE) Sequence (Command 52 or D8)                                    |            |

| Figure 20. Chip Erase (CE) Sequence (Command 60 or C7)                                     |            |

| Figure 21. Page Program (PP) Sequence (Command 02)                                         |            |

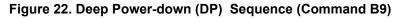

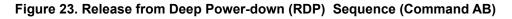

| Figure 22. Deep Power-down (DP) Sequence (Command B9)                                      |            |

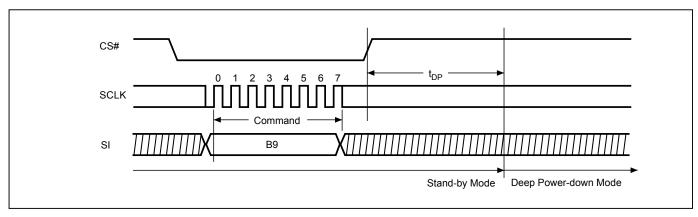

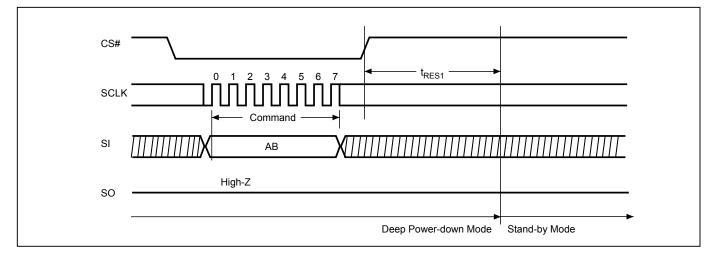

| Figure 23. Release from Deep Power-down (RDP) Sequence (Command AB)                        |            |

| Figure 24. Release from Deep Power-down and Read Electronic Signature (RES) Sequence (Comn | nand AB)36 |

| Figure 25. Read Identification (RDID) Sequence (Command 9F)                                |            |

| Figure 26. Read Electronic Manufacturer & Device ID (REMS) Sequence (Command 90)           |            |

| Figure 27. Read Security Register (RDSCUR) Sequence (Command 2B)                           |            |

| Figure 28. Write Security Register (WRSCUR) Sequence (Command 2F)                          |            |

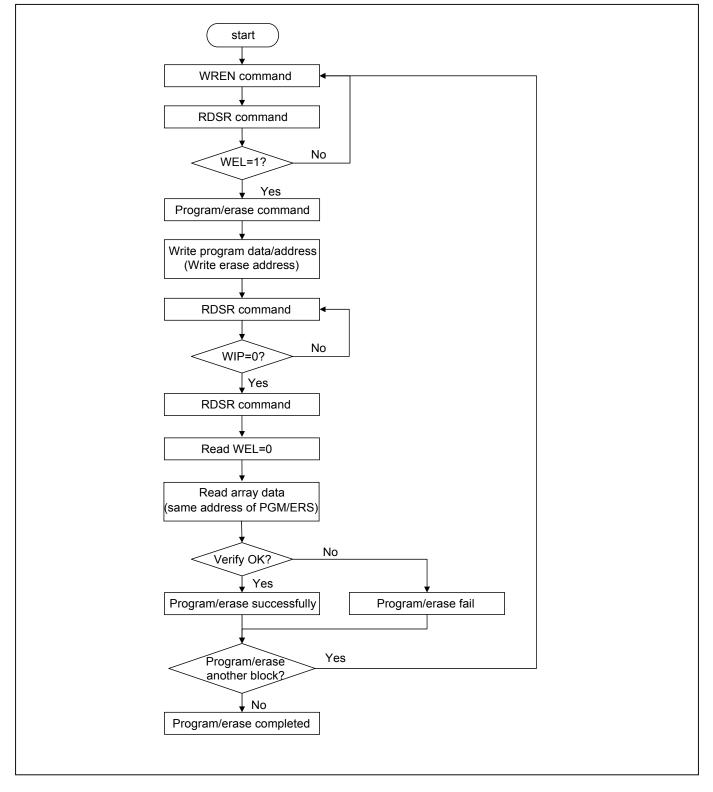

| Figure 29. Program/ Erase flow with read array data                                        |            |

| Figure 30. Power-up Timing                                                                 |            |

| Table 10. Power-Up Timing                                                                  |            |

| OPERATING CONDITIONS                                                                       | 41         |

| Figure 31. AC Timing at Device Power-Up                                                    | 41         |

| Figure 32. Power-Down Sequence                                                             |            |

| ERASE AND PROGRAMMING PERFORMANCE | 43 |

|-----------------------------------|----|

| DATA RETENTION                    |    |

| LATCH-UP CHARACTERISTICS          |    |

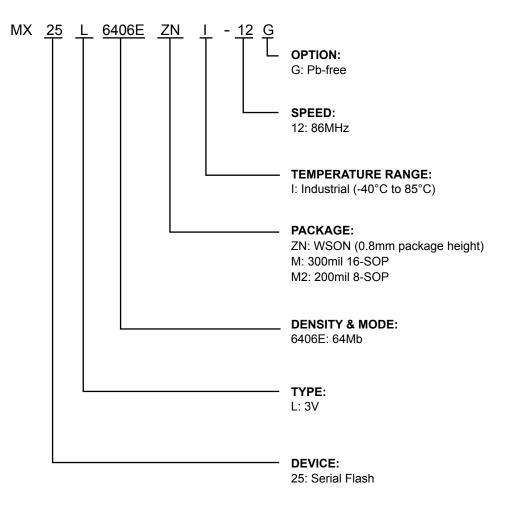

| ORDERING INFORMATION              |    |

| PART NAME DESCRIPTION             |    |

| PACKAGE INFORMATION               |    |

| REVISION HISTORY                  |    |

|                                   |    |

# MX25L6406E

# 64M-BIT [x 1 / x 2] CMOS SERIAL FLASH

# FEATURES

#### GENERAL

- Single Power Supply Operation

- 2.7 to 3.6 volt for read, erase, and program operations

- · Serial Peripheral Interface compatible -- Mode 0 and Mode 3

- 67,108,864 x 1 bit structure or 33,554,432 x 2 bits (Dual Output mode) structure

- 2048 Equal Sectors with 4K byte each

Any Sector can be erased individually

- 128 Equal Blocks with 64K byte each

- Any Block can be erased individually

- Program Capability

- Byte base

- Page base (256 bytes)

- Latch-up protected to 100mA from -1V to Vcc +1V

#### PERFORMANCE

- High Performance

- Fast access time: 86MHz serial clock

- Serial clock of Dual Output mode : 80MHz

- Fast program time: 1.4ms(typ.) and 5ms(max.)/page

- Byte program time: 9us (typical)

- Fast erase time: 60ms(typ.) /sector ; 0.7s(typ.) /block

- Low Power Consumption

- Low active read current: 25mA(max.) at 86MHz

- Low active programming current: 20mA (max.)

- Low active erase current: 20mA (max.)

- Low standby current: 50uA (max.)

- Deep power-down mode 5uA (typical)

- Typical 100,000 erase/program cycles

- · 20 years of data retention

## SOFTWARE FEATURES

- Input Data Format

- 1-byte Command code

- Advanced Security Features

- Block lock protection

The BP3~BP0 status bit defines the size of the area to be software protection against program and erase instructions

- Additional 512 bit secured OTP for unique identifier

- Auto Erase and Auto Program Algorithm

- Automatically erases and verifies data at selected sector

- Automatically programs and verifies data at selected page by an internal algorithm that automatically times the program pulse widths (Any page to be programed should have page in the erased state first)

- Status Register Feature

- Electronic Identification

- JEDEC 1-byte manufacturer ID and 2-byte device ID

- RES command for 1-byte Device ID

- REMS commands for 1-byte manufacturer ID and 1-byte device ID

#### HARDWARE FEATURES

- PACKAGE

- 16-pin SOP (300mil)

- 8-pin SOP (200mil)

- 8-land WSON (8x6mm)

- All Pb-free devices are RoHS Compliant

## **GENERAL DESCRIPTION**

The device feature a serial peripheral interface and software protocol allowing operation on a simple 3-wire bus. The three bus signals are a clock input (SCLK), a serial data input (SI), and a serial data output (SO). Serial access to the device is enabled by CS# input.

When it is in Dual Output read mode, the SI and SO pins become SIO0 and SIO1 pins for data output.

The device provides sequential read operation on whole chip.

After program/erase command is issued, auto program/ erase algorithms which program/ erase and verify the specified page or sector/block locations will be executed. Program command is executed on byte basis, or page basis, or word basis for erase command is executes on sector, or block, or whole chip basis.

To provide user with ease of interface, a status register is included to indicate the status of the chip. The status read command can be issued to detect completion status of a program or erase operation via WIP bit.

Advanced security features enhance the protection and security functions, please see security features section for more details.

When the device is not in operation and CS# is high, it is put in standby mode.

The device utilizes Macronix's proprietary memory cell, which reliably stores memory contents even after typical 100,000 program and erase cycles.

# MX25L6406E

# **PIN CONFIGURATIONS**

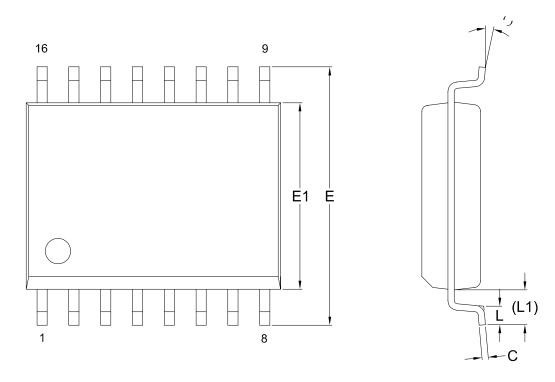

#### 16-PIN SOP (300mil)

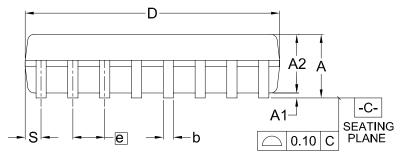

#### 8-PIN SOP (200mil)

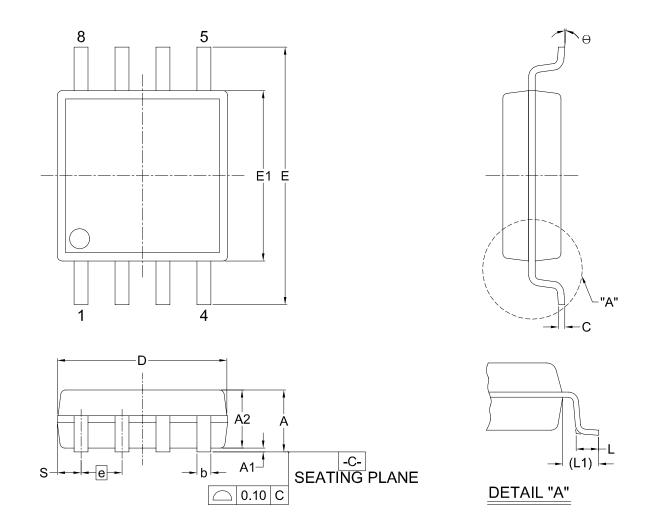

#### 8-LAND WSON (8x6mm)

## **PIN DESCRIPTION**

| SYMBOL  | DESCRIPTION                                                                           |

|---------|---------------------------------------------------------------------------------------|

| CS#     | Chip Select                                                                           |

| SI/SIO0 | Serial Data Input (for 1 x I/O)/ Serial Data<br>Input & Output (for Dual Output mode) |

| SO/SIO1 | Serial Data Output (for 1 x I/O)/ Serial Data<br>Output (for Dual Output mode)        |

| SCLK    | Clock Input                                                                           |

| WP#     | Write protection                                                                      |

| HOLD#   | Hold, to pause the device without deselecting the device                              |

| VCC     | + 3.3V Power Supply                                                                   |

| GND     | Ground                                                                                |

# BLOCK DIAGRAM

# MEMORY ORGANIZATION

# Table 1. Memory Organization

| Block | Sector | Address Range |         |  |  |  |

|-------|--------|---------------|---------|--|--|--|

|       | 2047   | 7FF000h       | 7FFFFFh |  |  |  |

| 127   | :      | :             | :       |  |  |  |

|       | 2032   | 7F0000h       | 7F0FFFh |  |  |  |

|       | 2031   | 7EF000h       | 7EFFFFh |  |  |  |

| 126   | :      | :             | :       |  |  |  |

|       | 2016   | 7E0000h       | 7E0FFFh |  |  |  |

| :     | :      | :             | :       |  |  |  |

| :     | :      | :             | :       |  |  |  |

|       | 15     | 00F000h       | 00FFFFh |  |  |  |

|       | :      | :             | :       |  |  |  |

| 0     | 3      | 003000h       | 003FFFh |  |  |  |

| 0     | 2      | 002000h       | 002FFFh |  |  |  |

|       | 1      | 001000h       | 001FFFh |  |  |  |

|       | 0      | 000000h       | 000FFFh |  |  |  |

# DEVICE OPERATION

- 1. Before a command is issued, status register should be checked to ensure device is ready for the intended operation.

- 2. When incorrect command is inputted to this LSI, this LSI becomes standby mode and keeps the standby mode until next CS# falling edge. In standby mode, SO pin of this LSI should be High-Z. The CS# falling time needs to follow tCHCL spec.

- 3. When correct command is inputted to this LSI, this LSI becomes active mode and keeps the active mode until next CS# rising edge. The CS# rising time needs to follow tCLCH spec.

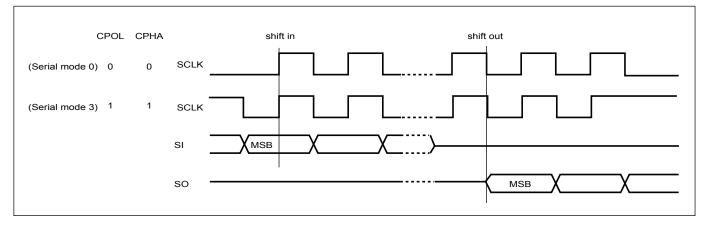

- 4. Input data is latched on the rising edge of Serial Clock(SCLK) and data shifts out on the falling edge of SCLK. The difference of Serial mode 0 and mode 3 is shown in Figure 1.

- 5. For the following instructions:RDID, RDSR, RDSCUR, READ, FAST\_READ, DREAD, RES, and REMS the shifted-in instruction sequence is followed by a data-out sequence. After any bit of data being shifted out, the CS# can be high. For the following instructions: WREN, WRDI, WRSR, SE, BE, CE, PP, RDP, DP, ENSO, EXSO, and WRSCUR, the CS# must go high exactly at the byte boundary; otherwise, the instruction will be rejected and not executed.

- 6. During the progress of Write Status Register, Program, Erase operation, to access the memory array is neglected and not affect the current operation of Write Status Register, Program, Erase.

## Figure 1. Serial Modes Supported

Note:

CPOL indicates clock polarity of Serial master, CPOL=1 for SCLK high while idle, CPOL=0 for SCLK low while not transmitting. CPHA indicates clock phase. The combination of CPOL bit and CPHA bit decides which Serial mode is supported.

# DATA PROTECTION

The device is designed to offer protection against accidental erasure or programming caused by spurious system level signals that may exist during power transition. During power up the device automatically resets the state machine in the standby mode. In addition, with its control register architecture, alteration of the memory contents only occurs after successful completion of specific command sequences. The device also incorporates several features to prevent inadvertent write cycles resulting from VCC power-up and power-down transition or system noise.

- Valid command length checking: The command length will be checked whether it is at byte base and completed on byte boundary.

- Write Enable (WREN) command: WREN command is required to set the Write Enable Latch bit (WEL) before other command to change data. The WEL bit will return to reset stage under following situation:

Power-up

- Power-up

- Write Disable (WRDI) command completion

- Write Status Register (WRSR) command completion

- Page Program (PP) command completion

- Sector Erase (SE) command completion

- Block Erase (BE) command completion

- Chip Erase (CE) command completion

- Deep Power Down Mode: By entering deep power down mode, the flash device also is under protected from writing all commands except Release from deep power down mode command (RDP) and Read Electronic Signature command (RES).

- Advanced Security Features: there are some protection and security features which protect content from inadvertent write and hostile access.

#### I. Block lock protection

- The Software Protected Mode (SPM):

MX25L6406E: use (BP3, BP2, BP1, BP0) bits to allow part of memory to be protected as read only. The proected area definition is shown as table of "Protected Area Sizes", the protected areas are more flexible which may protect various area by setting value of BP0-BP3 bits.

Please refer to table of "protected area sizes".

- The Hardware Proteced Mode (HPM) uses WP# to protect the MX25L6406E: BP3-BP0 bits and SRWD bit.

#### Table 2. Protected Area Sizes

|     | Statu | us bit |     | Protect Level                   |  |  |  |

|-----|-------|--------|-----|---------------------------------|--|--|--|

| BP3 | BP2   | BP1    | BP0 | 64Mb                            |  |  |  |

| 0   | 0     | 0      | 0   | 0 (none)                        |  |  |  |

| 0   | 0     | 0      | 1   | 1 (2block, block 126th-127th)   |  |  |  |

| 0   | 0     | 1      | 0   | 2 (4blocks, block 124th-127th)  |  |  |  |

| 0   | 0     | 1      | 1   | 3 (8blocks, block 120th-127th)  |  |  |  |

| 0   | 1     | 0      | 0   | 4 (16blocks, block 112th-127th) |  |  |  |

| 0   | 1     | 0      | 1   | 5 (32blocks, block 96th-127th)  |  |  |  |

| 0   | 1     | 1      | 0   | 6 (64blocks, block 64th-127th)  |  |  |  |

| 0   | 1     | 1      | 1   | 7 (128blocks, all)              |  |  |  |

| 1   | 0     | 0      | 0   | 8 (128blocks, all)              |  |  |  |

| 1   | 0     | 0      | 1   | 9 (64blocks, 0th-63th)          |  |  |  |

| 1   | 0     | 1      | 0   | 10 (96blocks, block 0th-95th)   |  |  |  |

| 1   | 0     | 1      | 1   | 11 (112blocks, block 0th-111th) |  |  |  |

| 1   | 1     | 0      | 0   | 12 (120blocks, block 0th-119th) |  |  |  |

| 1   | 1     | 0      | 1   | 13 (124blocks, block 0th-123th) |  |  |  |

| 1   | 1     | 1      | 0   | 14 (126blocks, block 0th-125th) |  |  |  |

| 1   | 1     | 1      | 1   | 15 (128blocks, all)             |  |  |  |

**II. Additional 512 bit secured OTP** for unique identifier: to provide 512 bit one-time program area for setting device unique serial number - Which may be set by factory or system customer. Please refer to table 3. 512 bit-secured OTP definition.

- Security register bit 0 indicates whether the chip is locked by factory or not.

- To program the 512 bit secured OTP by entering 512 bit secured OTP mode (with ENSO command), and going through normal program procedure, and then exiting 512 bit secured OTP mode by writing EXSO command.

- Customer may lock-down the customer lockable secured OTP by writing WRSCUR(write security register) command to set customer lock-down bit1 as "1". Please refer to table of "security register definition" for security register bit definition and table of "512 bit secured OTP definition" for address range definition.

- Note: Once lock-down whatever by factory or customer, it cannot be changed any more. While in 512 bit secured OTP mode, array access is not allowed.

| Table 3. 512 bit Secured OTP Definiti | on |

|---------------------------------------|----|

|---------------------------------------|----|

| Address range | Size                                   | Standard Factory Lock | Customer Lock          |

|---------------|----------------------------------------|-----------------------|------------------------|

| xxxx00~xxxx0F | 128-bit ESN (electrical serial number) |                       | Determined by sustamor |

| xxxx10~xxxx3F | 384-bit                                | N/A                   | Determined by customer |

# HOLD FEATURES

HOLD# pin signal goes low to hold any serial communications with the device. The HOLD feature will not stop the operation of write status register, programming, or erasing in progress.

The operation of HOLD requires Chip Select(CS#) keeping low and starts on falling edge of HOLD# pin signal while Serial Clock (SCLK) signal is being low (if Serial Clock signal is not being low, HOLD operation will not start until Serial Clock signal being low). The HOLD condition ends on the rising edge of HOLD# pin signal while Serial Clock(SCLK) signal is being low( if Serial Clock signal is not being low, HOLD operation will not end until Serial Clock being low), see Figure 2.

The Serial Data Output (SO) is high impedance, both Serial Data Input (SI) and Serial Clock (SCLK) are don't care during the HOLD operation. If Chip Select (CS#) drives high during HOLD operation, it will reset the internal logic of the device. To re-start communication with chip, the HOLD# must be at high and CS# must be at low.

# COMMAND DESCRIPTION

#### Table 4. COMMAND DEFINITION

| Command<br>(byte) | WREN (write enable)                         | WRDI (write disable) | WRSR<br>(write status<br>register)               | RDID<br>(read identific-<br>ation)                                          | RDSR<br>(read status<br>register)                      | READ (read<br>data)                        | FAST READ<br>(fast read<br>data)           |

|-------------------|---------------------------------------------|----------------------|--------------------------------------------------|-----------------------------------------------------------------------------|--------------------------------------------------------|--------------------------------------------|--------------------------------------------|

| 1st byte          | 06 (hex)                                    | 04 (hex)             | 01 (hex)                                         | 9F (hex)                                                                    | 05 (hex)                                               | 03 (hex)                                   | 0B (hex)                                   |

| 2nd byte          |                                             |                      |                                                  |                                                                             |                                                        | AD1                                        | AD1                                        |

| 3rd byte          |                                             |                      |                                                  |                                                                             |                                                        | AD2                                        | AD2                                        |

| 4th byte          |                                             |                      |                                                  |                                                                             |                                                        | AD3                                        | AD3                                        |

| 5th byte          |                                             |                      |                                                  |                                                                             |                                                        |                                            | Dummy                                      |

| Action            | sets the (WEL)<br>write enable<br>latch bit | (WEL) write          | to write new<br>values to the<br>status register | outputs<br>JEDEC<br>ID: 1-byte<br>Manufact-urer<br>ID & 2-byte<br>Device ID | to read out<br>the values<br>of the status<br>register | n bytes read<br>out until CS#<br>goes high | n bytes read<br>out until CS#<br>goes high |

|          |                | REMS (read   | DREAD        |              |                |                |              |

|----------|----------------|--------------|--------------|--------------|----------------|----------------|--------------|

| Command  | RES (read      | electronic   | (Double      | SE (sector   | BE (block      | CE (chip       | PP (page     |

| (byte)   | electronic ID) | manufacturer | Output Mode  | erase)       | erase)         | erase)         | program)     |

|          |                | & device ID) | command)     |              |                |                |              |

| 1st byte | AB (hex)       | 90 (hex)     | 3B (hex)     | 20 (hex)     | 52 or D8 (hex) | 60 or C7 (hex) | 02 (hex)     |

| 2nd byte | х              | х            | AD1          | AD1          | AD1            |                | AD1          |

| 3rd byte | х              | х            | AD2          | AD2          | AD2            |                | AD2          |

| 4th byte | х              | ADD (Note 1) | AD3          | AD3          | AD3            |                | AD3          |

| 5th byte |                |              | Dummy        |              |                |                |              |

|          | to read out    | output the   | n bytes read | to erase the | to erase the   | to erase       | to program   |

|          | 1-byte Device  | Manufacturer | out by Dual  | selected     | selected       | whole chip     | the selected |

| Action   | ID             | ID & Device  | Output until | sector       | block          |                | page         |

|          |                | ID           | CS# goes     |              |                |                | -            |

|          |                |              | high         |              |                |                |              |

| Command<br>(byte) | RDSCUR<br>(read security<br>register)    | WRSCUR<br>(write security<br>register)                                             | ENSO (enter secured OTP)                       | EXSO (exit secured OTP)                    | DP (Deep<br>power down)           | RDP (Release<br>from deep<br>power down) |

|-------------------|------------------------------------------|------------------------------------------------------------------------------------|------------------------------------------------|--------------------------------------------|-----------------------------------|------------------------------------------|

| 1st byte          | 2B (hex)                                 | 2F (hex)                                                                           | B1 (hex)                                       | C1 (hex)                                   | B9 (hex)                          | AB (hex)                                 |

| 2nd byte          |                                          |                                                                                    |                                                |                                            |                                   |                                          |

| 3rd byte          |                                          |                                                                                    |                                                |                                            |                                   |                                          |

| 4th byte          |                                          |                                                                                    |                                                |                                            |                                   |                                          |

| 5th byte          |                                          |                                                                                    |                                                |                                            |                                   |                                          |

| Action            | to read value<br>of security<br>register | to set the<br>lock-down bit<br>as "1" (once<br>lock-down,<br>cannot be<br>updated) | to enter<br>the 512 bit<br>secured OTP<br>mode | to exit the 512<br>bit secured<br>OTP mode | enters deep<br>power down<br>mode | release from<br>deep power<br>down mode  |

Note 1: ADD=00H will output the manufacturer ID first and ADD=01H will output device ID first.

Note 2: It is not recommended to adopt any other code not in the command definition table, which will potentially enter the hidden mode.

#### (1) Write Enable (WREN)

The Write Enable (WREN) instruction is for setting Write Enable Latch (WEL) bit. For those instructions like PP, SE, BE, CE, and WRSR, which are intended to change the device content, should be set every time after the WREN instruction setting the WEL bit.

The sequence is shown as *Figure 11*.

#### (2) Write Disable (WRDI)

The Write Disable (WRDI) instruction is for resetting Write Enable Latch (WEL) bit.

The sequence is shown as *Figure 12*.

The WEL bit is reset by following situations:

- Power-up

- Write Disable (WRDI) instruction completion

- Write Status Register (WRSR) instruction completion

- Page Program (PP) instruction completion

- Sector Erase (SE) instruction completion

- Block Erase (BE) instruction completion

- Chip Erase (CE) instruction completion

#### (3) Read Status Register (RDSR)

The RDSR instruction is for reading Status Register Bits. The Read Status Register can be read at any time (even in program/erase/write status register condition) and continuously. It is recommended to check the Write in Progress (WIP) bit before sending a new instruction when a program, erase, or write status register operation is in progress.

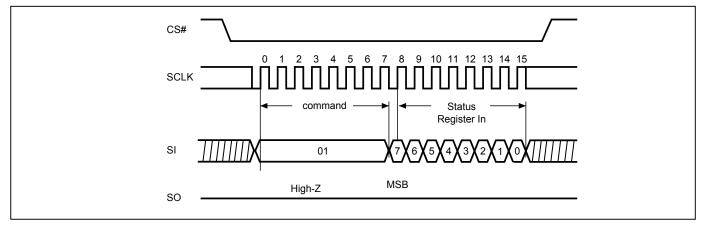

The sequence is shown as Figure 13.

The definition of the status register bits is as below:

**WIP bit.** The Write in Progress (WIP) bit, a volatile bit, indicates whether the device is busy in program/erase/write status register progress. When WIP bit sets to 1, which means the device is busy in program/erase/write status register progress. When WIP bit sets to 0, which means the device is not in progress of program/erase/write status register cycle.

**WEL bit.** The Write Enable Latch (WEL) bit, a volatile bit, indicates whether the device is set to internal write enable latch. When WEL bit sets to 1, which means the internal write enable latch is set, the device can accept program/ erase/write status register instruction. When WEL bit sets to 0, which means no internal write enable latch; the device will not accept program/erase/write status register instruction. The program/erase command will be ignored and not affect value of WEL bit if it is applied to a protected memory area.

**BP3, BP2, BP1, BP0 bits.** The Block Protect (BP3-BP0) bits, non-volatile bits, indicate the protected area (as defined in table 2) of the device to against the program/erase instruction without hardware protection mode being set. To write the Block Protect (BP3-BP0) bits requires the Write Status Register (WRSR) instruction to be executed. Those bits define the protected area of the memory to against Page Program (PP), Sector Erase (SE), Block Erase (BE) and Chip Erase (CE) instructions (only if all Block Protect bits set to 0, the CE instruction can be executed).

**SRWD bit.** The Status Register Write Disable (SRWD) bit, non-volatile bit, is operated together with Write Protection (WP#) pin for providing hardware protection mode. The hardware protection mode requires SRWD sets to 1 and WP# pin signal is low stage. In the hardware protection mode, the Write Status Register (WRSR) instruction is no longer accepted for execution and the SRWD bit and Block Protect bits (BP3-BP0) are read only.

#### **Status Register**

| bit7                                       | bit6 | bit5                                    | bit4                                    | bit3                                    | bit2                                    | bit1                                       | bit0                                                |

|--------------------------------------------|------|-----------------------------------------|-----------------------------------------|-----------------------------------------|-----------------------------------------|--------------------------------------------|-----------------------------------------------------|

| SRWD (status<br>register write<br>protect) | 0    | BP3<br>(level of<br>protected<br>block) | BP2<br>(level of<br>protected<br>block) | BP1<br>(level of<br>protected<br>block) | BP0<br>(level of<br>protected<br>block) | WEL<br>(write enable<br>latch)             | WIP<br>(write in<br>progress bit)                   |

| 1=status<br>register write<br>disable      | 0    | (note 1)                                | (note 1)                                | (note 1)                                | (note 1)                                | 1=write<br>enable<br>0=not write<br>enable | 1=write<br>operation<br>0=not in write<br>operation |

| Non-volatile<br>bit                        | 0    | Non-volatile<br>bit                     | Non-volatile<br>bit                     | Non-volatile<br>bit                     | Non-volatile<br>bit                     | volatile bit                               | volatile bit                                        |

note 1: see the table "Protected Area Size".

#### (4) Write Status Register (WRSR)

The WRSR instruction is for changing the values of Status Register Bits. Before sending WRSR instruction, the Write Enable (WREN) instruction must be decoded and executed to set the Write Enable Latch (WEL) bit in advance. The WRSR instruction can change the value of Block Protect (BP3-BP0) bits to define the protected area of memory (as shown in *table 1*). The WRSR also can set or reset the Status Register Write Disable (SRWD) bit in accordance with Write Protection (WP#) pin signal. The WRSR instruction cannot be executed once the Hardware Protected Mode (HPM) is entered.

The sequence is shown as *Figure 14*.

The WRSR instruction has no effect on b6, b1, b0 of the status register.

The CS# must go high exactly at the byte boundary; otherwise, the instruction will be rejected and not executed. The self-timed Write Status Register cycle time (tW) is initiated as soon as Chip Select (CS#) goes high. The Write in Progress (WIP) bit still can be check out during the Write Status Register cycle is in progress. The WIP sets 1 during the tW timing, and sets 0 when Write Status Register Cycle is completed, and the Write Enable Latch (WEL) bit is reset.

#### **Table 5. Protection Modes**

| Mode                                                                                                                                          | Status register condition | WP# and SRWD bit status                                                  | Memory                                               |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|--------------------------------------------------------------------------|------------------------------------------------------|--|

| Software protection<br>mode (SPM)Status register can be written<br>in (WEL bit is set to "1") and<br>the SRWD, BP3-BP0<br>bits can be changed |                           | WP#=1 and SRWD bit=0, or<br>WP#=0 and SRWD bit=0, or<br>WP#=1 and SRWD=1 | The protected area<br>cannot<br>be program or erase. |  |

| Hardware protection<br>mode (HPM)                                                                                                             |                           |                                                                          | The protected area<br>cannot<br>be program or erase. |  |

Note:

1. As defined by the values in the Block Protect (BP3-BP0) bits of the Status Register, as shown in Table 2.

As the above table showing, the summary of the Software Protected Mode (SPM) and Hardware Protected Mode (HPM).

Software Protected Mode (SPM):

- When SRWD bit=0, no matter WP# is low or high, the WREN instruction may set the WEL bit and can change the values of SRWD, BP3-BP0. The protected area, which is defined by BP3-BP0 is at software protected mode (SPM).

- When SRWD bit=1 and WP# is high, the WREN instruction may set the WEL bit can change the values of SRWD, BP3-BP0. The protected area, which is defined by BP3-BP0 is at software protected mode (SPM)

Note: If SRWD bit=1 but WP# is low, it is impossible to write the Status Register even if the WEL bit has previously been set. It is rejected to write the Status Register and not be executed.

#### Hardware Protected Mode (HPM):

When SRWD bit=1, and then WP# is low (or WP# is low before SRWD bit=1), it enters the hardware protected mode (HPM). The data of the protected area is protected by software protected mode by BP3-BP0 and hardware protected mode by the WP# to against data modification.

Note: to exit the hardware protected mode requires WP# driving high once the hardware protected mode is entered. If the WP# pin is permanently connected to high, the hardware protected mode can never be entered; only can use software protected mode via BP3-BP0.

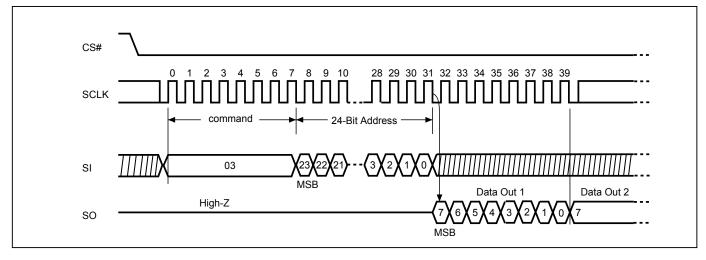

#### (5) Read Data Bytes (READ)

The read instruction is for reading data out. The address is latched on rising edge of SCLK, and data shifts out on the falling edge of SCLK at a maximum frequency fR. The first address byte can be at any location. The address is automatically increased to the next higher address after each byte data is shifted out, so the whole memory can be read out at a single READ instruction. The address counter rolls over to 0 when the highest address has been reached.

The sequence is shown as Figure 15.

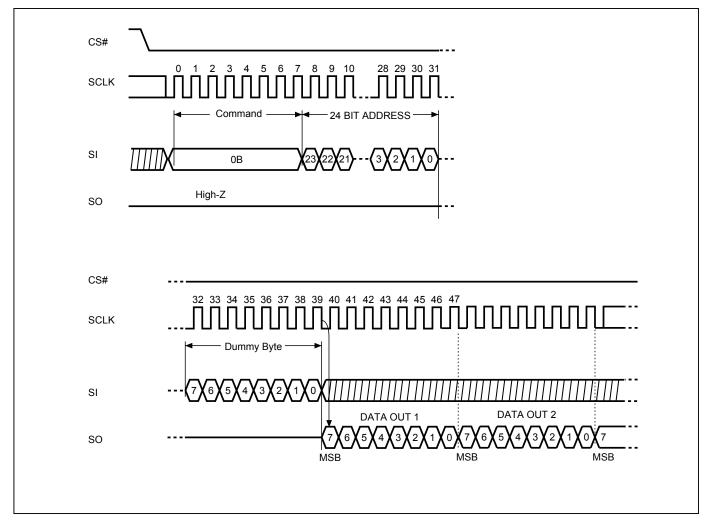

#### (6) Read Data Bytes at Higher Speed (FAST\_READ)

The FAST\_READ instruction is for quickly reading data out. The address is latched on rising edge of SCLK, and data of each bit shifts out on the falling edge of SCLK at a maximum frequency fC. The first address byte can be at any location. The address is automatically increased to the next higher address after each byte data is shifted out, so the whole memory can be read out at a single FAST\_READ instruction. The address counter rolls over to 0 when the highest address has been reached.

The sequence is shown as *Figure 16*.

While Program/Erase/Write Status Register cycle is in progress, FAST\_READ instruction is rejected without any impact on the Program/Erase/Write Status Register current cycle.

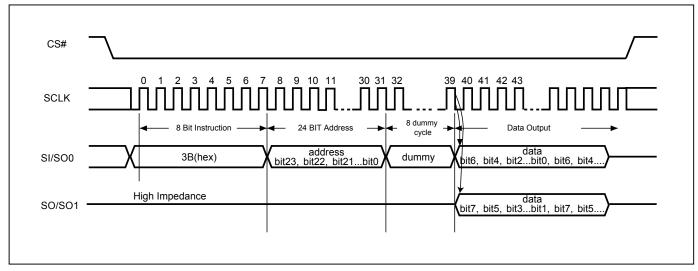

#### (7) Dual Output Mode (DREAD)

The DREAD instruction enable double throughput of Serial Flash in read mode. The address is latched on rising edge of SCLK, and data of every two bits(interleave on 1I/20 pins) shift out on the falling edge of SCLK at a maximum frequency fT. The first address byte can be at any location. The address is automatically increased to the next higher address after each byte data is shifted out, so the whole memory can be read out at a single DREAD instruction. The address counter rolls over to 0 when the highest address has been reached. Once writing DREAD instruction, the following address/dummy/data out will perform as 2-bit instead of previous 1-bit.

The sequence is shown as *Figure 17*.

While Program/Erase/Write Status Register cycle is in progress, DREAD instruction is rejected without any impact on the Program/Erase/Write Status Register current cycle.

The DREAD only perform read operation. Program/Erase /Read ID/Read status....operation do not support DREAD throughputs.

#### (8) Sector Erase (SE)

The Sector Erase (SE) instruction is for erasing the data of the chosen sector to be "1". The instruction is used for any 4K-byte sector. A Write Enable (WREN) instruction must execute to set the Write Enable Latch (WEL) bit before sending the Sector Erase (SE). Any address of the sector (see table 1) is a valid address for Sector Erase (SE) instruction. The CS# must go high exactly at the byte boundary (the latest eighth of address byte been latched-in); otherwise, the instruction will be rejected and not executed.

Address bits [Am-A12] (Am is the most significant address) select the sector address.

The sequence is shown as *Figure 18*.

The self-timed Sector Erase Cycle time (tSE) is initiated as soon as Chip Select (CS#) goes high. The Write in Progress (WIP) bit still can be check out during the Sector Erase cycle is in progress. The WIP sets 1 during the tSE timing, and sets 0 when Sector Erase Cycle is completed, and the Write Enable Latch (WEL) bit is reset. If the page is protected by BP3-BP0 bits, the Sector Erase (SE) instruction will not be executed on the page.

#### (9) Block Erase (BE)

The Block Erase (BE) instruction is for erasing the data of the chosen block to be "1". The instruction is used for 64K-byte sector erase operation. A Write Enable (WREN) instruction must execute to set the Write Enable Latch (WEL) bit before sending the Block Erase (BE). Any address of the block (see table 1) is a valid address for Block Erase (BE) instruction. The CS# must go high exactly at the byte boundary (the latest eighth of address byte been latched-in); otherwise, the instruction will be rejected and not executed.

The sequence is shown as *Figure 19*.

The self-timed Block Erase Cycle time (tBE) is initiated as soon as Chip Select (CS#) goes high. The Write in Progress (WIP) bit still can be check out during the Sector Erase cycle is in progress. The WIP sets 1 during the tBE timing, and sets 0 when Sector Erase Cycle is completed, and the Write Enable Latch (WEL) bit is reset. If the page is protected by BP3-BP0 bits, the Block Erase (BE) instruction will not be executed on the page.

#### (10) Chip Erase (CE)

The Chip Erase (CE) instruction is for erasing the data of the whole chip to be "1". A Write Enable (WREN) instruction must execute to set the Write Enable Latch (WEL) bit before sending the Chip Erase (CE). Any address of the sector (see table 1) is a valid address for Chip Erase (CE) instruction. The CS# must go high exactly at the byte boundary( the latest eighth of address byte been latched-in); otherwise, the instruction will be rejected and not executed.

The sequence is shown as *Figure 20*.

The self-timed Chip Erase Cycle time (tCE) is initiated as soon as Chip Select (CS#) goes high. The Write in Progress (WIP) bit still can be check out during the Chip Erase cycle is in progress. The WIP sets 1 during the tCE timing, and sets 0 when Chip Erase Cycle is completed, and the Write Enable Latch (WEL) bit is reset. If the chip is protected by BP3-BP0 bits, the Chip Erase (CE) instruction will not be executed. It will be only executed when BP3-BP0 all set to "0".

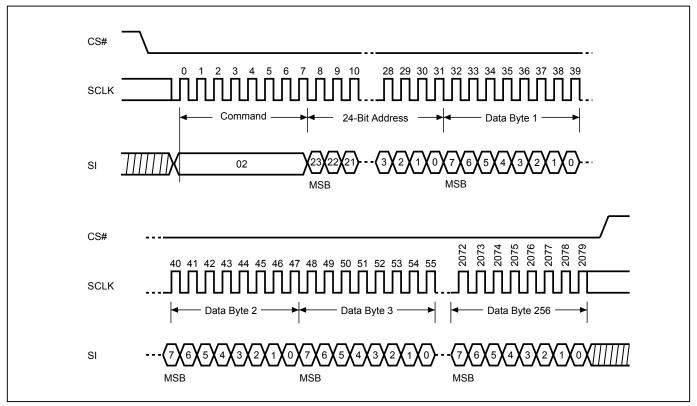

#### (11) Page Program (PP)

The Page Program (PP) instruction is for programming the memory to be "0". A Write Enable (WREN) instruction must execute to set the Write Enable Latch (WEL) bit before sending the Page Program (PP). If the eight least significant address bits (A7-A0) are not all 0, all transmitted data which goes beyond the end of the current page are programmed from the start address if the same page (from the address whose 8 least significant address bits (A7-A0) are all 0). The CS# must keep during the whole Page Program cycle. The CS# must go high exactly at the byte boundary( the latest eighth of address byte been latched-in); otherwise, the instruction will be rejected and not executed. If more than 256 bytes are sent to the device, the data of the last 256-byte is programmed at the request page and previous data will be disregarded. If less than 256 bytes are sent to the device, the same page.

The sequence is shown as *Figure 21*.

The self-timed Page Program Cycle time (tPP) is initiated as soon as Chip Select (CS#) goes high. The Write in

Progress (WIP) bit still can be check out during the Page Program cycle is in progress. The WIP sets 1 during the tPP timing, and sets 0 when Page Program Cycle is completed, and the Write Enable Latch (WEL) bit is reset. If the page is protected by BP3-BP0 bits, the Page Program (PP) instruction will not be executed.

#### (12) Deep Power-down (DP)

The Deep Power-down (DP) instruction is for setting the device on the minimizing the power consumption (to entering the Deep Power-down mode), the standby current is reduced from ISB1 to ISB2). The Deep Power-down mode requires the Deep Power-down (DP) instruction to enter, during the Deep Power-down mode, the device is not active and all Write/Program/Erase instruction are ignored. When CS# goes high, it's only in standby mode not deep power-down mode. It's different from Standby mode.

The sequence is shown as *Figure 22*.

Once the DP instruction is set, all instruction will be ignored except the Release from Deep Power-down mode (RDP) and Read Electronic Signature (RES) instruction. (those instructions allow the ID being reading out). When Power-down, the deep power-down mode automatically stops, and when power-up, the device automatically is in standby mode. For RDP instruction the CS# must go high exactly at the byte boundary (the latest eighth bit of instruction code been latched-in); otherwise, the instruction will not executed. As soon as Chip Select (CS#) goes high, a delay of tDP is required before entering the Deep Power-down mode and reducing the current to ISB2.

#### (13) Release from Deep Power-down (RDP), Read Electronic Signature (RES)

The Release from Deep Power-down (RDP) instruction is terminated by driving Chip Select (CS#) High. When Chip Select (CS#) is driven High, the device is put in the Stand-by Power mode. If the device was not previously in the Deep Power-down mode, the transition to the Stand-by Power mode is immediate. If the device was previously in the Deep Power-down mode, though, the transition to the Stand-by Power mode is delayed by tRES2, and Chip Select (CS#) must remain High for at least tRES2(max), as specified in *Table 9*. Once in the Stand-by Power mode, the device waits to be selected, so that it can receive, decode and execute instructions.

RES instruction is for reading out the old style of 8-bit Electronic Signature, whose values are shown as table of ID Definitions. This is not the same as RDID instruction. It is not recommended to use for new design. For new design, please use RDID instruction. Even in Deep power-down mode, the RDP and RES are also allowed to be executed, only except the device is in progress of program/erase/write cycle; there's no effect on the current program/erase/ write cycle in progress.

#### The sequence is shown in *Figure 23* and *Figure 24*.

The RES instruction is ended by CS# goes high after the ID been read out at least once. The ID outputs repeatedly if continuously send the additional clock cycles on SCLK while CS# is at low. If the device was not previously in Deep Power-down mode, the device transition to standby mode is immediate. If the device was previously in Deep Power-down mode, there's a delay of tRES2 to transit to standby mode, and CS# must remain to high at least tRES2(max). Once in the standby mode, the device waits to be selected, so it can be receive, decode, and execute instruction.

The RDP instruction is for releasing from Deep Power Down Mode.

#### (14) Read Identification (RDID)

The RDID instruction is for reading the manufacturer ID of 1-byte and followed by Device ID of 2-byte. The MXIC Manufacturer ID and Device ID are listed as table of "ID Definitions".

The sequence is shown as *Figure 25*.

While Program/Erase operation is in progress, it will not decode the RDID instruction, so there's no effect on the cycle of program/erase operation which is currently in progress. When CS# goes high, the device is at standby stage.

#### (15) Read Electronic Manufacturer ID & Device ID (REMS)

The REMS instruction is an alternative to the Release from Power-down/Device ID instruction that provides both the JEDEC assigned manufacturer ID and the specific device ID.

The REMS instruction is very similar to the Release from Power-down/Device ID instruction. The instruction is initiated by driving the CS# pin low and shift the instruction code "90h" followed by two dummy bytes and one bytes address (A7~A0). After which, the Manufacturer ID for MXIC and the Device ID are shifted out on the falling edge of SCLK with most significant bit (MSB) first as shown in *Figure 26*. The Device ID values are listed in Table of ID Definitions. If the one-byte address is initially set to 01h, then the device ID will be read first and then followed by the Manufacturer ID. The Manufacturer and Device IDs can be read continuously, alternating from one to the other. The instruction is completed by driving CS# high.

#### Table 6. ID DEFINITIONS

| Command Type   | MX25L6406E      |             |                |  |  |  |  |

|----------------|-----------------|-------------|----------------|--|--|--|--|

| RDID Command   | manufacturer ID | memory type | memory density |  |  |  |  |

| RDID Command   | C2              | 20          | 17             |  |  |  |  |

| DES Command    | electronic ID   |             |                |  |  |  |  |

| RES Command    | 16              |             |                |  |  |  |  |

| REMS Command   | manufacturer ID | device ID   |                |  |  |  |  |

| REIVIS COMMAND | C2              | 16          |                |  |  |  |  |

#### (16) Enter Secured OTP (ENSO)

The ENSO instruction is for entering the additional 512 bit secured OTP mode. The additional 512 bit secured OTP is independent from main array, which may use to store unique serial number for system identifier. After entering the Secured OTP mode, and then follow standard read or program, procedure to read out the data or update data. The Secured OTP data cannot be updated again once it is lock-down.

Please note that WRSR/WRSCUR commands are not acceptable during the access of secure OTP region, once security OTP is lock down, only read related commands are valid.

#### (17) Exit Secured OTP (EXSO)

The EXSO instruction is for exiting the additional 512 bit secured OTP mode.

#### (18) Read Security Register (RDSCUR)

The RDSCUR instruction is for reading the value of Security Register bits. The Read Security Register can be read at any time (even in program/erase/write status register/write security register condition) and continuously.

The sequence is shown as *Figure 27*.

The definition of the Security Register bits is as below:

**Secured OTP Indicator bit.** The Secured OTP indicator bit shows the chip is locked by factory before ex- factory or not. When it is "0", it indicates non- factory lock; "1" indicates factory- lock.

**Lock-down Secured OTP (LDSO) bit.** By writing WRSCUR instruction, the LDSO bit may be set to "1" for customer lock-down purpose. However, once the bit is set to "1" (lock-down), the LDSO bit and the 512 bit Secured OTP area cannot be update any more. While it is in 512 bit secured OTP mode, array access is not allowed.

| bit7         | bit6         | bit5         | bit4         | bit3         | bit2         | bit1                                                                  | bit0                                          |

|--------------|--------------|--------------|--------------|--------------|--------------|-----------------------------------------------------------------------|-----------------------------------------------|

| x            | х            | х            | х            | х            | х            | LDSO<br>(indicate if<br>lock-down                                     | Secured OTP indicator bit                     |

| reserved     | reserved     | reserved     | reserved     | reserved     | reserved     | 0 = not lockdown<br>1 = lock-down<br>(cannot<br>program/erase<br>OTP) | 0 = nonfactory<br>lock<br>1 = factory<br>lock |

| volatile bit | non-volatile bit                                                      | non-volatile bit                              |

#### **Table 7. SECURITY REGISTER DEFINITION**

#### (19) Write Security Register (WRSCUR)

The WRSCUR instruction is for changing the values of Security Register Bits. Unlike write status register, the WREN instruction is not required before sending WRSCUR instruction. The WRSCUR instruction may change the values of bit1 (LDSO bit) for customer to lock-down the 512 bit Secured OTP area. Once the LDSO bit is set to "1", the Secured OTP area cannot be updated any more.

The CS# must go high exactly at the boundary; otherwise, the instruction will be rejected and not executed.

The sequence is shown as *Figure 28*.

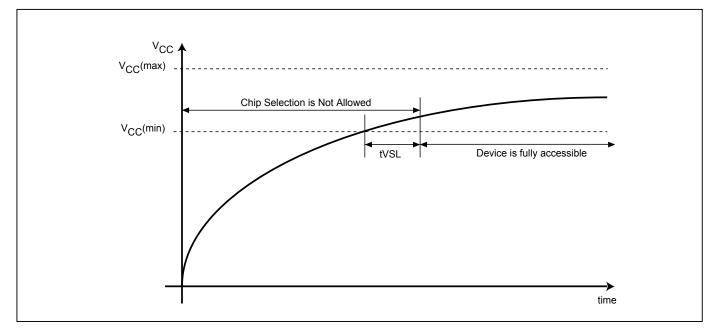

# **POWER-ON STATE**

The device is at below states when power-up:

- Standby mode ( please note it is not deep power-down mode)

- Write Enable Latch (WEL) bit is reset

The device must not be selected during power-up and power-down stage unless the VCC achieves below correct level:

- VCC minimum at power-up stage and then after a delay of tVSL

- GND at power-down

Please note that a pull-up resistor on CS# may ensure a safe and proper power-up/down level.

An internal power-on reset (POR) circuit may protect the device from data corruption and inadvertent data change during power up state.

For further protection on the device, if the VCC does not reach the VCC minimum level, the correct operation is not guaranteed. The read, write, erase, and program command should be sent after the below time delay:

- tVSL after VCC reached VCC minimum level

The device can accept read command after VCC reached VCC minimum and a time delay of tVSL. Please refer to the figure of "power-up timing".

Note:

- To stabilize the VCC level, the VCC rail decoupled by a suitable capacitor close to package pins is recommended.(generally around 0.1uF)

#### INITIAL DELIVERY STATE

The device is delivered with the memory array erased: all bits are set to 1 (each byte contains FFh).

# ELECTRICAL SPECIFICATIONS

#### **ABSOLUTE MAXIMUM RATINGS**

| RATING                        |                  | VALUE          |  |  |  |

|-------------------------------|------------------|----------------|--|--|--|

| Ambient Operating Temperature | Industrial grade | -40°C to 85°C  |  |  |  |

| Storage Temperature           |                  | -55°C to 125°C |  |  |  |

| Applied Input Voltage         |                  | -0.5V to 4.6V  |  |  |  |

| Applied Output Voltage        |                  | -0.5V to 4.6V  |  |  |  |

| VCC to Ground Potential       |                  | -0.5V to 4.6V  |  |  |  |

NOTICE:

1. Stresses greater than those listed under ABSOLUTE MAXIMUM RATINGS may cause permanent damage to the device. This is stress rating only and functional operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended period may affect reliability.

- 2. Specifications contained within the following tables are subject to change.

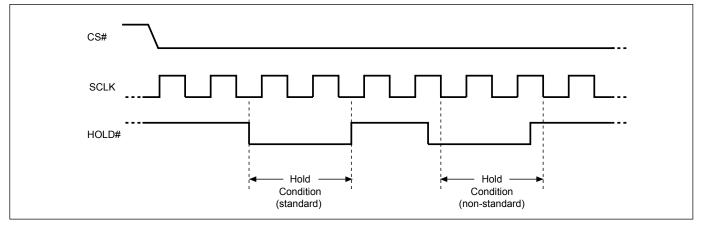

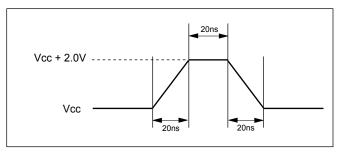

- 3. During voltage transitions, all pins may overshoot Vss to -2.0V and Vcc to +2.0V for periods up to 20ns, see Figure 3 and 4.

#### Figure 3.Maximum Negative Overshoot Waveform

#### Figure 4. Maximum Positive Overshoot Waveform

#### CAPACITANCE TA = 25°C, f = 1.0 MHz

| SYMBOL | PARAMETER          | MIN. | TYP | MAX. | UNIT | CONDITIONS |

|--------|--------------------|------|-----|------|------|------------|

| CIN    | Input Capacitance  |      |     | 6    | pF   | VIN = 0V   |

| COUT   | Output Capacitance |      |     | 8    | pF   | VOUT = 0V  |

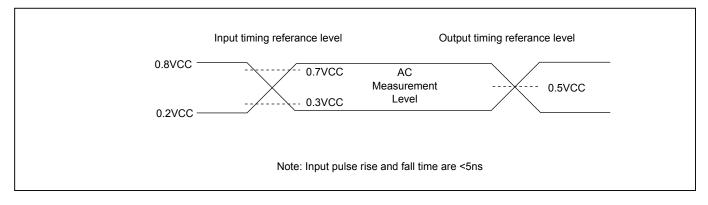

#### Figure 5. INPUT TEST WAVEFORMS AND MEASUREMENT LEVEL

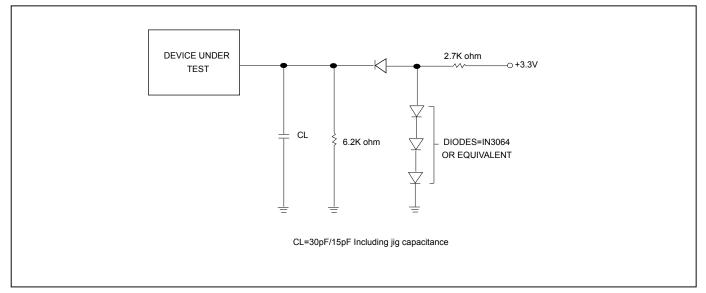

# Figure 6. OUTPUT LOADING

# **Table 8. DC CHARACTERISTICS**

| SYMBOL | PARAMETER                                   | NOTES | MIN.    | TYP. | MAX.    | UNITS | TEST CONDITIONS                                                      |

|--------|---------------------------------------------|-------|---------|------|---------|-------|----------------------------------------------------------------------|

| ILI    | Input Load Current                          | 1     |         |      | ± 2     | uA    | VCC = VCC Max,<br>VIN = VCC or GND                                   |

| ILO    | Output Leakage Current                      | 1     |         |      | ± 2     | uA    | VCC = VCC Max,<br>VIN = VCC or GND                                   |

| ISB1   | VCC Standby Current                         | 1     |         |      | 50      | uA    | VIN = VCC or GND,<br>CS# = VCC                                       |

| ISB2   | Deep Power-down<br>Current                  |       |         | 5    | 20      | uA    | VIN = VCC or GND,<br>CS# = VCC                                       |

|        |                                             |       |         |      | 25      | mA    | f=86MHz<br>fT=80MHz (2 x I/O read)<br>SCLK=0.1VCC/0.9VCC,<br>SO=Open |

| ICC1   | VCC Read                                    | 1     |         |      | 20      | mA    | f=66MHz,<br>SCLK=0.1VCC/0.9VCC,<br>SO=Open                           |

|        |                                             |       |         |      | 10      | mA    | f=33MHz,<br>SCLK=0.1VCC/0.9VCC,<br>SO=Open                           |

| ICC2   | VCC Program Current<br>(PP)                 | 1     |         |      | 20      | mA    | Program in Progress,<br>CS# = VCC                                    |

| ICC3   | VCC Write Status<br>Register (WRSR) Current |       |         |      | 20      | mA    | Program status register in<br>progress, CS#=VCC                      |

| ICC4   | VCC Sector Erase<br>Current (SE)            | 1     |         |      | 20      | mA    | Erase in Progress, CS#=VCC                                           |

| ICC5   | VCC Chip Erase Current (CE)                 | 1     |         |      | 25      | mA    | Erase in Progress, CS#=VCC                                           |

| VIL    | Input Low Voltage                           |       | -0.5    |      | 0.3VCC  | V     |                                                                      |

| VIH    | Input High Voltage                          |       | 0.7VCC  |      | VCC+0.4 | V     |                                                                      |

| VOL    | Output Low Voltage                          |       |         |      | 0.4     | V     | IOL = 1.6mA                                                          |

| VOH    | Output High Voltage                         |       | VCC-0.2 |      |         | V     | IOH = -100uA                                                         |

Notes :

Typical values at VCC = 3.3V, T = 25°C. These currents are valid for all product versions (package and speeds).

Not 100% tested.

# Table 9. AC CHARACTERISTICS

| Symbol    | Alt.  | Parameter                                               |            | Min. | Тур. | Max. | Unit |

|-----------|-------|---------------------------------------------------------|------------|------|------|------|------|

|           |       | Clock Frequency for the following instructions:         |            |      |      |      |      |

| fSCLK     | fC    | FAST_READ, PP, SE, BE, CE, DP, RES, RDP,                |            | DC   |      | 86   | MHz  |

|           |       | WREN, WRDI, RDID, RDSR, WRSR                            |            |      |      |      |      |

| fRSCLK    | fR    | Clock Frequency for READ instructions                   |            | DC   |      | 33   | MHz  |

| fTSCLK    | fT    | Clock Frequency for DREAD instructions                  |            | DC   |      | 80   | MHz  |

| tCH(1)    | tCLH  |                                                         | =86MHz     | 5.5  |      |      | ns   |

|           | (OEII | Į <sup>r</sup>                                          | =33MHz     | 13   |      |      | ns   |

| tCL(1)    | tCLL  |                                                         | =86MHz     | 5.5  |      |      | ns   |

|           | IOLL  | fR                                                      | =33MHz     | 13   |      |      | ns   |

| tCLCH(2)  |       | Clock Rise Time (3) (peak to peak)                      |            | 0.1  |      |      | V/ns |

| tCHCL(2)  |       | Clock Fall Time (3) (peak to peak)                      |            | 0.1  |      |      | V/ns |

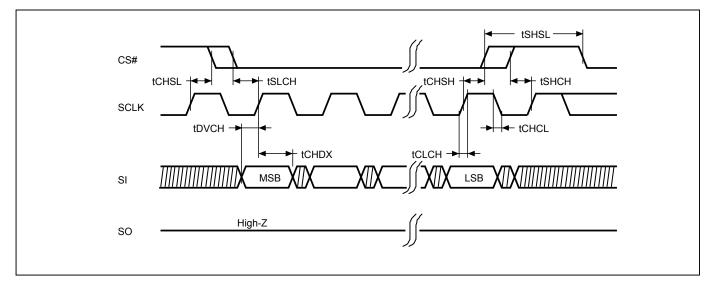

| tSLCH     | tCSS  | CS# Active Setup Time (relative to SCLK)                |            | 7    |      |      | ns   |

| tCHSL     |       | CS# Not Active Hold Time (relative to SCLK)             |            | 7    |      |      | ns   |

| tDVCH     | tDSU  | Data In Setup Time                                      |            | 2    |      |      | ns   |

| tCHDX     | tDH   | Data In Hold Time                                       |            | 5    |      |      | ns   |

| tCHSH     |       | CS# Active Hold Time (relative to SCLK)                 |            | 7    |      |      | ns   |

| tSHCH     |       | CS# Not Active Setup Time (relative to SCLK)            |            | 7    |      |      | ns   |

| 401101    | 10011 | CS# Deselect Time                                       | ead        | 15   |      |      | ns   |

| tSHSL     | ICSH  |                                                         | /rite      | 40   |      |      | ns   |

| tSHQZ(2)  | tDIS  | Output Disable Time                                     |            |      |      | 8    | ns   |

|           | £) /  | Cleak Low to Output Valid (CL =15pE) 2.                 | 7V~3.6V    |      |      | 8    | ns   |

| tCLQV     | tV    | Clock Low to Output Valid (CL=15pF)                     | 0V~3.6V    |      |      | 6    | ns   |

| tCLQX     | tHO   | Output Hold Time                                        |            | 0    |      |      | ns   |

| tHLCH     |       | HOLD# Setup Time (relative to SCLK)                     |            | 5    |      |      | ns   |

| tCHHH     |       | HOLD# Hold Time (relative to SCLK)                      |            | 5    |      |      | ns   |

| tHHCH     |       | HOLD Setup Time (relative to SCLK)                      |            | 5    |      |      | ns   |

| tCHHL     |       | HOLD Hold Time (relative to SCLK)                       |            | 5    |      |      | ns   |

| tHHQX(2)  | tLZ   | HOLD to Output Low-Z                                    |            |      |      | 8    | ns   |

| tHLQZ(2)  | tHZ   | HOLD# to Output High-Z                                  |            |      |      | 8    | ns   |

| tWHSL(4)  |       | Write Protect Setup Time                                |            | 20   |      |      | ns   |

| tSHWL (4) |       | Write Protect Hold Time                                 |            | 100  |      |      | ns   |

| tDP(2)    |       | CS# High to Deep Power-down Mode                        |            |      |      | 10   | us   |

| tRES1(2)  |       | CS# High to Standby Mode without Electronic Signation   | ature Read |      |      | 8.8  | us   |

| tRES2(2)  |       | CS# High to Standby Mode with Electronic Signature Read |            |      |      | 8.8  | us   |

| tW        |       | Write Status Register Cycle Time                        |            |      | 5    | 40   | ms   |

| tBP       |       | Byte-Program                                            |            |      | 9    | 300  | us   |

| tPP       |       | Page Program Cycle Time                                 |            |      | 1.4  | 5    | ms   |

| tSE       |       | Sector Erase Cycle Time                                 | İ          |      | 60   | 300  | ms   |

| tBE       |       | Block Erase Cycle Time                                  | 1          |      | 0.7  | 2    | s    |

| tCE       |       | Chip Erase Cycle Time                                   |            |      | 50   | 80   | s    |

| tRPD1     |       | CS# High to Power-Down                                  | İ          | 100  |      |      | ns   |

Notes:

1. tCH + tCL must be greater than or equal to 1/ fC. For Fast Read, tCL/tCH=5.5/5.5.

Value guaranteed by characterization, not 100% tested in production.

Expressed as a slew-rate.

4. Only applicable as a constraint for a WRSR instruction when SRWD is set at 1.

5. Test condition is shown as Figure 5.

6. The CS# rising time needs to follow tCLCH spec and CS# falling time needs to follow tCHCL spec.

# **Timing Analysis**

# Figure 7. Serial Input Timing

#### Figure 8. Output Timing

# Figure 9. Hold Timing

\* SI is "don't care" during HOLD operation.

# Figure 11. Write Enable (WREN) Sequence (Command 06)

# Figure 12. Write Disable (WRDI) Sequence (Command 04)

Figure 14. Write Status Register (WRSR) Sequence (Command 01)

Figure 16. Read at Higher Speed (FAST\_READ) Sequence (Command 0B)

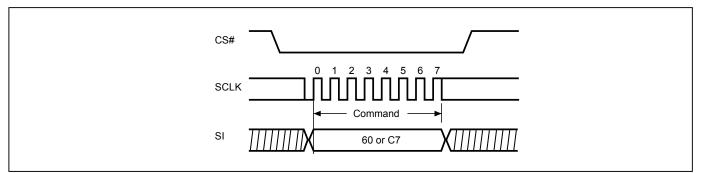

#### Figure 18. Sector Erase (SE) Sequence (Command 20)

Note: SE command is 20(hex).

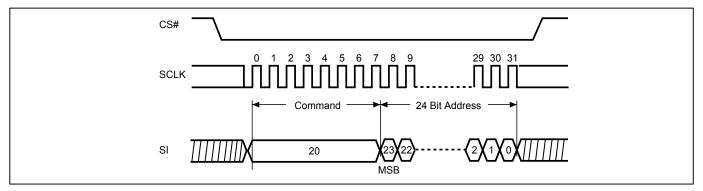

## Figure 19. Block Erase (BE) Sequence (Command 52 or D8)

Note: BE command is 52 or D8(hex).

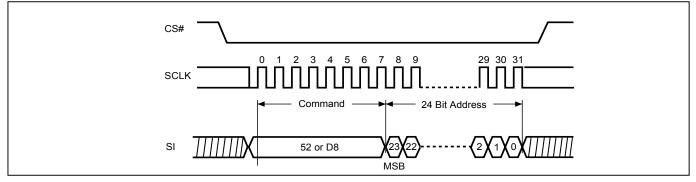

#### Figure 20. Chip Erase (CE) Sequence (Command 60 or C7)

Note: CE command is 60(hex) or C7(hex).

### Notes:

(1) ADD=00H will output the manufacturer's ID first and ADD=01H will output device ID first.

# Figure 28. Write Security Register (WRSCUR) Sequence (Command 2F)

#### Figure 29. Program/ Erase flow with read array data

# Figure 30. Power-up Timing

Note: VCC (max.) is 3.6V and VCC (min.) is 2.7V.

#### Table 10. Power-Up Timing

| Symbol  | Parameter           | Min. | Max. | Unit |  |

|---------|---------------------|------|------|------|--|

| tVSL(1) | VCC(min) to CS# low | 200  |      | us   |  |

Note: 1. The parameter is characterized only.

### **OPERATING CONDITIONS**

#### At Device Power-Up and Power-Down

AC timing illustrated in Figure 31 and Figure 32 are the supply voltages and the control signals at device power-up and power-down. If the timing in the figures is ignored, the device will not operate correctly.

During power-up and power down, CS# needs to follow the voltage applied on VCC to keep the device not be selected. The CS# can be driven low when VCC reach Vcc(min.) and wait a period of tVSL.

Figure 31. AC Timing at Device Power-Up

| Symbol | Parameter     | Notes | Min. | Max.   | Unit |  |

|--------|---------------|-------|------|--------|------|--|

| tVR    | VCC Rise Time | 1     | 20   | 500000 | us/V |  |

Notes :

1. Sampled, not 100% tested.

2. For AC spec tCHSL, tSLCH, tDVCH, tCHDX, tSHSL, tCHSH, tSHCH, tCHCL, tCLCH in the figure, please refer to "AC CHARACTERISTICS" table.

## Figure 32. Power-Down Sequence

During power down, CS# need to follow the voltage drop on VCC to avoid mis-operation.

| VCC  |  |

|------|--|

| CS#  |  |

| SCLK |  |

|      |  |

### ERASE AND PROGRAMMING PERFORMANCE

| PARAMETER                                    | Min. | TYP. (1) | Max. (2) | UNIT   |

|----------------------------------------------|------|----------|----------|--------|

| Write Status Register Time                   |      | 5        | 40       | ms     |

| Sector Erase Time                            |      | 60       | 300      | ms     |

| Block Erase Time                             |      | 0.7      | 2        | s      |

| Chip Erase Time                              |      | 50       | 80       | s      |

| Byte Program Time (via page program command) |      | 9        | 300      | us     |

| Page Program Time                            |      | 1.4      | 5        | ms     |

| Erase/Program Cycle                          |      | 100,000  |          | cycles |

Note:

- 1. Typical program and erase time assumes the following conditions: 25°C, 3.3V, and checker board pattern.

- 2. Under worst conditions of 85°C and 2.7V.

- 3. System-level overhead is the time required to execute the first-bus-cycle sequence for the programming command.

- 4. Erase/Program cycles comply JEDEC: JESD-47 & JESD22-A117 standard.

## DATA RETENTION

| PARAMETER      | Condition | Min. | Max. | UNIT  |

|----------------|-----------|------|------|-------|

| Data retention | 55°C      | 20   |      | years |

### LATCH-UP CHARACTERISTICS

|                                                                               | MIN.   | MAX.       |  |  |  |  |  |  |  |

|-------------------------------------------------------------------------------|--------|------------|--|--|--|--|--|--|--|

| Input Voltage with respect to GND on all power pins, SI, CS#                  | -1.0V  | 2 VCCmax   |  |  |  |  |  |  |  |

| Input Voltage with respect to GND on SO                                       | -1.0V  | VCC + 1.0V |  |  |  |  |  |  |  |

| Current                                                                       | -100mA | +100mA     |  |  |  |  |  |  |  |

| Includes all pins except VCC. Test conditions: VCC = 3.0V, one pin at a time. |        |            |  |  |  |  |  |  |  |

# ORDERING INFORMATION

| PART NO.          | CLOCK<br>(MHz) | CURRENT   CURRENT |    | Temperature | PACKAGE            | Remark  |

|-------------------|----------------|-------------------|----|-------------|--------------------|---------|

| MX25L6406EMI-12G  | 86             | 25                | 50 | -40°C~85°C  | 16-SOP<br>(300mil) | Pb-free |

| MX25L6406EM2I-12G | 86             | 25                | 50 | -40°C~85°C  | 8-SOP<br>(200mil)  | Pb-free |

| MX25L6406EZNI-12G | 86             | 25                | 50 | -40°C~85°C  | 8-WSON<br>(8x6mm)  | Pb-free |

## PART NAME DESCRIPTION

# PACKAGE INFORMATION

Doc. Title: Package Outline for SOP 16L (300MIL)

Dimensions (inch dimensions are derived from the original mm dimensions)

| SY<br>UNIT | MBOL | Α     | A1    | A2    | b     | С     | D     | Е     | E1    | е     | L     | L1    | S     | θ |

|------------|------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|---|

|            | Min. |       | 0.10  | 2.34  | 0.36  | 0.20  | 10.10 | 10.10 | 7.42  |       | 0.40  | 1.31  | 0.51  | 0 |

| mm         | Nom. |       | 0.20  | 2.39  | 0.41  | 0.25  | 10.30 | 10.30 | 7.52  | 1.27  | 0.84  | 1.44  | 0.64  | 5 |

|            | Max. | 2.65  | 0.30  | 2.44  | 0.51  | 0.30  | 10.50 | 10.50 | 7.60  |       | 1.27  | 1.57  | 0.77  | 8 |

|            | Min. |       | 0.004 | 0.092 | 0.014 | 0.008 | 0.397 | 0.397 | 0.292 |       | 0.016 | 0.052 | 0.020 | 0 |

| Inch       | Nom. |       | 800.0 | 0.094 | 0.016 | 0.010 | 0.405 | 0.405 | 0.296 | 0.050 | 0.033 | 0.057 | 0.025 | 5 |

|            | Max. | 0.104 | 0.012 | 0.096 | 0.020 | 0.012 | 0.413 | 0.413 | 0.299 |       | 0.050 | 0.062 | 0.030 | 8 |

| Dwg. No.  | Revision | Reference |      |  |  |  |  |  |  |

|-----------|----------|-----------|------|--|--|--|--|--|--|

|           |          | JEDEC     | EIAJ |  |  |  |  |  |  |

| 6110-1402 | 9        | MS-013    |      |  |  |  |  |  |  |

Doc. Title: Package Outline for SOP 8L 200MIL (official name - 209MIL)

Dimensions (inch dimensions are derived from the original mm dimensions)

| SY<br>UNIT | MBOL | Α     | A1    | A2    | b     | С     | D     | Е     | E1    | е     | L     | L1    | S     | θ |

|------------|------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|---|

|            | Min. |       | 0.05  | 1.70  | 0.36  | 0.19  | 5.13  | 7.70  | 5.18  |       | 0.50  | 1.21  | 0.62  | 0 |

| mm         | Nom. |       | 0.15  | 1.80  | 0.41  | 0.20  | 5.23  | 7.90  | 5.28  | 1.27  | 0.65  | 1.31  | 0.74  | 5 |

|            | Max. | 2.16  | 0.20  | 1.91  | 0.51  | 0.25  | 5.33  | 8.10  | 5.38  |       | 0.80  | 1.41  | 0.88  | 8 |

|            | Min. |       | 0.002 | 0.067 | 0.014 | 0.007 | 0.202 | 0.303 | 0.204 | -     | 0.020 | 0.048 | 0.024 | 0 |

| Inch       | Nom. |       | 0.006 | 0.071 | 0.016 | 0.008 | 0.206 | 0.311 | 0.208 | 0.050 | 0.026 | 0.052 | 0.029 | 5 |

|            | Max. | 0.085 | 0.008 | 0.075 | 0.020 | 0.010 | 0.210 | 0.319 | 0.212 |       | 0.031 | 0.056 | 0.035 | 8 |

| Dwg. No.  | Revision | Reference |      |  |  |  |  |  |  |

|-----------|----------|-----------|------|--|--|--|--|--|--|

|           |          | JEDEC     | EIAJ |  |  |  |  |  |  |

| 6110-1406 | 2        |           |      |  |  |  |  |  |  |

Doc. Title: Package Outline for WSON 8L (8x6x0.8MM, LEAD PITCH 1.27MM)

Dimensions (inch dimensions are derived from the original mm dimensions)

\*1 : This package has exposed metal pad underneath the package, it can't contact to metal trace or pad on board.

\*2 : The exposed pad size must not violate the min. metal separtion requirement, 0.2mm with terminals.

| SY<br>UNIT | (MBOL   | Α     | A1       | A2    | b      | D     | D1    | E         | E1    | L     | е    | у     |

|------------|---------|-------|----------|-------|--------|-------|-------|-----------|-------|-------|------|-------|

|            | Min.    | 0.70  |          | -     | 0.35   | 7.90  | 4.65  | 5.90      | 4.55  | 0.40  |      | 0.00  |

| mm         | Nom.    | —     |          | 0.20  | 0.40   | 8.00  | 4.70  | 6.00      | 4.60  | 0.50  | 1.27 | _     |

|            | Max.    | 0.80  | 0.05     | -     | 0.48   | 8.10  | 4.75  | 6.10      | 4.65  | 0.60  | —    | 0.08  |

|            | Min.    | 0.028 |          |       | 0.014  | 0.311 | 0.183 | 0.232     | 0.179 | 0.016 |      | 0.00  |

| Inch       | Nom.    |       |          | 0.008 | 0.016  | 0.315 | 0.185 | 0.236     | 0.181 | 0.020 | 0.05 | _     |

|            | Max.    | 0.032 | 0.002    | -     | 0.019  | 0.319 | 0.187 | 0.240     | 0.183 | 0.024 |      | 0.003 |

| Dw         | vg. No. |       | Revision |       |        |       |       | Reference | 2     |       |      |       |

|            | 0       |       |          |       | IEDEC  |       | EIAJ  |           |       |       |      |       |

| 611        | 0-3402  |       | 5        |       | MO-220 |       |       |           |       |       |      |       |

# **REVISION HISTORY**

| <b>Revision No.</b> | Description                                                            | Page        | Date        |

|---------------------|------------------------------------------------------------------------|-------------|-------------|

| 1.0                 | 1. Modified Figure 19. Block Erase (BE) Sequence                       | P34         | JUL/09/2010 |

|                     | 2. Modified "Initial Delivery State" description                       | P24         |             |

|                     | 3. Revised Note 4 of Erase And Programming Performance table           | P42         |             |

|                     | <ol><li>Removed DMC sequence description &amp; content table</li></ol> | P6,10,14,24 | 1           |

|                     | 5. Removed "Advanced Information"                                      | P5          |             |

|                     | 6. Modified ISB1 & ICC5                                                | P27         |             |

| 1.1                 | 1. Added RDSCUR & WRSCUR diagram form                                  | P38         | NOV/17/2010 |

|                     | <ol><li>Added CS# rising and falling time description</li></ol>        | P10,28      |             |

|                     | 3. Modified tW from 40(typ.)/100(max.) to 5(typ.)/40(max.)             | P28,43      |             |

|                     | <ol><li>Modified tCLQV (15pF loading)</li></ol>                        | P28         |             |

|                     | 5. Modified standby current                                            | P5,44       |             |