# **Micron Serial NOR Flash Memory**

3V, Multiple I/O, 4KB Sector Erase N25Q128A

### Features

- SPI-compatible serial bus interface

- 108 MHz (MAX) clock frequency

- 2.7–3.6V single supply voltage

- Dual/quad I/O instruction provides increased throughput up to 432 MHz

- Supported protocols

- Extended SPI, dual I/O, and quad I/O

- Execute-in-place (XIP) mode for all three protocols

- Configurable via volatile or nonvolatile registers

- Enables memory to work in XIP mode directly after power-on

- PROGRAM/ERASE SUSPEND operations

- Continuous read of entire memory via a single command

- Fast read

- Quad or dual output fast read

- Quad or dual I/O fast read

- Flexible to fit application

- Configurable number of dummy cycles

- Output buffer configurable

- Software reset

- 64-byte, user-lockable, one-time programmable (OTP) dedicated area

- Erase capability

- Subsector erase 4KB uniform granularity blocks

- Sector erase 64KB uniform granularity blocks

- Full-chip erase

- Write protection

- Software write protection applicable to every 64KB sector via volatile lock bit

- Hardware write protection: protected area size defined by five nonvolatile bits (BP0, BP1, BP2, BP3, and TB)

- Additional smart protections, available upon request

- Electronic signature

- JEDEC-standard 2-byte signature (BA18h)

- Unique ID code (UID): 17 read-only bytes, including:

- Two additional extended device ID (EDID) bytes to identify device factory options

- Customized factory data (14 bytes)

- Minimum 100,000 ERASE cycles per sector

- More than 20 years data retention

- Packages JEDEC standard, all RoHS compliant

- F7 = V-PDFN-8 6mm x 5mm Sawn (MLP8 6mm x 5mm)

- F8 = V-PDFN-8 8mm x 6mm (MLP8 8mm x 6mm)

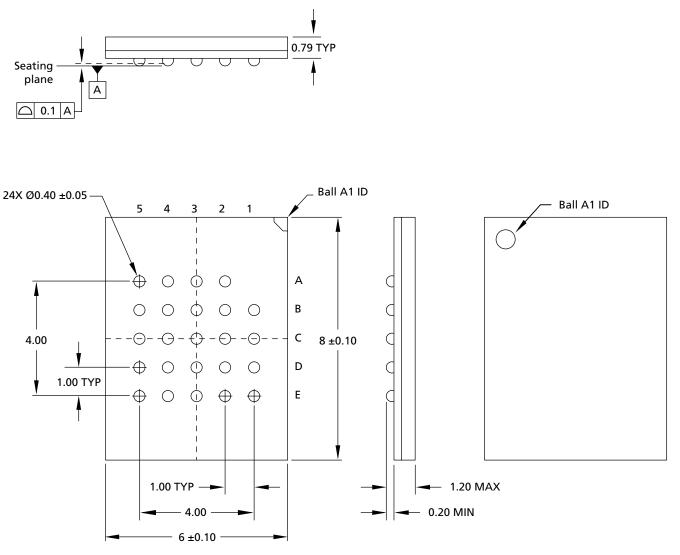

- 12 = T-PBGA-24b05 6mm x 8mm

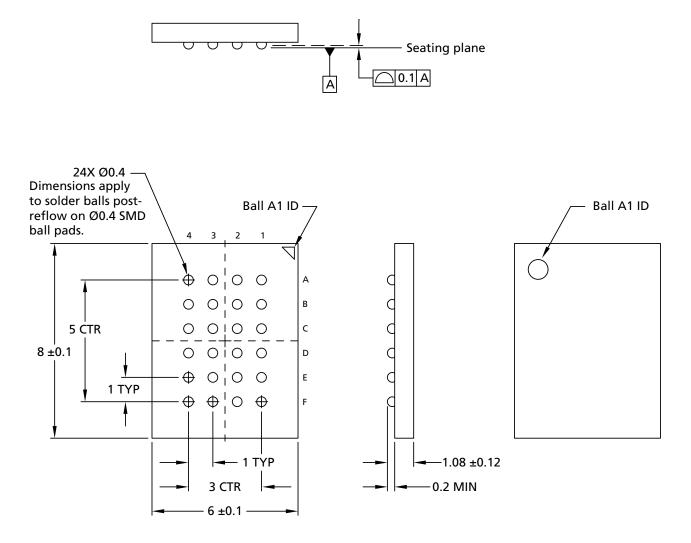

- 14 = T-PBGA-24b05 6mm x 8mm, 4x6 ball array

- SF = SOP2-16 300 mils body width (SO16W)

- SE = SOP2-8 208 mils body width (SO8W)

### Contents

| Device Description                                                 |      |

|--------------------------------------------------------------------|------|

| Features                                                           | 6    |

| Operating Protocols                                                | 6    |

| XIP Mode                                                           | 6    |

| Device Configurability                                             | 7    |

| Signal Assignments                                                 | 8    |

| Signal Descriptions                                                | . 10 |

| Memory Organization                                                | . 12 |

| Memory Configuration and Block Diagram                             | . 12 |

| Memory Map – 128Mb Density                                         |      |

| Device Protection                                                  |      |

| Serial Peripheral Interface Modes                                  |      |

| SPI Protocols                                                      |      |

| Nonvolatile and Volatile Registers                                 | . 19 |

| Status Register                                                    |      |

| Nonvolatile and Volatile Configuration Registers                   |      |

| Enhanced Volatile Configuration Register                           | . 23 |

| Flag Status Register                                               |      |

| Command Definitions                                                |      |

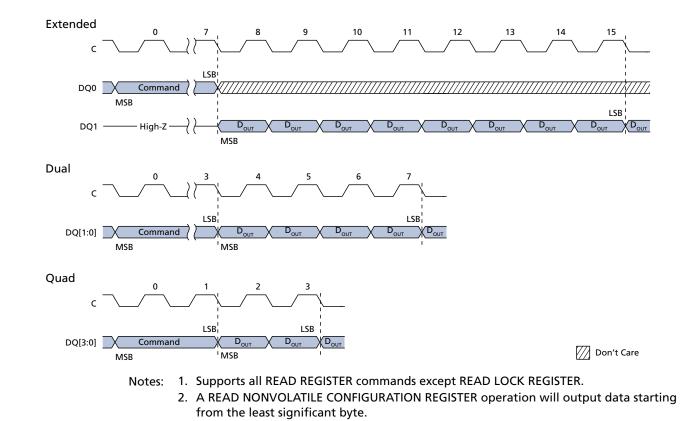

| READ REGISTER and WRITE REGISTER Operations                        |      |

| READ STATUS REGISTER or FLAG STATUS REGISTER Command               | 28   |

| READ NONVOLATILE CONFIGURATION REGISTER Command                    | 28   |

| READ VOLATILE or ENHANCED VOLATILE CONFIGURATION REGISTER Command  |      |

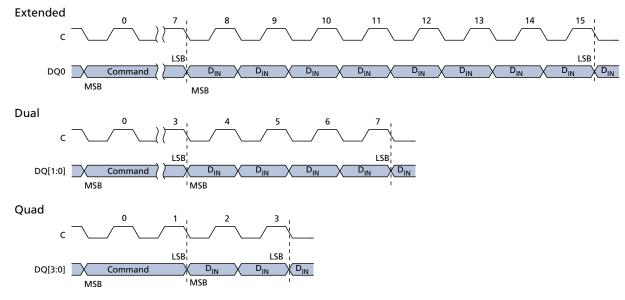

| WRITE STATUS REGISTER Command                                      |      |

| WRITE NONVOLATILE CONFIGURATION REGISTER Command                   |      |

| WRITE VOLATILE CONTIGURATION REGISTER Command                      |      |

| READ LOCK REGISTER Command                                         |      |

| WRITE LOCK REGISTER Command                                        |      |

| CLEAR FLAG STATUS REGISTER Command                                 |      |

| READ IDENTIFICATION Operations                                     |      |

| READ ID and MULTIPLE I/O READ ID Commands                          |      |

| READ SERIAL FLASH DISCOVERY PARAMETER Command                      |      |

| READ SERIAL PLASH DISCOVERT FARAVETER Command                      |      |

| PROGRAM Operations                                                 |      |

| WRITE Operations                                                   |      |

| WRITE ENABLE Command                                               |      |

| WRITE ENABLE Command                                               |      |

|                                                                    |      |

| ERASE Operations                                                   |      |

| SUBSECTOR ERASE Command                                            |      |

| SECTOR ERASE Command                                               |      |

| BULK ERASE Command                                                 |      |

| PROGRAM/ERASE SUSPEND Command                                      |      |

| PROGRAM/ERASE RESUME Command                                       |      |

| ONE TIME PROGRAMMABLE Operations                                   |      |

| READ OTP ARRAY Command                                             |      |

| PROGRAM OTP ARRAY Command                                          |      |

| XIP Mode                                                           |      |

| Activate or Terminate XIP Using Volatile Configuration Register    |      |

| Activate or Terminate XIP Using Nonvolatile Configuration Register |      |

| Confirmation Bit Settings Required to Activate or Terminate XIP    | 58   |

#### 128Mb, 3V, Multiple I/O Serial Flash Memory Features

| Terminating XIP After a Controller and Memory Reset | 59 |

|-----------------------------------------------------|----|

| Power-Up and Power-Down                             | 60 |

| Power-Up and Power-Down Requirements                | 60 |

| Power Loss Rescue Sequence                          | 61 |

| AC Reset Specifications                             |    |

| Absolute Ratings and Operating Conditions           | 67 |

| DC Characteristics and Operating Conditions         | 69 |

| AC Characteristics and Operating Conditions         | 70 |

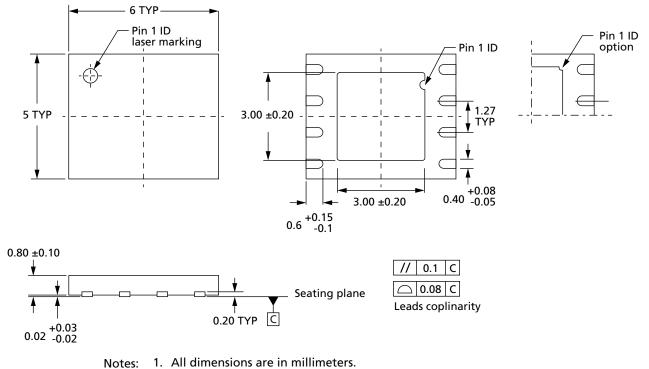

| Package Dimensions                                  |    |

| Part Number Ordering Information                    | 78 |

| Revision History                                    |    |

| Rev. P – 06/2013                                    | 80 |

| Rev. O – 04/2013                                    | 80 |

| Rev. N – 01/2013                                    | 80 |

| Rev. M – 07/2012                                    | 80 |

| Rev. L – 06/2012                                    | 80 |

| Rev. K – 2/2012                                     | 80 |

| Rev. J – 12/2011                                    | 80 |

| Rev. I – 10/2011                                    | 80 |

| Rev. H – 08/2011                                    | 80 |

| Rev. G – 08/2011                                    | 80 |

| Rev. F – 02/2011                                    | 80 |

| Rev. E – 01/2011                                    | 80 |

| Rev. D – 10/2010                                    | 81 |

| Rev. C – 2/2010                                     | 81 |

| Rev. B – 05/2009                                    | 81 |

| Rev. A – 01/2009                                    | 81 |

|                                                     |    |

## **List of Figures**

| Figure 1: L  | ogic Diagram                                                                   | . 7 |

|--------------|--------------------------------------------------------------------------------|-----|

| Figure 2: 8  | B-Pin, VDFPN8 – MLP8 and SOP2 – SO8W (Top View)                                | . 8 |

|              | 6-Pin, Plastic Small Outline – SO16 (Top View)                                 |     |

| Figure 4: 2  | 24-Ball TBGA (Balls Down)                                                      | . 9 |

| Figure 5: 2  | 24-Ball TBGA , 4x6 (Balls Down)                                                | . 9 |

|              | Block Diagram                                                                  |     |

| Figure 7: B  | Bus Master and Memory Devices on the SPI Bus                                   | 17  |

| Figure 8: S  | SPI Modes                                                                      | 17  |

| Figure 9: In | nternal Configuration Register                                                 | 19  |

| Figure 10:   | READ REGISTER Command                                                          | 28  |

| Figure 11:   | WRITE REGISTER Command                                                         | 30  |

|              | READ LOCK REGISTER Command                                                     |     |

| Figure 13:   | WRITE LOCK REGISTER Command                                                    | 33  |

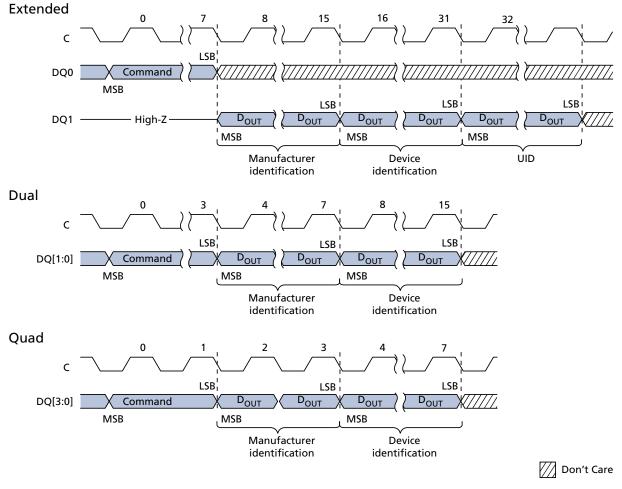

| Figure 14:   | READ ID and MULTIPLE I/O Read ID Commands                                      | 35  |

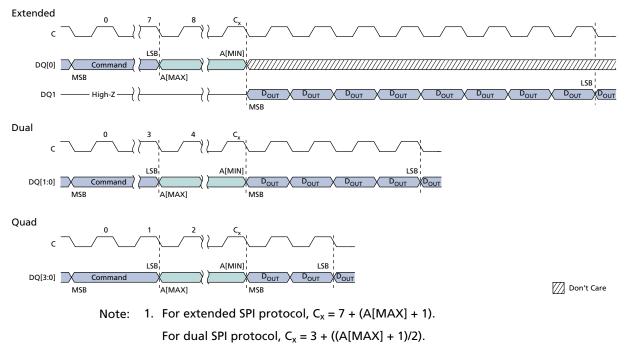

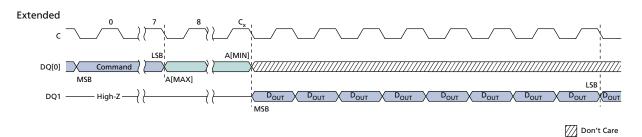

| Figure 15:   | READ Command                                                                   | 39  |

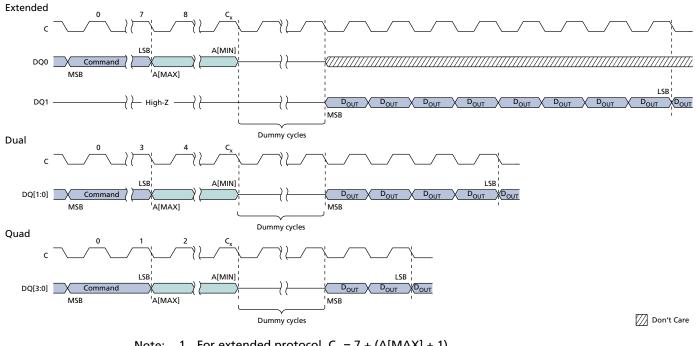

| Figure 16:   | FAST READ Command                                                              | 39  |

| Figure 17:   | DUAL OUTPUT FAST READ                                                          | 40  |

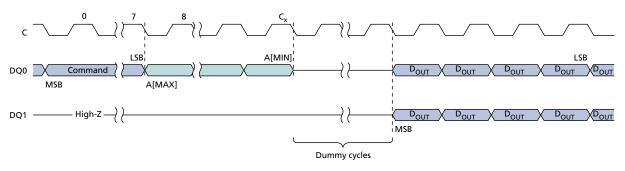

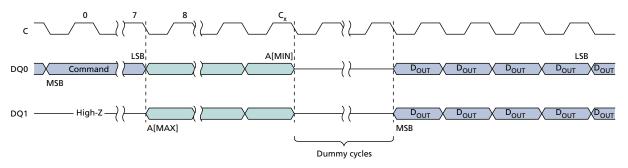

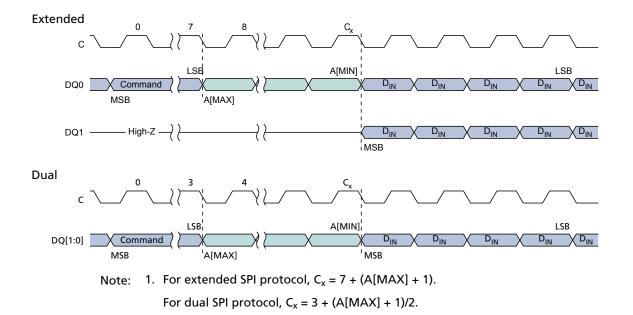

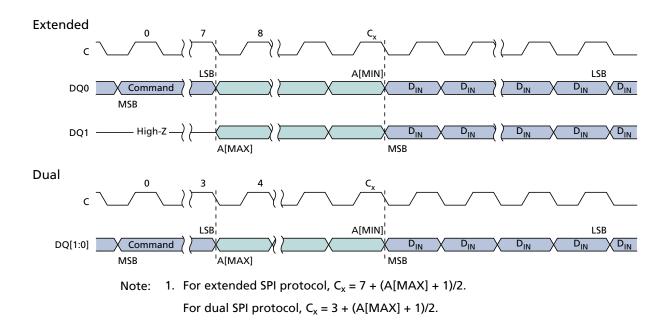

| Figure 18:   | DUAL INPUT/OUTPUT FAST READ Command                                            | 40  |

| Figure 19:   | QUAD OUTPUT FAST READ Command                                                  | 41  |

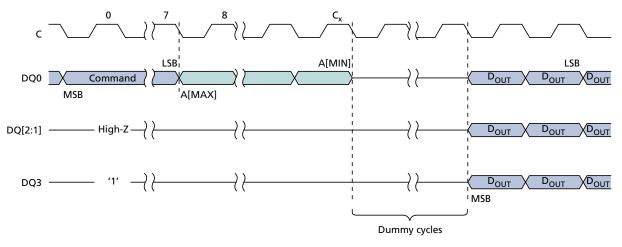

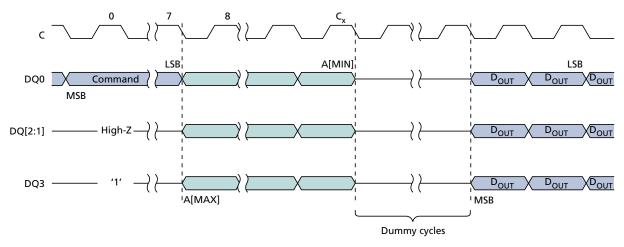

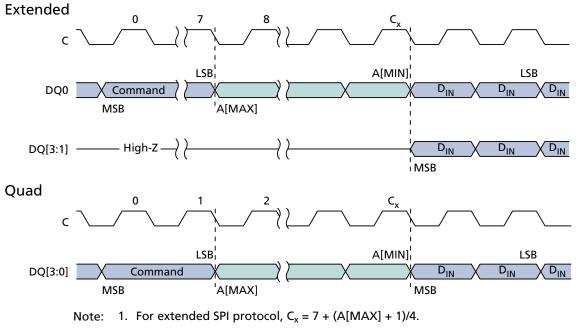

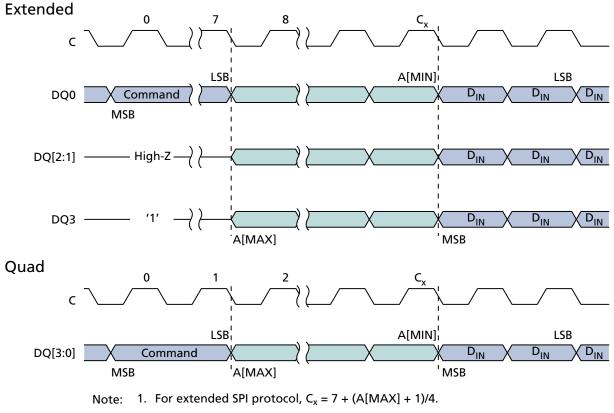

| Figure 20:   | OUAD INPUT/OUTPUT FAST READ Command                                            | 41  |

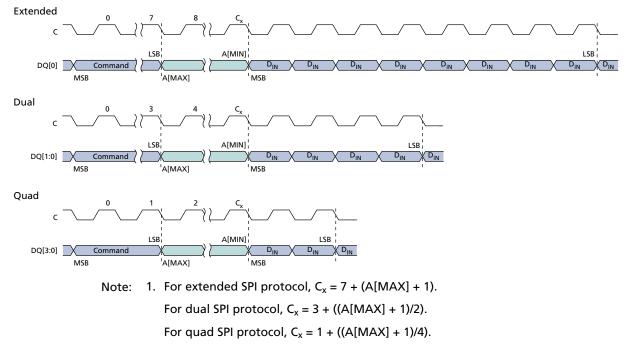

| Figure 21:   | PAGE PROGRAM Command                                                           | 43  |

| Figure 22:   | DUAL INPUT FAST PROGRAM Command                                                | 44  |

|              | EXTENDED DUAL INPUT FAST PROGRAM Command                                       |     |

| Figure 24:   | QUAD INPUT FAST PROGRAM Command                                                | 45  |

|              | EXTENDED QUAD INPUT FAST PROGRAM Command                                       |     |

|              | WRITE ENABLE and WRITE DISABLE Command Sequence                                |     |

| Figure 27:   | SUBSECTOR and SECTOR ERASE Command                                             | 50  |

| Figure 28:   | BULK ERASE Command                                                             | 51  |

|              | READ OTP Command                                                               |     |

| Figure 30:   | PROGRAM OTP Command                                                            | 56  |

|              | XIP Mode Directly After Power-On                                               |     |

| Figure 32:   | Power-Up Timing                                                                | 60  |

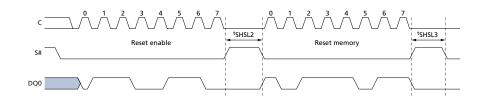

|              | Reset AC Timing During PROGRAM or ERASE Cycle                                  |     |

|              | Reset Enable                                                                   |     |

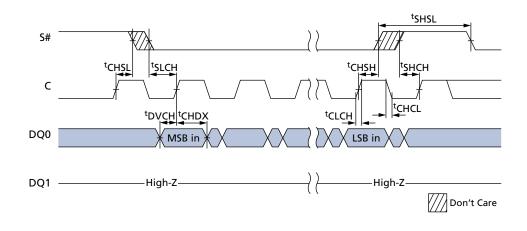

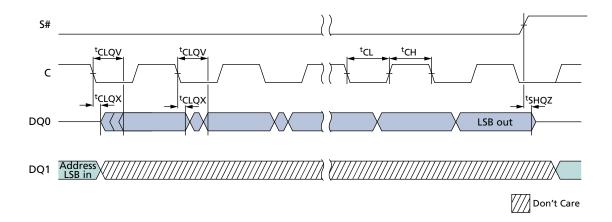

|              | Serial Input Timing                                                            |     |

| Figure 36:   | Write Protect Setup and Hold During WRITE STATUS REGISTER Operation (SRWD = 1) | 64  |

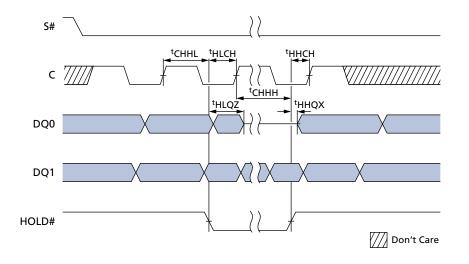

|              | Hold Timing                                                                    |     |

|              |                                                                                | 66  |

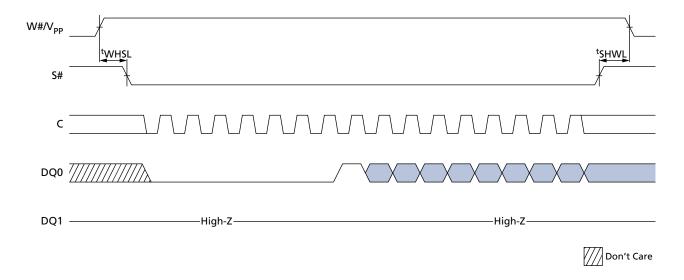

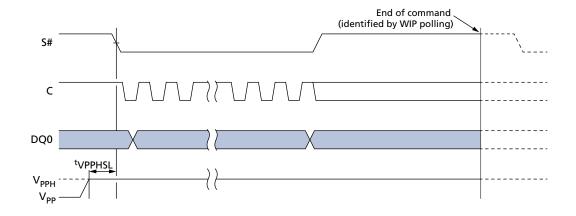

| Figure 39:   | V <sub>PPH</sub> Timing                                                        |     |

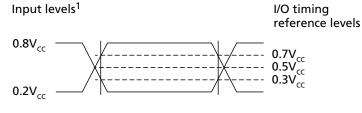

|              | AC Timing Input/Output Reference Levels                                        |     |

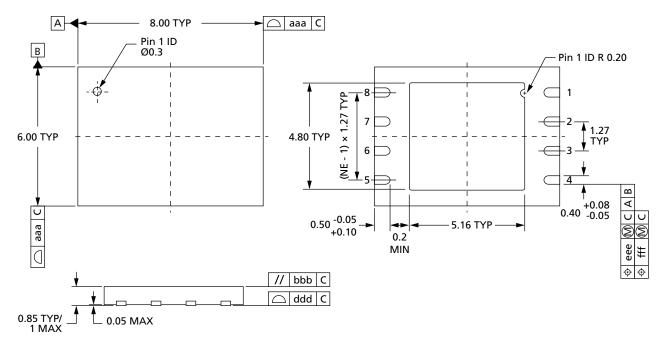

|              | V-PDFN-8 6mm x 5mm Sawn (MLP8) – Package Code: F7                              |     |

|              | V-PDFN-8 8mm x 6mm (MLP8) – Package Code: F8                                   |     |

|              | T-PBGA-24b05 6mm x 8mm – Package Code: 12                                      |     |

|              | T-PBGA-24b05 6mm x 8mm – Package Code: 12                                      |     |

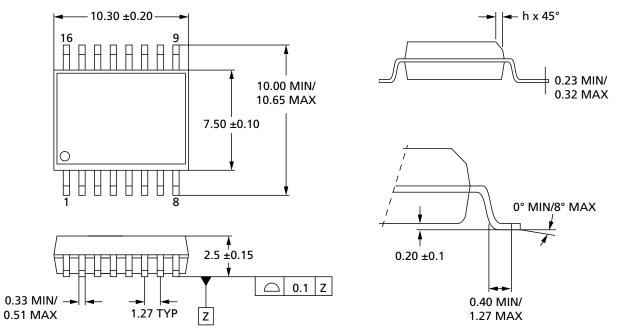

|              | SOP2-16 (300 mils body width) – Package Code: SF                               |     |

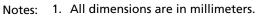

|              | SOP2-8 (208 mils body width) – Package Code: SE                                |     |

|              | (                                                                              | ••• |

### **List of Tables**

|             | ignal Descriptions                                               |    |

|-------------|------------------------------------------------------------------|----|

|             | ectors[255:0]                                                    |    |

|             | ata Protection using Device Protocols                            |    |

|             | Iemory Sector Protection Truth Table                             |    |

| Table 5: Pr | rotected Area Sizes – Upper Area                                 | 14 |

| Table 6: Pr | rotected Area Sizes – Lower Area                                 | 15 |

|             | PI Modes                                                         |    |

|             | xtended, Dual, and Quad SPI Protocols                            |    |

|             | tatus Register Bit Definitions                                   |    |

| Table 10: N | Nonvolatile Configuration Register Bit Definitions               | 21 |

|             | Volatile Configuration Register Bit Definitions                  |    |

| Table 12: S | Sequence of Bytes During Wrap                                    | 23 |

|             | Supported Clock Frequencies                                      |    |

|             | Enhanced Volatile Configuration Register Bit Definitions         |    |

|             | Flag Status Register Bit Definitions                             |    |

|             | Command Set                                                      |    |

|             | Lock Register                                                    |    |

|             | Data/Address Lines for READ ID and MULTIPLE I/O READ ID Commands |    |

|             | Read ID Data Out                                                 |    |

|             | Extended Device ID, First Byte                                   |    |

|             | Serial Flash Discovery Parameter – Header Structure              |    |

|             | Parameter ID                                                     |    |

|             | Command/Address/Data Lines for READ MEMORY Commands              |    |

|             | Data/Address Lines for PROGRAM Commands                          |    |

|             | Suspend Parameters                                               |    |

| Table 26: C | Operations Allowed/Disallowed During Device States               | 53 |

|             | OTP Control Byte (Byte 64)                                       |    |

| Table 28: X | XIP Confirmation Bit                                             | 58 |

| Table 29: E | Effects of Running XIP in Different Protocols                    | 58 |

| Table 30: P | Power-Up Timing and V <sub>WI</sub> Threshold                    | 61 |

|             | AC RESET Conditions                                              |    |

|             | Absolute Ratings                                                 |    |

|             | Operating Conditions                                             |    |

|             | Input/Output Capacitance                                         |    |

| Table 35: A | AC Timing Input/Output Conditions                                | 68 |

|             | DC Current Characteristics and Operating Conditions              |    |

|             | DC Voltage Characteristics and Operating Conditions              |    |

|             | AC Characteristics and Operating Conditions                      |    |

|             | Part Number Information                                          |    |

| Table 40: P | Package Details                                                  | 79 |

|             |                                                                  |    |

### **Device Description**

The N25Q is the first high-performance multiple input/output serial Flash memory device manufactured on 65nm NOR technology. It features execute-in-place (XIP) functionality, advanced write protection mechanisms, and a high-speed SPI-compatible bus interface. The innovative, high-performance, dual and quad input/output instructions enable double or quadruple the transfer bandwidth for READ and PROGRAM operations.

#### **Features**

The memory is organized as 256 (64KB) main sectors that are further divided into 16 subsectors each (4096 subsectors in total). The memory can be erased one 4KB subsector at a time, 64KB sectors at a time, or as a whole.

The memory can be write protected by software through volatile and nonvolatile protection features, depending on the application needs. The protection granularity is of 64KB (sector granularity) for volatile protections

The device has 64 one-time programmable (OTP) bytes that can be read and programmed with the READ OTP and PROGRAM OTP commands. These 64 bytes can also be permanently locked with a PROGRAM OTP command.

The device also has the ability to pause and resume PROGRAM and ERASE cycles by using dedicated PROGRAM/ERASE SUSPEND and RESUME instructions.

#### **Operating Protocols**

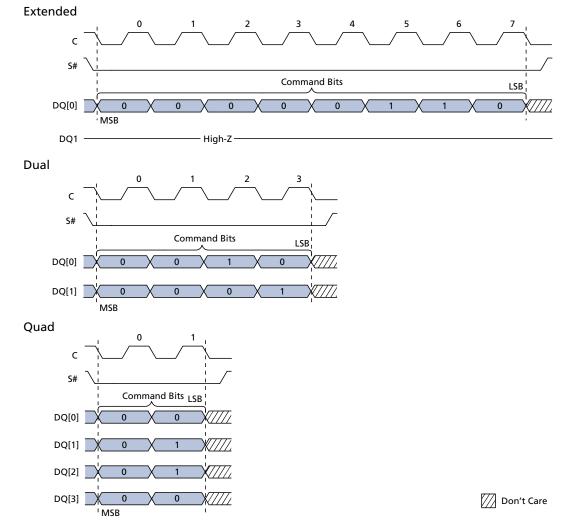

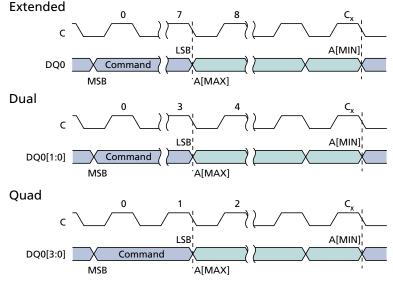

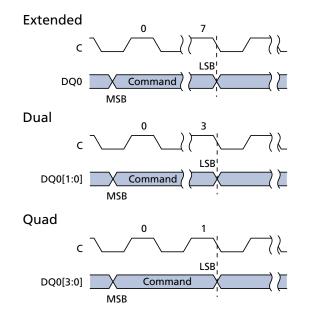

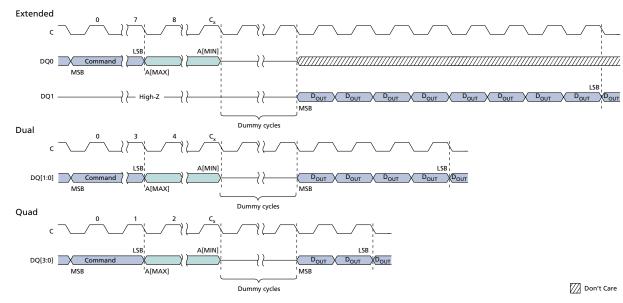

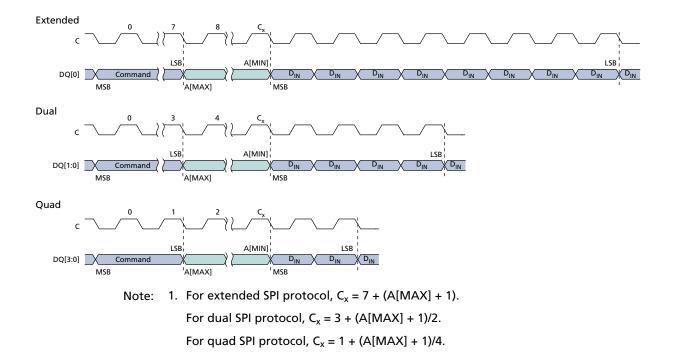

The memory can be operated with three different protocols:

- Extended SPI (standard SPI protocol upgraded with dual and quad operations)

- Dual I/O SPI

- Quad I/O SPI

The standard SPI protocol is extended and enhanced by dual and quad operations. In addition, the dual SPI and quad SPI protocols improve the data access time and throughput of a single I/O device by transmitting commands, addresses, and data across two or four data lines.

#### **XIP Mode**

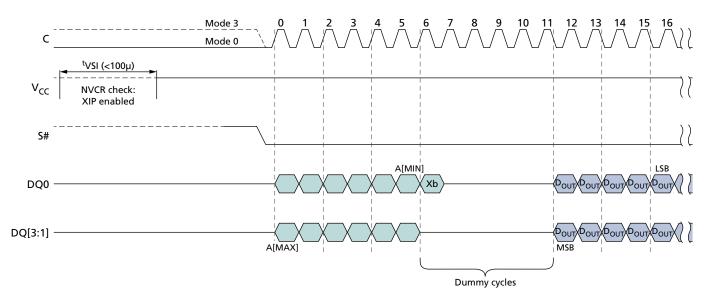

XIP mode requires only an address (no instruction) to output data, improving random access time and eliminating the need to shadow code onto RAM for fast execution.

All protocols support XIP operation. For flexibility, multiple XIP entry and exit methods are available. For applications that must enter XIP mode immediately after powering up, XIP mode can be set as the default mode through the nonvolatile configuration register bits.

### **Device Configurability**

The N25Q family offers additional features that are configured through the nonvolatile configuration register for default and/or nonvolatile settings. Volatile settings can be configured through the volatile and volatile-enhanced configuration registers. These configurable features include the following:

- Number of dummy cycles for the fast READ commands

- Output buffer impedance

- SPI protocol types (extended SPI, DIO-SPI, or QIO-SPI)

- Required XIP mode

- Enabling/disabling HOLD (RESET function)

- Enabling/disabling wrap mode

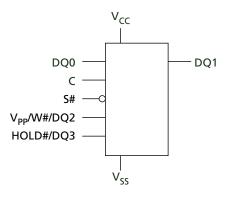

#### Figure 1: Logic Diagram

Note: 1. Reset functionality is available in devices with a dedicated part number. See Part Number Ordering Information for more details.

### **Signal Assignments**

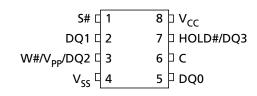

#### Figure 2: 8-Pin, VDFPN8 – MLP8 and SOP2 – SO8W (Top View)

- Notes: 1. On the underside of the MLP8 package, there is an exposed central pad that is pulled internally to  $V_{SS}$  and must not be connected to any other voltage or signal line on the PCB.

- 2. Reset functionality is available in devices with a dedicated part number. See Part Number Ordering Information for complete package names and details.

#### Figure 3: 16-Pin, Plastic Small Outline – SO16 (Top View)

| HOLD#/DQ3 □ | 1 | 16 🗆 | С                       |

|-------------|---|------|-------------------------|

| $V_{cc}$    | 2 | 15 🗆 | DQ0                     |

| DNU 🗆       | 3 | 14 🗆 | DNU                     |

| DNU 🗆       | 4 | 13 🗆 | DNU                     |

| DNU 🗆       | 5 | 12 🗖 | DNU                     |

| DNU 🗆       | 6 | 11 🗅 | DNU                     |

| S# ⊏        | 7 | 10 🗖 | V <sub>SS</sub>         |

| DQ1 🗆       | 8 | 9 🗆  | W#/V <sub>PP</sub> /DQ2 |

|             |   |      |                         |

Note: 1. Reset functionality is available in devices with a dedicated part number. See Part Number Ordering Information for complete package names and details.

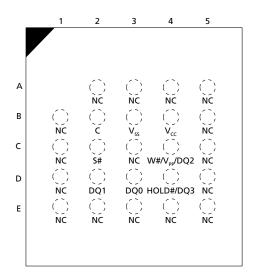

#### Figure 4: 24-Ball TBGA (Balls Down)

Note: 1. See Part Number Ordering Information for complete package names and details.

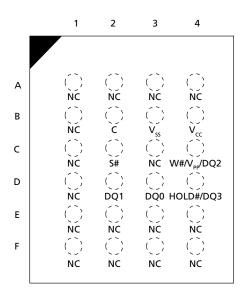

#### Figure 5: 24-Ball TBGA , 4x6 (Balls Down)

Note: 1. See Part Number Ordering Information for complete package names and details.

### **Signal Descriptions**

The signal description table below is a comprehensive list of signals for the N25 family devices. All signals listed may not be supported on this device. See Signal Assignments for information specific to this device.

#### **Table 1: Signal Descriptions**

| Symbol | Туре              | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|--------|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| С      | Input             | <b>Clock:</b> Provides the timing of the serial interface. Commands, addresses, or data present at serial data inputs are latched on the rising edge of the clock. Data is shifted out on the falling edge of the clock.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| S#     | Input             | <b>Chip select:</b> When S# is HIGH, the device is deselected and DQ1 is at High-Z. When in exten-<br>ded SPI mode, with the device deselected, DQ1 is tri-stated. Unless an internal PROGRAM,<br>ERASE, or WRITE STATUS REGISTER cycle is in progress, the device enters standby power mode<br>(not deep power-down mode). Driving S# LOW enables the device, placing it in the active pow-<br>er mode. After power-up, a falling edge on S# is required prior to the start of any command.                                                                                                                                                                                                                                                                                |

| DQ0    | Input<br>and I/O  | <ul> <li>Serial data: Transfers data serially into the device. It receives command codes, addresses, and the data to be programmed. Values are latched on the rising edge of the clock. DQ0 is used for input/output during the following operations: DUAL OUTPUT FAST READ, QUAD OUTPUT FAST READ, DUAL INPUT/OUTPUT FAST READ, and QUAD INPUT/OUTPUT FAST READ. When used for output, data is shifted out on the falling edge of the clock.</li> <li>In DIO-SPI, DQ0 always acts as an input/output, with the exception of the PROGRAM or ERASE cycle performed with V<sub>PP</sub>. The device temporarily enters the extended SPI protocol and then returns to QIO-SPI as soon as V<sub>PP</sub> goes LOW.</li> </ul>                                                   |

| DQ1    | Output<br>and I/O | <ul> <li>Serial data:Transfers data serially out of the device. Data is shifted out on the falling edge of the clock. DQ1 is used for input/output during the following operations: DUAL INPUT FAST PROGRAM, QUAD INPUT FAST PROGRAM, DUAL INPUT EXTENDED FAST PROGRAM, and QUAD INPUT EXTENDED FAST PROGRAM. When used for input, data is latched on the rising edge of the clock.</li> <li>In DIO-SPI, DQ1 always acts as an input/output.</li> <li>In QIO-SPI, DQ1 always acts as an input/output, with the exception of the PROGRAM or ERASE cycle performed with the enhanced program supply voltage (V<sub>PP</sub>). In this case the device temporarily enters the extended SPI protocol and then returns to QIO-SPI as soon as V<sub>PP</sub> goes LOW.</li> </ul> |

| DQ2    | Input<br>and I/O  | <b>DQ2:</b> When in QIO-SPI mode or in extended SPI mode using QUAD FAST READ commands, the signal functions as DQ2, providing input/output.<br>All data input drivers are always enabled except when used as an output. Micron recommends customers drive the data signals normally (to avoid unnecessary switching current) and float the signals before the memory device drives data on them.                                                                                                                                                                                                                                                                                                                                                                           |

| DQ3    | Input<br>and I/O  | <b>DQ3:</b> When in quad SPI mode or in extended SPI mode using quad FAST READ commands, the signal functions as DQ3, providing input/output. HOLD# is disabled and RESET# is disabled if the device is selected.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

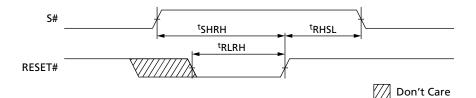

| RESET# | Control<br>Input  | <b>RESET:</b> This is a hardware RESET# signal. When RESET# is driven HIGH, the memory is in the normal operating mode. When RESET# is driven LOW, the memory enters reset mode and output is High-Z. If RESET# is driven LOW while an internal WRITE, PROGRAM, or ERASE operation is in progress, data may be lost.                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

#### **Table 1: Signal Descriptions (Continued)**

| Symbol          | Туре             | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|-----------------|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| HOLD#           | Control<br>Input | <ul> <li>HOLD: Pauses any serial communications with the device without deselecting the device. DQ1 (output) is High-Z. DQ0 (input) and the clock are "Don't Care." To enable HOLD, the device must be selected with S# driven LOW.</li> <li>HOLD# is used for input/output during the following operations: QUAD OUTPUT FAST READ, QUAD INPUT/OUTPUT FAST READ, QUAD INPUT FAST PROGRAM, and QUAD INPUT EXTENDED FAST PROGRAM.</li> <li>In QIO-SPI, HOLD# acts as an I/O (DQ3 functionality), and the HOLD# functionality is disabled when the device is selected. When the device is deselected (S# is HIGH) in parts with RESET# functionality, it is possible to reset the device unless this functionality is not disabled by means of dedicated registers bits.</li> <li>The HOLD# functionality can be disabled using bit 4 of the NVCR or bit 4 of the VECR. On devices that include DTR mode capability, the HOLD# functionality is disabled as soon as a DTR operation is recognized.</li> </ul> |

| W#              | Control<br>Input | <b>Write protect:</b> W# can be used as a protection control input or in QIO-SPI operations. When in extended SPI with single or dual commands, the WRITE PROTECT function is selectable by the voltage range applied to the signal. If voltage range is low (0V to V <sub>CC</sub> ), the signal acts as a write protection control input. The memory size protected against PROGRAM or ERASE operations is locked as specified in the status register block protect bits 3:0.<br>W# is used as an input/output (DQ2 functionality) during QUAD INPUT FAST READ and QUAD INPUT/OUTPUT FAST READ operations and in QIO-SPI.                                                                                                                                                                                                                                                                                                                                                                                |

| V <sub>PP</sub> | Power            | <ul> <li>Supply voltage: If V<sub>PP</sub> is in the voltage range of V<sub>PPH</sub>, the signal acts as an additional power supply, as defined in the AC Measurement Conditions table.</li> <li>During QIFP, QIEFP, and QIO-SPI PROGRAM/ERASE operations, it is possible to use the additional V<sub>PP</sub> power supply to speed up internal operations. However, to enable this functionality, it is necessary to set bit 3 of the VECR to 0.</li> <li>In this case, V<sub>PP</sub> is used as an I/O until the end of the operation. After the last input data is shifted in, the application should apply V<sub>PP</sub> voltage to V<sub>PP</sub> within 200ms to speed up the internal operations. If the V<sub>PP</sub> voltage is not applied within 200ms, the PROGRAM/ERASE operations start at standard speed.</li> <li>The default value of VECR bit 3 is 1, and the V<sub>PP</sub> functionality for quad I/O modify operations is disabled.</li> </ul>                                   |

| V <sub>CC</sub> | Power            | Device core power supply: Source voltage.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| V <sub>SS</sub> | Ground           | Ground: Reference for the V <sub>CC</sub> supply voltage.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| DNU             | _                | Do not use.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| NC              | _                | No connect.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

### **Memory Organization**

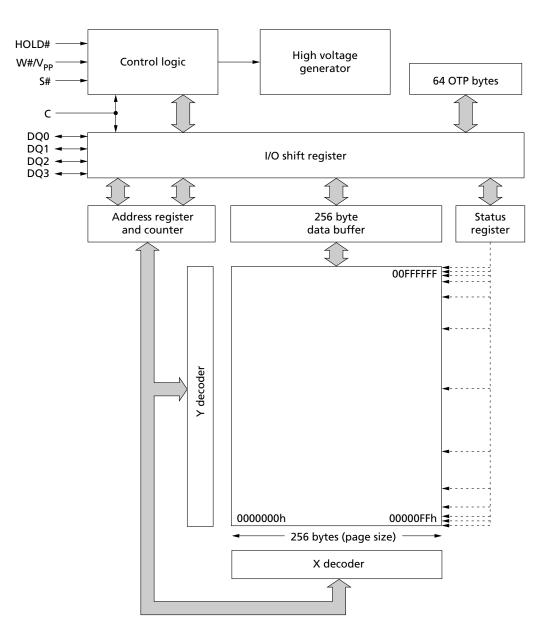

#### **Memory Configuration and Block Diagram**

Each page of memory can be individually programmed. Bits are programmed from one through zero. The device is subsector, sector, or bulk-erasable, but not page-erasable. Bits are erased from zero through one. The memory is configured as 16,777,216 bytes (8 bits each); 256 sectors (64KB each); 4096 subsectors (4KB each); and 65,536 pages (256 bytes each); and 64 OTP bytes are located outside the main memory array.

#### Figure 6: Block Diagram

### Memory Map – 128Mb Density

#### Table 2: Sectors[255:0]

|        |           | Address    | Range      |

|--------|-----------|------------|------------|

| Sector | Subsector | Start      | End        |

| 255    | 4095      | 00FF F000h | 00FF FFFFh |

|        | ÷         | :          | :          |

|        | 4080      | 00FF 0000h | 00FF 0FFFh |

| :      | :         | :          | :          |

| 127    | 2047      | 007F F000h | 007F FFFFh |

|        | ÷         | :          | :          |

|        | 2032      | 007F 0000h | 007F 0FFFh |

| ÷      | :         | :          | :          |

| 63     | 1023      | 003F F000h | 003F FFFFh |

|        | :         | :          | :          |

|        | 1008      | 003F 0000h | 003F 0FFFh |

| ÷      | :         | :          | :          |

| 0      | 15        | 0000 F000h | 0000 FFFFh |

|        | :         | :          | :          |

|        | 0         | 0000 0000h | 0000 0FFFh |

### **Device Protection**

#### **Table 3: Data Protection using Device Protocols**

Note 1 applies to the entire table

| Protection by:                    | Description                                                                                                                                                        |

|-----------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Power-on reset and internal timer | Protects the device against inadvertent data changes while the power supply is out-<br>side the operating specification.                                           |

| Command execution check           | Ensures that the number of clock pulses is a multiple of one byte before executing a PROGRAM or ERASE command, or any command that writes to the device registers. |

| WRITE ENABLE operation            | Ensures that commands modifying device data must be preceded by a WRITE ENABLE command, which sets the write enable latch bit in the status register.              |

Note: 1. Extended, dual, and quad SPI protocol functionality ensures that device data is protected from excessive noise.

#### **Table 4: Memory Sector Protection Truth Table**

| Sector Lock Register<br>Sector Lock Sector Write Lock<br>Down Bit Bit |   |                                                                                                                        |

|-----------------------------------------------------------------------|---|------------------------------------------------------------------------------------------------------------------------|

|                                                                       |   | Memory Sector Protection Status                                                                                        |

| 0                                                                     | 0 | Sector unprotected from PROGRAM and ERASE operations. Protection status reversible.                                    |

| 0                                                                     | 1 | Sector protected from PROGRAM and ERASE operations. Protection status reversible.                                      |

| 1                                                                     | 0 | Sector unprotected from PROGRAM and ERASE operations. Protection status not reversible except by power cycle or reset. |

| 1                                                                     | 1 | Sector protected from PROGRAM and ERASE operations. Protection status not reversible except by power cycle or reset.   |

Note 1 applies to the entire table

Note: 1. Sector lock register bits are written to when the WRITE LOCK REGISTER command is executed. The command will not execute unless the sector lock down bit is cleared (see the WRITE LOCK REGISTER command).

#### **Table 5: Protected Area Sizes – Upper Area**

| Status Register Content |     |     |     |     | Memory Content |                    |  |

|-------------------------|-----|-----|-----|-----|----------------|--------------------|--|

| Top/<br>Bottom<br>Bit   | BP3 | BP2 | BP1 | BPO | Protected Area | Unprotected Area   |  |

| 0                       | 0   | 0   | 0   | 0   | None           | All sectors        |  |

| 0                       | 0   | 0   | 0   | 1   | Upper 256th    | Sectors (0 to 254) |  |

| 0                       | 0   | 0   | 1   | 0   | Upper 128th    | Sectors (0 to 253) |  |

| 0                       | 0   | 0   | 1   | 1   | Upper 64th     | Sectors (0 to 251) |  |

| 0                       | 0   | 1   | 0   | 0   | Upper 32th     | Sectors (0 to 247) |  |

| 0                       | 0   | 1   | 0   | 1   | Upper 16nd     | Sectors (0 to 239) |  |

#### Table 5: Protected Area Sizes - Upper Area (Continued)

| Status Register Content |     |     | Memory | v Content |                |                    |

|-------------------------|-----|-----|--------|-----------|----------------|--------------------|

| Top/<br>Bottom<br>Bit   | BP3 | BP2 | BP1    | BPO       | Protected Area | Unprotected Area   |

| 0                       | 0   | 1   | 1      | 0         | Upper 8th      | Sectors (0 to 223) |

| 0                       | 0   | 1   | 1      | 1         | Upper quarter  | Sectors (0 to 191) |

| 0                       | 1   | 0   | 0      | 0         | Upper half     | Sectors (0 to 127) |

| 0                       | 1   | 0   | 0      | 1         | All sectors    | None               |

| 0                       | 1   | 0   | 1      | 0         | All sectors    | None               |

| 0                       | 1   | 0   | 1      | 1         | All sectors    | None               |

| 0                       | 1   | 1   | 0      | 0         | All sectors    | None               |

| 0                       | 1   | 1   | 0      | 1         | All sectors    | None               |

| 0                       | 1   | 1   | 1      | 0         | All sectors    | None               |

| 0                       | 1   | 1   | 1      | 1         | All sectors    | None               |

#### Note 1 applies to the entire table

Note: 1. See the Status Register for details on the top/bottom bit and the BP 3:0 bits.

#### **Table 6: Protected Area Sizes – Lower Area**

#### Note 1 applies to the entire table

|                       | Statu | s Register Co | ontent |     | Memory         | Content              |

|-----------------------|-------|---------------|--------|-----|----------------|----------------------|

| Top/<br>Bottom<br>Bit | BP3   | BP2           | BP1    | BPO | Protected Area | Unprotected Area     |

| 1                     | 0     | 0             | 0      | 0   | None           | All sectors          |

| 1                     | 0     | 0             | 0      | 1   | Lower 256th    | Sectors (1 to 255)   |

| 1                     | 0     | 0             | 1      | 0   | Lower 128th    | Sectors (2 to 255)   |

| 1                     | 0     | 0             | 1      | 1   | Lower 64th     | Sectors (4 to 255)   |

| 1                     | 0     | 1             | 0      | 0   | Lower 32th     | Sectors (8 to 255)   |

| 1                     | 0     | 1             | 0      | 1   | Lower 16nd     | Sectors (16 to 255)  |

| 1                     | 0     | 1             | 1      | 0   | Lower 8th      | Sectors (32 to 255)  |

| 1                     | 0     | 1             | 1      | 1   | Lower quarter  | Sectors (64 to 255)  |

| 1                     | 1     | 0             | 0      | 0   | Lower half     | Sectors (128 to 255) |

| 1                     | 1     | 0             | 0      | 1   | All sectors    | None                 |

| 1                     | 1     | 0             | 1      | 0   | All sectors    | None                 |

| 1                     | 1     | 0             | 1      | 1   | All sectors    | None                 |

| 1                     | 1     | 1             | 0      | 0   | All sectors    | None                 |

| 1                     | 1     | 1             | 0      | 1   | All sectors    | None                 |

| 1                     | 1     | 1             | 1      | 0   | All sectors    | None                 |

| 1                     | 1     | 1             | 1      | 1   | All sectors    | None                 |

Note: 1. See the Status Register for details on the top/bottom bit and the BP 3:0 bits.

### **Serial Peripheral Interface Modes**

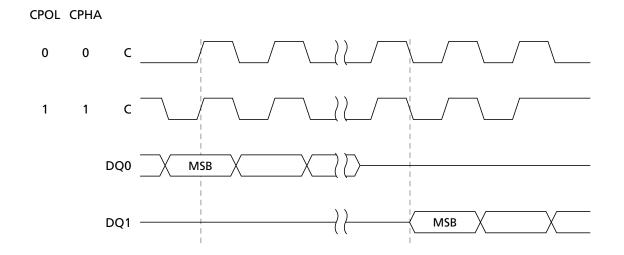

The device can be driven by a microcontroller while its serial peripheral interface is in either of the two modes shown here. The difference between the two modes is the clock polarity when the bus master is in standby mode and not transferring data. Input data is latched in on the rising edge of the clock, and output data is available from the falling edge of the clock.

#### Table 7: SPI Modes

Note 1 applies to the entire table

| SPI Modes          | Clock Polarity                          |

|--------------------|-----------------------------------------|

| CPOL = 0, CPHA = 0 | C remains at 0 for (CPOL = 0, CPHA = 0) |

| CPOL = 1, CPHA = 1 | C remains at 1 for (CPOL = 1, CPHA = 1) |

Note: 1. The listed SPI modes are supported in extended, dual, and quad SPI protocols.

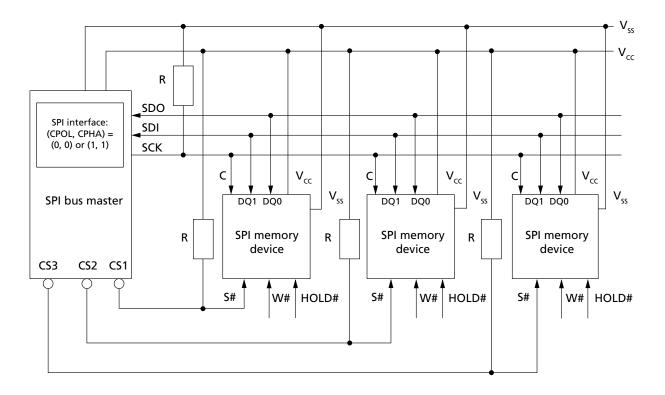

Shown below is an example of three memory devices in extended SPI protocol in a simple connection to an MCU on an SPI bus. Because only one device is selected at a time, that one device drives DQ1, while the other devices are High-Z.

Resistors ensure the device is not selected if the bus master leaves S# High-Z. The bus master might enter a state in which all input/output is High-Z simultaneously, such as when the bus master is reset. Therefore, the serial clock must be connected to an external pull-down resistor so that S# is pulled HIGH while the serial clock is pulled LOW. This ensures that S# and the serial clock are not HIGH simultaneously and that <sup>t</sup>SHCH is met. The typical resistor value of  $100k\Omega$ , assuming that the time constant R × Cp (Cp = parasitic capacitance of the bus line), is shorter than the time the bus master leaves the SPI bus in High-Z.

**Example:** Cp = 50pF, that is  $R \times Cp = 5\mu s$ . The application must ensure that the bus master never leaves the SPI bus High-Z for a time period shorter than 5 $\mu$ s. W# and HOLD# should be driven either HIGH or LOW, as appropriate.

#### **Figure 8: SPI Modes**

### **SPI Protocols**

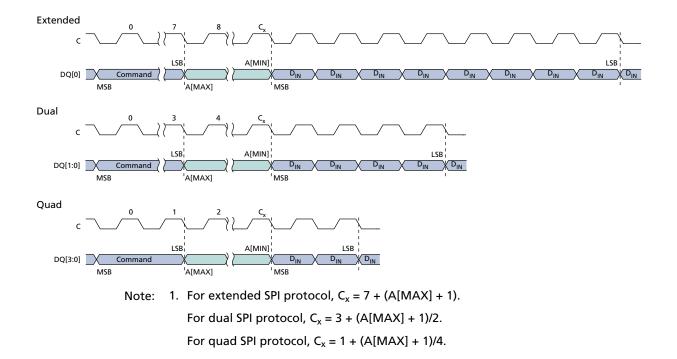

#### Table 8: Extended, Dual, and Quad SPI Protocols

| Protocol<br>Name  | Com-<br>mand<br>Input | Address<br>Input                                           | Data<br>Input/Output                               | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|-------------------|-----------------------|------------------------------------------------------------|----------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Extended          | DQ0                   | Multiple DQ <i>n</i><br>lines, depending<br>on the command | Multiple DQn<br>lines, depending<br>on the command | Device default protocol from the factory. Additional com-<br>mands extend the standard SPI protocol and enable address<br>or data transmission on multiple DQ <i>n</i> lines.                                                                                                                                                                                                                                                                                                                                                         |

| Dual              | DQ[1:0]               | DQ[1:0]                                                    | DQ[1:0]                                            | <b>Volatile selectable:</b> When the enhanced volatile configu-<br>ration register bit 6 is set to 0 and bit 7 is set to 1, the de-<br>vice enters the dual SPI protocol immediately after the<br>WRITE ENHANCED VOLATILE CONFIGURATION REGISTER<br>command. The device returns to the default protocol after<br>the next power-on. In addition, the device can return to de-<br>fault protocol using the rescue sequence or through new<br>WRITE ENHANCED VOLATILE CONFIGURATION REGISTER<br>command, without power-off or power-on. |

|                   |                       |                                                            |                                                    | <b>Nonvolatile selectable:</b> When nonvolatile configuration register bit 2 is set, the device enters the dual SPI protocol after the next power-on. Once this register bit is set, the device defaults to the dual SPI protocol after all subsequent power-on sequences until the nonvolatile configuration register bit is reset to 1.                                                                                                                                                                                             |

| Quad <sup>1</sup> | DQ[3:0]               | DQ[3:0]                                                    | DQ[3:0]                                            | <b>Volatile selectable:</b> When the enhanced volatile configu-<br>ration register bit 7 is set to 0, the device enters the quad<br>SPI protocol immediately after the WRITE ENHANCED VOL-<br>ATILE CONFIGURATION REGISTER command. The device re-<br>turns to the default protocol after the next power-on. In ad-<br>dition, the device can return to default protocol using the<br>rescue sequence or through new WRITE ENHANCED VOLA-<br>TILE CONFIGURATION REGISTER command, without power-<br>off or power-on.                  |

|                   |                       |                                                            |                                                    | <b>Nonvolatile selectable:</b> When nonvolatile configuration register bit 3 is set to 0, the device enters the quad SPI protocol after the next power-on. Once this register bit is set, the device defaults to the quad SPI protocol after all subsequent power-on sequences until the nonvolatile configuration register bit is reset to 1.                                                                                                                                                                                        |

Note: 1. In quad SPI protocol, all command/address input and data I/O are transmitted on four lines except during a PROGRAM and ERASE cycle performed with V<sub>PP</sub>. In this case, the device enters the extended SPI protocol to temporarily allow the application to perform a PROGRAM/ERASE SUSPEND operation or to check the write-in-progress bit in the status register or the program/erase controller bit in the flag status register. Then, when V<sub>PP</sub> goes LOW, the device returns to the quad SPI protocol.

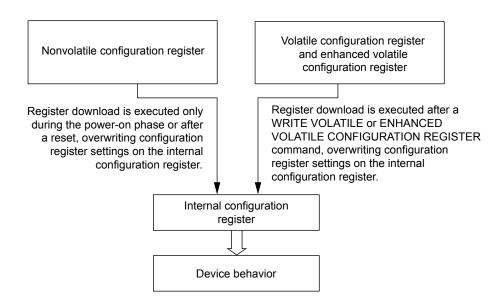

### **Nonvolatile and Volatile Registers**

The device features the following volatile and nonvolatile registers that users can access to store device parameters and operating configurations:

- Status register

- Nonvolatile and volatile configuration registers

- Enhanced volatile configuration register

- · Flag status register

- Lock register

Note: The lock register is defined in READ LOCK REGISTER Command.

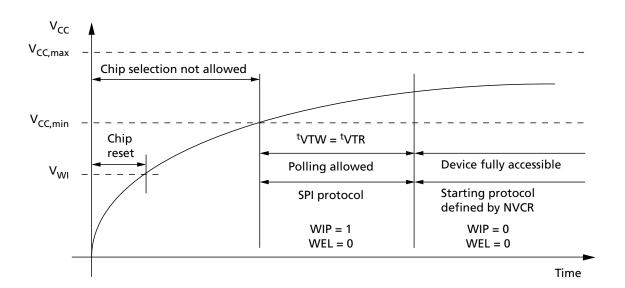

In addition to these user-accessible registers, the working condition of memory is set by an internal configuration register that is not directly accessible to users. As shown below, parameters in the internal configuration register are loaded from the nonvolatile configuration register during each device boot phase or power-on reset. In this sense, then, the nonvolatile configuration register contains the default settings of memory.

Also, during the life of an application, each time a WRITE VOLATILE or ENHANCED VOLATILE CONFIGURATION REGISTER command executes to set configuration parameters in these respective registers, these new settings are copied to the internal configuration register. Therefore, memory settings can be changed in real time. However, at the next power-on reset, the memory boots according to the memory settings defined in the nonvolatile configuration register parameters.

#### **Figure 9: Internal Configuration Register**

#### **Status Register**

#### **Table 9: Status Register Bit Definitions**

Note 1 applies to entire table

| Bit    | Name                                    | Settings                                                                                     | Description                                                                                                                                                                                                                                       | Notes |

|--------|-----------------------------------------|----------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| 7      | Status register<br>write enable/disable | 0 = Enabled<br>1 = Disabled                                                                  | <b>Nonvolatile bit:</b> Used with the W#/V <sub>PP</sub> signal to enable or disable writing to the status register.                                                                                                                              | 2     |

| 5      | Top/bottom                              | 0 = Top<br>1 = Bottom                                                                        | <b>Nonvolatile bit:</b> Determines whether the protected memory area defined by the block protect bits starts from the top or bottom of the memory array.                                                                                         | 3     |

| 6, 4:2 | Block protect 3–0                       | See Protected Area<br>Sizes – Upper Area<br>and Lower Area<br>tables in Device<br>Protection | <b>Nonvolatile bit:</b> Defines memory to be software protec-<br>ted against PROGRAM or ERASE operations. When one or<br>more block protect bits is set to 1, a designated memory<br>area is protected from PROGRAM and ERASE operations.         | 3     |

| 1      | Write enable latch                      | 0 = Cleared (Default)<br>1 = Set                                                             | <b>Volatile bit:</b> The device always powers up with this bit cleared to prevent inadvertent WRITE STATUS REGISTER, PROGRAM, or ERASE operations. To enable these operations, the WRITE ENABLE operation must be executed first to set this bit. | 4     |

| 0      | Write in progress                       | 0 = Ready<br>1 = Busy                                                                        | Volatile bit: Indicates if one of the following command cy-<br>cles is in progress:<br>WRITE STATUS REGISTER<br>WRITE NONVOLATILE CONFIGURATION REGISTER<br>PROGRAM<br>ERASE                                                                      | 4     |

Notes: 1. Bits can be read from or written to using READ STATUS REGISTER or WRITE STATUS REG-ISTER commands, respectively.

- 2. The status register write enable/disable bit, combined with the W#/V<sub>PP</sub> signal as described in the Signal Descriptions, provides hardware data protection for the device as follows: When the enable/disable bit is set to 1, and the W#/V<sub>PP</sub> signal is driven LOW, the status register nonvolatile bits become read-only and the WRITE STATUS REGISTER operation will not execute. The only way to exit this hardware-protected mode is to drive W#/V<sub>PP</sub> HIGH.

- 3. See Protected Area Sizes tables in Device Protection. The BULK ERASE command is executed only if all bits are 0.

- 4. Volatile bits are cleared to 0 by a power cycle or reset.

#### **Nonvolatile and Volatile Configuration Registers**

#### **Table 10: Nonvolatile Configuration Register Bit Definitions**

| Bit   | Name                               | Settings                                                                                                                                                                                                                               | Description                                                                                                                                                                                    | Notes |

|-------|------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| 15:12 | Number of<br>dummy clock<br>cycles | 0000 (identical to 1111)<br>0001<br>0010<br>1101<br>1110                                                                                                                                                                               | Sets the number of dummy clock cycles subse-<br>quent to all FAST READ commands.<br>The default setting targets the maximum al-<br>lowed frequency and guarantees backward com-<br>patibility. | 2, 3  |

| 11:9  | XIP mode at<br>power-on re-<br>set | 1111<br>000 = XIP: Fast Read<br>001 = XIP: Dual Output Fast Read<br>010 = XIP: Dual I/O Fast Read<br>011 = XIP: Quad Output Fast Read<br>100 = XIP: Quad I/O Fast Read<br>101 = Reserved<br>110 = Reserved<br>111 = Disabled (Default) | Enables the device to operate in the selected XIP mode immediately after power-on reset.                                                                                                       |       |

| 8:6   | Output driver<br>strength          | 000 = Reserved<br>001 = 90 Ohms<br>010 = 60 Ohms<br>011 = 45 Ohms<br>100 = Reserved<br>101 = 20 Ohms<br>110 = 15 Ohms<br>111 = 30 (Default)                                                                                            | Optimizes impedance at V <sub>CC</sub> /2 output voltage.                                                                                                                                      |       |

| 5     | Reserved                           | x                                                                                                                                                                                                                                      | "Don't Care."                                                                                                                                                                                  |       |

| 4     | Reset/hold                         | 0 = Disabled<br>1 = Enabled (Default)                                                                                                                                                                                                  | Enables or disables hold or reset.<br>(Available on dedicated part numbers.)                                                                                                                   |       |

| 3     | Quad I/O pro-<br>tocol             | 0 = Enabled<br>1 = Disabled (Default, Extended SPI prot-<br>cocol)                                                                                                                                                                     | Enables or disables quad I/O protocol.                                                                                                                                                         | 4     |

| 2     | Dual I/O pro-<br>tocol             | 0 = Enabled<br>1 = Disabled (Default, Extended SPI pro-<br>tocol)                                                                                                                                                                      | Enables or disables dual I/O protocol.                                                                                                                                                         | 4     |

| 1:0   | Reserved                           | x                                                                                                                                                                                                                                      | "Don't Care."                                                                                                                                                                                  |       |

Notes: 1. Settings determine device memory configuration after power-on. The device ships from the factory with all bits erased to 1 (FFFFh). The register is read from or written to by READ NONVOLATILE CONFIGURATION REGISTER or WRITE NONVOLATILE CONFIGURA-TION REGISTER commands, respectively.

- 2. The 0000 and 1111 settings are identical in that they both define the default state, which is the maximum frequency of  $f_c = 108$  MHz. This ensures backward compatibility.

- 3. If the number of dummy clock cycles is insufficient for the operating frequency, the memory reads wrong data. The number of cycles must be set according to and sufficient

#### 128Mb, 3V, Multiple I/O Serial Flash Memory Nonvolatile and Volatile Registers

for the clock frequency, which varies by the type of FAST READ command, as shown in the Supported Clock Frequencies table.

4. If bits 2 and 3 are both set to 0, the device operates in quad I/O. When bits 2 or 3 are reset to 0, the device operates in dual I/O or quad I/O respectively, after the next power-on.

#### Table 11: Volatile Configuration Register Bit Definitions

| Bit | Name                              | Settings                                                         | Description                                                                                                                                                                                   | Notes |

|-----|-----------------------------------|------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| 7:4 | Number of dum-<br>my clock cycles | 0000 (identical to 1111)<br>0001<br>0010<br>1101<br>1110<br>1111 | Sets the number of dummy clock cycles subsequent to<br>all FAST READ commands.<br>The default setting targets maximum allowed frequen-<br>cy and guarantees backward compatibility.           | 2, 3  |

| 3   | XIP                               | 0<br>1                                                           | Enables or disables XIP. For device part numbers with<br>feature digit equal to 2 or 4, this bit is always "Don't<br>Care," so the device operates in XIP mode without set-<br>ting this bit. |       |

| 2   | Reserved                          | X = Default                                                      | 0b = Fixed value.                                                                                                                                                                             |       |

| 1:0 | Wrap                              | 00 = 16-byte boundary<br>aligned                                 | 16-byte wrap: Output data wraps within an aligned 16-<br>byte boundary starting from the 3-byte address issued<br>after the command code.                                                     | 4     |

|     |                                   | 01 = 32-byte boundary<br>aligned                                 | 32-byte wrap: Output data wraps within an aligned 32-<br>byte boundary starting from the 3-byte address issued<br>after the command code.                                                     |       |

|     |                                   | 10 = 64-byte boundary<br>aligned                                 | 64-byte wrap: Output data wraps within an aligned 64-<br>byte boundary starting from the 3-byte address issued<br>after the command code.                                                     |       |

|     |                                   | 11 = sequential (default)                                        | Continuous reading (default): All bytes are read sequentially.                                                                                                                                |       |

- Notes: 1. Settings determine the device memory configuration upon a change of those settings by the WRITE VOLATILE CONFIGURATION REGISTER command. The register is read from or written to by READ VOLATILE CONFIGURATION REGISTER or WRITE VOLATILE CONFIGURATION REGISTER commands respectively.

- 2. The 0000 and 1111 settings are identical in that they both define the default state, which is the maximum frequency of  $f_c = 108$  MHz. This ensures backward compatibility.

- 3. If the number of dummy clock cycles is insufficient for the operating frequency, the memory reads wrong data. The number of cycles must be set according to and be sufficient for the clock frequency, which varies by the type of FAST READ command, as shown in the Supported Clock Frequencies table.

- 4. See the Sequence of Bytes During Wrap table.

| Starting Address | 16-Byte Wrap     | 32-Byte Wrap     | 64-Byte Wrap   |

|------------------|------------------|------------------|----------------|

| 0                | 0-1-215-0-1      | 0-1-231-0-1      | 0-1-263-0-1    |

| 1                | 1-215-0-1-2      | 1-231-0-1-2      | 1-263-0-1-2    |

| 15               | 15-0-1-2-315-0-1 | 15-16-1731-0-1   | 15-16-1763-0-1 |

| 31               | 31-16-1731-16-17 | 31-0-1-2-331-0-1 | 31-32-3363-0-1 |

| 63               | 63-48-4963-48-49 | 63-32-3363-32-33 | 63-0-163-0-1   |

#### Table 12: Sequence of Bytes During Wrap

#### **Table 13: Supported Clock Frequencies**

#### Note 1 applies to entire table

| Number of<br>Dummy<br>Clock Cycles | FAST READ | DUAL OUTPUT<br>FAST READ | DUAL I/O FAST<br>READ | QUAD OUTPUT<br>FAST READ | QUAD I/O FAST<br>READ | Unit   |

|------------------------------------|-----------|--------------------------|-----------------------|--------------------------|-----------------------|--------|

| 1                                  | 90        | 80                       | 50                    | 43                       | 30                    |        |

| 2                                  | 100       | 90                       | 70                    | 60                       | 40                    |        |

| 3                                  | 108       | 100                      | 80                    | 75                       | 50                    |        |

| 4                                  | 108       | 105                      | 90                    | 90                       | 60                    |        |

| 5                                  | 108       | 108                      | 100                   | 100                      | 70                    | MHz    |

| 6                                  | 108       | 108                      | 105                   | 105                      | 80                    | IVITIZ |

| 7                                  | 108       | 108                      | 108                   | 108                      | 86                    |        |

| 8                                  | 108       | 108                      | 108                   | 108                      | 95                    |        |

| 9                                  | 108       | 108                      | 108                   | 108                      | 105                   |        |

| 10                                 | 108       | 108                      | 108                   | 108                      | 108                   |        |

Note: 1. Values are guaranteed by characterization and not 100% tested in production.

### **Enhanced Volatile Configuration Register**

#### **Table 14: Enhanced Volatile Configuration Register Bit Definitions**

| Bit | Name              | Settings                                                        | Description                                                                  | Notes |

|-----|-------------------|-----------------------------------------------------------------|------------------------------------------------------------------------------|-------|

| 7   | Quad I/O protocol | 0 = Enabled<br>1 = Disabled (Default,<br>extended SPI protocol) | Enables or disables quad I/O protocol.                                       | 2     |

| 6   | Dual I/O protocol | 0 = Enabled<br>1 = Disabled (Default,<br>extended SPI protocol) | Enables or disables dual I/O protocol.                                       | 2     |

| 5   | Reserved          | X = Default                                                     | 0b = Fixed value.                                                            |       |

| 4   | Reset/hold        | 0 = Disabled<br>1 = Enabled (Default)                           | Enables or disables hold or reset.<br>(Available on dedicated part numbers.) |       |

#### Table 14: Enhanced Volatile Configuration Register Bit Definitions (Continued)

| Bit | Name                   | Settings                                                                                                                                    | Description                                                                                                                           | Notes |

|-----|------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|-------|

| 3   | $V_{PP}$ accelerator   | 0 = Enabled<br>1 = Disabled (Default)                                                                                                       | Enables or disables V <sub>PP</sub> acceleration for QUAD<br>INPUT FAST PROGRAM and QUAD INPUT EX-<br>TENDED FAST PROGRAM OPERATIONS. |       |

| 2:0 | Output driver strength | 000 = Reserved<br>001 = 90 Ohms<br>010 = 60 Ohms<br>011 = 45 Ohms<br>100 = Reserved<br>101 = 20 Ohms<br>110 = 15 Ohms<br>111 = 30 (Default) | Optimizes impedance at V <sub>CC</sub> /2 output voltage.                                                                             |       |

- Notes: 1. Settings determine the device memory configuration upon a change of those settings by the WRITE ENHANCED VOLATILE CONFIGURATION REGISTER command. The register is read from or written to in all protocols by READ ENHANCED VOLATILE CONFIGURATION REGISTER or WRITE ENHANCED VOLATILE CONFIGURATION REGISTER commands, respectively.

- 2. If bits 6 and 7 are both set to 0, the device operates in quad I/O. When either bit 6 or 7 is reset to 0, the device operates in dual I/O or guad I/O, respectively, following the next WRITE ENHANCED VOLATILE CONFIGURATION command.

### **Flag Status Register**

#### **Table 15: Flag Status Register Bit Definitions**

| Bit | Name                              | Settings                                     | Description                                                                                                                                                                                             | Notes |

|-----|-----------------------------------|----------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| 7   | Program or<br>erase<br>controller | 0 = Busy<br>1 = Ready                        | <b>Status bit:</b> Indicates whether a PROGRAM, ERASE,<br>WRITE STATUS REGISTER, or WRITE NONVOLATILE CON-<br>FIGURATION command cycle is in progress.                                                  | 2, 3  |

| 6   | Erase suspend                     | 0 = Not in effect<br>1 = In effect           | <b>Status bit:</b> Indicates whether an ERASE operation has been or is going to be suspended.                                                                                                           | 3     |

| 5   | Erase                             | 0 = Clear<br>1 = Failure or protection error | <b>Error bit:</b> Indicates whether an ERASE operation has succeeded or failed.                                                                                                                         | 4, 5  |

| 4   | Program                           | 0 = Clear<br>1 = Failure or protection error | <b>Error bit:</b> Indicates whether a PROGRAM operation has succeeded or failed. Also indicates an attempt to program a 0 to a 1 when $V_{PP} = V_{PPH}$ and the data pattern is a multiple of 64 bits. | 4, 5  |

| 3   | V <sub>PP</sub>                   | 0 = Enabled<br>1 = Disabled (Default)        | <b>Error bit:</b> Indicates an invalid voltage on V <sub>PP</sub> during a PROGRAM or ERASE operation.                                                                                                  | 4, 5  |

| 2   | Program<br>suspend                | 0 = Not in effect<br>1 = In effect           | <b>Status bit:</b> Indicates whether a PROGRAM operation has been or is going to be suspended.                                                                                                          | 3     |

#### Table 15: Flag Status Register Bit Definitions (Continued)

Note 1 applies to entire table

| - 2 |     |            |          |                                                                                                                                                                                                      |       |  |