## Advance Information

## Three-Phase Gate Driver IC

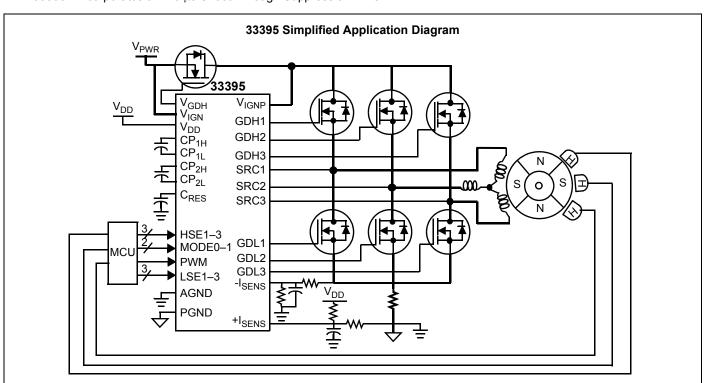

The 33395 simplifies the design of high-power BLDC motor control design by combining the gate drive, charge pump, current sense, and protection circuitry necessary to drive a three-phase bridge configuration of six N-channel power MOSFETs. Mode logic is incorporated to route a pulse width modulation (PWM) signal to either the low-side MOSFETs or high-side MOSFETs of the bridge, or to provide complementary PWM outputs to both the low- and high-sides of the bridge.

Detection and drive circuitry are also incorporated to control a reverse battery protection high-side MOSFET switch. PWM frequencies up to 28 kHz are possible. Built-in protection circuitry prevents damage to the MOSFET bridge as well as the drive IC and includes overvoltage shutdown, overtemperature shutdown, overcurrent shutdown, and undervoltage shutdown.

The device is parametrically specified over an ambient temperature range of -40°C ≤  $T_A$  ≤ 125°C and 5.5 V ≤  $V_{IGN}$  ≤ 24 V supply.

#### **Features**

- Drives Six N-Channel Low R<sub>DS(ON)</sub> Power MOSFETs

- **Built-In Charge Pump Circuitry**

- Built-In Current Sense Comparator and Output Drive Current Limiting

- Built-In PWM Mode Control Logic

- · Built-In Circuit Protection

- · Designed for Fractional to Integral HP BLDC Motors

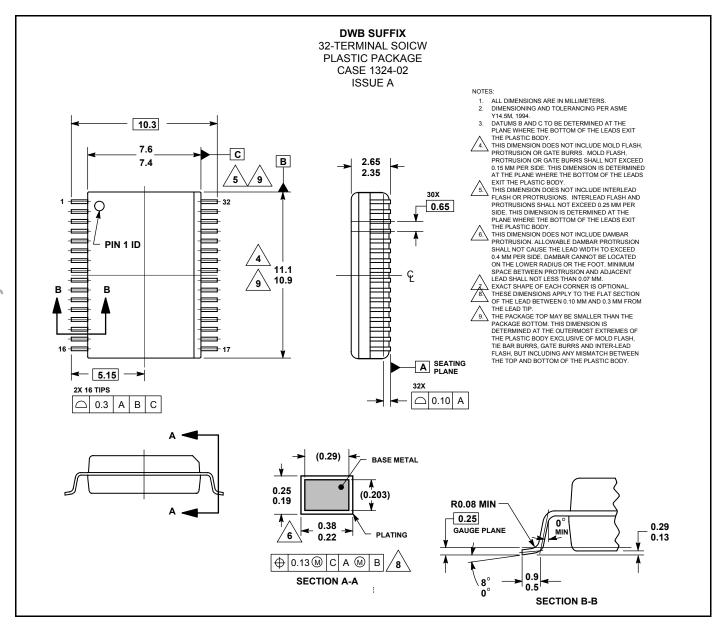

- 32-Terminal SOIC Wide Body Surface Mount Package

- 33395 Incorporates a <5.0 μs Shoot-Through Suppression Timer

- 33395T Incorporates a <1.0 μs Shoot-Through Suppression Timer</li>

# 33395 33395T

### THREE-PHASE GATE DRIVER IC

#### **ORDERING INFORMATION**

| Device         | Temperature<br>Range (T <sub>A</sub> ) | Package   |  |

|----------------|----------------------------------------|-----------|--|

| MC33395DWB/R2  | -40°C to 125°C                         | 32 SOICW  |  |

| MC33395TDWB/R2 | -40 0 10 123 0                         | 32 301CVV |  |

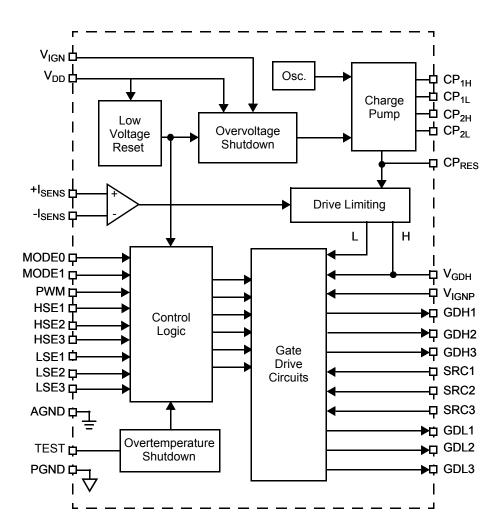

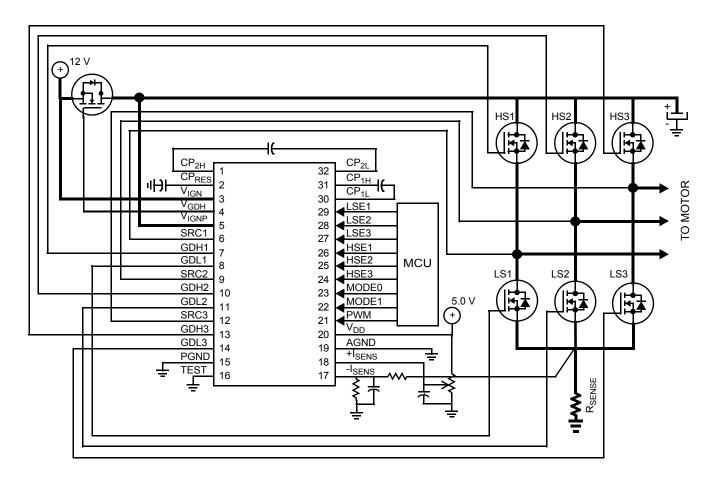

Figure 1. 33395 Simplified Internal Block Diagram

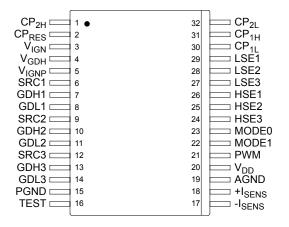

#### **TERMINAL FUNCTION DESCRIPTION**

| Terminal | Terminal Name      | Formal Name             | Definition                                                              |  |

|----------|--------------------|-------------------------|-------------------------------------------------------------------------|--|

| 1        | CP <sub>2H</sub>   | Charge Pump Cap         | High potential terminal connection for secondary charge pump capacitor  |  |

| 2        | CP <sub>RES</sub>  | Charge Pump Reserve Cap | Input from external reservoir capacitor for charge pump                 |  |

| 3        | $V_{IGN}$          | Input Voltage           | Input from ignition level supply voltage for power functions            |  |

| 4        | $V_{GDH}$          | High-Side Gate Voltage  | Output full-time gate drive for auxiliary high-side power MOSFET switch |  |

| 5        | V <sub>IGNP</sub>  | Input Voltage Protected | Input from protected ignition level supply for power functions          |  |

| 6        | SRC1               | High-Side Sense         | Sense for high-side source voltage, phase 1                             |  |

| 7        | GDH1               | Gate Drive High         | Output for gate high-side, phase 1                                      |  |

| 8        | GDL1               | Output for Gate         | Output for gate drive low-side, phase 1                                 |  |

| 9        | SRC2               | High-Side Sense         | Sense for high-side source voltage, phase 2                             |  |

| 10       | GDH2               | Gate Drive High         | Output for gate high-side, phase 2                                      |  |

| 11       | GDL2               | Output for Gate         | Output for gate drive low-side, phase 2                                 |  |

| 12       | SRC3               | High-Side Sense         | Sense for high-side source voltage, phase 3                             |  |

| 13       | GDH3               | Gate Drive High         | Output for gate drive high-side, phase 3                                |  |

| 14       | GDL3               | Gate Drive Low          | Output for gate drive low-side, phase 3                                 |  |

| 15       | PGND               | Power Ground            | Ground terminals for power functions                                    |  |

| 16       | Test               | Test Terminal           | This should be connected to ground or left open                         |  |

| 17       | -I <sub>SENS</sub> | IS Minus                | Inverting input for current limit comparator                            |  |

| 18       | +I <sub>SENS</sub> | IS Plus                 | Non-inverting input for current limit comparator                        |  |

| 19       | AGND               | Analog Ground           | Ground terminal for logic functions                                     |  |

| 20       | $V_{DD}$           | Logic Supply Voltage    | Supply voltage for logic functions                                      |  |

| 21       | PWM                | Pulse Width Modulator   | Input for pulse width modulated driver duty cycle                       |  |

| 22       | MODE1              | Mode Control Bit 1      | Input for mode control selection                                        |  |

| 23       | MODE0              | Mode Control Bit 0      | Input for mode control selection                                        |  |

| 24       | HSE3               | High-Side Enable        | Input for high-side enable logic, phase 3                               |  |

### **TERMINAL FUNCTION DESCRIPTION (continued)**

| Terminal | Terminal Name    | Formal Name             | Definition                                                                                       |

|----------|------------------|-------------------------|--------------------------------------------------------------------------------------------------|

| 25       | HSE2             | High-Side Enable        | Input for high-side enable logic, phase 2                                                        |

| 26       | HSE1             | High-Side Enable        | Input for high-side enable logic, phase 1                                                        |

| 27       | LSE3             | Low-Side Enable         | Input for low-side enable logic, phase 3                                                         |

| 28       | LSE2             | Low-Side Enable         | Input for low-side enable logic, phase 2                                                         |

| 29       | LSE1             | Low-Side Enable         | Input for low-side enable logic, phase 1                                                         |

| 30       | CP <sub>1L</sub> | External Pump Capacitor | Input from external pump capacitor for charge pump and secondary terminals                       |

| 31       | CP <sub>1H</sub> | External Pump Capacitor | Input from external pump capacitor for charge pump and secondary terminals                       |

| 32       | CP <sub>2L</sub> | Charge Pump Capacitor   | Input from external reservoir, external pump capacitors for charge pump, and secondary terminals |

#### **MAXIMUM RATINGS**

All voltages are with respect to ground unless otherwise noted

| Rating                                                       | Symbol                   | Value        | Unit |

|--------------------------------------------------------------|--------------------------|--------------|------|

| V <sub>IGN</sub> Supply Voltage                              | V <sub>IGN</sub>         | -15.5 to 40  | VDC  |

| V <sub>IGNP</sub> Load Dump Survival                         | $V_{IGNP_{LD}}$          | -0.3 to 65   | VDC  |

| V <sub>DD</sub> Logic Supply Voltage (Fail Safe)             | V <sub>DD</sub>          | -0.3 to 7.0  | VDC  |

| Logic Input Voltage (LSEn, HSEn, PWM, and MODEn)             | V <sub>IN</sub>          | 0.3 to 7.0   | VDC  |

| Start Up Current V <sub>IGNP</sub>                           | l <sub>VIGNStartUp</sub> | 100          | mA   |

| ESD Voltage Human Body Model (Note 1) Machine Model (Note 2) | V <sub>ESD1</sub>        | ±500<br>±200 | V    |

| Storage Temperature                                          | T <sub>STG</sub>         | -65 to 160   | °C   |

| Operating Ambient Temperature                                | T <sub>A</sub>           | -40 to 125   | °C   |

| Operating Case Temperature                                   | T <sub>C</sub>           | -40 to 125   | °C   |

| Maximum Junction Temperature                                 | T <sub>J</sub>           | 150          | °C   |

| Power Dissipation (T <sub>A</sub> = 25°C)                    | P <sub>D</sub>           | 1.5          | W    |

| Terminal Soldering Temperature                               | T <sub>SOLDER</sub>      | 240          | °C   |

| Thermal Resistance, Junction-to-Ambient                      | $R_{	heta JA}$           | 65           | °C/W |

#### Notes

- 1. ESD1 testing is performed in accordance with the Human Body Model ( $C_{ZAP}$  = 100 pF,  $R_{ZAP}$  = 1500  $\Omega$ ).

- 2. ESD2 testing is performed in accordance with the Machine Model ( $C_{ZAP}$  = 200 pF,  $R_{ZAP}$  = 0  $\Omega$ ).

#### STATIC ELECTRICAL CHARACTERISTICS

Characteristics noted under conditions -40°C  $\leq$  T<sub>A</sub>  $\leq$  125°C, 5.5 V  $\leq$  V<sub>IGNP</sub>  $\leq$  24 V unless otherwise noted. Typical values reflect approximate parameter mean at T<sub>A</sub> = 25°C under normal conditions unless otherwise noted.

| Characteristic                                                                                                                                                                                                            | Symbol                                   | Min               | Тур               | Max                  | Unit     |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------|-------------------|-------------------|----------------------|----------|

| POWER INPUT                                                                                                                                                                                                               |                                          |                   |                   | <b>-</b>             |          |

| V <sub>IGN</sub> Current @ 5.5 V-24 V, V <sub>DD</sub> = 5.5 V                                                                                                                                                            | I <sub>IGN</sub>                         | -                 | 0.2               | 1.0                  | mA       |

| V <sub>IGNP</sub> Current @ 5.5 V-24 V, V <sub>DD</sub> = 5.5 V                                                                                                                                                           | I <sub>IGNP</sub>                        | -                 | -                 | 100                  | mA       |

| V <sub>IGNP</sub> Overvoltage Shutdown                                                                                                                                                                                    | V <sub>IGNPSD</sub>                      | 25                | 33                | 36.5                 | V        |

| V <sub>IGNP</sub> Voltage                                                                                                                                                                                                 | V <sub>IGNP</sub>                        | 5.5               | _                 | 24                   | V        |

| $V_{DD}$ Current @ 5.5 VDC, 5.5 V $\leq$ $V_{IGNP} \leq$ 24 V                                                                                                                                                             | $I_{V_{DD}}$                             | -                 | 1.8               | 4.0                  | mA       |

| V <sub>DD</sub> Low-Voltage Reset Level                                                                                                                                                                                   | V <sub>DD(RESET)</sub>                   | 2.5               | 3.2               | 4.0                  | V        |

| V <sub>DD</sub> One-Time Fuse (Logic Supply)                                                                                                                                                                              | -                                        | 7.0               | _                 | _                    | V        |

| NPUT/OUTPUT                                                                                                                                                                                                               | 1                                        |                   | <b>-</b>          | 1                    |          |

| Input Current at V <sub>DD</sub> = 5.5 V<br>LSEn, HSEn, PWM, and MODEn = 3.0 V                                                                                                                                            | I <sub>IN</sub>                          | 5.0               | 12                | 25                   | μА       |

| Input Threshold at V <sub>DD</sub> = 5.5 V<br>LSEn, HSEn, PWM, and MODEn (Note 3)                                                                                                                                         | V <sub>TH</sub>                          | 1.0               | 2.0               | 3.0                  | V        |

| V <sub>SCRn</sub> Source Sense Voltage<br>SRC1, SRC2, SRC3                                                                                                                                                                | V <sub>SCRn</sub>                        | -0.3              | V <sub>IGNP</sub> | 24                   | V        |

| Comparator Input Offset Voltage                                                                                                                                                                                           | V <sub>INP(OFFSET)</sub>                 | 5.0               | 14                | 20                   | mV       |

| Comparator Input Bias Current                                                                                                                                                                                             | V <sub>INP(BIAS)</sub>                   | -500              | -170              | 500                  | nA       |

| Comparator Input Offset Current                                                                                                                                                                                           | I <sub>INP(OFFSET)</sub>                 | -300              | -3.0              | 300                  | nA       |

| Common Mode Voltage (Note 4)                                                                                                                                                                                              | V <sub>CMR</sub>                         | 0                 | -                 | V <sub>DD</sub> -2.0 | $V_{DC}$ |

| Comparator Differential Input Voltage (Note 4)                                                                                                                                                                            | $V_{INPdiff}$                            | -V <sub>DD</sub>  | -                 | +V <sub>DD</sub>     | V        |

| Charge Pump Voltage $V_{IGN}$ (Note 5)<br>$V_{IGNP} = 5.5 \text{ V}$ , $I_{CRES} = 1.0 \text{ mA}$<br>$V_{IGNP} = 9.0 \text{ V}$ , $I_{CRES} = 1.0 \text{ mA}$<br>$V_{IGNP} = 12 \text{ V}$ , $I_{CRES} = 5.0 \text{ mA}$ | V <sub>CRES</sub> -V <sub>IGNP</sub>     | 4.0<br>4.0<br>4.5 | 6.0<br>7.5<br>10  | 18<br>18<br>18       | V        |

| $V_{IGNP}$ = 24 V, $I_{CRES}$ = 1.0 mA<br>$V_{IGNP}$ = 24 V, $I_{CRES}$ = 5.0 mA                                                                                                                                          |                                          | 8.0<br>4.5        | 16<br>12          | 18<br>18             |          |

| $V_{GDH}$ Output Voltage with GDHn in ON State $V_{IGNP}$ = 5.5 V, $I_{GDHn}$ = 1.0 mA $V_{IGNP}$ = 12 V, $I_{GDHn}$ = 5.0 mA $V_{IGNP}$ = 24 V, $I_{GDHn}$ = 5.0 mA                                                      | V <sub>GDHn(on)</sub> -V <sub>SRCn</sub> | 4.0<br>4.0<br>4.5 | 5.2<br>9.0<br>11  | 18<br>18<br>18       | V        |

| $V_{GDH}$ Output Voltage with GDHn in OFF State $V_{IGNP}$ = SRCn = 14 V, $I_{GDHn}$ = 1.0 mA                                                                                                                             | V <sub>GDHn(off)</sub>                   | -1.0              | 0.6               | 1.0                  | V        |

#### Notes

- 3. Logic inputs LSEn, HSEn, PWM, and MODEn have internal 20  $\mu A$  internal sinks.

- 4. Guaranteed by design and characterization. Not production tested.

- 5. The Charge Pump has a positive temperature coefficient. Therefore the Min's occur at -40°C, Typ's at 25°C, and Max's at 125°C.

#### STATIC ELECTRICAL CHARACTERISTICS

Characteristics noted under conditions -40°C  $\leq$  T<sub>A</sub>  $\leq$  125°C, 5.5 V  $\leq$  V<sub>IGNP</sub>  $\leq$  24 V unless otherwise noted. Typical values reflect approximate parameter mean at T<sub>A</sub> = 25°C under normal conditions unless otherwise noted.

| Characteristic                                            | Symbol                | Min  | Тур | Max | Unit |

|-----------------------------------------------------------|-----------------------|------|-----|-----|------|

| INPUT/OUTPUT (continued)                                  |                       |      |     |     | •    |

| V <sub>GDL</sub> Low-Side Output Voltage GDHn in ON State | V <sub>GDL(on)</sub>  |      |     |     | V    |

| V <sub>IGNP</sub> = 5.5 V, I <sub>GDLn</sub> = 1.0 mA     |                       | 5.0  | 8.0 | 18  |      |

| V <sub>IGNP</sub> = 12 V, I <sub>GDLn</sub> = 5.0 mA      |                       | 8.0  | 14  | 18  |      |

| V <sub>IGNP</sub> = 24 V, I <sub>GDLn</sub> = 0.0 mA      |                       | 8.0  | 17  | 19  |      |

| $V_{IGNP}$ = 24 V, $I_{GDLn}$ = 5.0 mA                    |                       | 8.0  | 16  | 19  |      |

| V <sub>GDL</sub> Output Voltage GDHn in OFF State         | V <sub>GDL(off)</sub> |      |     |     | V    |

| V <sub>IGNP</sub> = 14 V, I <sub>GDLn</sub> = 1.0 mA      |                       | -1.0 | 0.3 | 1.0 |      |

| Thermal Shutdown (Note 6)                                 | T <sub>LIM</sub>      | 160  | _   | 190 | °C   |

#### Notes

6. Guaranteed by design and characterization. Not production tested.

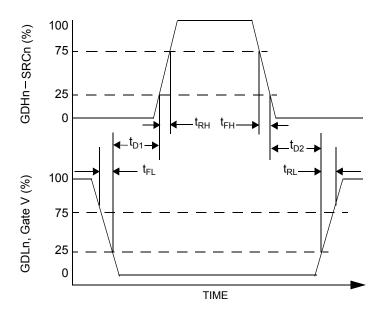

#### **DYNAMIC ELECTRICAL CHARACTERISTICS**

Characteristics noted under conditions -40°C  $\leq$  T<sub>A</sub>  $\leq$  125°C, 5.5 V  $\leq$  V<sub>IGNP</sub>  $\leq$  24 V unless otherwise noted. Typical values reflect approximate parameter mean at T<sub>A</sub> = 25°C under normal conditions unless otherwise noted.

| Characteristic                                                                                                 | Symbol                           | Min | Тур  | Max | Unit |

|----------------------------------------------------------------------------------------------------------------|----------------------------------|-----|------|-----|------|

| High-Side (GDHn) and Low-Side Drivers (GDHn) Rise Time (25% to 75%), C <sub>ISS</sub> Value = 2000 pF (Note 7) | t <sub>RH</sub>                  | -   | 0.35 | 1.5 | μs   |

| High-Side (GDHn) and Low-Side Drivers (GDHn) Fall Time                                                         | t <sub>FH</sub>                  |     |      |     | μS   |

| (75% to 25%), C <sub>ISS</sub> Value = 2000 pF (Note 7)                                                        |                                  | -   | 0.25 | 1.5 |      |

| Shoot-Through Suppression Time Delay (33395) (Note 7), (Note 8)                                                | t <sub>D1,</sub> t <sub>D2</sub> |     |      |     | μ\$  |

| 33395                                                                                                          |                                  | 1.0 | 3.0  | 5.5 |      |

| 33395T                                                                                                         |                                  | 0.2 | 0.65 | 1.0 |      |

| Current Limit Time Delay (Note 9)                                                                              | t <sub>ILIMDELAY</sub>           | 1.5 | 2.8  | 5.0 | μ\$  |

#### Notes

- See <u>Figure 2</u>, page 9.

- 8. Shoot-Through Suppression Time Delay is provided to prevent directly connected high- and low-side MOSFETs from being on simultaneously.

- 9. Current Limit Time Delay: The internal comparator places the device in the current limit mode when the comparator output goes LOW and sets an internal logic bit. This takes a finite amount of time and is stated as the Current Limit Time Delay.

## **Timing Diagram**

Figure 2. Shoot-Through Suppression

### SYSTEM/APPLICATION INFORMATION

#### INTRODUCTION

The 33395 and 33395T devices are designed to provide the necessary drive and control signal buffering and amplification to enable a DSP or MCU to control a three-phase array of power MOSFETs such as would be required to energize the windings of powerful brushless DC (BLDC) motors. It contains built-in

charge pump circuitry so that the MOSFET array may consist entirely of N-Channel MOSFETs. It also contains feedback sensing circuitry and control circuitry to provide a robust overall motor control design.

#### **FUNCTIONAL DESCRIPTION**

#### **Gate Drive Circuits**

The gate drive outputs (GDH1, GDH2, etc.) supply the peak currents required to turn ON and hold ON the MOSFETs, as well as turn OFF and hold OFF the MOSFETs.

#### **Charge Pump**

The current capability of the charge pump is sufficient to supply the gate drive circuit's demands when PWM'ing at up to 28 kHz. Two external charge pump capacitors and a reservoir capacitor are required to complete the charge pump's circuitry.

Charge reservoir capacitance is a function of the total MOSFET gate charge  $(Q_{G})$  gate drive voltage level relative to the source  $(V_{GS})$  and the allowable sag of the drive level during the turn-on interval  $(V_{SAG}).\ C_{RES}$  can be expressed by the following formula:

$$C_{RES} = \frac{Q_G x V_{GS}}{2 x V_{GS} x V_{SAG} - V_{SAG}^2}$$

For example, for  $Q_G$  = 60 nC,  $V_{GS}$  = 14 V,  $V_{SAG}$  = 0.2 V:

$$C_{RES} = \frac{(60 \text{ nC}) \text{ x } (14 \text{ V})}{2 \text{ x } (14 \text{ V}) \text{ x } (0.2 \text{ V}) - (0.2)^2} = 0.15 \text{ }\mu\text{F}$$

Proper charge pump capacitance is required to maintain, and provide for, adequate gate drive during high demand turn-ON intervals. Use the following formula to determine values for  $C_{P1}$  and  $C_{P2}$ :

For example, for the above determination of  $C_{RES} = 0.15 \mu F$ :

$$\frac{C_{RES}}{20} \le C_{P1} = C_{P2} \le \frac{C_{RES}}{10}$$

By averaging these two values, the proper  $C_{\mbox{\footnotesize{Pn}}}$  value can be determined:

$$\frac{0.15 \ \mu F}{20}$$

= 0.075  $\mu F$ , lower limit; and  $\frac{0.15 \ \mu F}{10}$  = .015  $\mu F$ , upper limit

$$C_{P1}$$

and  $C_{P2}$  =(0.0075  $\mu F$  + 0.015  $\mu F$ )  $\div$  2 = 0.01  $\mu F$

#### **Thermal Shutdown Function**

The device has internal temperature sensing circuitry which activates a protective shutdown function should the die reach excessively elevated temperatures. This function effectively limits power dissipation and thus protects the device.

### **Overvoltage Shutdown Function**

When the supply voltage ( $V_{\rm IGN}$ ) exceeds the specified overvoltage shutdown level, the part will automatically shut down to protect both internal circuits as well as the load. Operation will resume upon return of  $V_{\rm IGN}$  to normal operating levels.

### **Low Voltage Reset Function**

When the logic supply voltage ( $V_{DD}$ ) drops below the minimum voltage level or when the part is initially powered up, this function will turn OFF and hold OFF the external MOSFETs until the voltage increases above the minimum voltage level required for normal operation.

#### **Control Logic**

The control logic block controls when the low-side and high-side drivers are enabled. The logic implements the Truth Table found in the specification and monitors the M0, M1, PWM, CL, OT, OV, LSE, and HSE terminals. Note that the drivers are enabled 3  $\mu s$  after the PWM edge. During complimentary chop mode the high-side and low-side drives are alternatively enabled and disabled during the PWM cycle. To prevent shoot-through current, the high-side drive turn-on is delayed by  $t_{\rm D1}$ , and the low-side drive turn on is delayed by  $t_{\rm D2}$  (see Figure 2, page 9).

Note that the drivers are disabled during an overtemperature or overvoltage fault. A flip-flop keeps the drive off until the following PWM cycle. This prevents erratic operation during fault conditions. The current limit circuit also uses a flip-flop for latching the drive off until the following PWM cycle.

**Note** PWM must be toggled after POR, Thermal Limit, <u>or</u> overvoltage faults to re-enable the gate drivers.

### V<sub>GDH</sub>

The  $V_{GDH}$  terminal is used to provide a gate drive signal to a reverse battery protection MOSFET. If reverse battery protection is desired,  $V_{IGN}$  would be applied to the source of an external MOSFET, and the drain of the MOSFET would then deliver a "protected" supply voltage ( $V_{IGNP}$ ) to the three phase array of external MOSFETs as well as the supply voltage to the  $V_{IGNP}$  terminal of the IC.

In a reverse polarity event (e.g., an erroneous installation of the system battery), the  $V_{GDH}$  signal will not be supplied to the external protection MOSFET, and the MOSFET will remain off and thus prevent reverse polarity from being applied to the load and the  $V_{IGNP}$  supply terminal of the IC.

### **High-Side Gate Drive Circuits**

Outputs GDH1, GDH2, and GDH3 provide the elevated drive voltage to the high-side external MOSFETs (HS1, HS2, and HS3; see Figure 3, page 13). These gate drive outputs supply the peak currents required to turn ON and hold ON the high-side MOSFETs, as well as turn OFF the MOSFETs. These gate drive circuits are powered from an internal charge pump, and therefore compensate for voltage dropped across the load that is reflected to the source-gate circuits of the high-side MOSFETs.

#### **Low-Side Gate Drive Circuits**

Outputs GDL1, GDL2, and GDL3 provide the drive voltage to the low-side external MOSFETs (LS1, LS2, and LS3; see Figure 3). These gate drive outputs supply the peak currents required to turn ON and hold ON the low-side MOSFETs, as well as turn OFF the MOSFETs.

### V<sub>DD</sub> Fuse

The  $V_{DD}$  supply of the 33395 IC has an internal fuse, which will blow and set all outputs of the device to OFF, if the  $V_{DD}$  voltage exceeds that stated in the maximum rating section of the data sheet. When this fuse blows, the device is permanently disabled.

### I<sub>SENS</sub> Inputs

The +I<sub>sens</sub> and -I<sub>sens</sub> terminals are inputs to the internal current sense comparator. In a typical application, these would receive a a low-pass filtered voltage derived from a current

sense resistor placed in series with the ground return of the three-phase output bridge. When triggered by the comparator, the CL (current limit) bit of the internal error register is set, and the output gate drive pairs (i.e., GDH1 and GDL1, GDH2 and GDL2, GDH3 and GDL3), are controlled such that current will cease flowing through the load (refer to Table 1, Truth Table, page 12).

# Overtemperature and Overvoltage Shutdown Circuits

Internal monitoring is provided for both over temperature conditions and over voltage conditions. When any of these conditions presents itself to the IC, the corresponding internally set bits of the error register are set, and the output gate drive pairs (i.e., GDH1 and GDL1, GDH2 and GDL2, GDH3 and GDL3), are controlled such that current will cease flowing through the load (refer to Table 1).

#### **LSE and HSE Input Circuits**

The low-side enable input terminals (LSE1, LSE2, LSE3) and high-side enable input terminals (HSE1, HSE2, HSE3) form the input pairs (HSE1 and LSE1, HSE2 and LSE2, HSE3 and LSE3) which set the logic states of the output gate drive pairs (i.e., GDH1 and GDL1, GDH2 and GDL2, GDH3 and GDL3) in accordance with the logic set forth in the Truth Table (page 12). Typically these inputs are supplied from an MCU or DSP to provide the phasing of the currents applied to a brushless dc motor's stator coils via the output MOSFET pairs.

#### **PWM Input**

The pulse width modulation input provides a single input terminal to accomplish PWM modulation of the output pairs in accordance with the states of the Mode 0 and Mode 1 inputs as set forth in the Truth Table (page 12).

### **Mode Selection Inputs**

The mode selection inputs (Mode 0 and Mode 1) determine the PWM implementation of the output pairs in accordance with the logic set forth in the Truth Table (page 12). PWM'ing can thus be set to occur either on the high-side MOSFETs or the low-side MOSFETs, or can be set to occur on both the high-side and low-side MOSFETs as "complementary chopping".

#### **Test Terminal**

This terminal should be grounded or left floating (i.e., do not connect it to the printed circuit board). It is used by the automated test equipment to verify proper operation of the internal overtemperature shut down circuitry. This terminal is susceptible to latch-up and therefore may cause erroneous operation or device failure if connected to external circuitry.

#### Table 1. Truth Table

The logic state of each output pair, GDLn and GDHn (n = 1, 2, 3), is a function of its corresponding input pair, LSEn and HSEn (n = 1, 2, 3), along with the logic states of the MODEn and PWM inputs and the internally set overtemperature shutdown (OT), overvoltage (OV), and current limit (CL) bits provided in this table.

### NORMAL OPERATION

| Switching Modes |       | Interr | Internally Set Bits |    |      | Input Pairs<br>(e.g., LSE2 and HSE2) |      | t Pairs<br>and GDH2) |

|-----------------|-------|--------|---------------------|----|------|--------------------------------------|------|----------------------|

| MODE1           | MODE0 | ОТ     | ov                  | CL | LSEn | HSEn                                 | GDLn | GDHn                 |

| 0               | 0     | 0      | 0                   | 0  | 0    | 0                                    | 0    | 0                    |

| 0               | 0     | 0      | 0                   | 0  | 0    | 1                                    | 0    | 1                    |

| 0               | 0     | 0      | 0                   | 0  | 1    | 0                                    | PWM  | 0                    |

| 0               | 0     | 0      | 0                   | 0  | 1    | 1                                    | 0    | 0                    |

| 0               | 1     | 0      | 0                   | 0  | 0    | 0                                    | 0    | 0                    |

| 0               | 1     | 0      | 0                   | 0  | 0    | 1                                    | 0    | 1                    |

| 0               | 1     | 0      | 0                   | 0  | 1    | 0                                    | PWM  | PWM                  |

| 0               | 1     | 0      | 0                   | 0  | 1    | 1                                    | 0    | 0                    |

| 1               | 0     | 0      | 0                   | 0  | 0    | 0                                    | 0    | 0                    |

| 1               | 0     | 0      | 0                   | 0  | 0    | 1                                    | 0    | PWM                  |

| 1               | 0     | 0      | 0                   | 0  | 1    | 0                                    | 1    | 0                    |

| 1               | 0     | 0      | 0                   | 0  | 1    | 1                                    | 0    | 0                    |

| 1               | 1     | 0      | 0                   | 0  | 0    | 0                                    | 0    | 0                    |

| 1               | 1     | 0      | 0                   | 0  | 0    | 1                                    | PWM  | PWM                  |

| 1               | 1     | 0      | 0                   | 0  | 1    | 0                                    | 1    | 0                    |

| 1               | 1     | 0      | 0                   | 0  | 1    | 1                                    | 0    | 0                    |

#### **FAULT MODE OPERATION**

| Switching Modes |       | Interr | Internally Set Bits |    | Input<br>(e.g., LSE2 | Input Pairs<br>(e.g., LSE2 and HSE2) |      | t Pairs<br>and GDH2) |

|-----------------|-------|--------|---------------------|----|----------------------|--------------------------------------|------|----------------------|

| MODE1           | MODE0 | ОТ     | OV                  | CL | LSEn                 | HSEn                                 | GDLn | GDHn                 |

| 0               | 0     | 0      | 0                   | 1  | 0                    | 0                                    | 0    | 0                    |

| 0               | 0     | 0      | 0                   | 1  | 0                    | 1                                    | 0    | 1                    |

| 0               | 0     | 0      | 0                   | 1  | 1                    | 0                                    | 0    | 0                    |

| 0               | 0     | 0      | 0                   | 1  | 1                    | 1                                    | 0    | 0                    |

| 0               | 1     | 0      | 0                   | 1  | 0                    | 0                                    | 0    | 0                    |

| 0               | 1     | 0      | 0                   | 1  | 0                    | 1                                    | 0    | 1                    |

| 0               | 1     | 0      | 0                   | 1  | 1                    | 0                                    | 0    | 1                    |

| 0               | 1     | 0      | 0                   | 1  | 1                    | 1                                    | 0    | 0                    |

| 1               | 0     | 0      | 0                   | 1  | 0                    | 0                                    | 0    | 0                    |

| 1               | 0     | 0      | 0                   | 1  | 0                    | 1                                    | 0    | 0                    |

| 1               | 0     | 0      | 0                   | 1  | 1                    | 0                                    | 1    | 0                    |

| 1               | 0     | 0      | 0                   | 1  | 1                    | 1                                    | 0    | 0                    |

| 1               | 1     | 0      | 0                   | 1  | 0                    | 0                                    | 0    | 0                    |

| 1               | 1     | 0      | 0                   | 1  | 0                    | 1                                    | 1    | 0                    |

| 1               | 1     | 0      | 0                   | 1  | 1                    | 0                                    | 1    | 0                    |

| 1               | 1     | 0      | 0                   | 1  | 1                    | 1                                    | 0    | 0                    |

| Х               | х     | Х      | 1                   | Х  | х                    | х                                    | 0    | 0                    |

| х               | х     | 1      | Х                   | Х  | х                    | х                                    | 0    | 0                    |

Figure 3. Typical Application Diagram

### **PACKAGE DIMENSIONS**

**NOTES**

Information in this document is provided solely to enable system and software implementers to use Motorola products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits or integrated circuits based on the information in this document.

Motorola reserves the right to make changes without further notice to any products herein. Motorola makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Motorola assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters which may be provided in Motorola data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. Motorola does not convey any license under its patent rights nor the rights of others. Motorola products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Motorola product could create a situation where personal injury or death may occur. Should Buyer purchase or use Motorola products for any such unintended or unauthorized application, Buyer shall indemnify and hold Motorola and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Motorola was negligent regarding the design or manufacture of the part.

MOTOROLA and the Stylized M Logo are registered in the US Patent and Trademark Office. All other product or service names are the property of their respective owners.

© Motorola, Inc. 2004

#### **HOW TO REACH US:**

**USA/EUROPE/LOCATIONS NOT LISTED:** Motorola Literature Distribution P.O. Box 5405, Denver, Colorado 80217 1-800-521-6274 or 480-768-2130

JAPAN: Motorola Japan Ltd.; SPS, Technical Information Center 3-20-1 Minami-Azabu. Minato-ku, Tokyo 106-8573, Japan 81-3-3440-3569

**ASIA/PACIFIC:** Motorola Semiconductors H.K. Ltd.; Silicon Harbour Centre 2 Dai King Street, Tai Po Industrial Estate, Tai Po, N.T., Hong Kong 852-26668334

HOME PAGE: http://motorola.com/semiconductors